тора, выход которого подключен к первым входам восьмого и девятого элементов И, второй вход восьмого элемента И соединен с выходом триггера записи, а выход - входом формироват

теля записи, второй вход девятого элемента И связан с выходом триггера считывания, а выход - с третьим входом первого триггера управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления для памяти на цилиндрических магнитных доменах | 1984 |

|

SU1265855A1 |

| Устройство управления для доменной памяти | 1982 |

|

SU1056267A1 |

| Устройство управления для доменной памяти | 1984 |

|

SU1265856A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737510A1 |

| Блок управления для доменного запоминающего устройства | 1982 |

|

SU1022217A1 |

| Устройство формирования маскирующих сигналов для доменной памяти | 1986 |

|

SU1317480A1 |

| Устройство управления буферным накопителем для доменной памяти | 1981 |

|

SU1275536A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

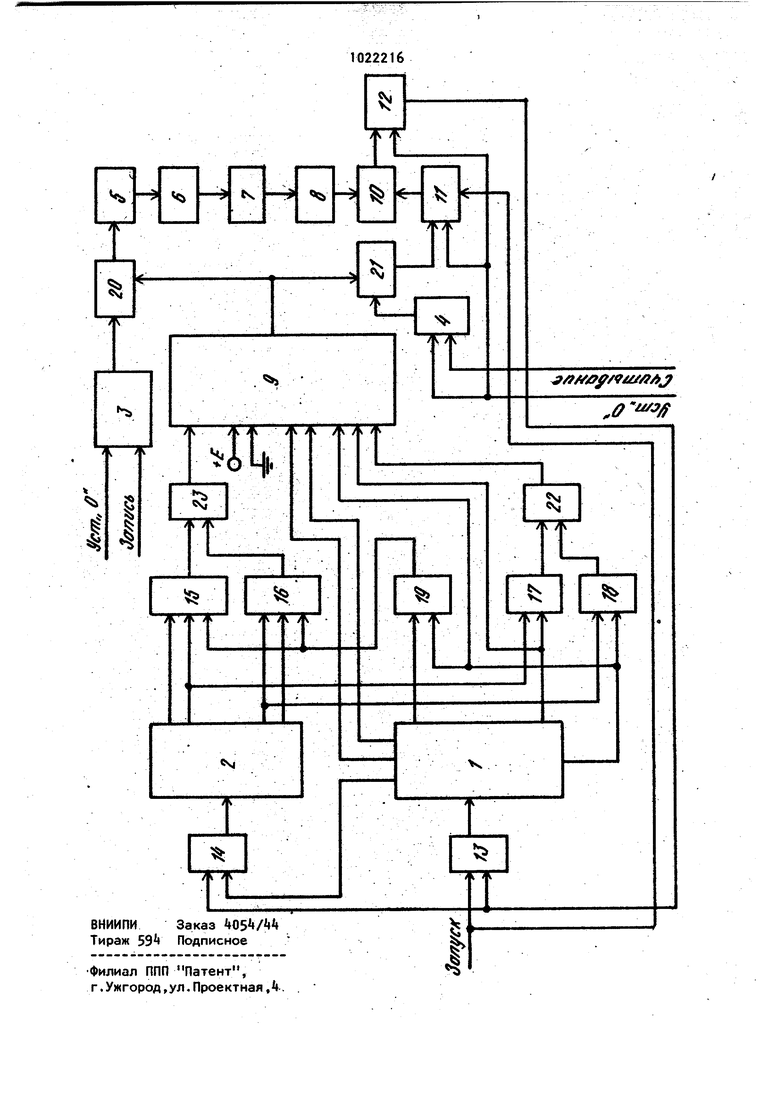

Изобретение относится к вычислительной технике и может быть использовано для проверки и контроля запоминающих устройств цифровых вычислительных машин на цилиндрических магнитных доменах ЦМД . Известно запоминающее устройство с блокировкой неисправных запоминающих элементов, содержащее регистр адреса, соединенный через дешифратор адреса с основным накопителем, регистр слова, подключенный к первому блоку контроля, основному и дополнительному накопителям, блок пере адресации неисправных групп разрядов соединенный с регистром адреса, реги стром слова, дополнительным накопите лем и счетчиком, блок управления, кодирующий блок, элементы И, ИЛИ, второй блок контроля Устройство имеет повышенную надеж ность в результате блокировки неисправ ных ячеек с помощью дополнительного накопителя, однако в нем не предусмотрено формирование различных кодов их последовательная запись и сравнение считанной информации с первоначально записанной в одном цикле проверки памяти. Наиболее близким к предлагаемому является запоминающее устройство с блокировкой неисправных запоминающих ячеек, содержащее первый регистр адреса, подключенныйчерез дешифрато адреса к накопителю, соединенному с регистром числа, второй регистр адреса, блок управления, дополнитель ный регистр, схему сравнению и счетмик.2 ., . Известное устройство обладает сравнительной простотой и повышен ной над ежностью за счет блокировки неисправных ячеек, адреса которых мо гут быть записаны в накопитель, однако в нем не предусмотрена последовательная запись различной информации в накопитель с последующим срав-нением ее со считываемой информацией 8 одном цикле проверки накопителя. 3 этом устройстве отсутствуют блоки, предусматривающие блокировку всего устройства с фиксацией неисправных адресов и разрядов. Эти недостатки особенно существенны при проверке и контроле последовательных запоминающих устройств (типа устройств на цилиндрических магнитных доменах, где запись и считывание информации производятся чаще всего по одному каналу (разряду, и время контроля даже для одного однотипного кода ; очень значительно. Автоматическая же проверка с контролем и блокировкой неисправных адресов по всем тяжелым кодам в таком устройстве практически невозможна. В результате надежность и достоверность контроля блоков памяти (особенно доменной памяти остаются низкими, что ухудшает надежность цифровых вычислительных машин, в которых эти блоки используются. Цель изобретения - повышение надежности устройства для контроля доменной памяти. Поставлнная цель достигается тем, что устройство для контроля доменной памяти; содержащее два счетчика, триггеры записи и считывания, соединенные с кодовой шиной Установка О и соответственно с кодовыми шинами .Запись и Считывание, формирователь записи, выход которого ЯЕ}ляется выходом устройства, и триггер числа, содержит коммутатор, первый вход которого соединен с положительной клеммой источника питания, второй вход - с шиной нулевого потенциала, блок сравнения, первый вход которого подключен к триггеру числа, первый триггер управления, первый вход которого связан с кодовой шиной Запуск, второй вход - с О, а кодовой шиной Установка выход - с вторым входом блока сравг нения, второй триггер управления, первый вход которого соединен с бло ком сравнения, а второй вход - с ко довой шиной Установка О, элементы И и ИЛИ, причем первые входы пер вого и второго элементов И подключе ны к выходу второго триггера управ ления, второй вход первого элемента И - к. кодовой шине Запуск, выход первого элемента И - к входу первого счетчика, первый выход которого связан с вторым входом второго элемента И, выход которого подключен к входу второго счетчика, первый выход которого соединен с первым входо третьего элемента И, второй выход с первым входом четвертого элемента И, третий выход - с вторым входом третьего элемента И и первым входом пятого элемента И, четвертый выход - с вторым входом четвертого элемента И и первым входом шестого элемента И, второй выход первого счетчика подключен к третьему входу коммутатора, второму входу шестого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, и к первому входу седьмого элемента И, выход которого соединен с третьими входами третьего и четвертого элементов И, третий вь|ход первого счетчика подключен к четвертому входу коммутатора и к второму входу пятого элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, выход которого связан с пятым входом коммутатора четвертый выуод первого счетчика под ключен к второму входу седьмого элемента И, а пятый и шестой выходы к шестому и седьмому входам коммутатора, выходы третьего и четвертого элементов И связаны с первым и вторы входами второго элемента ИЛИ, выход которого соединен с восьмым входом коммутатора, выход которого подключен к первым входам восьмого и девятого элементов И, второй вход вось мого элемента И соединен с выходом триггера записи, а выход - с входом формирователя записи, второй вход де вятого элемента И связан с выходом триггера считывания, а выход с третьим входом первого триггера управления. Предлагаемое устройство позволяет осуществлять запись всевозможных ко64дов в доменную память CB том числе и всех тяжелых кодов ), производить считывание информации из накопителя и ее автоматическое сравнение с тем, что было записано. При этом производится фиксация неисправной информации и адреса как по адресу записанной страницы (адресу группы слов), так и по адресу такта ( адресу конкратного разряда в группе слов). На чертеже представлена блоксхема предлагаемого устройства для . контроля доменной памяти. Устрюйство для контроля доменной памяти содержит первый и второй счетчики 1 и 2, триггеры 3 записи и k считывания, соединенные с кодовой шиной Установка О и соответственно с кодовыми шинами Запись и Считывание, формирователь 5 записи, подключенный к накопителю 6 на НМД, соединенному с усилителем 7 считывания, связанным с триггером 8 числа. С целью повышения надежности и достоверности контроля доменной памяти в устройство введены коммутатор 9, блок 10 сравнения, первый триггер 11 управления, второй триггер 12 управления, девять элементов И 13-21 и два элемента ИЛИ 22 и 23. Устройство работает следующим образом. Первоначально сигналом Установка О все блоки и элементы устройства устанавливаются в исходное состояние (в первую очередь триггер 3 записи, триггер считывания, первый 11 и второй 12 триггеры управления. После этого на устройство поступает сигнал Запуск, который в случае отсутствия потенциала запрета с три|- гера 12 через первый элемент И 13 проходит на первый счетчик 1 и далее через второй элемент И l на второй счетчик 2. Первый 1 и второй 2 счетчики формируют всю временную диаграмму работы накопителя 6 на ЦМД, включая и создание вращающегося магнитного поля. Но этим не исчерпываются функции первого 1 и второго 2 счетчиков. С помощью третьего; четвертоГО; пятого, шестого и седьмого элеентов И 15 - 19 и первого 22 и второго 23 элементов ИЛИ они формируют разнообразные коды для записи инфорации в накопитель 6 на ЦМД и для контроля информации при ее считываии из накопители 6. Эти коды поступают на коммутатор 9, имеющий столько входов, сколько кодов формируется в устройстве, и один выход соединенный с входами восьмого 20 и девятого 21 элементов И. От источника питания через коммутатор осуществляется запись всех 1 и всех О в накопитель 6 на ЦМД. С помощью сигналов, снимаемых с первого разряда первого счетчика 1 (счетчик тактов) по второму и третьему выходам (..прямой и инверсный выходы осущест вляется запись прямого и обратного шахматных кодов в регистр связи накопителя 6. Сигналы, снимаемые с третьего разряда первого счетчика 2 по пятому и шестому выходам, позволяют записывать в накопитель 6 прямой и обратный код перемещающихся трех 1 и трех О в регистр связи Пятый 17 и шестой 18 элементы И и первый элемент ИЛИ 22 осуществляют запись прямого и обратного кодов в регистры хранения накопителя. С помощью третьего 15, четвертого 1б и седьмого 19 элементов И и второго элемента. ИЛИ 23 осуществляется формирование записи перемещающихся трех 1 и одного О и наоборот в регист ре хранения накопителя 6. Формирование различных кодов может быть расширено применением различных комбинаций элементов И и ИЛИ и соединением их с различными разрядами первого и второго счетчиков 1 и 2. В режиме записи после установки в О триггера 3 записи сигналом Установка О и запуска первого счетчика 1 Л счетчика тактов) и вто рого счетчика 2 (счетчика страниц триггер 3 записи устанавливается в 1 сигналом Запись, и в соответ ствующие такты общего цикла с коммутатора 9 импульсы записи кодов, определяющие какой-то определенный код будут проходить через восьмой эле4мент И 20 на формираватель 5 записи осуществляя запись этого кода в нако питель 6. При этом запись может быт осуществлена как в определенную страницу накопителя 6, так и во вес накопитель. При переключении в режим считывания ввиду отсутствия сигнала запис 166 импульсы с коммутатора 9 не будут проходить на запуск формирователя 5 записи, но в то же время при подаче сигнала Считывание триггер k считывания устанавливается в 1, разрешая прохождение в определенные такты общего цикла импульсов с коммутатора 9 через девятый элемент И 21 на запуск триггера 11, который в начале каждого такта устанавливается в О. Если с коммутатора 9 поступает импульс сигнал 1 , то первый триггер 11 устанавливается в 1, если нет импульса сигнал О , то он остается в состйянии О. Одновременно, в- определенные такты общего цикла из накопителя 6 производится считывание информации, которая после усиления в ус1 лителях 7считывания поступает на триггер 8числа, устанавливая его в каждом такте в сос тояние 1 или О. Информация, которая была записана в накопитель 6 и теперь поступившая на первый дополнительный триггер 11, и информация, считанная из накопителя 6 и теперь поступившая на триггер 8 числа, сравниваются на блоке 10 сравнения. В случае идентичности этих двух информации производится считывание информации в следующем такте. В противном случае сигнал несравнения устанавливает в 1 триггер 12, который блокирует работу 1 и второго 2 счетчиков, фиксируя номер неисправной страницы (группы слов) в накопителе 6 и номер такта (разряда в данной группе слов;. Таким образом, использование изобретения позволяет автоматически формировать разнообразные тяжелые коды записи в накопитель на ЦМД (как во весь накопитель, так и в отдельные страницы), затем производить опрос накопителя и автоматически сравнивать записанные и считанные сигналы, что значительно повышает надежность и достоверность контроля доменной памяти, увеличивая общую надежность проверки и контроля устройств памяти цифровых вычислительных машин.

«

r /

f

Ni

I

/ k f

iS

t . I

ff//ff /9 /ffAJ

,0

«Vl

Ni /Л л

«

V7 Г7 г

r7v

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Оперативное запоминающее устройство с блокировкой неисправных запоминающих элементов | 1975 |

|

SU556502A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР №+92935, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| . | |||

Авторы

Даты

1983-06-07—Публикация

1982-02-26—Подача