11з(|бре 1 СНИС относился к FJbI4Ht IHTe, lbной технике и может ohiib использовано при nor i jioeiiHH .wji o:viHf aK)iiuix стройств на ци. ш ирических ма1 нит111)1х доменах (НМД). 11,е. 1ы) и;«)0ре1ен11я является новышенне быст)о;1ейстБия и на.и- жиостн устройства формирования маекирук)ни1Х сигналов для доменной памяти.

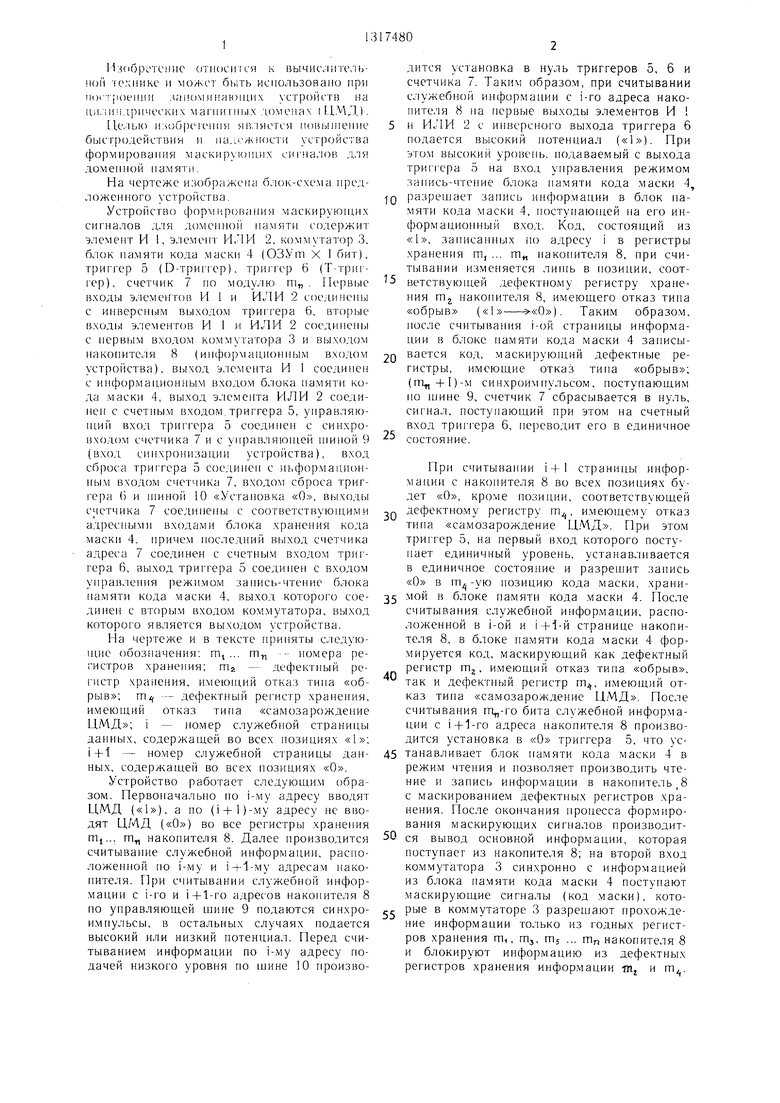

На чертеже изображена блок-схема нред- ложенного устройства.

Устройство формнрС Ва1Н1я 1аскируюн1нх сигналов д:1я доменно намяти содержит элемент И 1, элемент ИЛИ 2, коммутатор 3. блок намяти кода маски 4 (ОЗУт X 1 бит), триггер о (D-триггер), триггер 6 (Т триг- 1Ч р), ечетчик 7 по модулю т„ . Иервые входы элементов И 1 и ИЛИ 2 соединен| 1 с инверсным выходом триггера 6, вторые входы элементов И I и ИЛИ 2 соединены с нервым входом коммутатора 3 и выходом наконителя 8 (информационным входом устройства), выход элемента И 1 соединен с информанионньгм входом блока памяти кода .маски 4, выход элемента ИЛИ 2 соединен с счетны.м входом, триггера 5, уиравляю- 1НИЙ вход тригтера 5 еоединен е еинхро- входо.м счетчика 7 и с унравляюн1ей Н1иной 9 (вход синхронизации устройства), вход сброса триггера 5 еоединен с и.форманион- ньгм входом счетчика 7, входом сброса триггера () и тиной 10 «Уетановка «О, вьгчоды счетчика 7 соединены с соответствуюн1ими адрес1 ыми входами блока хранения кода маски 4, нричем иоеледний выход счетчика адреса 7 соединен с счетньгм входо.м триггера 6, выход триггера 5 соединен с входом унравления режи.мом запись-чтение блока намяти кода маски 4, выход которого соединен с вторым входом ком.мутатора, выход которог О являетея выходом устройства. На чертеже и в тексте нриняты следуюН1ие обозначения; гп ... гп.,, номера региетров хранения; т - дефектный регистр хранения, имеюгций отказ тииа «обрыв ; гп, - дефектный регистр хранения, и.меющий отказ тина «самозарождение i - номер служебной етранины данных, содержащей во всех позициях + - номер служебной страницы данных, содержащей во всех позициях «О.

Устройство работает следующим образом. Нервоначально но i-.му адресу вводят ЦМД («1), а но (1 + 1)-.му адресу не вводят ЦМД («О) во вее регистры хранения nij.., m накопителя 8. Далее нроизводится считывание служебной информации, расположенной но i-му и i-f-1-му адресам накопителя. При считывании служебной информации е i-ro и i+1-го адресов накопителя 8 по управляющей шине 9 подаются синхро- и.мнульсы, в остальных случаях подается высокий или низкий потенциал. Иеред считыванием информации по i-.му адресу подачей низкого уровня по шине 10 нроизво0

5

0

5

0

0

дится установка в нуль триггеров 5, 6 и счетчика 7. Таким образом, при считывании служебной ин({зормации с i-ro адреса нако- щггеля 8 на первые выходы элементов И 1 и ИЛИ 2 с инверсного вы.хода триггера б подается высокий нотенпиал («1). Нри этом высокий уровень, подаваемый с выхода триггера 5 на вход унравления режимом заиись-чтепие блока иамяти кода маски 4, разрен.1ает запись информации в блок памяти кода маски 4, поступающей на его информационный вход. Код, состоящий из «1, записанных по адресу i в регистры храпения т, ... т„ накопителя 8, при считывании из.меняется лишь в позиции, соот- ветствуюихей дефектному регистру хранения гп накопителя 8, имеющего отказ тина

«обрыв (). Таким образом,

носле считывания i-ой страницы информации в блоке памяти кода маски 4 записывается код, маскируюн;ий дефектные регистры, имеющие отказ тина «обрыв ; (ггц,+1)-м синхроимпульсом, поступающим по тине 9, счетчик 7 сбрасывается в нуль, сигнал, поступаюц.шй при этом на счетный вход триггера 6, не|)еводит его в единичное состояние.

Нри ечитывании i + 1 страницы информации с наконителя 8 во всех позициях будет «О, кроме позиции, соответствующей дефектному регистру пт, имеющему отказ

типа «самозарождение ЦМД. При этом триггер 5, на нервый вход которого поступает единичный уровень, устанавливается в единичное состояние и разрешит запись «О в позицию кода маски, храни5 мой в блоке памяти кода .маски 4. Носле считывания служебной информации, расположенной в 1-ой и i+i-й странице накопителя 8, в блоке намяти кода .маски 4 формируется код, маскирующий как дефектный регистр rOj, имеющий отказ типа «обрыв, так и дефектный регистр mj,, имеющий отказ типа «самозарождение ЦМД. После считывания гтц-го бита служебной инфор.ма- ции с i-fl-ro адреса накопителя 8 производится установка в «О триггера 5, что ус5 тапавливает блок намяти кода маски 4 в режим чтения и позволяет производить чтение и запись инфор.мации в накопитель,8 с маскированием дефектны.х регистров хранения. Носле окончания процесса формирования маскирующих сигналов производит0 ся вывод основной информации, которая ноступает из накопителя 8; на второй вход коммутатора 3 еинхронно с информацией из блока на.мяти кода маски 4 поступают маскирующие сигналы (код .маски), котог рые в коммутаторе 3 разрешают прохождение информации только из годных регистров хранения т,, mj, nij ... irin накопителя 8 и блокируют ипформацию из дефектных

регистров хранения информации irij и m

tФормула изобретения

Устройство формирования маскирующих сигналов AviH доменной памяти, содержащее блок памяти кода маски, счетчик и коммутатор, отличающееся тем, что, с целью повышения быстродействия и надежности устройства, оно содержит элемент И, элемент ИЛИ и два триггера, первые входы элементов И и ИЛИ подключены к инверсному выходу первого триггера, вторые входы элементов И и ИЛИ подключены к первому входу коммутатора и являются информационным входом устройства, выход элемента И подключен к информационному входу блока памяти кода маски, выход элемента ИЛИ подключен к счетному входу

0

5

второго триггера, управляющий вход которого подключен к синхровходу счетчика и является входом синхронизации устройства, вход сброса второго триггера подключен к информационному входу счетчика, входу сброса первого триггера и является установочным входом устройства, выходы счетчика соединены с соответствующими адресными Е ходами блока памяти кода маски, а последний выход счетчика подключен к счетному входу первого триггера, выход второго триггера подключен к входу управления режимом запись-чтение блока памяти кода маски, выход которого подключен к второму входу коммутатора, выход которого является выходом устро,йства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования маскирующих сигналов для доменного запоминающего устройства | 1981 |

|

SU1020861A1 |

| Устройство формирования маскирующих сигналов для доменной памяти | 1987 |

|

SU1429165A1 |

| Накопитель для запоминающего устройства на цилиндрических магнитных доменах | 1982 |

|

SU1084891A1 |

| Устройство управления для памяти на цилиндрических магнитных доменах | 1984 |

|

SU1265855A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1984 |

|

SU1188787A1 |

| Устройство управления для доменной памяти | 1984 |

|

SU1265856A1 |

| Устройство для контроля доменной памяти | 1982 |

|

SU1022216A1 |

| Устройство управления буферным накопителем для доменной памяти | 1981 |

|

SU1275536A1 |

| Устройство для обхода дефектных регистров в доменной памяти (его варианты) | 1985 |

|

SU1305773A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737510A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении запоминающих устройств на цилиндрических магнитных доменах (ЦМД). Целью изобретения является повыщение быстродействия и надежности устройства формирования маскирующих сигналов для доменной памяти. Устройство формирования маскирующих сигналов для доменной памяти содержит элемент И 1, элемент ИЛИ 2, коммутатор 3, блок памяти кода маски 4 (ОЗУ m X 1 бит), триггер 5 jl (D-триггер), триггер 6 (Т-триггер), счетчик 7 по модулю Шп. Первые входы элементов И 1 и ИЛИ 2 соединены с инверсным выходом триггера 6, вторые входы элементов И 1 и ИЛИ 2 соединены с первым входом коммутатора 3 и выходом накопителя 8 (информационным входом устройства), выход элемента и 1 соединен с информационным входом блока памяти кода маски 4, выход элемента ИЛИ 2 соединен со счетным входом триггера 5, управляющий вход триггера 5 соединен с синхровходом счетчика 7 и с управляющей шиной 9 (в.ход синхронизации устройства), вход сброса триггера 5 соединен с информационным, входом счетчика 7, входом сброса триггера 6 и щи- ной 10 «Установка «О, выходы счетчика 7 соединены с соответствующими адресными входами блока хранения кода маски 4, причем последний выход счетчика адреса 7 соединен с счетным входом триггера 6, выход триггера 5 соединен со входом управления режимом запись-чтение блока памяти кода маски 4, выход которого соединен со вторым входом коммутатора, выход которого является вы.ходом устройства. 1 ил. (Л со оо /77 /TJj /77f /77.,

| Патент США № 4090251, кд | |||

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Устройство для формирования маскирующих сигналов для доменного запоминающего устройства | 1981 |

|

SU1020861A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-06-15—Публикация

1986-01-06—Подача