блока итерации соединен с.входом -i+l)-ro разряда первого регистра последующего вычислительного блока итерации,, выходы первого и второго сумматоров предыдущего вычислительного блока итерации подключен соответственно к входам второго.и третьего регистров последующего вычислительного блока итерации, выход первого разряда первого сумматора (ii-2)-ro вычислительного блока итерации соединен с информационным входом триггера, выход второго сумматора (и 2)-го вычислительного блока итерации подключен к входу четвертого регистра устройства, второй вход третьего cyiviMaTopa, устройства и третьи входы вторых сумматоров каждого вычислитель,ного блока итерации соединены с шиной логического нуля, управляющие входы триггера и всех регистров соединены с выходом генератора тактовых импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Узловой элемент цифровой сетки для решения краевых задач | 1984 |

|

SU1246111A1 |

| Арифметико-логическое устройство | 1988 |

|

SU1599853A1 |

| Конвейерное устройство для вычисления функции @ = @ | 1981 |

|

SU964635A1 |

| Конвейерное устройство для вычисления функции Y=е @ | 1981 |

|

SU962927A1 |

| Процессор цифровой обработки сигналов | 1990 |

|

SU1789991A1 |

| Конвейерное устройство для вычисления функций синуса и косинуса | 1981 |

|

SU1003080A1 |

| Узловой процессор | 1986 |

|

SU1399763A1 |

| Устройство для вычисления квадратного корня | 1983 |

|

SU1141407A1 |

| Конвейерное устройство для вычисления гиперболических функций | 1981 |

|

SU1026141A1 |

| Устройство для вычисления степенных функций | 1985 |

|

SU1282120A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМОВ ДВОИЧНЫХ ЧИСЕЛ , содержащее два регистра, группу элементов 2И-ИЛИ, вход устройства соединен с входом первого регистра, инверсный выход второго регистра подключен к первому информационному входу группь элементов 2И-ИЛИ, отличающееся тек,что, с целью повышения быстродействия в него дополнительно введены три регистра, четыре сумматора, генератор тактовых импульсов. Триггер и (и-2) вычислительных блоков итерации, где V) - разрядность входного числа, причем выход i -го разряда первого регистра соединен с входом (i+2)-разряда второго регистра, второй информационный вход группы элементов 2И-ИЛИ подключен со сдвигом на два разряда вправо к вьЕходу л -го разряда третьего регистра, прямой выход первого разряда которого соединен с первым управляющим входом группы элементов 2И-ИЛИ, второй управляющий вход которой подключен к инверсному выходу первого разряда третьего регистра, выход i-го разряда первого регистра соединен с первым входом U+1.)-разряда и с вторым входом i-го разряда первого .сумматора, выход которого подключен к информационному входу третьего регистра, выход которого соединен с первым информационным, входом второго Сумматора, второй информационный вхЪд которого подключен к выходу группы элементов 2И-ИЛИ, инверсный выход первого разряда третьего регистра соединен с первым входом третьего сумматора, инверсный выход триггера подключен к первому входу четвертого сумматора, второй вход которого соеди- нен с выходом четвертого регистра, выход четвертого сумматора через пятый регистр подключен к выходу устройства, в каждом вьлчислительном блоке итерации, содержащем три регистра, группу элементов 2И-ИЛИ и два сумматора, инверсный выход первого регистт ра соединен с первым информационным . входом группы элементов 2И-ИЛИ, вы- § ход i -го разряда ВТОРОГО регистра сое-; динен с первым информационным входом первого сумматора и c(-i + j +2 -разрядом второго информационного входа группы элементов 2И-ИЛН, где - l,2,...,m(i- номер разряда регистра) , 1, 2,.,. ,И ()- номер вычислительного блока итерации), выход группы элементов 2И-ИЛИ подключен к второму информационному входу первого сумматора, первыйуправляющий вход группы элементов 2И-ИЛИ соединен с прямым выходом первого разряда второго регистра-, инверсный . вьдход которого подключен к второму управляющему входу группы элементов 2И-ИЛИ и первому входу второго, сумматора, второй вход которого соединен с выходом третьего регистра, кроме того вь;ход i -го разряда группы элементов 2И-ИЛИ устройства соединен с входом (-1 +1 )-го разряда первого регистра первого вычислительного блока итерации, выходы второго и третьего сумматоров устройства подключены соответственно к входам второго и третьего регистров первого вычислительного блока итерации, выход i -го разряда группы элементов 2И-ИЛИ предыдущего вычислительного .

Изобретение относится к вычисли- тельной технике и может быть использовано в универсальных и специализированных ЦВМ для логарифмирования больших массивов многоразрядных чисел.

Известно цифровое устройство для логарифмирования двоичных чисел, содержащее два сумматора, сдвиговый регистр, схему И-ИЛН, схему И, треггер, запоминающий блок, блок управления 11.

Недостатками известного устройства являются низкое быстродействие, а также необходимость хранения в памяти констант.

Наиболее близким к изобретению является устройство воспроизведения логарифмической и обратной зависимости , содержащее три регистра, счетчик, две схелы И-ИЛИ 2 .:

Недостатком известного устройства является низкое быстродействие.

Цель изобретения - повьлиение быстродействия устройства.

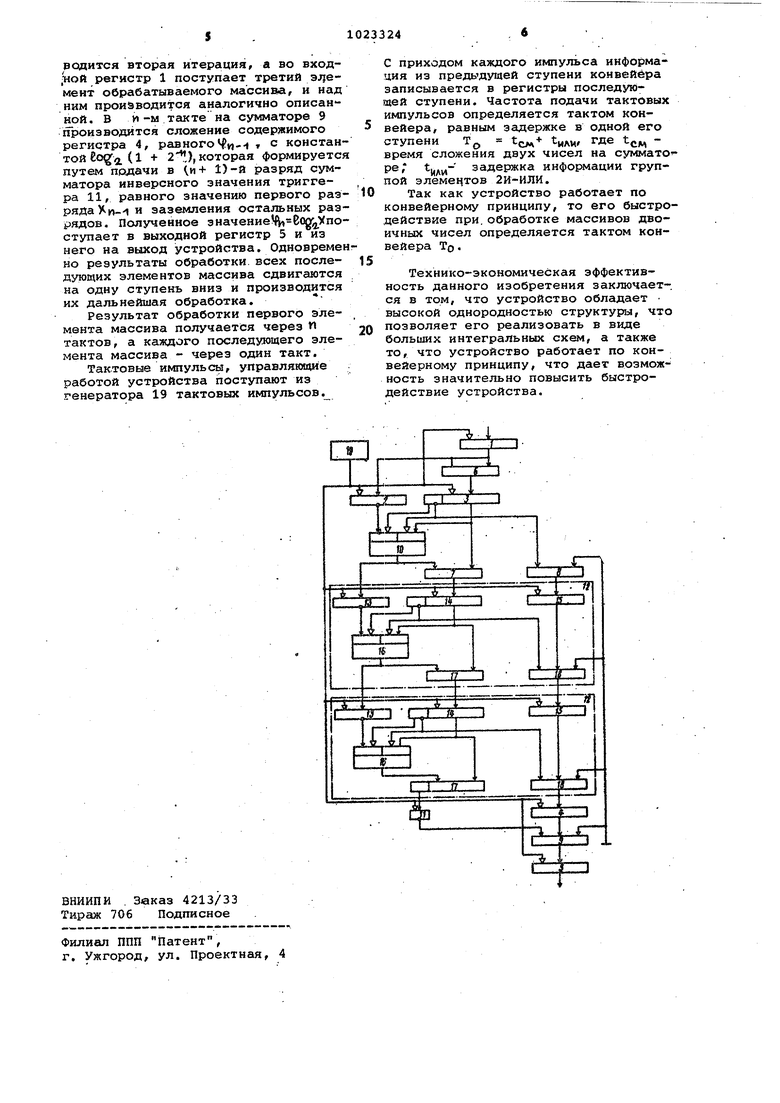

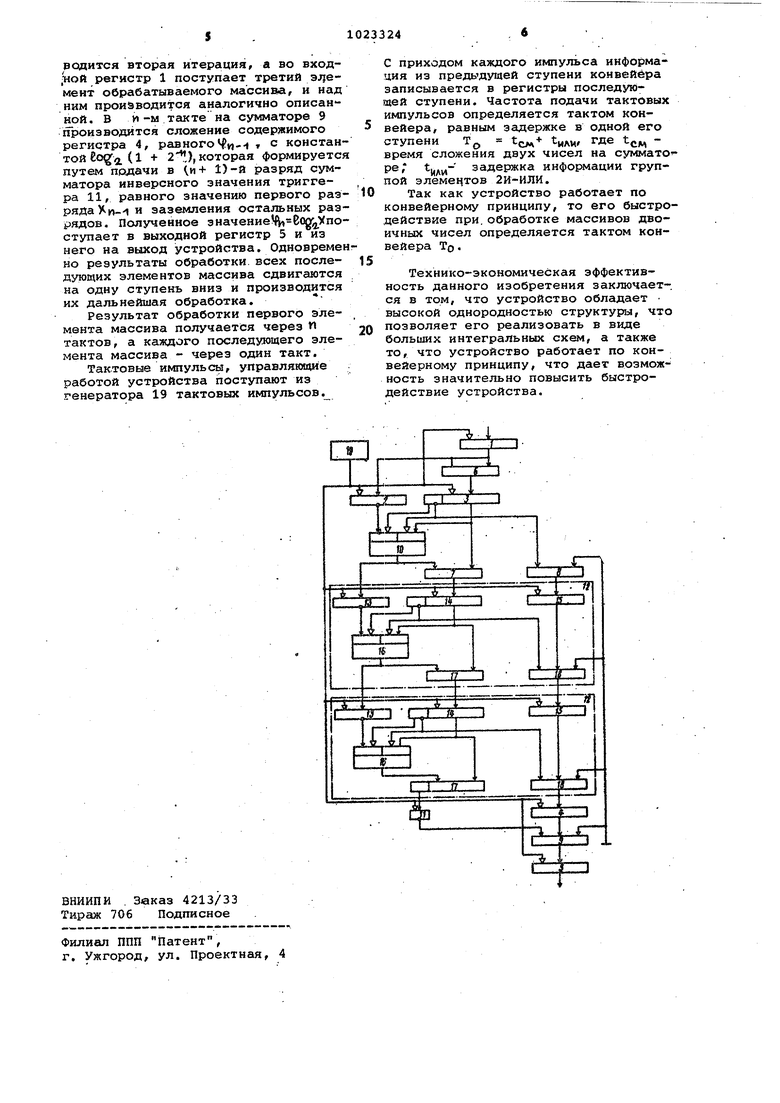

Поста1вленная цель достигаемся тем что в устройство для вычисления логарифмом двоичных-г чисел, содержащее два регистра, группу элементов 2И-ИЛ вход устройства соединен с входом пе вого регистра,; инверсный выход второго регистра подключен к первому информационному входу группы элементов 2И-ИЛИ, дополнительно введены три регистра, четыре сумматора, генератор тактовых импульсов, триггер и (и -2) в лчислительных блоков итерации, где разрядность входного числа, причем выход i-го разряда первого регистра соединен с входрм ( -i +2 ) разряда второго регист ра, второй информационный вход групп элементов 2И-ИЛИ подключен со сдвигом на два разряда вправо к выходу -го разряда третьего регистра, прямой выход первого разряда которого соединен с первым управляющим входом группы элементов 2И-ИЛИ, второй управляющий вход которой подключен к инверсному выходу первого разряда тре.тьего регистра, выход i разряда первого регистра соединен с первым входом () разряда и со вторым входом 1 -го разряда первого сумматора, выход которого подключен к информационному входу третьего регистра, выход которюго соединен с первым информационным входом второго сумматора, второй информационный вход которого подключен к выходу группы элементов 2И-ИЛИ, инверсный выход первого разряда третьего регистра соединен с первьм входом третьего сумматора, инверсный выход триггера подключен к первому входу четвертого сумматора, второй вход которого соединен с выходом четвертого регистра, выход четвертого сумматора через пятый регистр подключен к выходу устройства, в каждом вычислительном блоке итерации, содержащем три регистра, группу элементов 2И-ИЛИ и два сумматора, инверсный выход первого регистра соединен с первым информационным входом группы элементов 2И-ИЛИ,выход -го раЭ ряда второго регистра соединен с первым информационным входом первого сумматора и cf-i-I-j Ч-2) разрядом второго информационного входа группы элементов 2И-ИЛИ, где ( 1 1,2,.,.,т) i- номер разряда регистра, С ,...,} j - номер вычислительного блока итерации, выход группы элементов 2И-ИЛИ подключен к второму информационному вгходу первого сумматора, первый управляющий вход группы элементов 2И-ИЛИ соединен с прямым выходом первого разряда второго регистра, ин;зерсный выход которого подключен к второму управляющему входу группы, элементов 2И-ИЛН и первому входу второго сум1.1атора, второй вход которого соединен с выходом третьего регистра, кроме того, выход i-го разряда группы элементов 2И-ИЛИ устройства соединен с входом (1+1)-го разряда первого регистра первого вычислительного блок итерации, выходы второго и третьего суммато ро8 устроис7ва подключены соо ветственно к входам второго и третье го регистров первого вычислительного блока итерации, выход -i-го разряда группы элементов 2И-ИЛИ предыдущего вычислительного блока итерации соеди ней со входом (-i +1)-го разряда первого регистра последующего вычислительного блока итерации/ выходы первого и второго сумматоров предаадущего вычислительного блока итерации подключены соответственно к входам второго и, третьего регистров последующего вычислительного елока итерации, первого разряда первого сумматора (и -2 ) -го вычислительного блока итерации соединен с информационным входом триггера, выход второго сумматора |vi-2)-ro вычислительного блока итерации подключен к входу четвертого регистра устройства, второй вход третьего cyi taTOpa устройст ва-и третьи входа вторых сумматоров каждого вычислительного блока итерации соединены с шиной логического ну ля, управляющие входы триггера и все регистров соединены с выходом генератора тактовых импульсов. На чертеже изображена блок-схема устройства, Устройство сбдержит регистры 1-5, сумматоры 6-9, группу элементов 2И-ИЛИ 10, триггер 11, («-2) вычислительных блока 12 итерации, каждый из которых содержит регистры 13-15, группу элементов 2И-ЙЛИ 1-6, сумматор Г7 и 18, а также генератор 19 тактовых импульсов. Устройство предназначено для вычи ления функции нормализованных чисел, представленных в формате с фиксированной запятой. Алгоритм вычисления описывается следующими итерационными формулами N. .у- ) -fe.Vl. О 1 1 . . ,(), . to . f ч-.еслм Хч7/- ; TI I О, если Xi j которые при начальных значениях О ,% О , дают послеп, итераций Ч вод. Устройство состоит из и ступеней, в каждой из которых выполняется одна итерация вычислительного процес са. Число и равно разрядности обра батываемых чисел. Устройство работает следующим образом. В первом такте число X поступает во входной регистр 1. Содержимое ре гистра 1, а также его содержимое, сдвинутое на один разряд вправо, по с тупают на сумматор 6, на Buxjo ie оторого формируется выргокение VoH + (l-). Во втором такте-содержимое регистра 1, сдвинутое на .два разряда вправо, записывается в регистр 2,.а значение Хч с выходов сумматора 6 в регистр 3. Если у «: 1, т.е. первый разряд регистра;з, отображающий целую часть числа Х , нулю, то сигнал с .инверсного выхода первого разряда регистра 3 разрадает iipo-хождение на сумматор 7 через группу элементов 2И-ИЛИ 10 содержимого регистра 3, сдвинутого на два разряда вправо, т.е. . Если же Х;,/, то по сигналу с прямого выхода разряда perHctpa 3 через группу элементов 2Й-ИЛИ 10 проходит инверсное значение содержимого регистра 2, равное - Хо Таким образом, в группе элементов 2И-ИЛИ 10 формируется значение . Данное значение поступает на сумматор 7, где сум-. мируется с содержимым регистра 3, равным Х . На сумматоре 7 формируется значение Х . Подача содержимого регистра 2 на сумматор 7 обратньф кодом позволяет заменить операцию вычитания операцией сложения. . Константыeog,, + 2-) ( 1 + 2 / формируются на входах суммматора 8. Константа BoQ. 1 ) в двоичном коде имеет значение 0,100101011100, . а константа Bog (i + 2) 0,010100100111. Здесь принято, что п 12.Для их формирОва|1ия в разряды. сумматора, где значение разряда кОнстант ,ты равно единице,подается обратное значение первого разряда регистра 3. Если X-i 1, то в данные разряды по-, ступают единицы, если Х 7/ 1, то нули. Остальные разряды сумматора заземлены, т.е. на их входда постоянно подается значение логического р. Таким образом, на сумматоре 8 формируется значение этом же такте во входной регистр 1 поступает второй элемент массива, и над ним п.ро-. изводятся операции, которые были выполнены в первом такте над первым операндом. В. третьем такте значение 1# из группы элементов 2И-ИЛИ 10, сдвинутое на разряд вправо, записывается в регистр 13, в регистры 14 и 15 ,. записываются соответственно значения с выходов сумматоров 7 и 8. В группе элементов 2И-ИЛИ 16 первого вычислительного блока 12 формируется значение Э,, на сумматоре 17 -. Xj, на cyivD/iaTope 18 - этом же такте в регистры 2 и 3 записываются промежуточные результаты обработки второго элемента массива, над ними ВО второй ступени устройства произэодится вторая итерация, а во вход,тной регистр 1 поступает третий sjjeмент обрабатываемого массива, и над ним производится аналогично описанной. В и-м такте на сумматоре 9 производится сложение содержимого регистра 4, равного Ч vj--i т с константой .( + ,), которая формируется путем подачи в (,и+ 1)-й разряд сумматора инверсного значения триггера 11, равного значению первого разряда )ц и заземления остальных разрядов. Полученное значение% В(Упоступает в выходной регистр 5 и из него на выход устройства. Одновременно результаты обработки всех последующих элементов массива сдвигаются на одну ступень вниз и производится их дальнейшая обработка.

Результат обработки первого элемента массива получается через w тактов, а каждого последующего элемента массива - через один такт.

Тактовые импульсы, управляющие работой устройства поступают из генератора 19 тактовых импульсов.

С приходом каждого импульса информация из предыдущей ступени конвейера записывается в регистры последук)щей ступени. Частота подачи тактовых импульсов определяется тактом конвейера, равным задержке в одной его ступени Tjj tcM- W,, где t время сложения двух чисел на суммато ре; задержка инфорялации группой элементов 2И-ИЛИ.

0 Так как устройство работает по конвейерному принципу, то его быстродействие при. обработке массивов двоичных чисел определяется тактом конвейера TO .

Технико-экономическая эффективность данного изобретения заключает-, ся в том, что устройство обладает высокой однородностью структуры, что

0 позволяет его реализовать в виде больших интегральных схем, а также то, что устройство работает по конвейерному принципу, что дает возможность значительно повысить быстродействие устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровое устройство для логарифмирования двоичных чисел | 1972 |

|

SU448459A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Данчеев В.П | |||

| Цифро-частотные вычислительные устройства | |||

| М., Энергия, 1976, с | |||

| Устройство для сортировки каменного угля | 1921 |

|

SU61A1 |

Авторы

Даты

1983-06-15—Публикация

1981-10-08—Подача