соединен с входом сдвига на один разряд в сторону старших разрядов четвертого регистра, тактовым входом пятого регистра и входом второго распределителя импульсов, четвертый выход первого распределителя импульсов соединен с вторыми входами второго и третьего злементов И, пятый выход первого распределителя импульсов соединен с тактовым входом третьего регистра, разрядные выходы которого соединены со сдвигом на один разряд в сторону младших с первой группой разрядных входов счетчика, вторая и третья группы разрядных входов счетчика соединены соответственно с прямыми и инверсными разрядными выходами четвертого

регистра, разрядные выходы счетчика соединены соответственно с информационными входами третьего регистра, выходы второго распределителя импульсов с первого по k-й ( V- разрядность результата) соединены соответственно с вторыми входами элементов И группы, выходы которых соединены соответственно с информационными входами пятого регистра, вхЪд кода аргумента устройства соединен со сдвигом на 2fT разрядов в сторону старших (т - число разрядов дробной части результата) с информационными входами первого регистра, V-й выход второго распределителя импульсов соединен с вторым входом третьего элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1983 |

|

SU1108442A1 |

| Устройство для извлечения квадратного корня | 1983 |

|

SU1132289A1 |

| Вычислительное устройство | 1982 |

|

SU1070545A1 |

| Интегро-дифференциальный вычислитель | 1983 |

|

SU1108445A2 |

| Вычислительное устройство | 1983 |

|

SU1144105A2 |

| Устройство для логарифмирования | 1978 |

|

SU711560A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1335989A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ. КВАДРАТНОГО КОРНЯ, содержащее первый, второй и третий регистры, схе My сравнения, сумматор, блок управления, содержащий генератор импульсов и первьй элемент И, первый.вход которого соединен с выходом генератора импульсов, информационные выходы первого регистра соединены с первой группой входов схемы сравнения, вторая группа входов которой соединена с выходами сумматора и с информационными входами второго регистра, входы первого слагаемого сумматора соединены с выходами треть его регистра, отличающеес я тем, что, с целью повышения быстродействия устройства, в него введены счетчик, группа элементов И, четвертьй и пятый регистры, а в блок управления - первый и второй распределители импульсов, второй и третий элементы И, три элемента ИЛИ, элемент НЕ, триггер, выход которого соединен с вторым входом первого элемента И, выход которого соединен с входом первого распределителя импульсов, выход схемы сравнения соединен с первыми входами элементов И группы, первым входом второго элемента И и входом элемента НЕ, выход которого соединен с первым вxoдo третьего элемента И, выход которого соединен с первым входом первого элемента ИЛИ, с входом разрешения вычитания счетчика и входом синхронизации второго регистра, информационные выходы кото(Л рого соединены с входами второго слагаемого сумматора, второй вход первого элемента ИЛИ соединен с выходом второго элемента ИЛИ и входом сложения счетчика, первый вход вто(Рого элемента Ш1И соединен с выходом второго элемента И, вход синхронизации устройства соединен с входом 4 синхронизации первого регистра и S1 первым входом третьего элемента ИЛИ, выход которого соединен с входом О триггера, первый выход первого Pficч пределителя импульсов соединен с тактовым входом счетчика и входом сдвига на три разряда в сторону мпадг ших разрядов четвертого регистра, второй выход первого распределителя импульсов соединен с вторым входом второго элемента ИЛИ, выход которого соединен с входом разрешения сложения счетчика, вход управления счетом которого соединен с выходом первого элемента ИЛИ, третий выход первого распределителя импульсов

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении специализированных вычислительных устройств, функциональных преобразователей информации и как специализированньш процессор больших ЦВМ.

Известно устройство для вычисления квадратного корня,- содержар(ее три сумматора, счетчик, схему сравнения, блок 1зентилей сдвига и три регистра Cl .

Недостатком устройства является невысокое быстродействие.

Наиболее близким по технической сущности к предлагаемому является устройство для вычисления квадратного корня, содержащее первый, второй и третий регистры, схему сранения, первый и второй накапливающие сумматоры, блок управления, блок памяти, при этом информационные выходы первого регистра соединены с первой группой входов схемы сравнения, выход которой соединен с первым входом блока управления, с второй группой входов схемы сравнения соединены выходы первого сумматора, которые также соединены с информационными входами второго регистра, входы первого сумматора соединены с информационными выходами третьего регистра, информационные входы которого соединены с выходами второго сумматора, которые также соединены с информационньми входами первого регистра, входы второго сумматора подключены к информационным выходам второго регистра, информационные входы регистра второго накапливаюп;его сумматора соединены с входом кода аргумента, а также с выходами первого сумма:тора, первый выход блока памяти подключен к второму входу блока управления, а второй выход блока памяти - к информационным входам второго регистра, вход блока памяти соединен с первым выходом блока управления, второй выход которого соединен с входом синхронизации второго регистра, к тактируют(ему входу второго сумматора подключен третий выход блока управления, четвертьй выход которого соединен с входом синхронизации третьего регистра, пятый выход блока управления подключен к тактирующему входу первого сумматоIра, к третьему входу схемы сравнрния подключен шестой выход блока управления, седьмой выход которого соединен с входом синхронизации первого регистра 2.

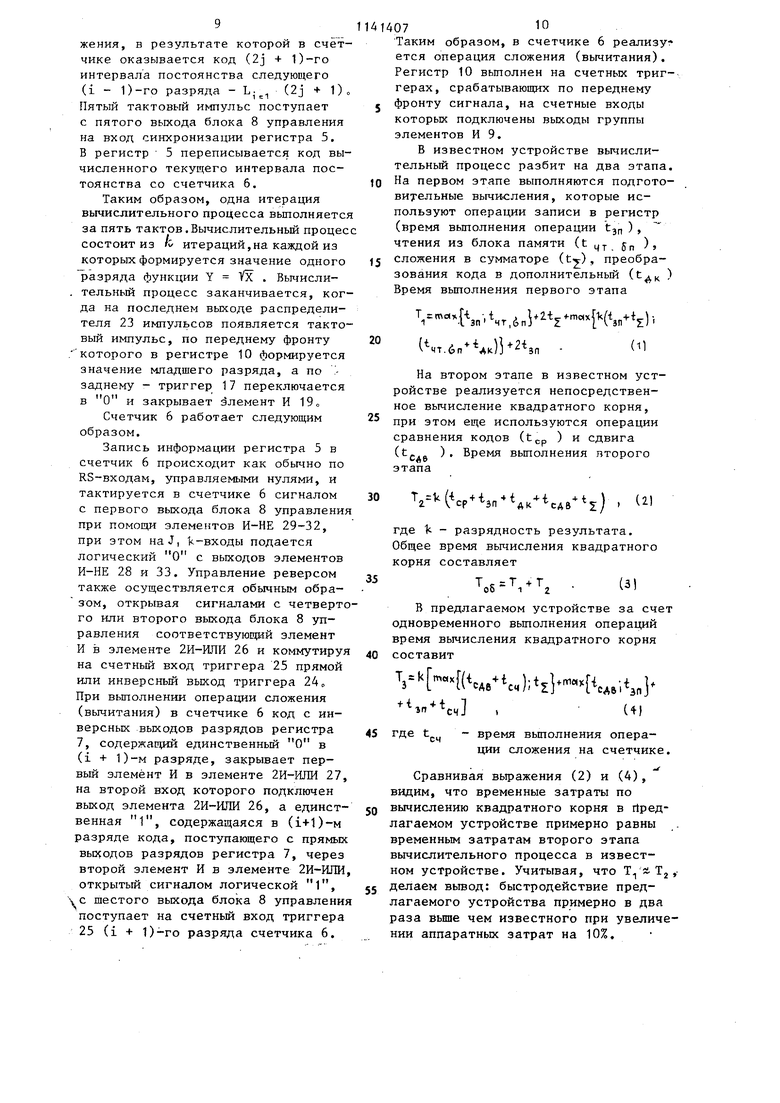

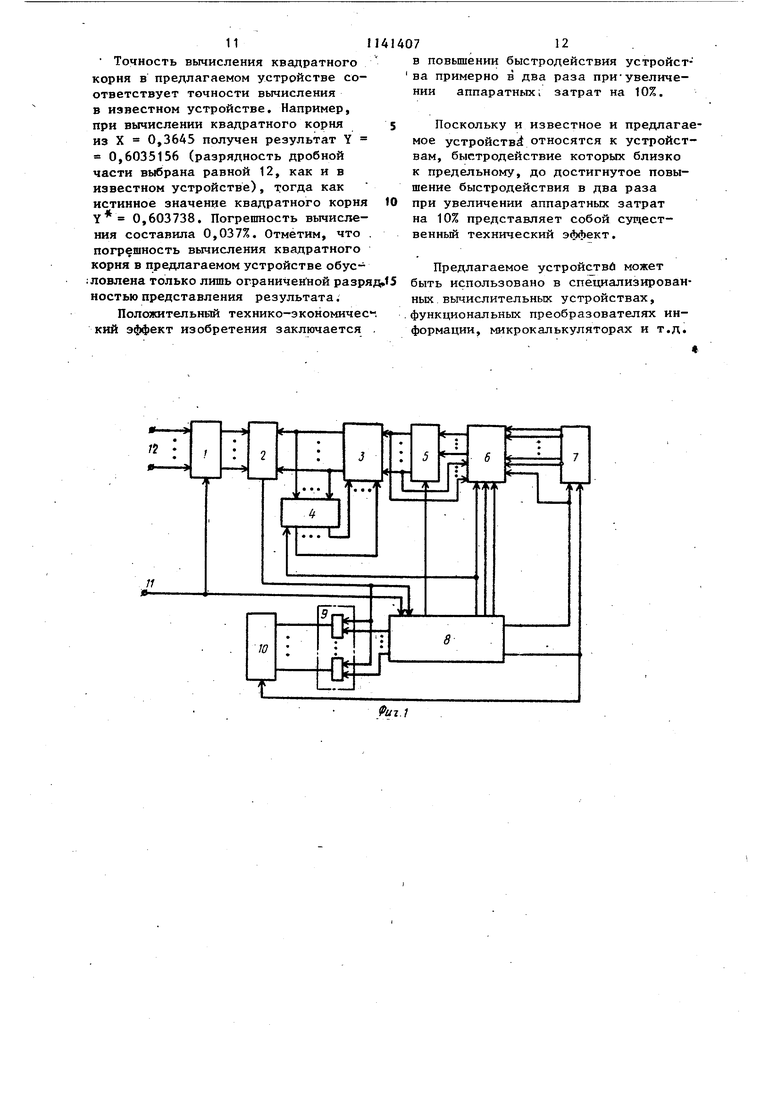

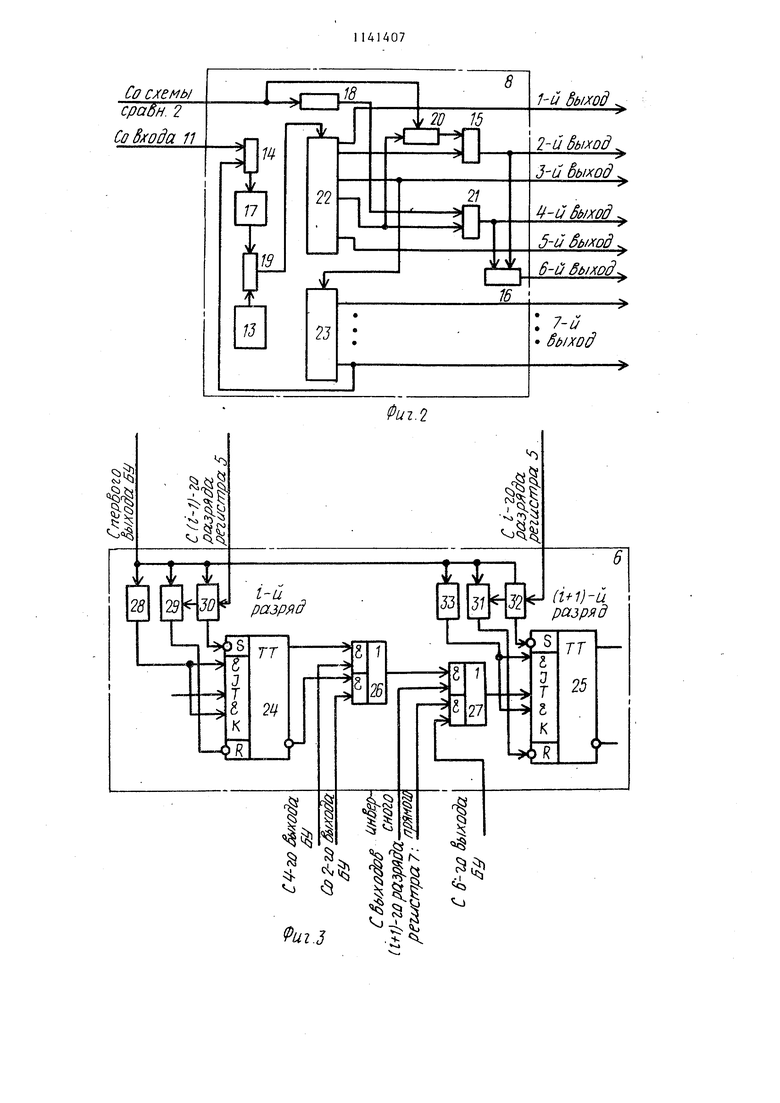

Недостатком известного устройства является сравнительно невысоко.е быстродействие. 3 . Цель изобретения - повьшение быстродействия устройства. Поставленная цель достигается тем, что в устройство для вычисления квадратного корня, содержащее первый, второй и третий регистры, (Схему сравнения,- сумматор, блок управления, содержащий генератор импульсов и первый элемент И, первый вход которого соединен с выходом генератора импульсов, информационны выходы первого регистра - с первой Iгруппой входов схемы сравнения, вто рая группа входов которой соединена с выходами сумматора и с информационными входами второго регистра, входы первого слагаемого сумматора с выходами третьего регистра, введе ны счетчик, группа элементов И, чет вертый и пятьш регистры, а в блок управления - первый и второй распре делители импульсов, второй и третий элементы И, три элемента ИЛИ, элемент НЕ, триггер, выход которого соединен с вторым входом первого элемента И, выход которого соединен с входом первого распределителя импульсов, выход схемы сравнения - с первыми входами элементов И группы, первым входом второго элемента И и входом элемента НЕ, выход которого соединен с первым входом третьего элемента И, выход которого соединен с первым входом первого элемента ИЛИ, с входом разрешения вычитания счетчика и входом синхронизации второго регистра, информационные вы ходы которого соединены с входами второго слагаемого сумматора, второй вход первого элемента ИЛИ - с выходом второго элемента ИЛИ и входом сложения счетчика, первый вход второго элемента ИЛИ - с выходом второго элемента И, вход синхрониза ции устройства - с входом синхронизации первого регистра и первым вхо дом третьего элемента ИЛИ, выход которого соединен с входом триггера, первый выход первого распредели теля импульсов - с тактовым входом счетчика и входом сдвига на три раз ряда в сторону младших разрядов четвертого регистра, второй выход первого распределителя импульсов с вторым входом второго элемента выход которого соединен с входом разрепшния сложения счетчика, вход управления которого, соединен с вых дом первого элемента ИЛИ, третий 074 выход первого распределителя импульсов - с входом сдвига на один разряд в сторону старших разрядов четвертого регистра, тактовым входом пятого регистра и входом второго распределителя импульсов, четвертый выход первого распределителя импульсов - с вторыми входами второго и третьего элементов И, пятьй выход первого распределителя импульсов с тактовым входом третьего регистра, разрядные выходы которого соедит нены со сдвигом на один разряд в сторону младших с первой группой разряд-. ных входов счетчика, вторая и третья группы разрядных входов счетчика соответственно с прямыми и инверсными разрядными выходами четвертого регистра, разрядные выходы счетчи- ка - соответственно с информационными входами третьего регистра, выходы второго распределителя импульсов с первого по V-й ( V. - разрядность результата) - соответственно с вто- рыми входами элементов И группы, выходы которых соединены соответственно с информационными входами пятого регистра, вход кода аргумента устройства - со сдвигом на 2т разрядов в сторону старших (т- число разрядов дробной части результата) с информационными входами первого регистра, -й выход второго распределителя импульсов - с вторым входом третьего элемента ИЛИ, На фиг. 1 представлена структурная схема предлагаемого устройства, на фиг. 2 - функциональная схема блока управления; на фиг, 3 - два разряда счетчика 6; на фиг. 4 - фрагмент двоичного представления функции Y Vx. Устройство (фиг. 1) содер хит регистр 1, схему 2 сравнения, сумматор 3, регистры 4 и 5, счетчик 6, регистр 7 сдвига, блок 8 управления, группу элементов И 9, регистр 10, вход 11 синхросигнала и вход 12 кода аргумента. Функциональная схема блока Я управления содержит генератор 13 тактовых импульсов, элементы ИЛИ 14-16, триггер 17, элемент НЕ 18, элементы И 19-21, распределители 22 и 23 импульсов, функциональная схема двух разрядов счетчика 6 содержит триггеры

1

24 и 25, элементы 2И-ИПИ 26 и 27, элементы И-НЕ 28-33.

Принцип работы устройства базируется на следунщих положениях.

Ic-m-l

Y,2

разность S L(j + 1) - L.j(j)

С; const,

где m 7- 1 - число дробных разрядовj L(j) - j-й интервал постоянства i-ro разряда, равный длине j-го участка изменения аргумента, на котором i-й разряд принимает только единичное или только нулевое значение о

М (0) / U.,(2j) L.(j)/2rSj8;

L,.,(..,(,/4;

t,(.Uj)-/.

(ei (ii где L;(j), L (j) - соответственно

нулевой и единичный интервалы постоянства i-ro разряда,

на которых j-й разряд принимает только нулевое (на L,-(j) или только единичное (на L,(j) значение.

Определение того, какому интервалу постоянства функции - единичному или нулевому в каждом разряде двоичного представления функции Y .Vx , полученном .при дискретности изменения аргумента ДХ, 2 , принадлежит значение аргумента Х-221, дает возможность сформировать значения всех разрядов функции Y. Данное определение реализуется при помощи сравнения с теку1414076

щим значением суммы инте1 валов постоянства функции Y Ух

-1тек 5UM

°л-17Т причем результат на выходе схемы 2 сравнения

если SUM

МО А МОА

В схеме устройства, представленной на фиг о 1, сравнение SUM.... с

МО

мол выполняется в схеме 2 сравнения, вычисление текущего значения

, осуществляется в сумматоре 3, вычисление интервалов постоянства в счетчике 6, формирование и хранение разности Б. интервалов постоянства реализуется в регистре 7 сдвига,

результат Y Vx формируется в регистре 10.

Устройство работает следующим образом.

В исходном состоянии в регистре 5 и счетчике 6 записан код первого интервала постоянства старшего разряда двоичного представления функции Y ТХ L 1, (1) 221 - 2 , в регистре 7 записан код разности S Lj(2) - L ,, (1) , остальные все регистры и триггер обнулены.

По синхросигналу с входа 11 код аргумента X с входа 12 записывается в регистр 1. Так.как запись проис- . ходит со сдвигом за счет жесткой связи на 2т разрядов в сторону старших, то в регистре оказывается код

Х-22. Синхросигнал с входа

X

WOA

11 поступает также на второй вход

блока 8 управления, в котором синхросигнал проходит элемент ИЛИ 14 и переключает в 1 триггер 17. Сигнал логической 1 с прямого выхода триггера 17 открывает элемент И 19, и тактовые импульсы с генератора 13 тактовых импульсов начинают поступать на вход распределителя 22 импульсов, который коммутирует их На

пять направлений. Первый тактовьй импульс с распределителя 22 импульсов поступает на первый выход блока 8 управления и далее на вход разрешения приема информации счетчика 6

и на вход управления сдвигом регистра 7, при этом в счетчике 6 осуществляется прием информации с рет гистра 5 со сдвигом за счет жесткой связи на один разряд в сторону младших, а в регистре 7 -.сдвиг его содержимого на. три разряда в сторону младших. Второй тактовый импульс с второго выхода распределителя 22 импульсов поступает на второй вход элемента ИЛИ 15, выход которого является вторым выходом блока 8 управ ления, кроме того, сигнал с выхода элемента ИЛИ 15 поступает на второй вход элемента ИЛИ 16 и с его выхода на шестой выход блока 8 управления. С второго выхода блока 8 управления тактовьй импульс поступает на вход разрешения сложения счетчика 6, Одновременно с шестого выхода блока . 8 управления сигнал логической 1 поступает на вход управления счетом счетчика 6, на первую группу разряд ных входов которого подан к.од с прямых выходов разрядов регистра 7, содержащий одну 1, а на третью группу разрядных входов счетчика 6 подан код с инверсных выходов разрядов регистра 7. В счетчике 6 реализуется сложение его содержимого с кодом регистра 7. Одновременно с вьтолнением операций, синхронизируемых первым.и вторым тактовыми импульсами, в сумматоре 3 вычисляет ся текущее значение суммы интервало постоянства, для этого код текущего интервала постоянства из регистра 5 складывается с предьщущим зна чением SUM, находящимся в регист ре 4. Полученное значение сравнивается в схеме 2 сравнения с |КОДОМ . , u(of, значи что в 1-м разряде двоичного представления функции Y -Vx данному значению агрумента X соответствует единичный интервал постоянства, в противном случае - нулевой. Результат сравнения со схемы 2 сравнения поступает на первую группу входов группы элементов И 9. Третий тактовый импульс поступает с третьего выхода распределителя 22 импульсов на вход распределителя 23 импульсов который коммутирует входные импульсы на k направлений, которые представляют собой 1 -разрядный седьмой выход блока 8 управления. Код с седьм го выхода блока 8 управления, соцержащий одну 1 в i-M разряде, роступает на вторую группу входов группы элементов И 9 и открьгоает в 1 78 ней i-й элемент И. Сигнал с выхода i-ro элемента И группы элементов И записывается в i-й разряд регистра 10 результата вычисления функции Y , на вход синхронизации которого поступает тактовый импульс с третьего выхода блока В управления. Сравнения в схеме 2 сравнения и запись значений разрядов функции Y Vx в регистр 10 осуществляются, начиная со старших разрядов. Тактовый импульс с третьего выхода блока 8 управления также поступает на вход управления сдвигом регистра 7 и осуществляет сдвиг его содержимого на один, разряд в сторону старпмх. Четвертый .тактовый чмпульс с четвертого выхода распределителя 22 импульсов поступает на второй вход элемента И- 21, на первый вход которого поступает инвертрфованное на элементе НЕ 18 эначение сигнала с выхода схемы 2 сравнения. Если на выходе схемы 2 сравнения логический О, то элемент И 21 оказывается открыт., и четвертьй тактовый и fflyльc проходит на четвертый выход блока 8 управления и далее на вход разрешения вычитания счетчика 6, кроме того, через элемент ИЛИ 16 четвертый тактовый импульс поступает на шестой выход блока 8 управления и далее на вход управле- ния счетом счетчика 6. В счетчике 6, реализуется операция вычитания, в результате которой в счетчике 6 оказывается код (2J - 1)-го интервала постоянства следующего (i - Т)-го разряда - Lj. (2j - 1). Если на выходе схемы 2 сравнения логическая 1, то элемент И 21 закрыт, а элемент И 20 открыт, и четВертый тактовый импульс через от- крытый элемент И 20 поступает на первый вход элемента ИЛИ 15, выход которого является вторым выходом блока 8 управления. С второго выхода блока 8 управления четвертый тактовый импульс поступает на вход разрешения сложения счетчика 6. Кроме того, четвертый тактовый импульс поступает с выхода элемента ИЛИ 15 на второй вход элемента ИЛИ 16 и с его выхода, который является шестым выходом блока 8 управления, на вход управления счетом счетчика 6. В счетчике 6 реализуется операция еложения, в результате которой в счетчике оказывается код (2j + 1)-го интервала постоянства следующего (i - 1)-го разряда - L- (2j + 1) Пятый тактовый импульс поступает с пятого выхода блока 8 управления на вход синхронизации регистра 5. В регистр 5 переписывается код вычисленного текущего интервала постоянства со счетчика 6. Таким образом, одна итерация вычислительного процесса вьшолняетс за пять тактов.Вычислительный процес состоит из fc итераций,на каждой из которьпс формируется значение одного разряда функции Y УХ . Вычисли. тельный процесс заканчивается, ког да на последнем выходе распределителя 23 импульсов появляется такто вый импульс, по переднему фронту .которого в регистре 10 формируется значение младшего разряда, а по заднему - триггер 17 переключается в О и закрывает Элемент И 19о Счетчик 6 работает следующим образом. Запись информации регистра 5 в счетчик 6 происходит как обычно по RS-входам, управляемыми нулями, и тактируется в счетчике 6 сигналом с первого выхода блока 8 управления при помощи элементов И-НЕ 29-32, при этом eaJ, Я-входы подается логический О с выходов элементов И-НЕ 28 и 33. Управление реверсом также осуществляется обычным образом, открывая сигналами с четверто го или второго выхода блока 8 управления соответствующий элемент И в элементе 2И-ИЛИ 26 и коммутируя на счетный вход триггера 25 прямой или инверсный выход триггера 24„ При выполнении операции сложения (вычитания) в счетчике 6 код с инверсных выходов разрядов регистра 7, содержащий единственный О в (i + 1)-м разряде, закрывает первый элемент И в элементе 2И-ИЛИ 27, на второй вход которого подключен выход элемента 2И-ИЛИ 26, а единственная 1, содержащаяся в (1+1)-м разряде кода, поступающего с прямых выходов разрядов регистра 7, через второй элемент И в элементе 2И-ИЛИ открытьш сигналом логической 1, ч с шестого выхода блока 8 управлени поступает на счетный вход триггера 25 (L + 1)-го разряда счетчика 6. 0710 Таким образом, в счетчике 6 реализуется операция сложения (вычитания), Регистр 10 вьшолнен на счетных триггерах, срабатывающих по переднему фронту сигнала, на счетные входы которых подключены выходы группы элементов И 9. В известном устройстве вычислительный процесс разбит на два этапа. На первом этапе выполняются подготовиуельные вычисления, которые используют операции записи в регистр (время выполнения операции tj ), чтения из блока памяти (t ц jp ), сложения в сумматоре (), преобразования кода в дополнительный (t ) Время выполнения первого этапа T, mc...2t.m«x{l(t,t), (%t.) - (1 На втором этапе в известном устройстве реализуется непосредственное вычисление квадратного корня. при этом еще используются операции сравнения кодов ( ) и сдвига (tg ). Бремя выполнения второго этапа V() где - разрядность результата. Общее время вычисления квадратного корня составляет 05 1 В предлагаемом устройстве за счет одновременного вьшолиеиия операций время вычисления квадратного корня составит (); 11-« л. Чч , (Я где tp - время вьтолнения операции сложения на счетчике. Сравнивая вьфажения (2) и (4), видим, что временные затраты по вычислению квадратного корня в йредлагаемом устройстве примерно равны . временным затратам второго этапа вычислительного процесса в известном устройстве. Учитывая, что Т я:-Т , делаем вьшод: быстродействие предлагаемого устройства примерно в два раза выше чем известного при увеличении аппаратных затрат на 10%, Точность вычисления квадратного корня в предлагаемом устройстве соответствует точности вычисления в известном устройстве. Например, при вычислении квадратного корня из X 0,3645 получен результат Y 0,6035156 (разрядность дробной части выбрана равной 12, как и в известном устройстве), тогда как истинное значение квадратного корня Y 0,603738. Погрешность вычисления составила 0,037%. Отметим, что погрешность вычисления квадратного корня в предлагаемом устройстве обус ловлена только лишь ограниченной разр ностью представления результата. Положительнйй технико-экономичес кий эффект изобретения заключается 7 в повьшении быстродействия устройства примерно в два раза при-увеличении аппаратных; затрат на 10%. Поскольку и известное и предлагаемое устройств относятся к устройствам, быстродействие которых близко к предельному, до достигнутое повышение быстродействия в два раза при увеличении аппаратных затрат на 10% представляет собой существенный технический эффект. Предлагаемое устройствй может быть использовано в специализированных вьпшслительных устройствах, функциональных преобразователях информации, микрокалькуляторах и т.д.

I

r

.

-V $

v I

«Ч M

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Байков В.Р., Селютин С.А | |||

| Вычисление элементарных функций в ЭКВМ | |||

| М., Радио, 1982, рис | |||

| Приспособление для плетения проволочного каркаса для железобетонных пустотелых камней | 1920 |

|

SU44A1 |

| Способ смешанной растительной и животной проклейки бумаги | 1922 |

|

SU49A1 |

| Оранский A.M | |||

| Аппаратные методы в цифровой вычислительной технике | |||

| Минск, БГУ, 1977, рис | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Ребристый каток | 1922 |

|

SU121A1 |

Авторы

Даты

1985-02-23—Публикация

1983-10-06—Подача