подсоединен к четвертому входу второго блока управления, а второй ВХОД и второй выход подключены соответственно к первому выходу и первому входу Спока поиска, второй вход которого подсоединен к седьмому выходу второго блока управления, третий вход подклк чен к Четвертому выходу блока определения максимума, четвертый вход подсоединен к четвертому выходу мультиплексора, а второй выход подключен к пятому входу блока преаставления результирующей информации.

2, Устройство по п. 1, отличающее с я тем, что блок управляемого сопоставления выполнен в виде синхронизатора,вход которого подключен к шее. тому выходу первого блока управления,первый выход подсоединен к первому входу двухуровневого квантователя, выход

которого подключен к первому входу блока записи. Второй вход которого подсоединен к второму выходу синхронизатора, а выход - к входу светодиодной матрицы, оптический выход которой связан с оптическим входом фотоприемной матрицы, выход которой подключен к второму входу анализатора годности, при этом вход двухуровневого квантователя подключен к выходу блока представления первичной информации, а светодиодная матрица механически связана с электромеханическим приводом, первый вход которого подсоединен к первому выходу блока установки в исходное состояние, второй вход подключен к третьему выходу второго блока управления, первый выход подсоединен к первому входу блока установки в исходное состояние, а вто{юй вьисод подключен к первому входу второго блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оптико-телевизионное устройство для контроля периодической планарной структуры | 1981 |

|

SU985974A1 |

| Устройство для контроля периодической структуры большой интегральной схемы | 1982 |

|

SU1037194A1 |

| Устройство для входного контроля изделий | 1989 |

|

SU1619313A1 |

| Устройство для допускового контроля разностенности | 1989 |

|

SU1777157A1 |

| Устройство для допускового контроля | 1986 |

|

SU1668982A1 |

| Устройство для контроля и селекции изделий по надежности | 1983 |

|

SU1112326A1 |

| Устройство для автоматического кон-троля больших интегральных схем намоп структурах | 1974 |

|

SU508788A1 |

| Устройство для контроля полупроводниковой памяти | 1982 |

|

SU1032481A1 |

| Устройство управления буферным накопителем для доменной памяти | 1981 |

|

SU1275536A1 |

| СПОСОБ УПРАВЛЕНИЯ ПРОЦЕССОМ МНОГОПАРАМЕТРИЧЕСКОГО КОНТРОЛЯ | 2004 |

|

RU2265875C1 |

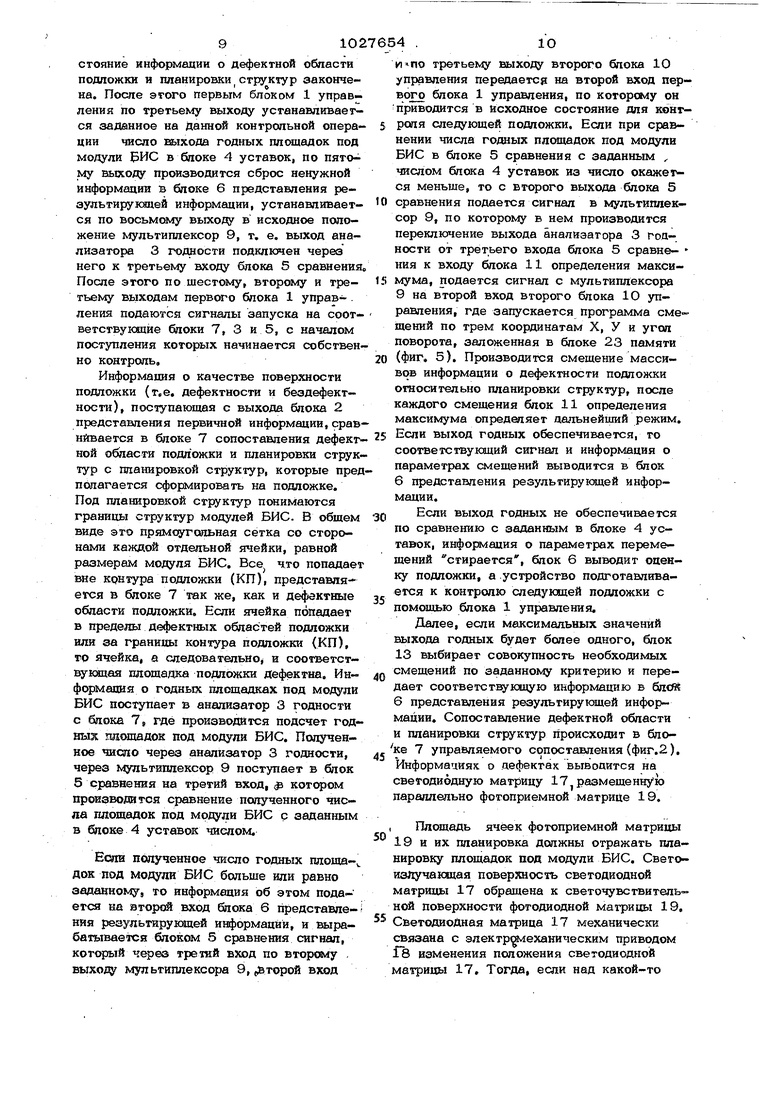

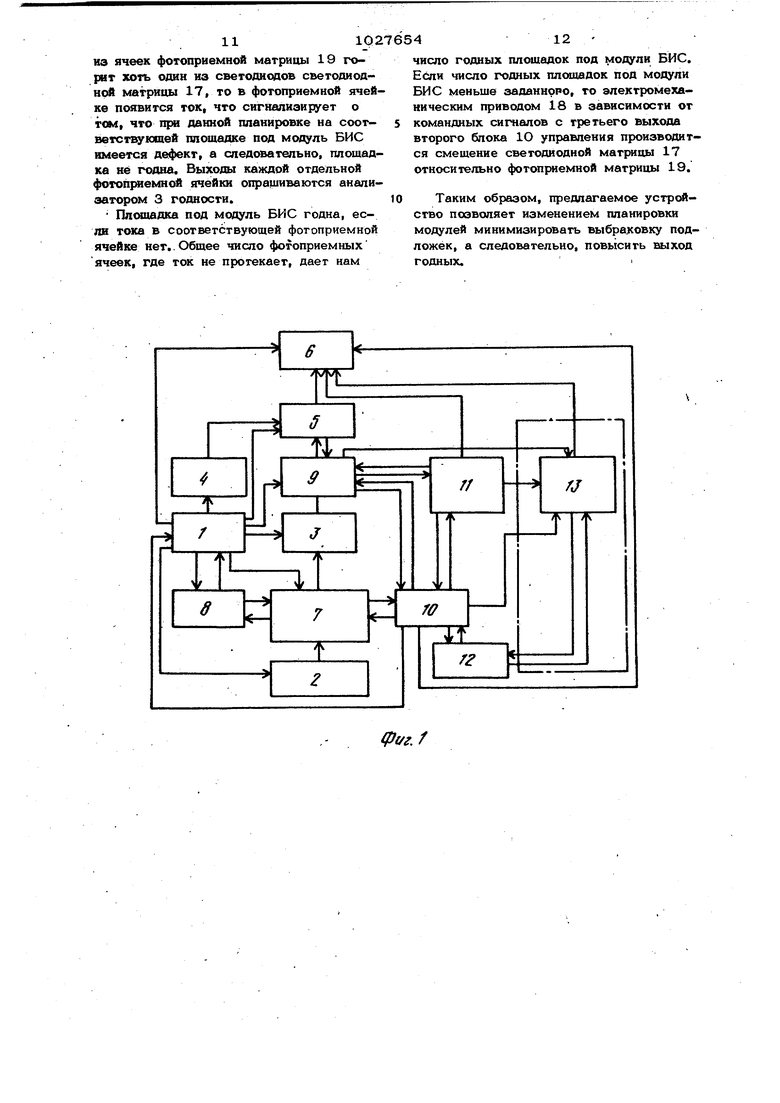

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОДЛОЖКИ БОЛЬШИХ ИНТЕГРАЛЬНЫХ СХЕМ, содержащее первый блок управления, блок представления первичной информации, вход которого подключен к первому выходу первого блока управления, анализатор годности, первый вход которого подключен к второму выходу первого блока управления, блок уставок вход которого подключен к третьему иыходу первого блока управления, блок срав нения, первые два входа которого подклю чены соответственно к четвертому выход первого блока управления и выходу блока уставок, блок представпения результирук щей информации, первые два входа коте рого подключены соответственно к пятому выходу первого блока управления и первому выходу блока сравнения, отличающееся тем, что, с целью повышения выхода годаых, в него введены блок установки в исходное состояние, мультиплексор, второй блок управления, блок определения максимума,, блок памяти, блок поиска и блок управляемого с6поставления, первый и второй входы которого подключены соответственно к шестому выходу первого блока управления и к выходу блока представления первичной информации, первый выход - к второму входу анализатора годности, а вторсй выходк первому входу блока установки в исходное состояние,.второй вход которого поасоёдинен к седьмому выходу первого блока управления, первый выход подключен к третьему входу блока управляемого сопоставления, а второй выход - к первому входу первого блока управления, восьмой выход которого подсоединен к первому входу мультиплексора, второй вход которого подключен к выходу анализатора годности, третий вход подсоединен к второму выходу блока сравнения, а первый и второй выходы подключены соответственно к третьему входу блока сравнения и к второму входу второго блока управления, первый вход которого .подсоединен к третьему выходу блока управляемого сопоставления, а первые четыре выхода подключены соответственно к второму входу первого блока управления, к третьему входу блока представления результирукадей информации, четвертому входу блока управляемого сопоставления и к четвертому входу мультиплексора,третий выход которого подсоединен к первому входу блока определения максимума, второй вход которого подключен к пятому выходу второго блока управления, первый выход - к четвертому входу блока представления результирующей информации, второй выход подсоединен к пятому входу мультиплексора, а третий выход - к третьему входу второго блока управления, шестой выход которого подключен к первому входу блока памяти, первый выход

Изобретение относится к приборостроению, а конкретнее к контрольно-измерительным устройствам, предназначенным для контроля подложек до формирования на них структур, для изготовления больЦ1ИХ интегральных схем (БИС), а также может применяться там, где требуется осуществить контроль плоских материалов и уменьшить потери на брак на последующих операциях по обработке, Известно устройство для неразрушающего контроля полуфабрикатов для изго.товпения БИС, KOTqpoe содержит блок представления первичной информации (on- тической или акустической, рентгеновской или электронной и т. п,), блок управления блок представления результирующей информации в виде изображения на видеоконтрольном устройстве, табло С1 3.

Указанное устройство позволяет исследовать контролируемые полуфабрикаты ИС в том числе и подложки, но не певволяет судить о том, какие влияния сжвжут эти дефектные области на выхоа гооивмх модулей БИС, структуры которых ф 0| гаруются на последующих операциях, вследствие того, что не произвошстся сопоставление дефектных о бластей с планировкой структур, формировавне которых предполагавгси и« подложках. Следовательно,

указанное устройство не позволяет снизить влияние дефектности подложек на выход годных.

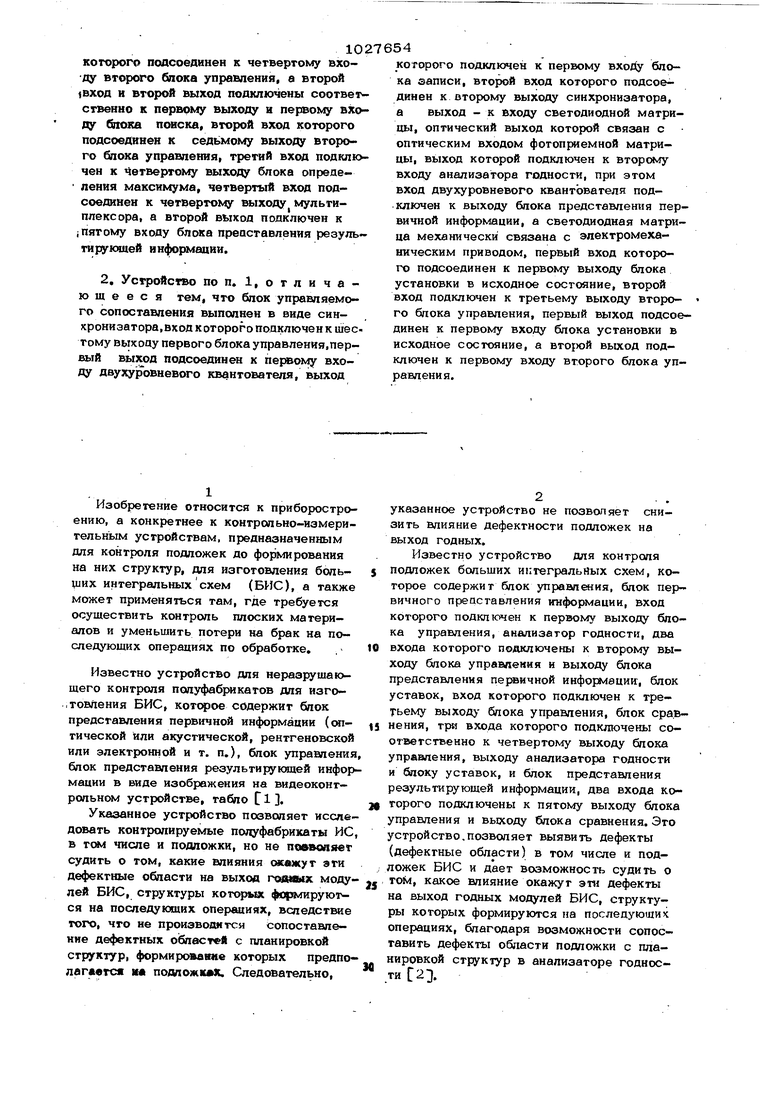

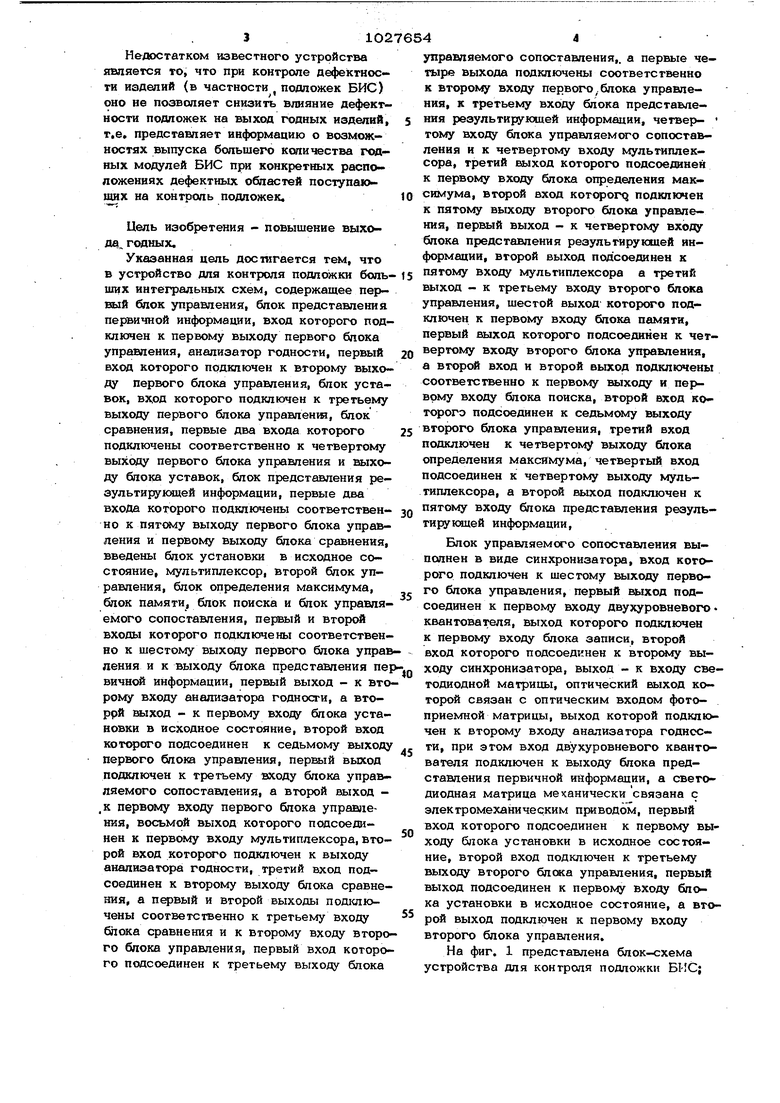

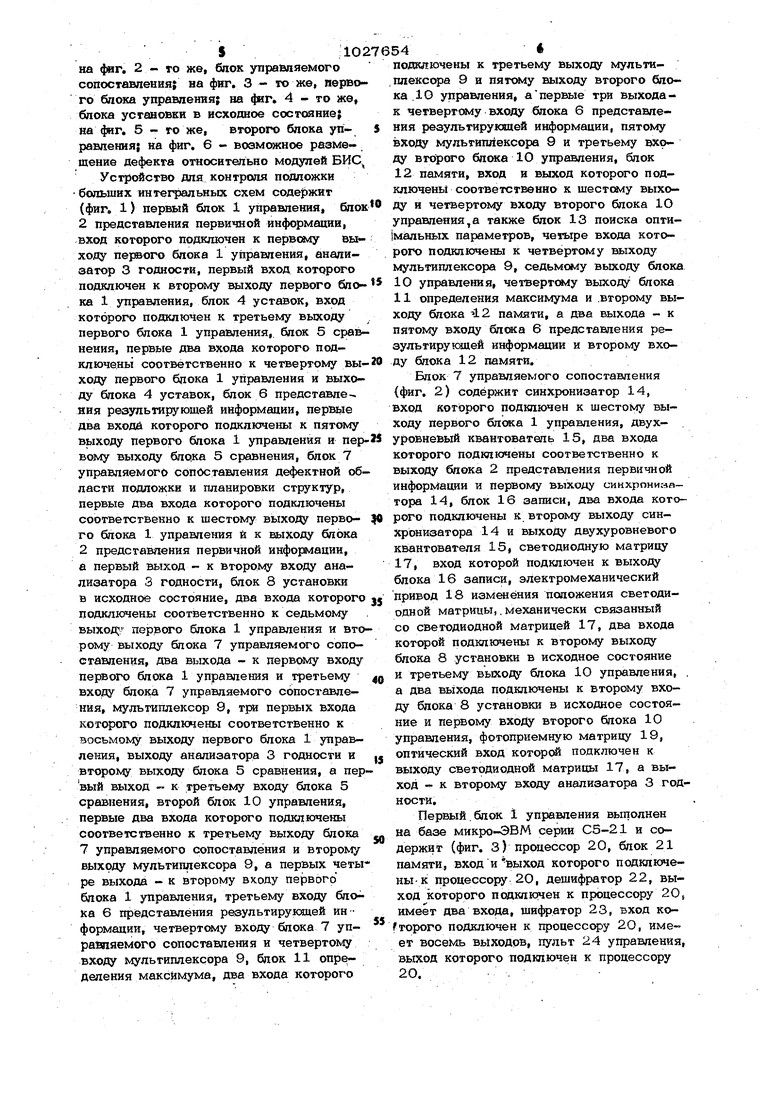

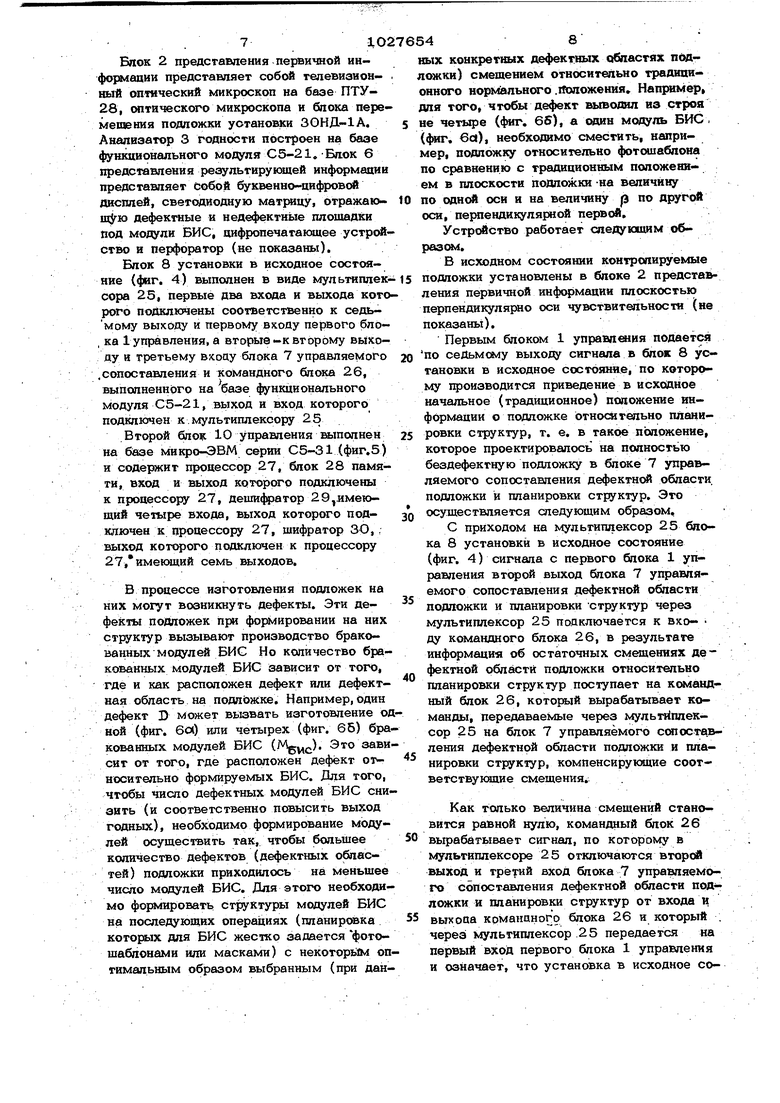

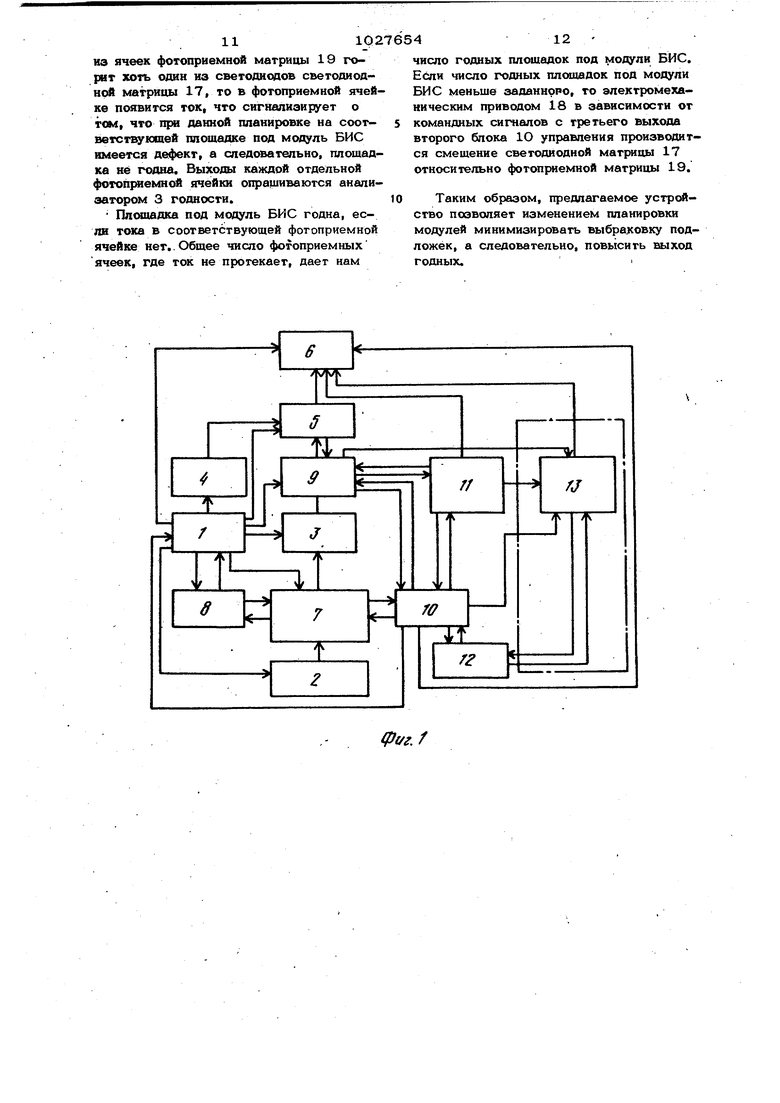

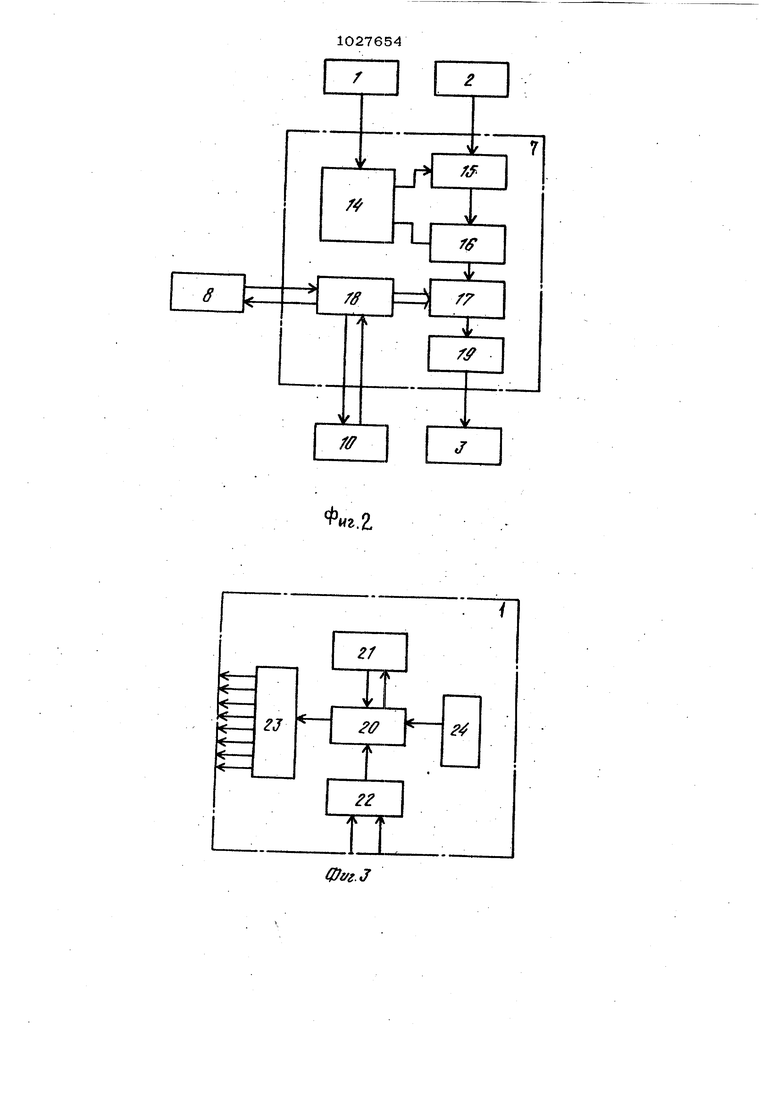

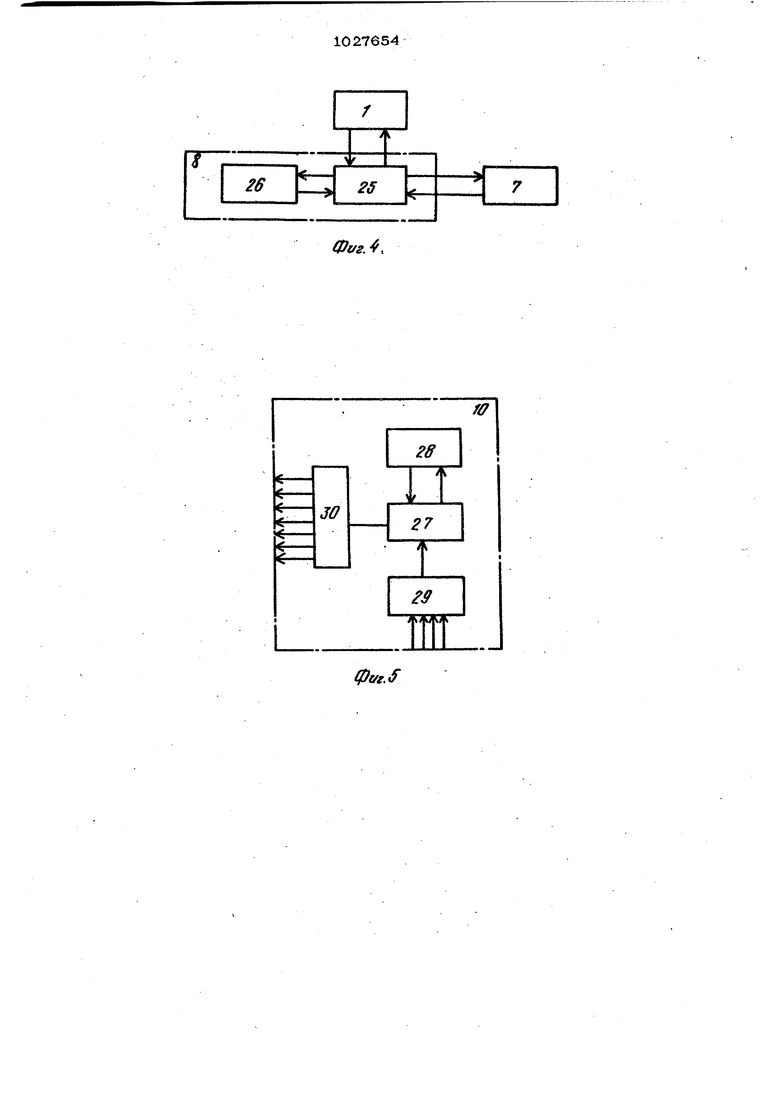

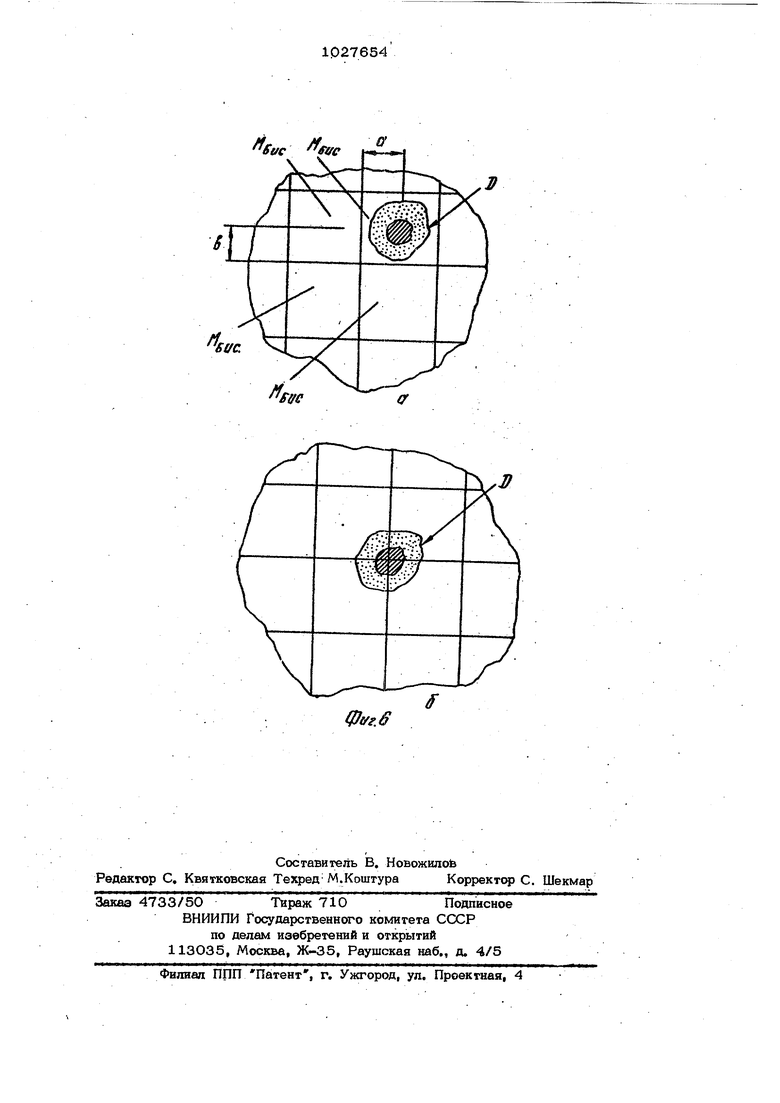

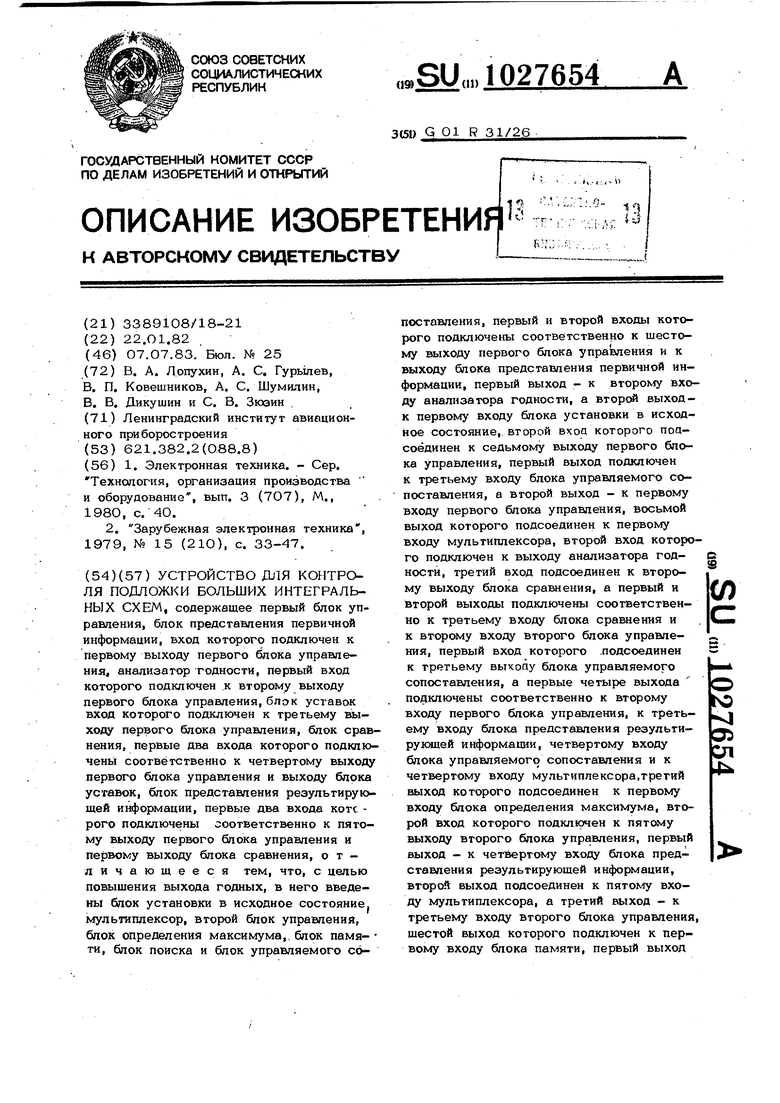

Известно устройство для контроля подложек больших интегральных схем, которое содержит блок управления, блок первичного препсгавления инфopv4aции, вход которого подключен к первому выходу блока управления, анализатор годности, два входа которого подключены к второму выходу блока управления и выходу блока представления пержичной информации, блок уставок, вход которого подключен к третьему выход блока управления, блок сра.внения, три входа которого подключены соответственно к четвертому выходу блока управления, выходу анализатора годности и блоку уставок, и блок представления результирующей информации, два входа которого подключены к пятому выходу блока управления и выходу блока сравнения. Это устройство,позволяет выявить дефекты (дефектные области) в том числе и подложек БИС и дает возможность судить о том, какое влияние окажут эти дефекты на выход годных модулей БИС, структуры которых формируются на последующих операциях, благодаря возможности сопоставить дефекты области подложки с планировкой структур в анализаторе годности 23. Недостатком известного устройства является то, что при контроле дефектности изделий (в частности , подложек БИС) оно не позволяет снизить влияние дефектности подложек на выход годных изделий, т.е. представляет информацию о возможностях выпуска большего коли юства годных модулей БИС при конкретных расположениях дефектных областей поступающих на контроль подложек. Цель изобретения - повышение выхода, годных. Указанная цель досшгается тем, что в устройство для контроля подложки больигах интегральных схем, содержащее первый блок управления, блок представления первичной информации, вход которого подключен к первому выходу первого блока управления, анализатор годности, первый вход которого подключен к второму выходу первого &1ока управления, блок уставок, вход которого подключен к третьему выходу первого блока управленга, блок сравнения, первые два входа которого подключены соответственно к четвертому выходу первого блока управления и выходу блока уставок, блок представления результируквдей информации, первые два входа которого подключены соответственно к пятому выходу первого блока управления и первому выходу блока сравнения, введены блок установки в исходное состояние, мультиплексор, второй блок управления, блок определения максимума, блок памяти, блок поиска и блок управляемого сопоставления, первый и второй входы которого подключены соответственно к шестому выходу первого блока управ ления и к выходу блока представления пе вичной информации, первый выход - к вто рому входу анализатора годности, а вторрй аыход - к первому ъх.опу блока установки в исходное состояние, второй вход которого подсоединен к седьмому выходу первого блока управления, выход подключен к третьему входу блока управляемого сопоставления, а второй выход ,к первому входу первого блока управления, восьмой выход которого подсоединен к первому входу мультиплексора, второй вход которого подключен к выходу анализатора годности, третий вход подсоединен к второму выходу блока сравнения, а и второй выходы подютючены соответственно к третьему входу блока сравнения и к второму входу второ го блока управления, первый вход которо го подсоединен к третьему выходу блока управляемого сопоставления,, а первые четыре выхода подключены соответственно к второк входу первого,.блока управления, к третьему входу блока представления результирующей информации, четвер- тому входу блока управляемого сопоставления и к четвертому входу мультиплексора, третий выход которого подсоединен к первому входу блока определения максимума, втсфой вход которого подключен к пятому выходу второго блока управления, первый выход - к четвертому входу блока представления результирующей информации, второй выход подсоединен к входу мультиплексора а третий выход - к третьему входу второго блока управления, шестой выход которотО подключен к первому входу блока памяти, первый выход которого подсоединен к четвертому входу второго блока управления, а второй вход и второй выход подключены соответственно к первому выходу и первому входу блока поиска, второй вход которого подсоединен к седьмому выходу второго блока управления, третий вход подключен к четвертому выходу блока определения максимума, четвертый вход подсоединен к четвертому выходу мультиплексора, а второй выход подключен к пятому входу блока представления результируклцей информации, Блок управляемого сопоставления выполнен в виде синхронизатора, вход которого подключен к шестому выходу первого блока управления, первый шлход подсоединен к первому входу двухуровневого квантователя, выход которого подключен к первому входу блока записи, второй вход которого подсоединен к второму выходу синхронизатора, выход - к входу светодиодной матрицы, оптический выход которой связан с оптическим входом фотоприемной матрицы, выход которой подклк чен к второму входу анализатора годности, при этом вход дв ухуровневого квантователя подключен к выходу блока представления первичной информации, а светодиодная матрица меканически связана с электромеханическим приводом, первый вход которого подсоединен к первому выходу блока установки в исходное состояние, второй вход подключен к третьему выходу второго блока управления, первый выход подсоединен к первому входу блока установки в исходное состояние, а второй выход подключен к первому входу второго блока управления. На фиг. 1 представлена блок-схема устройства для контроля подложки БИС; S; 102 на 4яг. 2-го же, блок управляемого сопоставпения на фиг. 3 - то же, иервого блока управления; на фиг, 4 - то же, блока установки в исходное состояние; на фиг. 5 - то же, второго блока управления; на фиг. 6 - возможное размещение дефекта относительно модулей БИС Устройство для контроля подложки больших интегральных схем содержит (фиг. 1) первый блок 1 управления, блок 2 представления первичной информации, вход которого подключен к первому выходу первого блока 1 управления, анализатор 3 годности, первый вход которого подключен к второму клходу первого блока 1 управления, блок 4 уставок, вход которого подключен к третьему выходу первого блока 1 управления, блок 5 сравнения, первые два входа которого подключены соответственно к четвертому выходу первого блока 1 управления и выходу блока 4 уставок, блок 6 представлення результирующей информации, первые два входи которого подключены к пятому выходу первого блока 1 управления и первому выходу блока 5 сравнения, блок 7 управляемого сопоставления дефектной области подложки и планировки структур. первые два входа которого подключены соответственно к шестому выходу первого блока 1 управления и к выходу блока 2 представяения первичной информации, а первый выход - к второму входу анализатора 3 годности, блок 8 установки в исходное состояние, два входа которого подключены соответственно к седьмому выход : первого блока 1 управления и второму выходу блока 7 управляемого сопоставления, два выхода - к первому входу первого блока 1 управления и третьему входу блока 7 управляемого сопоставления, мультиплексор 9, три первых входа которого подключены соответственно к восьмому выходу первого блока 1 управления, выходу анализатора 3 годности и второму выходу блока 5 сравнения, а первый выход - к третьему входу блока 5 сравнения, второй блок 10 управления, первые два входа которого подключены соответственно к третьему выходу блока 7 управляемого сопоставления и второму выходу мультиплексора 9, а первых четы ре выхода - к второму входу пеузвого блока 1 управления, третьему входу блока 6 пр едставлёния результирующей информации, четвертгалу входу блока 7 управляемого сопоставления и четвертому входу мультиплексора 9, блок 11 определения максимума, два входа которого 54 подключены к третьему выходу мульти.плексора 9 и выходу второго бпока ДО управления, апервые три выходак четвертс«му входу блока 6 представления результирующей информации, пятому входу мультиплексора 9 и третьему входу второго блока 10 управления, блок 12 памяти, вход и вьисод которого подключены соответственно к шестсаиу выхоДУ и четвертому входу второго блока 10 у правления, а также блок 13 поиска опти|мальных параметров, четыре входа которого подключены к четвертому выходу мультиплексора 9, седьмсму выходу блока Ю управления, четвертому выходу блока И определения максимума и .второму выходу блока и 2 памяти, а два выхода - к пятому входу блока 6 представления реэультирукшей информации и второму вхоДУ блока 12 памяти. Блок 7 управляемого сопоставления (фиг. 2) содержит синхронизатор 14, вход которого подключен к шестому выходу первого блсйса 1 управления, двухуровневый квантователь 15, два входа которого подключены соответственно к выходу блока 2 представления первичной информации и первому выходу синхрпниап- тора 14, блок 16 записи, два входа которого подключены к второму выходу синХрЬнизатора 14 и выходу двухуровневого квантователя 15, светодиодную матрицу 17, вход которой подключен к выходу блока 16 записи, электромеханический привод 18 изменения положения светодиодной матрицы,, механически связанный со светодиодной матрицей 17, два входа которой подключены к второму выходу блока 8 установки в исходное состояние и третьему выходу блока 1О управления, . а два выхода подключены к второму входу блока 8 установки в исходное состояние и первому входу второго блока 10 управления, фотоприемную матрицу 19, оптический вход которсй подключен к выходу светодиодной матрицы 17, а выход - к второму входу анализатора 3 годности. Первый. блок 1 управления выполнен на базе микро-ЭВМ серии С5-21 и содержит (фиг. З) процессор 20, блок 21 памяти, вход и выход которого подключены-к процессору 20, дешифратор 22, выход которрго подклю1чен к процессору 20, имеет два входа, 23, вход коToporo подключен к процессс у 20, имеет восемь выходов, пульт 24 управления, выход которого подключен к процессору 20. . Бпок 2 представления первичной информации представляет собой телевизионный оптический микроскоп на базе ПТУ28, оптического микроскопа и блока пере мещения подложки установки ЗОНД-1А. Анализатор 3 годности построен на базе функционального модуля С5-21,-Блок 6 представления результирующей инф фмааии представляет Собой буквенно-цифровой дисплей, светодиодную матртцу, отражающ гю дефектные и недефектные площадки под модули БИС, дифропечатакяцее устрЫ1 ство и перфоратор (не показаны). Блок 8 установки в исходное состояние (фиг. 4) выполнен в виде мул ьтиплек сора 25, первые два входа и выхода кото рото подключены соответственно к седьмому выходу и первому входу первого бло, ка 1 управления, а вторые-к втор ому выходу н третьему вхоау блока 7 управляемого .сопоставления и командного блока 26, выполненного на базе функционального модуля С5-21, выход и вход которого подключен к мультиплексору 25 Второй 10 управления выполнен на базе микро-ЭВМ серии С5-31(фиг,5) и содержит процессор 27, блок 28 памяти, вход и выход которого подключены к процессору 27, деши4чратор 29 лмеющий четыре входа, выход которого подключен к прюцессору 27, шифратор ЗО, ; выход которого подключен к процессору 27,имеквдий семь ш ходов. В процессе изготовления подложек на них могут возникнуть дефекты. Эти дефекты подложек при формировании на них структур вызывают производство бракованных модулей БИС Но количество бракованных модулей БИС зависит от того, где и как расположен дефект или дефектная область на подложке. Например, один дефект D может вызвать изготовление од ной (фиг. бси) или четырех (фиг. 66) бра кованных модулей БИС (Mgyjj). Это зави сит от того, где расположен дефект oi носительно формируемых БИС. Для того, чтобы число дефектных модулей БИС снизить (и соответственно повысить выход годных), необходимо формирование модулей осуществить так, чтобы большее количество дефектов (дефектных областей) подложки приходилось на меньшее число модулей БИС. jDLля этого необходимо формировать структуры модулей БИС на последующих операциях (планировка которых для БИС жестко задается фотошаблонами или масками) с некоторь1М оп тимальным образом выбранным (при даных конкретных дефектных областях подожки) смещением относительно традиоионного нормального .положения Например, ля того, чтобы дефект выводил из строя е четыре (фиг, 65), а один модуль БИС. (. 6с), необходимо сместить, например, подложку относительно фотошаблона по сравнению с традиционным положением в плоскости подложки -на величину по одной оси и на величину |3 по другой оси, перпендикулярной первЫ(. Устройство работает следующим образ. В исходном состоянии контролируемые подложки установлены в блоке 2 представления первичной информации плоскостью перпендикулярно оси чувствительности (не показань). Первым блоком 1 управлв1ия подается по седьмому выходу сигнала в блок 8 установки в Исходное состояние, по которому производится приведение в исходное начальное (традиционное) положение информации о подложке относительно планировки структур, т. е. в такое положение, которое проектировалось на полностью бездефектную подложку в блоке 7 управляемого сопоставления дефектнсЛ области, подложки и планировки структур. Это осуществляется следующим образом, С приходом на мультиплексор 25 блока 8 установки в исходное состояние (фиг. 4) сигнала с первого блока 1 управления втсфой выход блока 7 управляемого сопоставления дефектной области подложки и планировки -структур через мультиплексор 25 подключается к вхо ду командного блока 26, в результате информация об остаточных см цениях де фектной области поДложки относительно планировки структур поступает на комаищный блок 26, который вырабатывает команды, передаваемые через мульт1 плексор 25 на блок 7 управляемого сопоставления дефектной области подложки и планировки струк1ур, компенсирующие соответствукадие смещения. . Как только величина смещений становится равной нулю, командный блок 26 вырабатывает сигнал, по которому в мультиплексоре 25 отключаются второй выход и вход блока 7 управляемого сопоставления дефектной области подложки и планировки структур от входа и выхоаа крмаианого блока 26 и который . через мультиплексор 25 передается на первый вход первого блока 1 управления и означает, что установка в исходное со9102стояние информации о дефектной области подложки и планировки структур закончена. После этого первым блоком 1 управления по третьему выходу устанавливается заданное на данной контрольной операции число выхода годных плсшадок под модули рис в блоке 4 уставок, по пятому выходу производится сброс ненужной информации в блоке 6 представления результирующей информации, устанавливается по восьмому выходу в исходное положение мультиплексор 9, т. е. выход анализатора 3 годности подключен через него к третьему входу блока 5 сравнения После этого по шестому, второму и третьему выходам первсго блока 1 управ- . ления подаются сигналы запуска на соответствукядйе блоки 7, 3 и 5, с началом поступления которых начинается собствен но контроль. Информация о качестве поверхности подложки (т.е. дефектности и бездефектности), поступающая с выхода блока 2 представления первичной информации, срав нйваатся в блоке 7 сопоставления дефект ной области подложки и планировки струк тур с планировкой структур, которые пред полагается сформировать на подложке. Под планировкой структур пожимаются границы структур модулей БИС. В общем виде это прямоугольная сетка со сторонами каждой отд хьной ячейки, равной размерам модуля БИС. Все что попадае вне крнтура подложки (КП), предетавпяегся в блоке 7 так же, как и дефектные области подложки. Если ячейка попадает в пределы дефектных областей подложки или за границы контура подложки (КП), то ячейка, а следовательно и соогветствуквдая площадка подложки дефектна. Информация о годных площадках под модули БИС поступает в анализатор 3 годности с блока 7, где производится подсчет годных лйошадок под модули БИС. Полученное число через анализатор 3 годности, через мультиплексор 9 поступает в блок 5 сравнения на третий вход, котором производится сравнение полученного числа площадок под модули БИС с заданным в блоке 4 уставок числом. Если полученное число годных шIoщaдок под модули БИС больше или равно заданному, то информация об этом подается на второй вход блока 6 представления |юэультирукацей информации, и вырабатывается блоком 5 сравнения сигнал, который череа третей вход по второму , выходу мультиплексора 9, ьторой вход 4 третьему выходу второго блока 10 управления передается на второй вход первого блока 1 управления, по которому он приводится в исходное состояние для контроля следующей подложки. Если при сравнении числа годных площадок под модули БИС в блоке 5 сравнения с заданным , числом блсяса 4 уставок из число окажегся меньше, то с второго выхода блока 5 сравнения подается сигнал в мультиплексор 9, по которому в нем производится переключение выхода анализатора 3 годности от третьего входа блока 5 сравне- кия к входу блока 11 определения максимума, подается сигнал с мультиплексора 9 на второй вход второго блока 1О управления, где запускается программа смещений по трем координатам X, У и угол поворота, заложенная в блоке 23 памяти (фиг. 5). Производится смещение массивов информации о дефектности подложки относительно планировки структур, после каждого смещения блок 11 определения максимума определяет дальнейший режим. Если выход годных обеспечивается, то соответствующий сигнал и информация о параметрах смещений выводится в блок 6 представления результирукацей информации. Если выход годных не обеспечивается по сравнению с заданным в блоке 4 уставок, информация о параметрах перемещений стирается, блок 6 выводит оценку подложки, а устройство подготавливается к контролю следующей подложки с помощью блока 1 управления. Далее, если максимальных значений выхода годных будет более одного, блок 13 выбирает совокупность необходимых смещений по заданному критерию и передает соответствукяцую информацию в блей 6 представления результирующей информации. Сопоставление дефектной области и планировки структур происходит в бяоке 7 управляемого сопоставления (фиг.2). Информациях о дефектах выводится на светодиодную матрицу 17 размещенную параллельно фотоприемной матрице 19. Площадь ячеек фотоприемной матрицы 19 и их планировка должны отражать планировку площадок под модули БИС. Светоизлучаюшая поверхность светодиодной матрицы 17 обращена к светочувствитель ной поверхности фотодиодной матрицы 19, Светодиодная матрица 17 механически связана с электр еханическим приводом f8 изменения положения светодиодной матрицы 17, Тогда, если над какой-то

из ячеек фотоприемной матрицы 19 горит хоть оряя из светошопов светодиодноЛ матрицы 17, то в фотоприемной 51чейке появится ток, что сигнализирует о том, что при данной планировке на соответствующей площадке под модуль БИС имеется дефект, а следовательно, плошадка не годна. Выходы каждой отдельной фотоприемной ячейки сшрашиваются анализатором 3 ГОШ1ОСТИ.

Пжшшдка под модуль БИС годка, если тока в соответствующей фотоприемной ячейке нет..Общее число фотоприемных ячеек, где ток не протекает, дает нам

число ГОШ1ЫХ площадок под модули БИС. Если число ГОШ1ЫХ площадок под модули БИС меньше заданноро, то электромеханическим приводом IS в зависимости от командных сигналов с третьего выхода второго блока 1О управления производится смещение светодиодной матрицы 17 относительно фотоприемной матрицы 19.

Таким образом, предлагаемое устрсЛство позволяет изменением планировки модулей минимизировать выбраковку подложек, а следовательно, повысить выход годных.

f./

ф«г.г

26

Фаг. .

Фиг,

St/c fffc

hw

фуе.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Электронная техника, - Сер, Технология, организация производства и оборудование, вып, 3 | |||

Авторы

Даты

1983-07-07—Публикация

1982-01-22—Подача