1

Изобретение относится к области контрольно-измерительной техники и может быть использовано при изготовлении больших интегральных схем (БИС) на МОП-структурах, например, для электронных клавишных вычислительных машин (ЭКВМ).

Известно устройство для контроля цифровых вычислительных машин, включаюшее в себя испытываемую схему, блок задания входных и выходных комбинаций, блок сравнения, блок компараторов логических уровней, измерительные входы которого подключены к испытываемой схеме, а опорные входы - к блоку эталонов, блок формирователей, блок управления, блок индикации годности.

Однако известное устройство характеризуется большим количеством программируемых комбинаций и сложным программированием, требует Применения быстродействуюш,их дорогостояш,их запоминаюгцих устройств при контроле БИС на МОП-структурах с динамической логикой и не обеспе чивает предварительного контроля наличия электрических контактов выводов многовыводных цифровых схем с контактирующим устройством, необходимого для избежания ложной отбраковки испытываемых схем при функциональном контроле. Кроме того, в таком устройстве невозможно выполнение ручного режима контроля по произвольной программе, необходимого для отладки программ испытаний и выявления некоторых неполадок устройства.

Цель изобретения - увеличение достоверности контроля.

Это достигается тем, что в устройство введены клавиатура, соединенная с блоком задания программы, вычислитель, связанный через формирователь, коммутатор и контактируюш,ий блок с испытываемой схемой, блоком

сравнения и блоком задания выходных результатов, а входами - с клавиатурой, цифровой индикатор, соединенный с выходами вычислителя, блок определения контакта, подключенный к первой группе выходов коммутатора и

к блоку управления, и блок индикации отсутствия контакта, подсоединенный к блоку определения контакта.

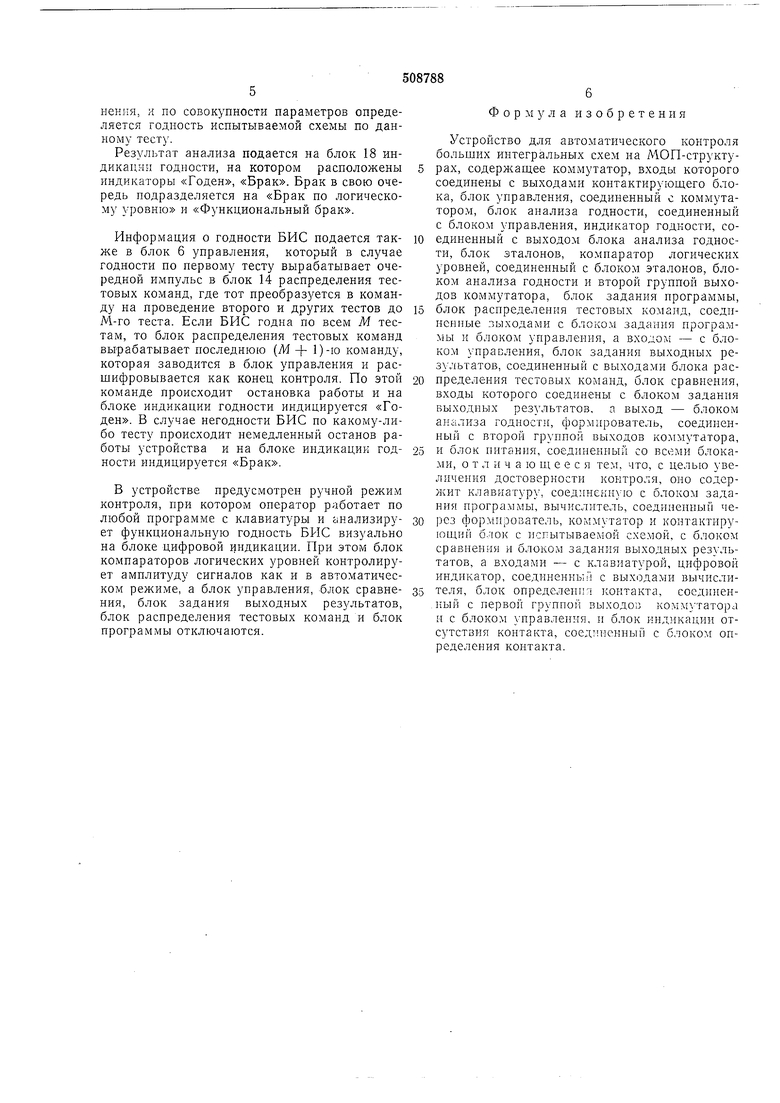

При ручном режиме контроля по любой произвольной программе оператор задаег клавиатурой код операции для ЭКВМ и контролирует на блоке цифровой индикации виз}ально результаты операций, выполненные ЭКВМ. На чертеже представлена блок-схема предлягаемого устройства.

Испытываемая схема 1 подсоединена СР,ОИми выводами к контактирующему блоку 2, выходы последнего - к входам ко.ммутаторр 3. Группа а выводов коммутатора 3 подключека к блоку 4 определения контакта, группа

выходов блока 4 - к блоку 5 индикации отсутствия контакта, управляющий выход - к первому входу блока 6 управления, а первый выход блока 6 - к управляющему входу коммутатора 3. Одна часть группы б выводов коммутатора подсоединена к измерительным входам блока компараторов 7 логических уровней и входам блока 8 формирователей, выход блока компараторов 7 - к первому входу блока 9 анализа годности, другая часть группы б выводов коммутатора - к выходам блока 8 формирователей. Блок формирователей соединен с вычислителем 10 с учетом направления прохождения сигналов, индикационные сегментные выходы вычислителя - с сегментными входами блока 11 цифровой индикации, выполненного по принципу последовательной поразрядной индикации, и с первой группой входов блока 12 сравнения, а индикационные разрядные выходы - с разрядными входами блока 11 цифровой индикации и с первой группой адресных входов блока 13 задания выходных результатов. Выходы блока 13 подключены к второй группе входов блока 12 сравнения, выход блока 12 - к второму входу блока 9 анализа годности. Вторая группа адресных входов блока 13 задания выходных результатов подсоединена к выходам 1-.М блока 14 распределения тестовых команд, выходы 1-М блока 14 - к входам блока 15 задания программы, а (М-|- 1)-й выход - к второму входу блока 6 управления. Выходы блока 15 задания программы подключены к входам блока 16 клавиатуры, выходы блока 16 - к клавищным входам вычислителя 10. Потенциальные уровни разбраковки логических «0 и «1 вырабатываются блоком 17 эталонов, выходы которого связаны с опорными входами блока 7 компараторов. Второй выход блока 6 управления соединен с входом блока 14 распределения тестовых команд, третий его выход - с третьим входом блока 9 анализа годности, первый выход которого подключен к блоку управления, а второй выход - к блоку 18 индикации годности.

Все блоки устройства для контроля БИС подключены к блоку 19 питания.

Испытываемую схему (БИС) подсоединяют выводами к контактирующему блоку 2. При автоматическом контроле по команде «Пуск все блоки устройства устанавливаются в начальное состояние, затем блок 6 управления вырабатывает команду на подключение БИС через коммутатор 3 к блоку 4 определения контакта.

Для определения наличия электрического контакта выводов ВИС с контактирующим блоком 2 на все выводы БИС через коммутатор 3 подается относительно подложки напряжение Е в прямом нерабочем направлении и пороговыми элементами одновременно на всех выводах группы а коммутатора 3 измеряются напряжения р-и-переходов стабилитронов, имеющихся в БИС для защиты от статического электричества и соединяющих вывод БИС с подложкой. Если пороговый эле.Лгент регистрирует низкое напряжение, то контакт есть, если напряжение равно Е, то в цепи обрыв. В случае нормального контактирования из блока 4 определения контакта поступает разрешение на начало контроля БИС в блок 6 управления.

Если какие-либо выводы БИС не законтактировали с контактирующим блоком 2, то блок определения контакта не дает разрещение на начало контроля БИС и на блоке 5 индикации отсутствия контакта включаются лампочки под номерами этих выводов. Когда оператор поправит выводы БИС в контактирующем блоке, лампочки гаснут и после повторного запуска поступает разрешение па начало контроля БИС в блок 6 управления.

Блок управления дает команду, по которой коммутатор 3 подключает выводы БИС к компараторам 7 логических уровней и блоку 8 формирователей, после чего совместно с вычислителем 10 в устройстве образуется полная электрическая схема ЭКВМ. Формирователи служат для восстановления сигналов, ослабленных в соединительных проводах. Компараторы подключены как можно ближе к выходам БИС до формирователей.

Из блока управления в блок 14 распределения тестовых команд поступает импульс, по которому вырабатывается команда на проведение первого теста. Эта команда в виде разрещающего потенциала подается на адресную шину в блок 15 задания программы и в блок 13 задания выходных результатов. В блоке задания программы вырабатывается команда, которая в клавиатуре производит действие, эквивалентное нажатию на клавишу ЭКВМ, согласно заложенной программе испытаний. Это вызывает выполнение в ЭКВМ некоторой операции, состоящей из большого числа промежуточных действий, равного числу тактов, необходимых для ее выполнения, например при умножении до 7500 тактов. БИС, будучи включенной в схему ЭКВМ, участвует во всех этих действиях и хотя бы один ее сбой приводит к искажению конечного результата операции. Во время проведения операции импульсы, поступающие с каждого выхода БИС, сравниваются компараторами логических уровней по амплитуде с эталонными уровнями «О и «1, задаваемыми блоком 17 эталонов, и результат сравнения подается в блок 9 анализа годности.

При проведении операции в ЭКВМ сигналы на блок 11 цифровой индикации не проходят. После выполнения операции результат подается на блок цифровой индикации и блок 12 сравнения, где поразрядно сравнивается с ожидаемым результатом, поступающим на вторые входы блока сравнения с блока 13 задания выходных результатов.

Результат сравнения по каждому разряду поступает в блок анализа годности, где обрабатывается информация, поступающая от компараторов логических уровней и блока сравнения, и по совокупности параметров определяется годность испытываемой схемы по данному тесту.

Результат анализа подается на блок 18 индикадип годности, на котором расположены индикаторы «Годен, «Брак. Брак в свою очередь подразделяется на «Брак по логическому уровню и «Функциональный брак.

Информация о годности БИС подается также в блок 6 управления, который в случае годности по первому тесту вырабатывает очередной импульс в блок 14 распределения тестовых команд, где тот преобразуется в команду па проведение второго и других тестов до М-го теста. Если БИС годна по всем М тестам, то блок распределения тестовых команд вырабатывает последнюю (М + 1)-ю команду, которая заводится в блок управления и расшифровывается как конец контроля. По этой команде происходит остановка работы и на блоке индикации годности индицируется «Годен. В случае негодности БИС по какому-либо тесту происходит немедленный останов работы устройства и па блоке индикации годности индицируется «Брак.

В устройстве предусмотрен ручной режим контроля, при котором оператор работает по любой программе с клавиатуры и анализирует функциональную годность БИС визуально на блоке цифровой индикации. При этом блок компараторов логических уровней контролирует амплитуду сигналов как и в автоматическом режиме, а блок управления, блок сравнения, блок задания выходных результатов, блок распределения тестовых команд и блок программы отключаются.

6 Формула изобретения

Устройство для автоматического контроля больших интегральных схем на МОП-структуpax, содержащее коммутатор, входы которого соединены с выходами контактирующего блока, блок управления, соединенный с коммутатором, блок анализа годности, соединенный с блоком управления, индикатор годности, соединенный с выходом блока анализа годности, блок эталонов, компаратор логических уровней, соединенный с блоком эталонов, блоком анализа годности и второй группой выходов коммутатора, блок задания программы,

блок распределения тестовых команд, соединенные зыходамц с блоко.м задания программы и блоком унравлення, а входом - с блоком управления, блок задания выходных результатов, соединенный с выходами блока распределения тестовых команд, блок сравнения, входы которого соединены с блоком задания выходных результатов, а выход - блоком анализа годности, формирователь, соединенный с второй группой выходов коммутатора,

и блок питания, соединенный со всеми блоками, о т л и ч а ю щ е е с я тем, что, с целью увеличения достоверности контроля, оно содержит клавиатуру, соединенную с блоком задания программы, вычислитель, соединенный через формирователь, коммутатор и контактирующий блок с испытываемой схемой, с блоком сравнения и блоком задания выходных результатов, а входами - с клавиатурой, цифровой индикатор, соединеиный с выходами вычислителя, блок определен л контакта, соедииенмый с первой группой выходов комм таторл и с блоком управления, и блок индикации отсутствия контакта, соединенный с блоком определения контакта.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых интегральных схем | 1978 |

|

SU943747A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для контроля схем цифровых вычислительных машин | 1978 |

|

SU734691A1 |

| Устройство сбора и обработки информации для систем контроля | 1983 |

|

SU1089585A1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1980 |

|

SU907556A1 |

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

| Устройство для контроля параметров | 1985 |

|

SU1291930A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Устройство для контроля логических схем | 1976 |

|

SU595735A1 |

Авторы

Даты

1976-03-30—Публикация

1974-04-11—Подача