Изобретение относится к автоматике и может быть использовано при входном контроле изделий на производстве.

Целью изобретения является повышение достоверности и производительности устройства за счет обеспечения возможности использования последовательного плана контроля.

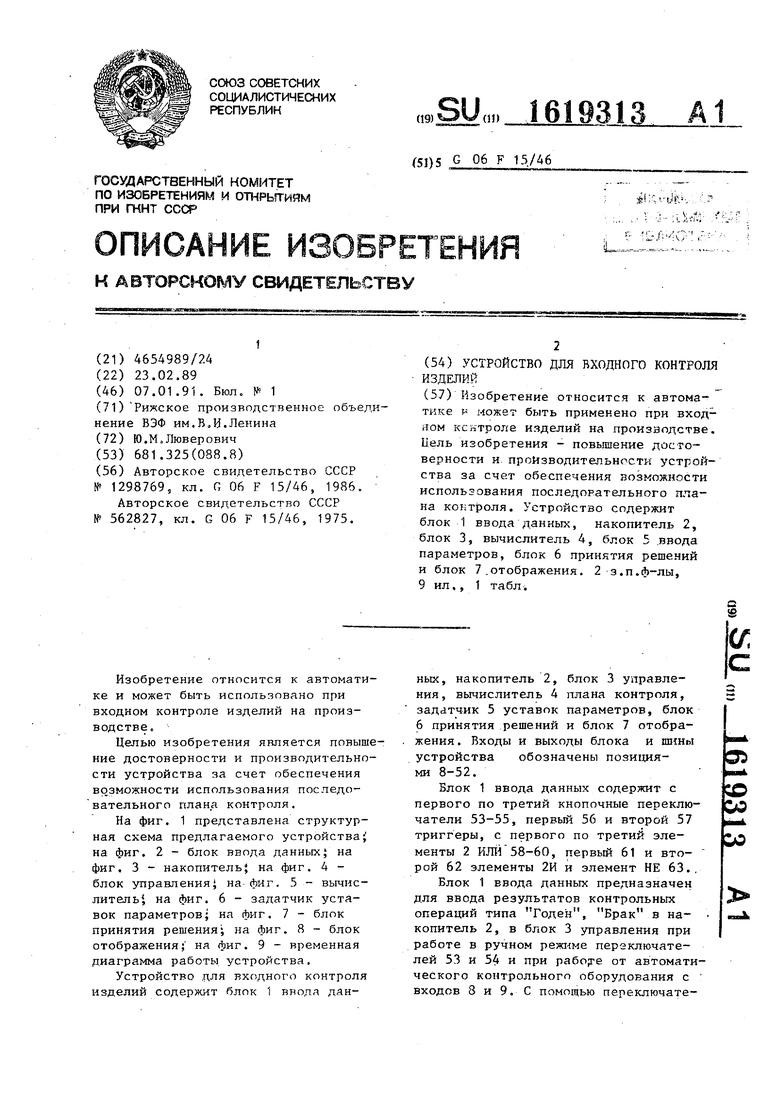

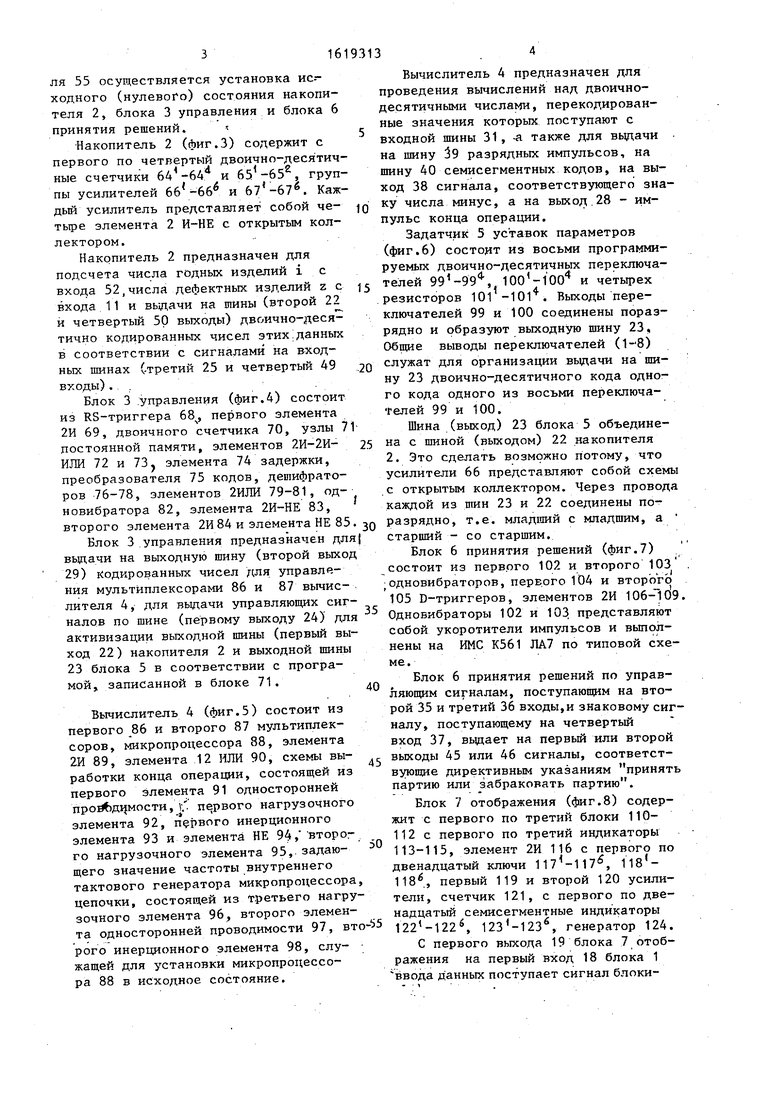

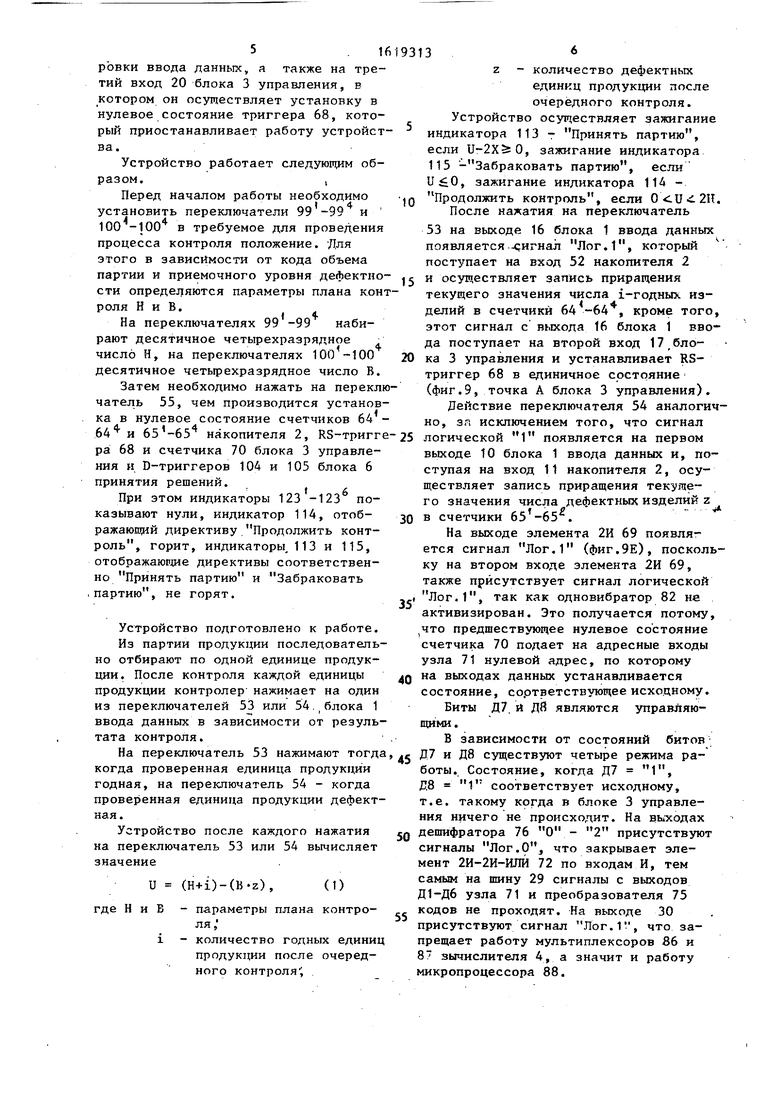

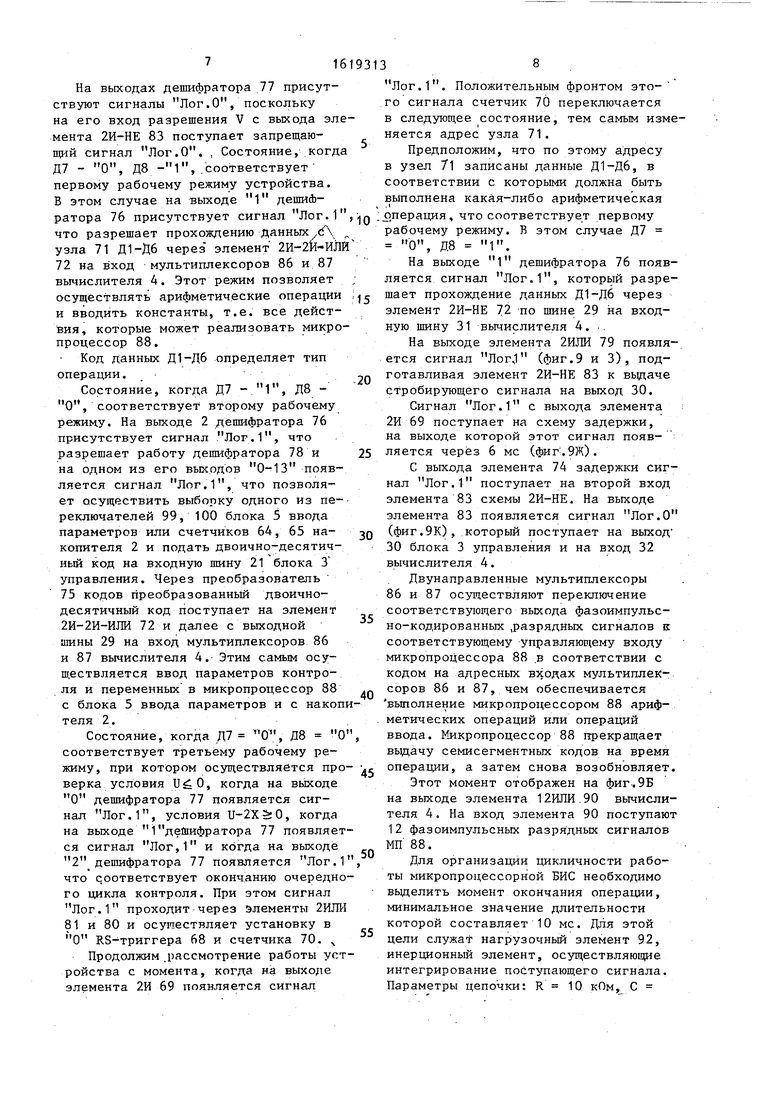

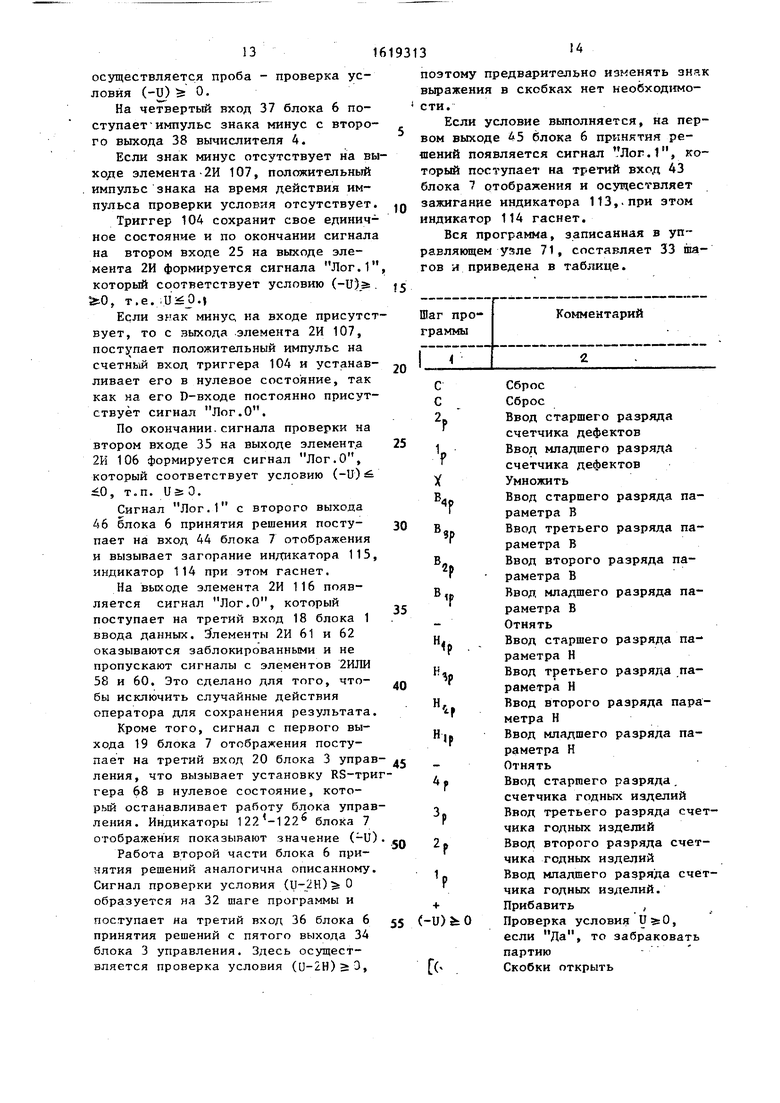

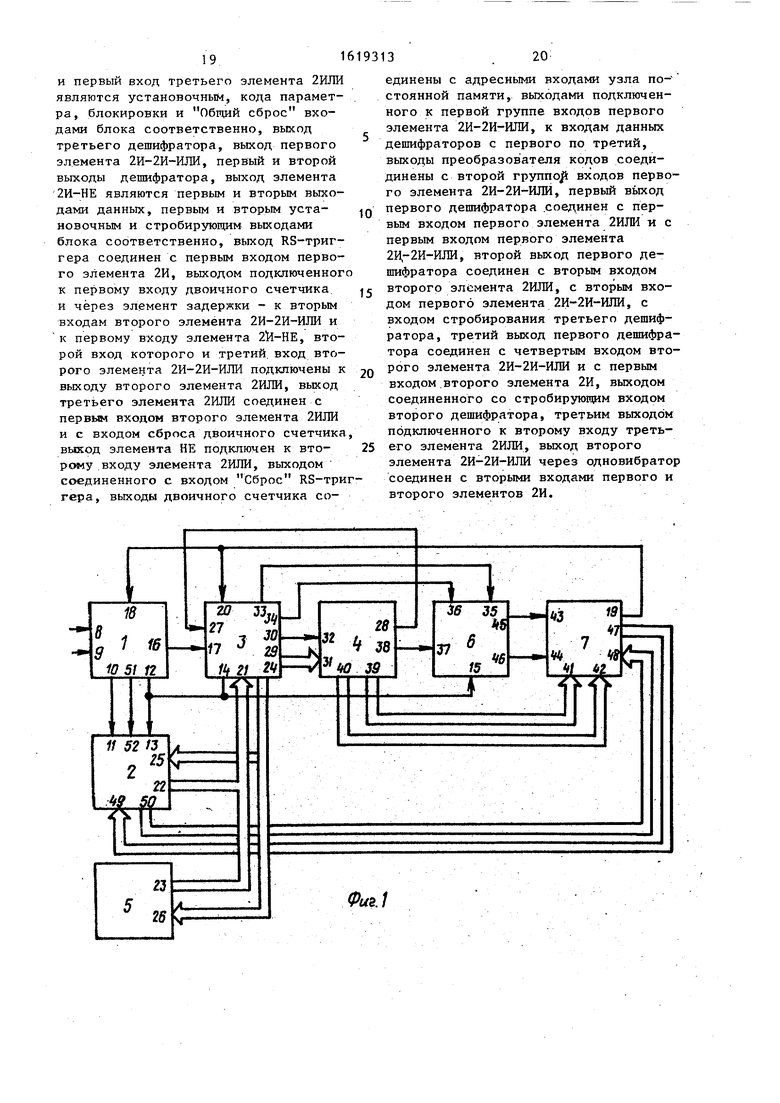

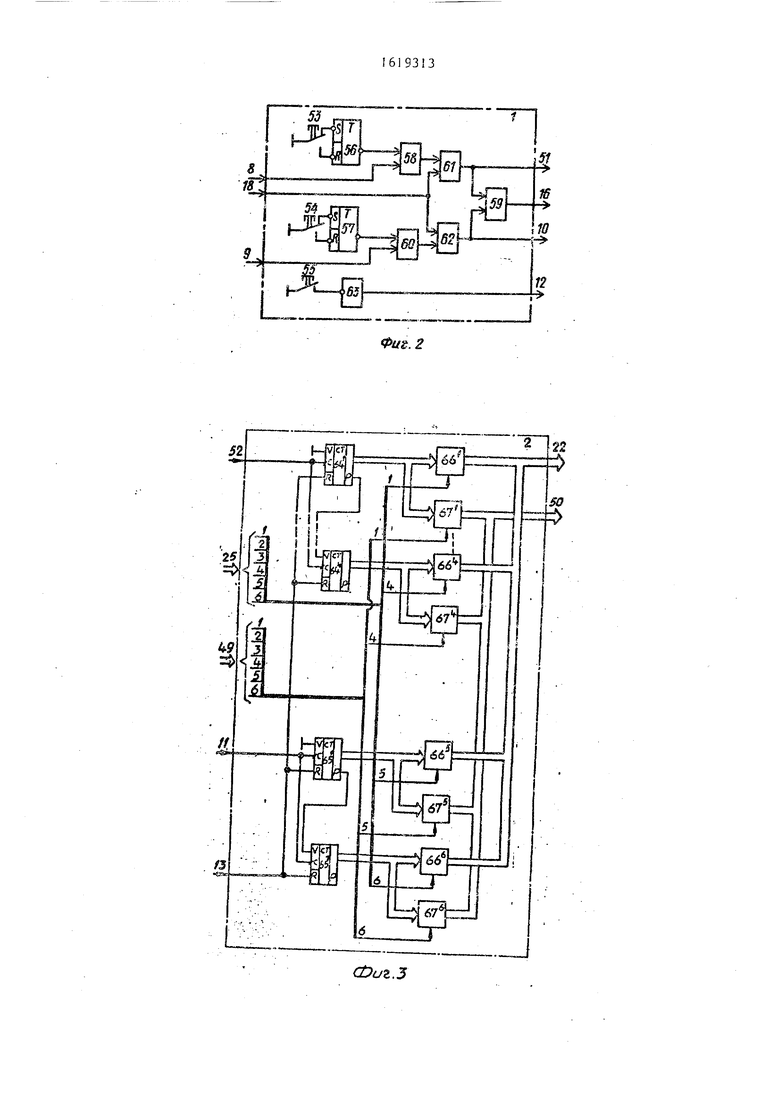

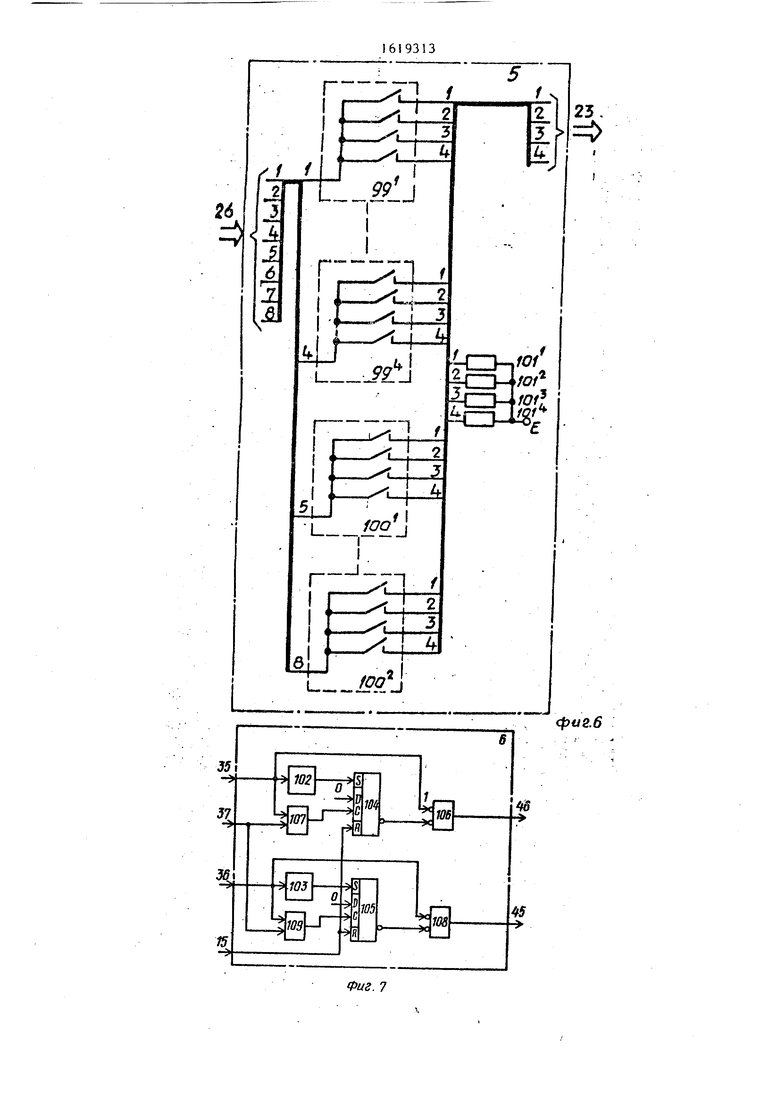

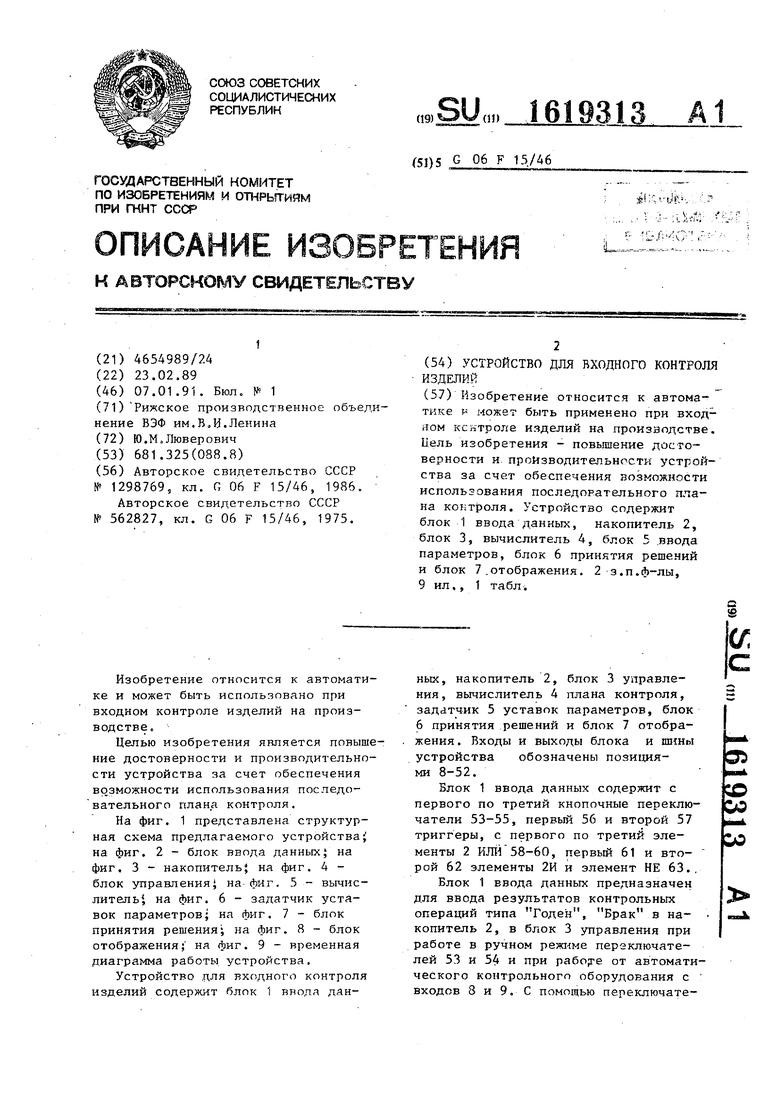

На фиг. 1 представлена структурная схема предлагаемого устройства , на фиг. 2 - блок ввода данных; на фиг. 3 - накопитель; на фиг. 4 - блок управленияJ на фиг. 5 - вычис- литель$ на фиг. 6 - задатчик уставок параметров; на фиг. 7 - блок принятия решения; на фиг. 8 - блок отображения; на фиг. 9 - временная диаграмма работы устройства.

Устройство для входного контроля изделий содержит блок 1 ввода данных, накопитель 2, блок 3 управления, вычислитель 4 плана контроля, задатчик 5 уставок параметров, блок 6 принятия решений и блок 7 отображения . Входы и выходы блока и шины устройства обозначены позициями 8-52.

Блок 1 ввода данных содержит с первого по третий кнопочные переключатели 53-55, первый 56 и второй 57 триггеры, с первого по третий элементы 2 ИЛИ 58-60, первый 61 и вто- рой 62 элементы 2И и элемент НЕ 63..

Блок 1 ввода данных предназначен для ввода результатов контрольных операций типа Годен, Брак в на- копитель 2, в блок 3 управления при работе в ручном режиме переключателей 53 и 54 и при работе от автоматического контрольного оборудования с входов 8 и 9. С помощью переключате(/: с

о со

UO

s

ля 55 осуществляется установка ис-- ходного (нулевого) состояния накопителя 2, блока 3 управления и блока 6 принятия решений.

Накопитель 2 (фиг.З) содержит с первого по четвертый двоично-десятичные счетчики 64 -64 и 65 -65 , группы усилителей 66 -66 и 67 -67 . Каждый усилитель представляет собой че- тыре элемента 2 И-НЕ с открытым коллектором.

Накопитель 2 предназначен для подсчета числа годных изделий i с входа 52,числа дефектных изделий z с входа 11 и выдачи на шины (второй 22 и четвертый 50 выходы) двоично-десятично кодированных чисел этих данных в соответствии с сигналами на входных шинах (третий 25 и четвертый 49 входы).

Блок 3 управления (фиг.4) состоит из RS-триггера 68ч, первого элемента 2И 69, двоичного счетчика 70, узлы 71 постоянной памяти, элементов 2И-2И- ИЛИ 72 и 73 элемента 74 задержки, преобразователя 75 кодов, дешифраторов 76-78, элементов 2ИЛИ 79-81, од- новибратора 82, элемента 2И-НЕ 83, второго элемента 2И84 и элемента НЕ 85.

Блок 3 управления предназначен для выдачи на выходную шину (второй выход 29) кодированных чисел для управления мультиплексорами 86 и 87 вычислителя 4, для выдачи управляющих сигналов по шине (первому выходу 24) для активизации выходной шины (первый выход 22) накопителя 2 и выходной шины 23 блока 5 в соответствии с програ- мой, записанной в блоке 71.

Вычислитель 4 (фиг.5) состоит из первого 86 и второго 87 мультиплексоров, микропроцессора 88, элемента 2И 89, элемента 12 ИЛИ 90, схемы вы- работки конца операции, состоящей из первого элемента 91 односторонней проводимости, f. первого нагрузочного элемента 92, первого инерционного элемента 93 и элемента НЕ 94, второ- го нагрузочного элемента 95, задаю- щего значение частоты внутреннего тактового генератора микропроцессора, цепочки, состоящей из третьего нагрузочного элемента 96, второго элемента односторонней проводимости 97, ВТО рого инерционного элемента 98, служащей для установки микропроцессора 88 в исходное состояние.

JQ

15 20

25 эд

| ,0

Д5 D -155

35

Вычислитель 4 предназначен для проведения вычислений над двоично- десятичными числами, перекодированные значения которых поступают с входной шины 31, -а также для выдачи на шину 39 разрядных импульсов, на шину 40 семисегментных кодов, на выход 38 сигнала, соответствующего знаку числа минус, а на выход 28 - импульс конца операции.

Задатчик 5 уставок параметров (фиг.6) состоит из восьми программируемых двоично-десятичных переключателей , ЮО -ЮО4 и четырех резисторов 101 -101 . Выходы переключателей 99 и 100 соединены поразрядно и образуют выходную шину 23, Общие выводы переключателей (1-8) служат для организации выдачи на шину 23 двоично-десятичного кода одного кода одного из восьми переключателей 99 и 100.

Шина (выход) 23 блока 5 объединена с шиной (выходом) 22 накопителя 2. Это сделать возможно потому, что усилители 66 представляют собой схемы с открытым коллектором. Через провода каждой из тин 23 и 22 соединены поразрядно, т.е. младший с младшим, а старший - со старшим.

Блок 6 принятия решений (фиг.7) состоит из первого 102 и второго 103 (одновибраторов, первого 104 и второго 105 D-триггеров, элементов 2И 106-109. Одновибраторы 102 и 103 представляют собой укоротители импульсов и выполнены на ИМС К561 ЛА7 по типовой схеме.

Блок 6 принятия решений по управляющим сигналам, поступающим на второй 35 и третий 36 входы,и знаковому сигналу, поступающему на четвертый вход 37, выдает на первый или второй выходы 45 или 46 сигналы, соответствующие директивным указаниям принять партию или забраковать партию.

Блок 7 отображения (фиг.8) содержит с первого по третий блоки 110- 112с первого по третий индикаторы 113-115, элемент 2И 116 с первого по двенадцатый ключи 1171-117, 118й, первый 119 и второй 120 усилители, счетчик 121, с первого по двенадцатый семисегментные индикаторы 122 -1226, 123-1236, генератор 124. С первого выхода 19 блока 7 отображения на первый вход 18 блока 1 ввода данных поступает сигнал блоки51fi

ровки ввода данных, а также на третий вход 20 блока 3 управления, в котором он осуществляет установку в нулевое состояние триггера 68, который приостанавливает работу устройства.

Устройство работает следующим образом.,

Перед началом работы необходимо установить переключатели 99 -99 и 100-100 в требуемое для проведения процесса контроля положение. Для этого в зависимости от кода объема партии и приемочного уровня дефектности определяются параметры плана контроля Н и В.

На переключателях 99 -99 набирают десятичное четырехразрядное число Н, на переключателях 100 -100 десятичное четырехразрядное число Б.

Затем необходимо нажать на переключатель 55, чем производится установка в нулевое состояние счетчиков 64 JQ Продолжить контроль, если 0. После нажатия на переключатель

53 на выходе 16 блока 1 ввода данных появляется -сигнал Лог.1, который поступает на вход 52 накопителя 2

j 5 и осуществляет запись приращения

текущего значения числа i-годных изделий в счетчики 64 -64 , кроме того этот сигнал с выхода 16 блока 1 вво да поступает на второй вход 17,бло20 ка 3 управления и устанавливает RS- триггер 68 в единичное состояние (фиг.9, точка А блока 3 управления).

Действие переключателя 54 аналоги но, эп исключением того, что сигнал

64 и 65-654 накопителя 2, RS-тригге-25 логической 1 появляется на первом

ра 68 и счетчика 70 блока 3 управления и D-триггеров 104 и 105 блока 6 принятия решений.

При этом индикаторы 123 -123 показывают нули, индикатор 114, отображающий директиву Продолжить контроль, горит, индикаторы, 113 и 115, отображающие директивы соответственно Принять партию и Забраковать

30

выходе 10 блока 1 ввода данных и, по ступая на вход 11 накопителя 2, осуществляет запись приращения текущего значения числа дефектных изделий z в счетчики 65 -65 .

На выходе элемента 2И 69 появляется сигнал Лог.1 (фиг.9Е), поскол ку на втором входе элемента 2И 69, также присутствует сигнал логической . Лог.1, так как одновибратор 82 не активизирован. Это получается потому что предшествующее нулевое состояние счетчика 70 подает на адресные входы узла 71 нулевой адрес, по которому на выходах данных устанавливается состояние, сортветствующее исходному.

партию

не горят.

Устройство подготовлено к работе.

Из партии продукции последовательно отбирают по одной единице продукции. После контроля каждой единицы продукции контролер нажимает на один из переключателей 53 или 54 р блока 1 ввода данных в зависимости от результата контроля.

z - количество дефектных

единиц продукции после очередного контроля. Устройство осуществляет зажигание индикатора 113 - Принять партию, если U-2XbO, зажигание индикатора 115 - Забраковать партию, если , зажигание индикатора 114 Продолжить контроль, если 0.. После нажатия на переключатель

53 на выходе 16 блока 1 ввода данных появляется -сигнал Лог.1, который поступает на вход 52 накопителя 2

и осуществляет запись приращения

текущего значения числа i-годных изделий в счетчики 64 -64 , кроме того, этот сигнал с выхода 16 блока 1 ввода поступает на второй вход 17,блока 3 управления и устанавливает RS- триггер 68 в единичное состояние (фиг.9, точка А блока 3 управления).

Действие переключателя 54 аналогично, эп исключением того, что сигнал

логической 1 появляется на первом

0

5

0

выходе 10 блока 1 ввода данных и, поступая на вход 11 накопителя 2, осуществляет запись приращения текущего значения числа дефектных изделий z в счетчики 65 -65 .

На выходе элемента 2И 69 появляется сигнал Лог.1 (фиг.9Е), поскольку на втором входе элемента 2И 69, также присутствует сигнал логической . Лог.1, так как одновибратор 82 не активизирован. Это получается потому, что предшествующее нулевое состояние счетчика 70 подает на адресные входы узла 71 нулевой адрес, по которому на выходах данных устанавливается состояние, сортветствующее исходному.

Биты Д7 и ДЯ являются управляющими.

В зависимости от состояний битов

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для входного контроля изделий | 1990 |

|

SU1746388A2 |

| Устройство для обмена информацией | 1982 |

|

SU1084776A1 |

| Многоканальное устройство тестового контроля логических узлов | 1990 |

|

SU1837295A1 |

| Электропривод постоянного тока | 1990 |

|

SU1741247A1 |

| Репродукционный фотоаппарат | 1987 |

|

SU1633372A1 |

| Запоминающее устройство с контролем и коррекцией ошибок | 1983 |

|

SU1117715A1 |

| Устройство для порогового контроля периода | 1987 |

|

SU1456928A1 |

| Устройство для входного контроля | 1985 |

|

SU1298769A1 |

| Делитель частоты с переменным дробным коэффициентом деления | 1989 |

|

SU1746530A1 |

| МНОГОКАНАЛЬНАЯ ТЕЛЕМЕТРИЧЕСКАЯ СЕЙСМОРАЗВЕДОЧНАЯ СИСТЕМА | 1994 |

|

RU2107312C1 |

Изобретение относится к автоматике v может быть применено при входном контроле изделий на производстве. Цель изобретения - повышение достоверности и производительности устройства за счет обеспечения возможности использования последовательного плана ког-троля. Устройство содержит блок 1 ввода данных, накопитель 2, блок 3, вычислитель 4, блок 5 ввода параметров, блок 6 принятия решений и блок 7 .отображения. 2 з.п.ф-лы, 9 ил,, 1 табл.

На переключатель 53 нажимают тогда, Д7 и Д8 существуют четыре режима ракогда проверенная единица продукции годная, на переключатель 54 - когда проверенная единица продукции дефектная.

Устройство после каждого нажатия на переключатель 53 или 54 вычисляет значение

боты. Состояние, когда Д7 1, Д8 1 соответствует исходному, т.е. такому когда в блоке 3 управления ничего не происходит. На выходах 5Q дешифратора 76 О - 2 присутствуют сигналы Лог.О, что закрывает элемент 2И-2И-ИЛИ 72 по входам И, тем самым на шину 29 сигналы с выходов Д1-Д6 узла 71 и преобразователя 75 кодов не проходят. На выходе 30 присутствуют сигнал Лог.1, что запрещает работу мультиплексоров 86 и 87 вычислителя 4, а значит и работу микропроцессора 88.

U Н и В

(H+i)-(B-z),

(О

-параметры плана контроля „

-количество годных единиц продукции после очередного контроля ,

Д7 и Д8 существуют четыре режима работы. Состояние, когда Д7 1, Д8 1 соответствует исходному, т.е. такому когда в блоке 3 управления ничего не происходит. На выходах дешифратора 76 О - 2 присутствуют сигналы Лог.О, что закрывает элемент 2И-2И-ИЛИ 72 по входам И, тем самым на шину 29 сигналы с выходов Д1-Д6 узла 71 и преобразователя 75 кодов не проходят. На выходе 30 присутствуют сигнал Лог.1, что запрещает работу мультиплексоров 86 и 87 вычислителя 4, а значит и работу микропроцессора 88.

На выходах дешифратора 77 присутствуют сигналы Лог.О, поскольку на его вход разрешения V с выхода элемента 2И-НЕ 83 поступает запрещающий сигнал Лог.О. , Состояние, когда Д7 - О, Д8 , соответствует первому рабочему режиму устройства. В этом случае на выходе 1 деши Ь16193138

Лог.1. Положительным фронтом этого сигнала счетчик 70 переключается в следующее достояние, тем самым изменяется адрес узла 71.

Предположим, что по этому адресу в узел 71 записаны данные Д1-Д6, в соответствии с которыми должна быть выполнена какая-либо арифметическая

ратора 76 присутствует сигнал Лог.1,п .операция, что соответствует первому

15

20

25

30

что разрешает прохождению данных/ f узла 71 Д1-Д6 через элемент 2И-2Й-ИЛЙ 72 на вход мультиплексоров 86 и 87 вычислителя 4. Этот режим позволяет осуществлять арифметические операции и вводить константы, т.е. все действия, которые может реализовать микропроцессор 88,

Код данных Д1-Д6 определяет тип операции.

Состояние, когда Д7 - 1, Д8 - О, соответствует второму рабочему режиму. На выходе 2 дешифратора 76 присутствует сигнал Лог.1, что разрешает работу дешифратора 78 и на одном из его выходов 0-13 появляется сигнал Лог.1, что позволяет осуществить выборку одного из переключателей 99, 100 блока 5 ввода параметров или счетчиков 64, 65 накопителя 2 и подать двоично-десятичный код на входную шину 21 блока 3 управления. Через преобразователь 75 кодов преобразованный двоично- десятичный код поступает на элемент 2И-2И-ИЛИ 72 и далее с выходной шины 29 на вход мультиплексоров 86 и 87 вычислителя 4. Этим самым осуществляется ввод параметров контроля и переменных в микропроцессор 88 с блока 5 ввода параметров и с накопителя 2.

Состояние, когда Д7 О, Д8 О, соответствует третьему рабочему режиму, при котором осуществляется про- дс верка условия , когда на выходе О дешифратора 77 появляется сигнал Лог.1, условия U-2XSO, когда на выходе 1 дешифратора 77 появляется сигнал Лог,1 и когда на выходе 2 дешифратора 77 появляется Лог.1, что соответствует окончанию очередного цикла контроля. При этом сигнал Лог.1 проходит через элементы 2ИЛИ 81 и 80 и осуществляет установку в О RS-триггера 68 и счетчика 70. ч

Продолжим рассмотрение работы устройства с момента, когда на выходе элемента 2И 69 появляется сигнал

35

40

50

55

рабочему режиму. В этом случае Д7 О, Д8 1.

На выходе 1 дешифратора 76 появляется сигнал Лог.1, который разрешает прохождение данных Д1-Д6 через элемент 2И-НЕ 72 по шине 29 на входную шину 31 вычислителя 4.

На выходе элемента 2ИЛИ 79 появляется сигнал Лог,1 (фиг.9 и 3), подготавливая элемент 2И-НЕ 83 к выдаче стробирующего сигнала на выход 30.

Сигнал Лог.1 с выхода элемента 2И 69 поступает на схему задержки, на выходе которой этот сигнал появляется через 6 мс (фиг.9Ж).

С выхода элемента 74 задержки сигнал Лог.1 поступает на второй вход элемента 83 схемы 2И-НЕ. На выходе элемента 83 появляется сигнал Лог.О (фиг.9К), который поступает на выход 30 блока 3 управления и на вход 32 вычислителя 4.

Двунаправленные мультиплексоры 86 и 87 осуществляют переключение соответствующего выхода фазоимпульс- но-кодированных разрядных сигналов к соответствующему управляющему входу микропроцессора 88 в соответствии с кодом на адресных входах мультиплексоров 86 и 87, чем обеспечивается выполнение микропроцессором 88 арифметических операций или операций ввода. Микропроцессор 88 прекращает выдачу семисегментных кодов на время операции, а затем снова возобновляет.

Этот момент отображен на фиг.9Б на выходе элемента 12ИЛИ 90 вычислителя 4. На вход элемента 90 поступают 12 фазоимпульсных разрядных сигналов МП 88.

Для организации цикличности работы микропроцессорной БИС необходимо выделить момент окончания операции, минимальное значение длительности которой составляет 10 мс. Для этой цели служат нагрузочный элемент 92, инерционный элемент, осуществляющие интегрирование поступающего сигнала. Параметры цепочки: R 10 кПм, С

п .операция, что соответствует первому

5

0

5

30

дс

35

40

50

55

рабочему режиму. В этом случае Д7 О, Д8 1.

На выходе 1 дешифратора 76 появляется сигнал Лог.1, который разрешает прохождение данных Д1-Д6 через элемент 2И-НЕ 72 по шине 29 на входную шину 31 вычислителя 4.

На выходе элемента 2ИЛИ 79 появляется сигнал Лог,1 (фиг.9 и 3), подготавливая элемент 2И-НЕ 83 к выдаче стробирующего сигнала на выход 30.

Сигнал Лог.1 с выхода элемента 2И 69 поступает на схему задержки, на выходе которой этот сигнал появляется через 6 мс (фиг.9Ж).

С выхода элемента 74 задержки сигнал Лог.1 поступает на второй вход элемента 83 схемы 2И-НЕ. На выходе элемента 83 появляется сигнал Лог.О (фиг.9К), который поступает на выход 30 блока 3 управления и на вход 32 вычислителя 4.

Двунаправленные мультиплексоры 86 и 87 осуществляют переключение соответствующего выхода фазоимпульс- но-кодированных разрядных сигналов к соответствующему управляющему входу микропроцессора 88 в соответствии с кодом на адресных входах мультиплексоров 86 и 87, чем обеспечивается выполнение микропроцессором 88 арифметических операций или операций ввода. Микропроцессор 88 прекращает выдачу семисегментных кодов на время операции, а затем снова возобновляет.

Этот момент отображен на фиг.9Б на выходе элемента 12ИЛИ 90 вычислителя 4. На вход элемента 90 поступают 12 фазоимпульсных разрядных сигналов МП 88.

Для организации цикличности работы микропроцессорной БИС необходимо выделить момент окончания операции, минимальное значение длительности которой составляет 10 мс. Для этой цели служат нагрузочный элемент 92, инерционный элемент, осуществляющие интегрирование поступающего сигнала. Параметры цепочки: R 10 кПм, С

0,32 мкФ. Элемент 91 ележит для быстрого восстановления отрицательного фронта сигнала (фиг.9Б).

На фиг.9Г показан сформированный импульс, положительный фронт которого несет информацию об окончании операции. Этот импульс с выхода 28 вычислителя .поступает на вход 27 блока управления и на вход элемента 2И-2И- ИЛИ 73, а с его выхода - на вход од- . новибратора 82, который запускается положительным фронтом импульса (фиг.9Д). Длительность импульса, вы10

нал поступает на счетный вход счетчика 70 и положительным фронтом осуществляет приращение на единицу его содержимого (фиг.9Е, момент времени t.). Для наглядности на временной диаграмме (фиг.9, моменты времени .) изображена выработка двух подряд управляющих сигналов на выходах 33 или 34 блока управления, т.е. когда устройство дважды обращается к третьму рабочему режиму.

Содержимое узла,71, соответствующее очередному адресу, таково, что

рабатываемого одновибратором 82, рав- Д7 Д8 О. На выходе О дешиф20

30

на 12 х Тр 5 мс и выбрана такой с тем, чтобы микропроцессор 88 полностью закончил выработку результата.

Импульс с выхода одновибратора 82 поступает на второй вход элемента 2И 69, с выхода которого этот импульс поступает на вход счетчика 70. Положительный фронт импульса вызывает срабатывание счетчика 70, осуществляя приращение его содержимого на единицу - 25 (фиг,9Е).

На вход узла 71 с выхода счетчика 70 поступает следующий адрес. Управляющие биты ПЗУ Д7, Д8 реализуют, один из трех рабочих режимов. В случае, когда реализуются первые два рабочих режима, работа устройства аналогична описанному.

Рассмотрим теперь переход к третьему рабочему режиму, который характеризуется тем, что при этом режиме осуществляются операции проверки.

Управляющие биты Д7, Д8 ПЗУ 71 принимают нулевое значение. На выходе О дешифратора 76 появляется сигнал Лог.1 (фиг.9И), который разрешает прохождение сигнала с выхода элемент 74 задержки через элемент 2И-2И-ИЛИ 73 (фиг.9Ж), момент времени tЈ.

Сигнал с выхода элемента 73 положительным фронтом запускает одно- вибратор 82. Сигнал с выхода одновибратора 82 (фиг.9Д) поступает на вход элемента 2И 84, с выхода которого стробирующий сигнал поступает на вход разрешения дешифратора 77 (фиг.9Л). Дешифратор 77 в зависимости от данных на его информационных входах выдает на свои выходы один из управляющих сигналов проверки или останова.

Сигнал с выхода одновибратора 82 поступает также на второй вход элемента 2И 69. С выхода последнего сигратора 76 снова присутствует Лог. элемент 2И 84 --снова подготов - ; лен к разрешению прохождения сигнала с выхода элемента 74 задержки в мо мент времени t4 (фиг.9Д), пдновибра- тор 82 вырабатывает очередной импульс который пройдя элемент 2И 69 вызывает очередное приращение счетчика 70 (фиг.9Е) в момент времени t

Предположим, что новое содержимое узла 71, соответствующее очередному адресу, таково, что Д7 1, Д8 О, что соответствует второму рабочему режиму. На выходе 2 дешифратора 76 имеется сигнал Лог.1, который разрешает прохождение через элемент 2И-2И-ИЛИ 72 на выход 29 сигналов с выхода преобразователя 75 кодов. Сигнал с выхода 2 дешифратора 76 поступает также на стробирующий вход V дешифратора 78, на одном из -выходов которого О - 13 появляется сигнал Лог.1.

С выхода 24 блока 3 управления сигналы с дешифратора 78 поступают на вход 25 накопителя и вход 26 за- датчика 5 уставок параметров. Этим самым на шине, 21 блока 3 управления появляется код выбранного парамет- ,е pa H, В или переменных i, z.

На выходе элемента 2ИЛИ 79 появляется сигнал Лог.1 (фиг.93), подготавливая элемент 2И-НЕ 83 к прохождению сигнала с выхода элемента 74 задержки (фиг.9Ж).

При совпадении этих сигналов по времени на выходе элемента 2И-НЕ 83 : - появляется стробирующий сигнал (фиг.9 К) , который с выхода 30 посту- пает на вход 32 вычислителя 4.

Мультиплексоры 86 и 87 вычислителя 4 осуществляют соединение в со- . ответствии с калькуляторным кодом управляющих входов, с фазоимпульсны35

40

50

55

нал поступает на счетный вход счетчика 70 и положительным фронтом осуществляет приращение на единицу его содержимого (фиг.9Е, момент времени t.). Для наглядности на временной диаграмме (фиг.9, моменты времени .) изображена выработка двух подряд управляющих сигналов на выходах 33 или 34 блока управления, т.е. когда устройство дважды обращается к третьму рабочему режиму.

Содержимое узла,71, соответствующее очередному адресу, таково, что

Д7 Д8 О. На выходе О дешиф20

30

25

ратора 76 снова присутствует Лог. элемент 2И 84 --снова подготов - ; лен к разрешению прохождения сигнала с выхода элемента 74 задержки в мо мент времени t4 (фиг.9Д), пдновибра- тор 82 вырабатывает очередной импульс, который пройдя элемент 2И 69 вызывает очередное приращение счетчика 70 (фиг.9Е) в момент времени t

Предположим, что новое содержимое узла 71, соответствующее очередному адресу, таково, что Д7 1, Д8 О, что соответствует второму рабочему режиму. На выходе 2 дешифратора 76 имеется сигнал Лог.1, который разрешает прохождение через элемент 2И-2И-ИЛИ 72 на выход 29 сигналов с выхода преобразователя 75 кодов. Сигнал с выхода 2 дешифратора 76 поступает также на стробирующий . вход V дешифратора 78, на одном из -выходов которого О - 13 появляется сигнал Лог.1.

С выхода 24 блока 3 управления сигналы с дешифратора 78 поступают на вход 25 накопителя и вход 26 за- датчика 5 уставок параметров. Этим самым на шине, 21 блока 3 управления появляется код выбранного парамет- ,е pa H, В или переменных i, z.

На выходе элемента 2ИЛИ 79 появляется сигнал Лог.1 (фиг.93), подготавливая элемент 2И-НЕ 83 к прохождению сигнала с выхода элемента 74 задержки (фиг.9Ж).

При совпадении этих сигналов по времени на выходе элемента 2И-НЕ 83 : - появляется стробирующий сигнал (фиг.9 К) , который с выхода 30 посту- пает на вход 32 вычислителя 4.

Мультиплексоры 86 и 87 вычислителя 4 осуществляют соединение в со- . ответствии с калькуляторным кодом управляющих входов, с фазоимпульсны35

40

0

5

ми разрядными выходами. Микропроцессор 88 прекращает выдачу семисег- ментных кодов и осуществляет операцию ввода (фиг.9В).

Сформированный импульс с выхода 28 вычислителя 4 (фиг.9Г) поступает на элемент 2И-2И-ИЛИ 73. Сигнал Лог.1 с выхода элемента 73 поступает на вход одновибратора и запускет его (фиг.9Д, момент времени tg).

Импульс с выхода одновибратора 82 поступает на второй вход элемента 2И 69, сигнал с выхода которого поступает на счетный вход счетчика 70 и вызывает приращение его содержимого на единицу (фиг.9Е и В, момент времени t.,).

Содержимое узла памяти, соответствующее очередному адресу, теперь таково, что Д7 Д8 О. На выходе О дешифратора 76 присутствует сигнал Лог.1 (фиг.9И).

Сигнал с выхода элемента 74 задержки меняет свое состояние с Лог.О на Лог.1 (фиг.9Ж) и поступает на вход элемента 2И-2И-ИЛИ 73 с выхода которого сигнал поступает на вход одновибратора 82 и положительным фронтом сигнала запускает его (фиг.9Д). Отрицательный фронт сигнала с выхода одновибратора 82 поступает на вход элемента 2И 84, с выхода которого сигнал поступает стробирующий вход дешифратора 77 (фиг.9Д). Рассматриваемый режим является третьим рабочим, причем прмем, что вырабатывается сигнал окончания контроля. В этом случае на выходе 2 дешифратора 77 появляется сигнал Лог.1, который поступает на вход элемента 2ИЛИ 81 ,с выхода которого сигнал Лог.1 поступает на вход установки в нулевое состояние - исход ное счетчика 70 и на вход элемента 2ИЛИ 80, с выхода которого сигнал Лог,, поступает на R-вход RS-триг- гера 68 и устанавливает его в нулевое состояние (фиг.9Д).

Узел/ 71 выдает на управляющие выходы Д7, Д8 сигнал Лог.1, что вызывает появление сигнала Лог.О на выходе дешифратора 76, а следовательно, на выходе элемента 2И 84 возникает синал Лог.О (фиг.9И и Л).

Сигнал с выхода одновибратора 82 поступает на вход элемента 2И, 69, однако теперь элемент 2И 69 закрыт для прохождения положительного фрон

0

5

0

5

0

5

0

5

0

5

та сигнала с выхода одновибратора 82 потому, что на втором его входе присутствует сигнал Лог.О.

Работа схемы приостанавливается. Микропроцессор 88 продолжает генерацию семисегм ентных кодов, обеспечивая индикацию на индикаторах 122 -122й текущего результата очередного акта контроля, в данном случае (U-2H).

Рассмотрим работу блока 6 принятия решений.

В соответствии с управляющей программой, записанной в узел 71 блока 3 управления, устройство шаг за шагом осуществляет вычисление формулы (1). Когда на определенном шаге, а именно на 20, МП 88 осуществляет вычисление значения U, на 21-м шаге нз выходе О дешифратора 77 появляется сигнал Лог.1, сигнал проверки условия U Ј 0.

I- Первый разрядный фазоимпульсный сигнал совместно с одним из сегментных сигналов на выходах микропроцессора 88 определяет знак результата вычисленного значения, причем первый сигнал перекрывает по времени второй. Длительность первого 400 мкс, а второго 300 мкс. При наличии знака минус на выходе элемента 2И 89 вычислителя 4 появляется положительный импульс.

При наличии положительного числа или нуля сигнал на выходе элемента 2И 89 отсутствует. Поэтому осуществить проверку напрямую затруднительно.

Для реализации проверки условия U 0 производится эквивалентная проверка (-и)э: 0. Изменение знака числа производится предварительно в программе.

На второй вход 35 блока 6 принятия решений поступает сигнал Лог.1 с четвертого выхода 33 блока J уп- равления. Этот сигнал поступает на первый вход элемента 2И 106 и запрещает его работу на все время действия сигнала. Первые два положительных импульса соответствуют длительности импульсов проверки условий (фиг«9Л).

Этот сигнал поступает на вход одновибратора 102, с выхода которого короткий положительный импульс устанавливает D-триггер 104 в единичное состояние, так как предвритель- но он установлен в нулевое состояние по первому входу 15. Этим самым

осуществляется проба - проверка условия (-U) 0.

На четвертый вход 37 блока 6 поступает импульс знака минус с второго выхода 38 вычислителя 4.

Если знак минус отсутствует на входе элемента-2И 107, положительный импульс знака на время действия импульса проверки условия отсутствует

Триггер 104 сохранит свое единичное состояние и по окончании сигнал на втором входе 25 на выходе элемента 2И формируется сигнала Лог.1 который соответствует условию (-U) 0, т.е. -UЈ0.|

Если знак минус, на входе присутсвует, то с выхода элемента 2И 107, поступает положительный импульс на счетный вход триггера 104 и устанавливает его в нулевое состояние, так как на его D-входе постоянно присутствует сигнал Лог.О.

По окончании.сигнала проверки на втором входе 35 на выходе элемента 2И 106 формируется сигнал Лог.О, который соответствует условию (-U) Ј0, т.п. U s О.

Сигнал Лог.1 с второго выхода 46 блока 6 принятия решения посту- пает на вход 44 блока 7 отображения и вызывает загорание индикатора 115 индикатор 114 при этом гаснет.

На выходе элемента 2И 116 появляется сигнал Лог.О, который поступает на третий вход 18 блока 1 ввода данных. Элементы 2И 61 и 62 оказываются заблокированными и не

пропускают сигналы с элементов 2ИЛИ 58 и 60. Это сделано для того, что- бы исключить случайные действия оператора для сохранения результата.

Кроме того, сигнал с первого выхода 19 блока 7 отображения поступает на третий вход 20 блока 3 управ ления, что вызывает установку RS-три гера 68 в нулевое состояние, который останавливает работу блока управления. Индикаторы блока 7 отображения показывают значение (-U)

Работа второй части блока 6 принятия решений аналогична описанному. Сигнал проверки условия () О образуется на 32 шаге программы и

поступает на третий вход 36 блока 6 принятия решений с пятого выхода 34 блока 3 управления. Здесь осуществляется проверка условия (и-2Н)Э,

поэтому предварительно изменять знак выражения в скобках нет необходимо- сти.

Если условие выполняется, на первом выходе 5 блока 6 принятия ре- тений появляется сигнал Лог.1, который поступает на третий вход 43 блока 7 отображения и осуществляет зажигание индикатора 113,-при этом индикатор 114 гаснет.

Вся программа, записанная в управляющем узле 71, составляет 33 шагов и приведена в таблице.

f5

20

25

30

ty

„ .« ty

дс

Г(,

35

50

Ч

«л

Ч

1

Р

5

+ (-U) fc О

счетчика дефектов Ввод младшего разряда счетчика дефектов Умножить

Ввод старшего разряда параметра В

Ввод третьего разряда параметра В

Ввод второго разряда параметра В

Ввод, младшего разряда параметра В Отнять

Ввод старшего разряда параметра Н

Ввод третьего разряда параметра Н

Ввод второго разряда параметра Н

Ввод младшего разряда параметра Н Отнять

Ввод старшего разряда . счетчика годных изделий Ввод третьего разряда счетчика годных изделий Ввод второго разряда счетчика годных изделий Ввод младшего разряда счетчика годных изделий. Прибавить , Проверка условия , если Да, то забраковать партию Скобки открыть

Продолжение таблицы

Да, то принять партию

Конец

Применение устройства для входного контроля изделий при использовании последовательного плана контроля позволяет повысить производительность труда контролера, поскольку значительно сокращает количество испытаний изделий до принятия решения принять или заброковать партию по сравнению с одноступенчатыми и двухступенчатыми планами контроля (по сравнению с одноступенчатыми в 2 раза) . Поэтому контролер может проконтролировать большое количество партий.

Исключаются субъективные ошибки контролера ввиду того, что даже пропуск при контроле изделий не может повлиять на точность принятия решений, поскольку директивное указание Продолжить контроль указывает контролеру на необходимость дальнейшего контроля до выработки устройством определенного решения.

В то же время при обычных планах контроля субъективные ошибки контролера могут привести к неверному результату ввиду пропусков при контрол неправильного подсчета годных или, негодных изделий и т.д. Снимаются также сложности организационного порядка, свойственные многоступенчатому плану контроля, поскольку дело сводится к простому нажатию на кнопки Брак или Годен. . .

Повышаемся достоверность контроля ввиду того, что оператор имеет возмоность наблюдать за ходом процесса контроля. В процессе контроля оператор последовательно раз за разом нажимает на переключатель 53 - Го

0

5

переключатель 54 Брак блока ввода данных. ,

Допустим, что в процессе контроля горит индикатор 114 - Продолжить контроль блока 7 отображения. После каждого акта контроля устройство на 32 шаге вычисляет выражение (и-2Н).и после окончания на 33 шаге индикаторы

Q блока 7 отображения показывают,это значение.

Примем также, что Н 50, В 50, В этом случае согласно формуле (1) выражение (TJ-2H) принимает по.следо5 вательно после каждого акта контроля ряд чисел, отличающихся на единицу;

49, 48, 47,,.. Если дефектные изделия отсутствуют, то последовательность чисел по абсолютной величине убывает и при (U-2H) загорается индикатор 113 блока 7 отображения, что соответствует директиве Принять партию.

Оператор имеет возможность наблюдать за ходом процесса контроля. На любом акте контроля у него имеется также возможность проверить численно достоверность хода контроля по формуле (1), так как значения Н, В набраны на переключателях 99 и 100 и ви0 зуально наблюдаемы, на индикаторах высвечиваются значения,i и z

Если в процессе контроля изделий встретилась дефектная единица, то согласно формуле (1), например, на

35 третьем акте контроля, выражение

(U-2H) принимает значение 98, вместо числа 47, т.е. проходит скачок зна- чений, что обращает внимание оператора на то, что вскоре может произой40 ти выработка определенной директивы, в данном случае Заброковать партию, поскольку в этом случае U 2, т. близко к нулевому значению.

Если произошла выработка директивы Заброковать партию, горит индикатор 115,тогда на индикаторах 117 высвечивается фактическое значение величины U. Оператор также имеет возможность численно проверить результат контроля. Кроме того, процесс контроля заблокирован путем подачи сигнала Лог.О с первого выхода 19 блока 7 отображения на 55 третий вход 18 блока 1 ввода данных. Повышение достоверности при входном контроле имеет существенное значение поскольку ошибка в выработке

45

50

определенных директив может привести к приемке партии, засоренной бракованными изделиями, и наоборот, забпо- кованкю партии, отвечаюгаей установленным требованиям.

Партии исделий могут содерх, тъ десятки тысяч изделий, что привести к неоправданн :м юльш м потерям, а на контрОлег я лолится ответственность,

Необчодямость отметить относительную простоту устройства, поскольку составление программы произвг т;1;тся на практически естественном языке, максималы о приближенном для по Г мг- нля не подготовленном пгчьзрвгтелем.

Формула и з о б р е т Р г и я

вым и вторым входами д шны б к-к отображения, вхпы Годен у Брак которого подключеьы к ОДНГЛМР -ШЫМ выходам блока принятия рогиепия. въ,- УОД общей блокировки работы jrrpofi- ствл - ч входам очоклрглки гк кя т,пр дарения и ело i ввода , выход ко rs при 1ЧТИЯ епе-шя бтока итс&- - к второму вход,, у на пителя, вторсч ВЬ УОД данных которо п ее единен с трггт им блока отображения.

j-строиттво гю п.

1

о г л и

f5

0

5

0

5

С

5

0

5

чан,щееся тем. t o блок принятая решений содрр-тт летвый и второй одковипра ы, 1 с.зыи TI второй D-триг- геры, с первс го п чстьертый элементы 2К, вл-гдь: сбрс:а Ь-трип еров и рыходы первого v третьего элементов 2И явля- отся гходсм Сотое и выходами Брак и Г ден Слока соответственно, гер- вье гходы первого ч второго элсме тоз 2И являются 1 1рвым стано оччим вчо- дгм устро гсзяач которы: через первый одноБиоратор соединен с устано; вхг дом первого D-триггера, , ; син- хроь зации и xo/fOM дгнньх подключенного соответственно к вы,оду второго элемента 2И и к шине нулевогс потенциала устройства, второй вгод ьтгро- го ji первый вход чегвертог о эл ментов 2И являются входом Знак операнда блока, второй вход четвертого и первый вход третьего элементов 2И является втор / установочным входом устройства, который череч второй од- новибратор подклн.чеч к гстановочному входу второго D-триггера, синхровуо- дом и входом данным подкпюченчого соотретственно к выходу ;етзер эго элемента 2И и к шине рулевого потеь- циала устройства, выходы первого и второго ti-григгеров ссепинены сопт- ьетственг о с вторыми входсччи первого и третьего элементов 2И.

и первый вход третьего элемента 2ИЛИ являются установочным, кода параметра, блокировки и Общий сброс входами блока соответственно, выход третьего дешифратора, выход первого элемента 2И-2И-ИЛИ, первый и второй выходы дешифратора, выход элемента 2И-НЕ являются первым и вторым выходами данных, первым и вторым уста- новочным и стробирующим выходами блока соответственно, выход RS-триг- гера соединен с первым входом первого элемента 2И, выходом подключенног к первому входу двоичного счетчика и через элемент задержки - к вторым входам второго элемента 2И-2И-ИЛИ и к первому входу элемента , второй вход которого и третий вход второго элемента 2И-2И-ИЛИ подключены к выходу второго элемента 2ИЛИ, выход третьего элемента 2ИЛИ соединен с первым входом второго элемента 2ИЛИ и с входом сброса двоичного счетчика выкод элемента НЕ подключен к вто- рому входу элемента 2ИЛИ, выходом соединенного с входом Сброс RS-три гера, выходы двоичного счетчика соединены с адресными входами узла по-1 стоянкой памяти, выходами подключенного к первой группе входов первого элемента 2И-2И-ИЛИ, к входам данных дешифраторов с первого по третий, выходы преобразователя кодов соеди- динены с второй группе входов первого элемента 2И-2И-ИЛИ, первый выход первого дешифратора соединен с первым входом первого элемента 2ИЛИ и с первым входом первого элемента 2И,-2И-ИЛИ, второй выход первого дешифратора соединен с вторым входом второго элемента 2ИЛИ, с вторым входом первого элемента 2И-2И-ИЛИ, с входом стробирования третьего дешифратора, третий выход первого дешифратора соединен с четвертым входом второго элемента 2И-2И-ИЛИ и с первым входом второго элемента 2И, выходом соединенного со стробирующим входом второго дешифратора, третьим выходом подключенного к второму входу третьего элемента 2ИЛИ, выход второго элемента 2И-2И-ИЛИ через одновибрато соединен с вторыми входами первого и второго элементов 2И.

52

l-ver

ы

Фиё.2

22

67

SO

&

Фиг.З

Фю.4

32

96 97

Фаг. 5

96

§if

дъпф

9

Ј2

иЛ.

CIC6I9I

| Устройство для входного контроля | 1985 |

|

SU1298769A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 562827, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-01-07—Публикация

1989-02-23—Подача