со

4

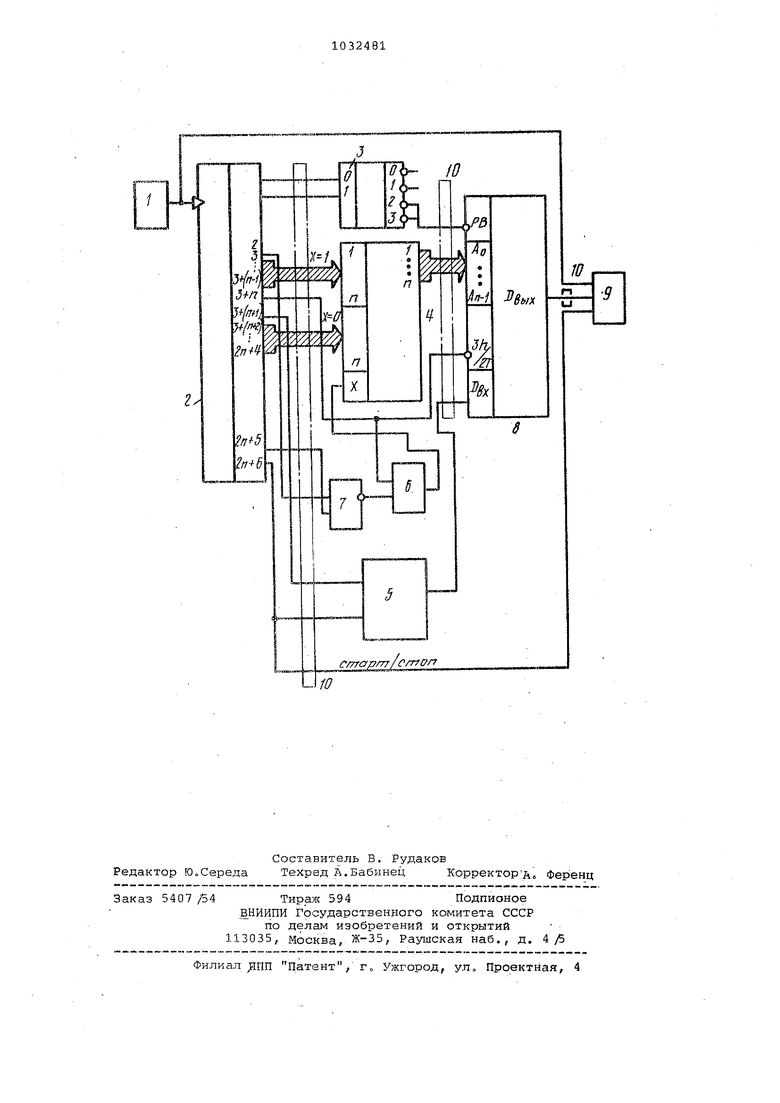

оо Изобретение относится к вычислительной технике и может быть исполь зовано для функционального контроля как отдельных корпусов микросхем оперативных запоминающих устройств (ОЗУ), так и посторонних на их основе массивов полупроводниковых ОЗУ произвольной емкости и организации. Известны устройства для контроля полупроводниковой памяти, содержащее генератор тактовых импульсов, генератор тестовой , блок фор мирования временной диаграммы, комI паратор, адресный мультиплексор, накопители и блок управления Недостатками этого устройства являются большие аппаратурные затра ты и невысокое быстродействие. Наиболее близким к предлагаемому является устройство для контроля полупроводниковой памяти, содержащее генератор синхросигналов, выход которого подключен к входу анализатора сигналов, второй вход кото рого является входом устройства, мультиплексор, выход которого,является одним из вьхходов устройства, да шифратор, сумматоры по модулю два и счетчик, вход которого подключен к выходу генератора синхросигналов, а выходы соединены соответственно с входами дешифратора, одними из входов мультиплексора, входами суммато ров по модулю два и третьим входом анализai;opa сигналов, выход одного из сумматоров по модулю два соедине . с другим входом мультиплексора, оди из выходов дешифратора и выходы сум 1аторов по модулю два другШЛи выходами устройства 2, Недостатком данного устройства является невысокая достоверность контроля,, поскольку при контроле не учитываются все состояния тестируемой микросхемы. Это cHi-скает надежность устройства Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем, что в устройство для контроля полупроводниковой памяти, содержащее генератор тактовых импульсов, дешифратор, анализатор сигналов, су матор по моду.гао два, мультиплексор и счетчик импульсов, одни из входов которого подключены соответственно входам дешифратора, одним из входов мультиплексора, входам сумматора по модулю два « первому входу анализатора сигналов, второй вход которого и вход счетчика импульсов соединены с выходами генератора тактовых импульсов, причем выходы дешифратора, мультиплексора и сумматора по модул два -являются одними из выходов устройства, входом которого являетс третий вход анализатора сигналов, введены элемент И-НЕ и элемент И, первый вход которого и входы элемента И-НЕ подключены соответственно к другим выходам счетчика, выход элемента И соединен с другим входом мультиплексора, второй вход - с выходом элемента И-НЕ,а первый вход элемента И соединен с другим выходом устройства. На чертеже изображена функциональная схема предлагаемого устройств.а. Устройство содержит генератор 1 тактовых импульсов, выход которого соединен с входом двоичного счетчика 2 импульсов с количеством разрядов ( 2п + 6) (п - количество сццресных входов контролируемой большой интегральной схемы (БИС) ОЗУ, который своими выходами подключен к дешифратору 3 (2- 4), к мультиплексору 4 ( 2п - п) , к сумматору 5 по модулю два, входу двухвходового элементаи б, а также к элементу И-НЕ 7. Выходы дешифратора 3, мультиплексора 4, счетчика 2 и сумматора 5 являются выходами устройства, к которым подключается контролируемая БИС ОЗУ 8. Устройство также содержит анализатор 9 сигналов, в качестве которого используется сигнатурный анализатор. Конструктивно устройство может быть выполнено так, что БИС ОЗУ 8 соединяется с элементами устройства и анализатором 9 с помощью интерфейсной коммутационной матрицы 10 различной для различных цоколевок корпусов (показанной пунктиром). Устройство работает следующим образом. Генератор1 запускает счетчик 2, который, работая в режиме непрерывного пересчета, с помощью выходов разрядов О и 1 и дешифратора 3 вырабатывает следующие друг за другом сигналы дешифрируемых статусов О , 2, 3 длительностью по такту { периоду) синхросигнала и имеющихактивным нулевое значение . Один из этих сигналов - стаиспользуется в качестве сигнала разрешения выборки контролируемой БИС ОЗУ 8. Такое формирование сигнала разрешения выборки гарантирует , что его переключения имеют место внутри сигналов Чтение/запись Вход данных, и, что самое главное, после переключения адресов. Выходы .разрядов 3,..., 3 + ( п - 1) счетчика 2 - низкочастотная адресная группа к (п + 5),..., (2п + 4) - высокочастотная адресная группа счетчика 2 подключаются соответственно к двум группам по п входов мультиплексора 4.. .Мультиплексор4 при нулевом состоянии управляющего входа (, передает на вход БИС ОЗУ 8 высокочастотную адресную группу разрядов (п + 5 , ( п + б),..., (2п + 4 счет чика 2, а при - низкочастотную адресную группу разрядов 3, 4, ... , (п + 2) счетчика 2. Разряд счетчика 2 (3 + п), являющийся сигналом стимуляции входа Запись /Чтение БИС ОЗУ 8, осуществляет помиМО своей основной задачи (формирова ние режима записи или чтейия для БИС ОЗУ 8 еще и вспомогательную управление коммутацией на адресные входы БИС ОЗУ 8 двух групп адресных сигналов, получаемых от счетчика 2. Первая, высокочастотная адресная Группа (в том смысле, что ее раэряды переключаются более часто, нежели разряд стимуляции входа Запись /1те ние) коммутируется на входы БИС ОЗУ 8 уровнем Чтение. Это-означает, 1то пока имеет место уровень Чтение будут перебраны все адреса БИС ОЗУ 8 и по всем адресам будет считана информация в порядке возрастания адресов, начинай с нулевого. Вторая, низкочастотная адресная груп па (в том смысле, что ее разряды . переключаются менее часто, нежели разряд стимуляции входа Запись /1тение) коммутируется на входы уровнем Запись. Указанным способом и реализуется необходимая для данного теста ситуация:запись информации,име щейся в данный момент на входе данных по одному текущему адресу и чтение фоновой (а также и текущей) информации по всем адресам БИС ОЗУ 8. Необходимо здесь пояснить, что поскольку длительность сигнала дение равна длительности сигнала Запись будет ipoBHO, столько сигналов разрешения выборки, сколько адресов имеет БИС ОЗУ 8. Однако для реализащ и тес та типа Галоп, необходимо обеспечит .считывание фоновой информации не под ряд, начиная с нулевого адреса, а галопирующим образом, т.е. считывание текущей ячейки, затем следующей за ней, вновь текущей, следующей через одну за ней и т.д. Для этого сигнал Запись Чтение с выхода счетчика 2 подается на вход мультиплексора 4 и непосредственно, а через элемент И б, который при участии элемента 7 и обеспечивает на фоне сигнаша Чтение на входе мультиплексора 4 соответствующие переключения. Сигналы с разрядов (п + 4) и(2п + 6) подаются на выходы сумматора 5, выход которого стимулирует вхоД данных БИС ОЗУ 8. Это позволяет в первой половине теста менять данные с нуля на единицу, тогда как во второй - с единицы на нуль. Сигнал с выхода контролируемой БИС ОЗУ 8- подается на третий информационный вход используемого в качестве анализатора 9 сигналов сигнатурного анализатора, первый вход (вход Старт / стоп) которого управляется от старшего разряда счетчика 2, а-второй вход (синхровход получает сигналы синхронизации от генератора 1 тактовых импульсов. Использование сигнатурного анализатора обеспечивает возможность контроля . выходных реакций БИС ОЗУ В- не только во время считывания, но что особенйо существенно, .при всех возможных состояниях таблицы истинности БИС ОЗУ -8, а именно, при запрете чтения, при запрете записи, при разрешении записи. Это обусловлено тем, что прием всех реакций в сигнатурный анализатор производится по каждому без исключения синхросигналу генератора 1.,Поэтому за время каждого адреса будет принята с определенной избыточностью выходная реакция при запрете записи, при разрешении записи, при запрете чтения и при разрешении чтения. Имеющая место избыточность особого значения не имеет в связи с применением сигнатурного анализа, обеспечивающего сжатие двоичной информации произвольной длины с весьма высокой достоверностью. Примен ение. предлагаемого устройства позволяет повысить достоверность контроля .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативной памяти | 1982 |

|

SU1053164A1 |

| Устройство для контроля полупроводниковой памяти | 1982 |

|

SU1070607A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1053165A1 |

| Устройство для контроля полупроводниковой памяти | 1981 |

|

SU968856A1 |

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705874A1 |

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| Устройство для контроля оперативной памяти тестом Марш с двоично-нарастающим адресным шагом | 1986 |

|

SU1532978A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1705875A1 |

| Устройство для контроля микросхем оперативной памяти | 1983 |

|

SU1149312A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОЛУПРОВОДНИКОВОЙ ПШЯТИ, содержащее генератор тактовых импульсов, дешифратор, анализатор сигналов, сумматор по модулю два, мультиплексор и счетчик импульсов, одни из входов которого подключены соответственно к входам дешифратора, одним из входов мультиплексора,(входам сумматора по модулю два и первому входу анализатора сигналов, второй вход которого и входсчетчика импульсов соединены с выходом генератора тактовых импульсов, причем выходы дешифратора, мультиплексора и сумматора по модулю два являются одними из выходов устройства, входом которого является третий вход анализатора сигналов, отличающеес я тем, что, с целью повышения надежности устройства, в него введены элемент Н-НЕ и элемент И, первый вход которого и входы элемента И-НЕ подклкхчены соответственно к другим выходам счетчика, выход элемента И соединен с другим входом I мультиплексора, второй вход с (Л выходом элемента И-НЕ, а первый вход элемента И соединен с другим с: выходом устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля полупроводниковой памяти | 1978 |

|

SU771730A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3242717/18-24, кЛ | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-07-30—Публикация

1982-04-07—Подача