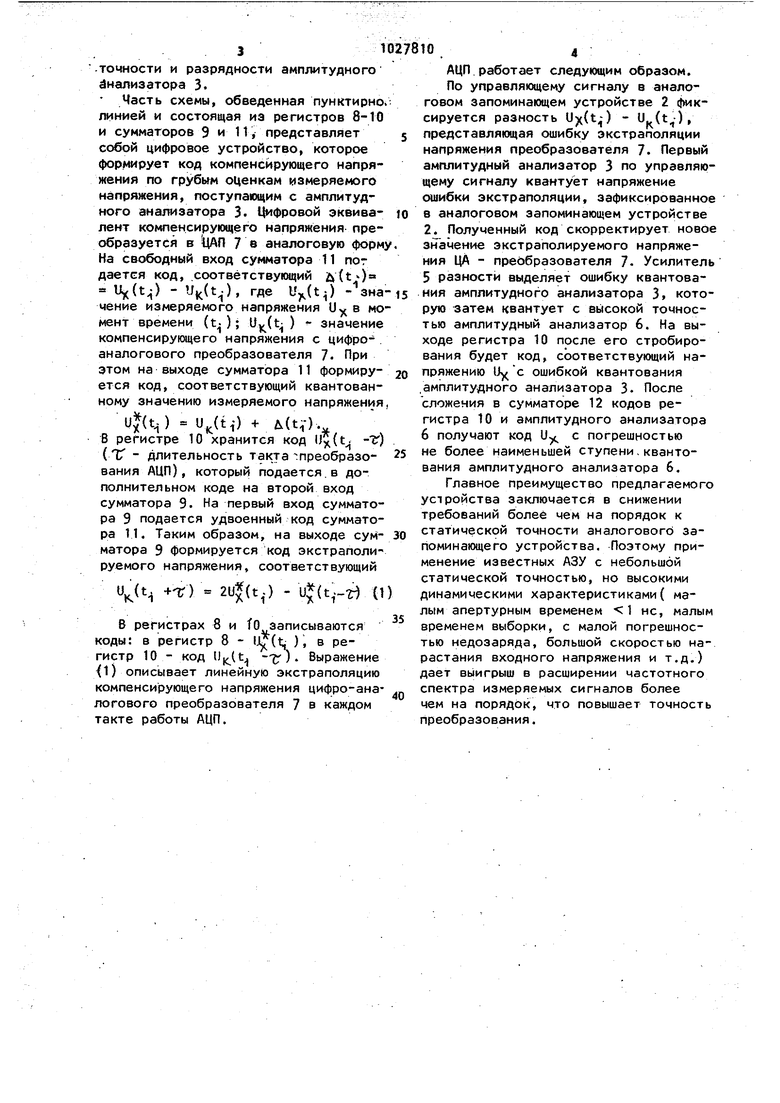

11 Изобретение относится к измерител ной и вычислительной технике и используется для получения количествен ной информации о .быстропротекающих процессах. Известен аналого-цифровой преобра йователь (АЦП) с аналоговым запомина ющим устройством (АЗУ) поразрядного уравновешивания с двухступенчатой по следовательной коррекцией динамической погрешности, который состоит из АЗУ,. сравнивающего устройства, цифро аналогового преобразователя (ЦАП), двух источников образцового напряжения, -триггерных регистров и схемы управления. Принцип работы АЦП основан на фиксации мгновенного значения измеряемого напряжения и его поразрядного уравновешивания, причем схема коррекции дин-амической погрешност сокращает время преобразования в 2,7 раза {1 . . Известен аналого-цифровой преобразователь, содержащий аналоговое запоминаюа1ее устройство, первый амплитудный анализатор, цифро-аналого. вый преобразователь, усилитель разности, второй амплитудный анализатор 2 . Недостатком данных устройств является низкая точность преобразовани Цель изобретения - повышение точности преобразователя. Поставленная цель достигается тем что в аналого-цифровой преобразователь, содержащий аналоговое запоминающее устройство, выход которого со единен с первым входом первого усилителя разности и входом первого амп литудного анализатора, выход которого соединен с входом первого цифро-ана- логового преобразователя, выход :которого соединен с вторым входом первого усилителя разности, выход которого соединен с входом второго амплитудного анализатора, в него введен второй цифро-аналоговый преобразователь, второй усилитель разности, два регистра, три сумматора, первый вход первого из которых соединен с выходом первого амплитудного анализатора, а выход - с первым входом второго сумм .тора и входом первого регистра, первый выход которого соединен с первым входом третьего сумматора, а второй выход - с вторым входом второго сумматора, выход которого соединен с входом второго регистра, выход кото0рого соединен с вторым входом первого сумматора и входом второго цифро-аналогового преобразователя, выход которого соединен с первым входом второго усилителя разности, второй вход которого соединен с входной шиной, а выход - с входом аналогового запоминающего устройства, при этом второй вход третьего сумматора соединен с выходом второго амплитудного анализатора. На чертеже представлена структурная схема предлагаемого аналого-цифрового преобразователя. Устройство содержит .усилитель 1 разности, аналоговое запоминающее устройство 2, первый амплитудный анализатор 3 первый цифро-аналоговый преобразователь 4, усилитель 5 разности, второй амплитудный анализатор 6, второй цифро-аналоговый преобразователь 7, второй регистр 8, сум матор 9| первый регистр 10, сумматоры 11 и 12. К первому входу усилителя 1 разности подключено измеряемое напряжение DX, к второму - выход цифро-аналогового преобразователя 7, выход усилителя 1 разности через аналоговое запоминающее устройство 2 соединен с входом амплитудного анализатора 3 и первым входом усилителя 5 разности, выход которого через второй амплитудный анализатор 6 соединен с первым входом сумматора 12, второй вход которого подключен к второму выходу регистра 10, выход первого амплитудного анализатора 3 соединен с первым входом сумматора 11, выход которого подключен к первому входу сумматора 9 и входу регистра 10, первый выхрд которого подключен к второму входу сумматора 9, выход которого подключен к входу регистра 8, выход которого соединен с входом цифро-аналогового преобразователя 7. Амплитудные анализаторы 3 и 5 имеют уровни квантования, распределенные по равномерному закону Iq., 2q, nq ., где q - наименьшая ступень, квантования соответствующего амплитудного анализатора. Точность цифро-аналогового преобразователя 7 соответствует числу разрядов АЦП, хотя число разрядов самого ЦАП преобразователя 7 может быть значительно меньше числа разрядов АЦП. Точность и число разрядов цифротаналогового преобразователя k соответствует -ТОЧНОСТИ и разрядности амплитудного ёнализатора 3. Часть схемы, обведенная пунктирно линией и состоящая из регистров 8-10 и сумматоров 9 и 11, представляет собой цифровое устройство, которое формирует код компенсирующего напряжения по грубым оценкам измеряемого напряжения, поступающим с амплитудного анализатора 3. Цифровой эквивалент компенсирующего напряжения преобразуется в ЦАП 7 в аналоговую форм На свободный вход сумматора 11 по дается код, .соответствующий u(t) U(t) - ..), где Uy(t) чение измеряемого напряжения Uv в мо мент времени (t); U(t ) значение компенсирующего напряжения с цифроаналогового преобразователя 7. При этом на выходе сумматора 11 формируется код, соответствующий квантованному значению измеряемого напряжения uj() ujti) + (tv).« В регистре 10 хранится код U(t -т) ( ТГ - длительность такта :преобразования АЦП), который подается.в дополнительном коде на второй вход сумматора 9. На первый вход сумматора 9 подается удвоенный код сумматора 11. Таким образом, на выходе сумматора 9 формируется код экстраполируемого напряжения, соответствующий U(t. +-Г) 2uJ{t.) - Uj( (1 В регистрах 8 и fO записываются коды: в регистр 8 - ( ), в № ). реti -г). гистр 10 - код Л Выражение (1) описывает линейную экстраполяцию компенсирующего напряжения цифро-аналогового преобразователя 7 в каждом такте работы АЦП. 1 104 АЦП.работает следующим образом. По управляющему сигналу в аналоговом запоминающем устройстве 2 фиксируется разность Uj((t) - U.(), представляющая ошибку экстраполяции напряжения преобразователя 7. Первый амплитудный анализатор 3 по управляющему сигналу квантует напряжение ошибки экстраполяции, зафиксированное в аналоговом запоминающем устройстве 2. Полученный код скорректирует новое значение экстраполируемого напряжения ЦА - преобразователя 7- Усилитель 5разности выделяет ошибку квантования амплитудного анализатора 3, которую затем квантует с высокой точностью амплитудный анализатор 6. На выходе регистра 10 после его стробирования будет код, соответствующий напряжению Цу с ошибкой квантования /амплитудного анализатора 3. После сложения в сумматоре 12 кодов регистра 10 и амплитудного анализатора 6получают код U с погрешностью не более наименьшей ступени,квантования амплитудного анализатора 6. Главное преимущество предлагаемого устройства заключается в снижении требований более чем на порядок к статической точности аналогового запоминающего устройства. Поэтому применение известных АЗУ с небольшой статической точностью, но высокими динамическими характеристиками( малым апертурным временем 1 не, малым временем выборки, с малой погрешностью недозаряда, большой скоростью нарастания входного напряжения и т.д.) дает вь1игрыш в расширении частотного спектра измеряемых сигналов более чем на порядок, что повышает точность преобразования.

УК

ммм

UK

| название | год | авторы | номер документа |

|---|---|---|---|

| Фотоэлектрический анализатор количества и размеров частиц | 1987 |

|

SU1518727A1 |

| Способ аналого-цифрового преобразователя и устройство для его осуществления | 1985 |

|

SU1305848A1 |

| Интерполирующий фильтр | 1982 |

|

SU1100715A1 |

| Статистический анализатор конечной разности фазы сигнала | 1988 |

|

SU1538143A2 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1378061A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1181144A1 |

| Следящий аналого-цифровой преобразователь | 1985 |

|

SU1361713A1 |

| Устройство аналого-цифрового преобразования | 1988 |

|

SU1501268A2 |

| СПОСОБ ОПРЕДЕЛЕНИЯ АМПЛИТУДЫ ИМПУЛЬСОВ И ИЗМЕРИТЕЛЬ ЕГО РЕАЛИЗУЮЩИЙ (ВАРИАНТЫ) | 2021 |

|

RU2773621C1 |

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1398093A1 |

АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий аналоговое запоминающее устройство, выход которого соединен с первым входом первого.усилителя разности и входом первого амплитудного анализатора, выход которого соединен с входом первого цифро-аналогового преобразователя, выход которого соединен с вторым входом первого усилителя разности, выход котоВСЕГОШ31ДЯ I рого соединен с входом второго амплитудного анализатора, о т л и ч а iro щ и и с я тем, что, с целью повышения точности преобразователя, в него введены -второй цифро-аналоговый преобразователь, второй усилитель разности, два регистра, три сумматора, первый вход первого из которых соединен с выходом первого амплитудного анализатора, а выход - с первым входом второго сумматора и входом первого регистра, первый выход которого соедин1ен с первым входом третьего сумматора, а второй выход - с вторым входом второго сумматора, выход которого соединен с входом второго реQ S гистра, выход которого соединен с вторым входом первого сумматора и вхоО) дом второго цифро-аналогового преобразователя , выход которого соединен с первым входом второго усилителя разности, второй вход которого соединен с входной шиной, а выход - с входом аналогового запоминающего устройства, о ю при этом второй вход третьего сумматора соединен с выходом второго амплитудного анализатора. X)

10 «J

Авторы

Даты

1983-07-07—Публикация

1981-12-18—Подача