1

1

Изобретение относится к информационно-измерительной технике и может быть использовано в устройствах прецизионного преобразования аналоговых сигналов в код.

Цель изобретения - повышение точности преобразования.

Способ предусматривает выполнение следующей последовательности операций. После фиксации мгновенного значения входного сигнала в аналоговом дискретизаторе, параллельно, первая и вторая ступени производят прямое преобразование соответствующих сигналов. Первая ступень кодирует старшие разряды, вторая - суммарную систематическую ошибку. Во время обратного преобразования старших разрядов производится обратное преобразование систематических ошибок. Получившиеся аналоговые эквиваленты одновременно поступают на вход второй ступени. Младшие разряды кодируются из разностного сигнала, включающего эквивалент старших разрядов, сигнал анало- 25 преобразования кода младших разрядов

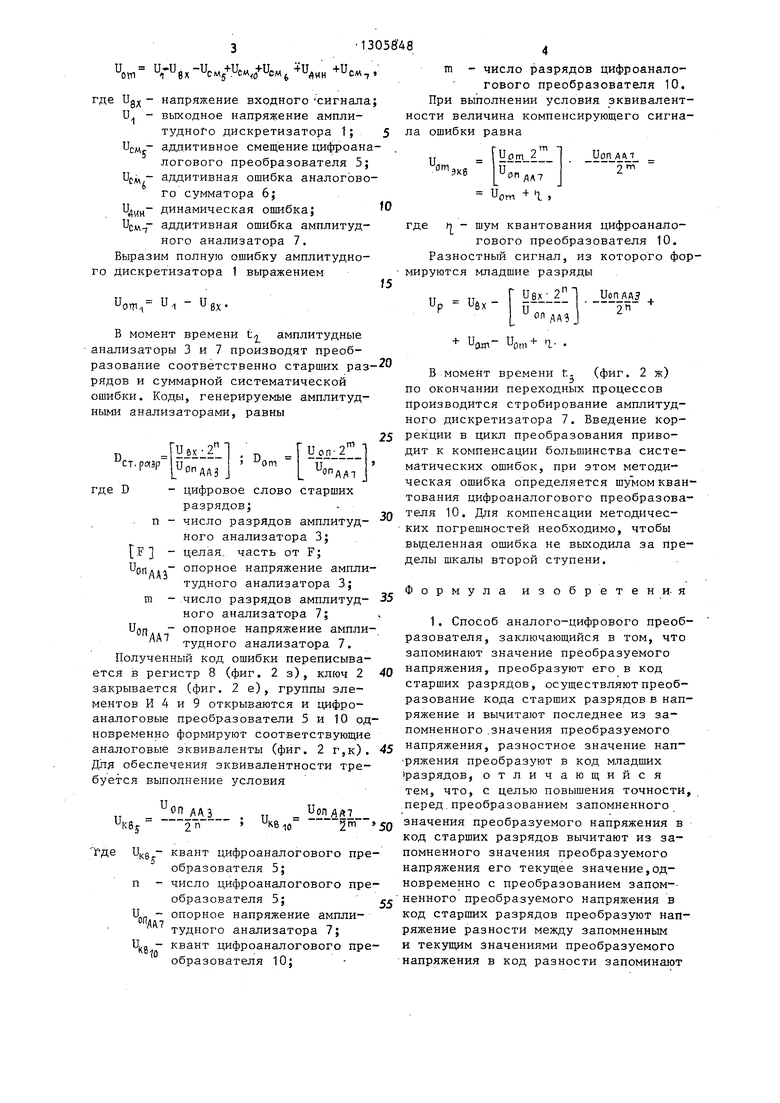

входного сигнала амплитудным анализатором 7) в момент времени с группы элементов И 4 и 9 закрываются, а ключ 2 открывается (фиг. 2 в, и, д). Пос- 3Q ле выборки мгновенного значения входного сигнала амплитудным дискретизатогового дискретизатора и эквивалент систематических ошибок. По окончании кодирования младших разрядов обратные преобразователи приводятся к нулевому значению подачей на их входы нулевых кодов, а к входу второй ступени коммутируется входной сигнал.

Таким образом, после фиксации мгновенного значения входного сигнала в аналоговом дискретизаторе на входе второй ступени формируется разностный сигнал, который является функцией приведенных к входу второй ступени систематических ошибок преобразоваром 1 в момент времени t на вход па35

раллельного сумматора 6 поступает входной сигнал, коммутируемы ключом 2, выходное напряжение амплитудного дискретизатора 1, выходные напряжения цифроаналоговых преобразователей 5 и 10 в этом случае близки к нулю и равны аддитивным ошибкам смещения. По теля для данного периода преобразова- Q окончании переходных процессов в циф- ния входного сигнала.роаналоговых преобразователях ключа.

Введенная процедура позволяет исключить суммарную ошибку амплитудного дискретизатора, суммарную аддитивную ошибку второй ступени (аддитив- ное смещение усилителя разности и смещения амплитудного анализатора), аддитивные ошибки обратных преобразоамплитудном дискретизаторе и аналоговом сумматоре на его выходе появляется сигнал, пропорциональный суммарной систематической ошибке. В ее состав также входит и динамическая ошибка от изменения входного сигнала между моментом стробирования аналогового дискретизатора и моментом стробировавателей старших разрядов и систематических ошибок. Кроме того, компен- п ния амплитудных анализаторов Зи 7

сируется динамическая опшбка измерения, связанная с тем, что между моментом фиксации мгновенного значения входного сигнала в дискретизаторе и моментом ц;ифрового преобразования суммарной ошибки имеется конечное время, в течение которого входной сигнал может изменяться на некоторую величину. Иными словами преобразова55

(фиг. 2 е). Интервал времени межд этими стробирующими импульсами, следовательно, и величина динамич кой ошибки определяются динамичес характеристиками аналогового диск тизатора и аналогового сумматора.

Суммарная ошибка в формализова ном виде может бь.:ть представлена ражением

13058 8 тель измеряет мгновенное значение входного сиг нала, зафиксированное не в момент выборки аналоговым дискрети- затором, а в момент кодирования суммарной систематической ошибки.

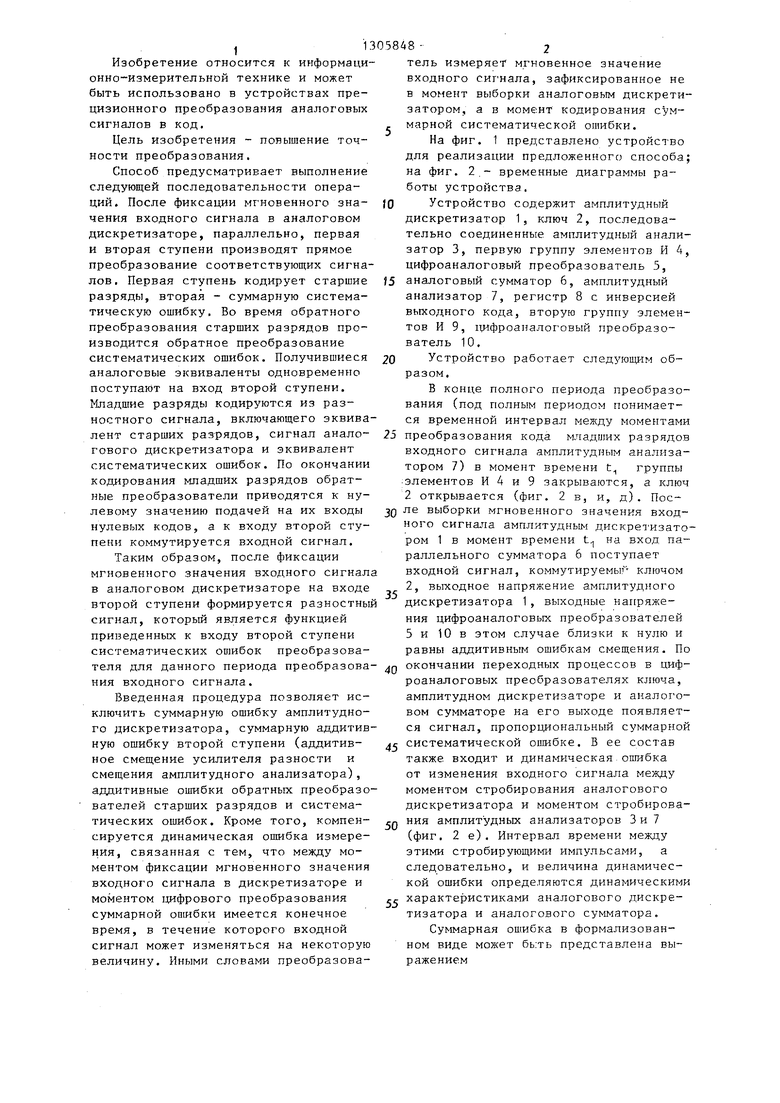

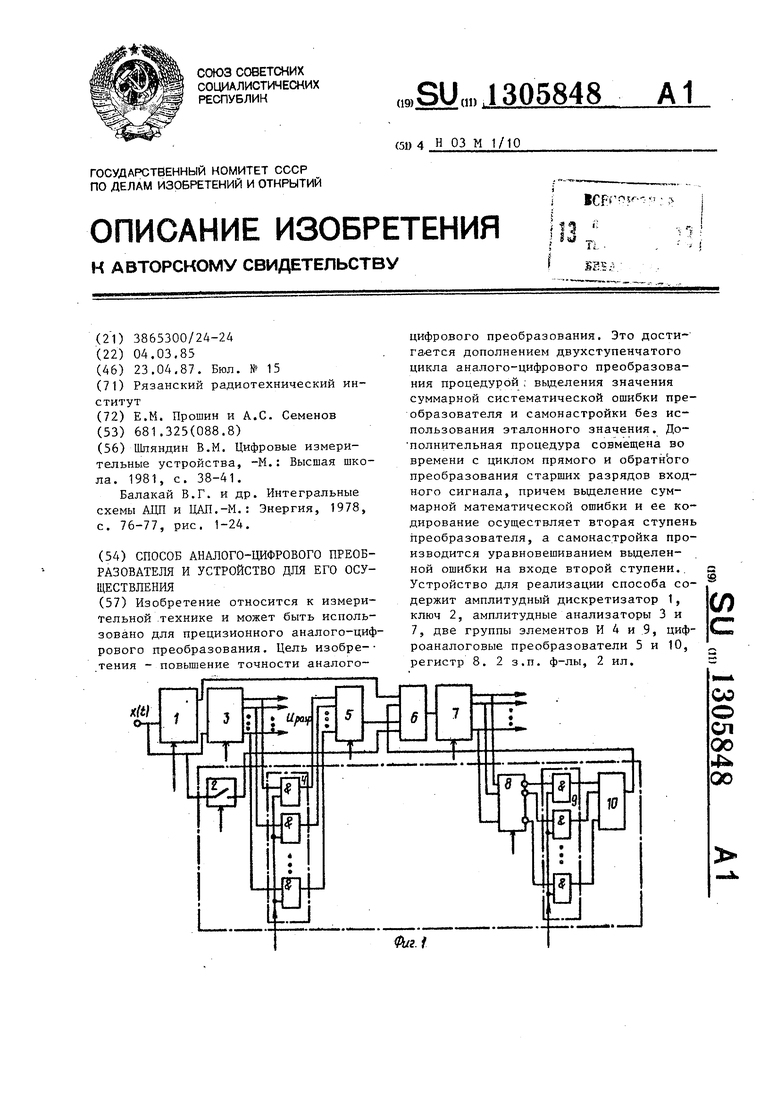

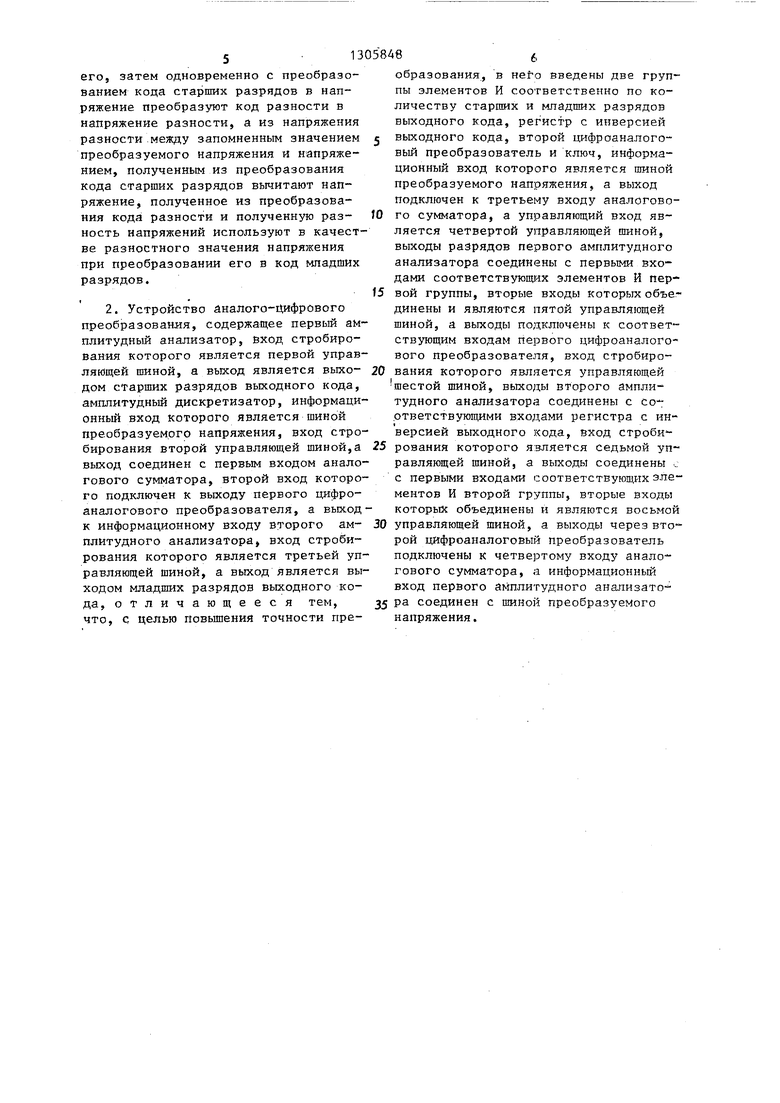

На фиг. 1 представлено устройство для реализации предложенного способа; на фиг. 2,- временные диаграммы работы устройства.

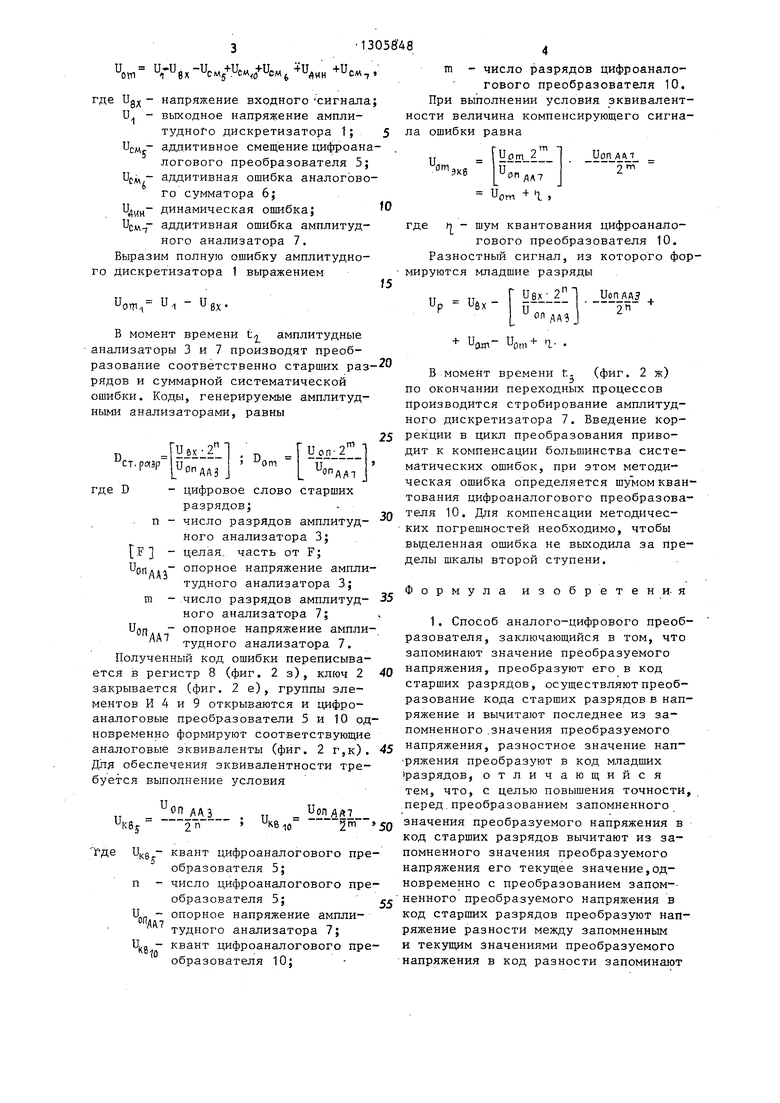

Устройство содержит амплитудный дискретизатор 1, ключ 2, последовательно соединенные амплитудный анализатор 3, первую группу элементов И 4, цифроаналоговый преобразователь 5,

аналоговый сумматор 6, амплитудный анализатор 7, регистр 8 с инверсией выходного кода, вторую группу элементов И 9, цифроаналоговый преобразователь 10.

Устройство работает следующим образом.

В конце полного периода преобразования (под полным периодом понимается временной интервал между моментами

ром 1 в момент времени t на вход параллельного сумматора 6 поступает входной сигнал, коммутируемы ключом 2, выходное напряжение амплитудного дискретизатора 1, выходные напряжения цифроаналоговых преобразователей 5 и 10 в этом случае близки к нулю и равны аддитивным ошибкам смещения. По окончании переходных процессов в циф- роаналоговых преобразователях ключа.

амплитудном дискретизаторе и аналоговом сумматоре на его выходе появляется сигнал, пропорциональный суммарной систематической ошибке. В ее состав также входит и динамическая ошибка от изменения входного сигнала между моментом стробирования аналогового дискретизатора и моментом стробирова

(фиг. 2 е). Интервал времени между этими стробирующими импульсами, а следовательно, и величина динамической ошибки определяются динамическими характеристиками аналогового дискретизатора и аналогового сумматора.

Суммарная ошибка в формализованном виде может бь.:ть представлена выражением

Uom .-UcM,.,-bUcM U,, +UeM,,

напряжение входного сигнала; U - выходное напряжение амплитудного дискретизатора 1; 5 UcMr аддитивное смещение цифроаналогового преобразователя 5; UCM, аддитивная ошибка аналогового сумматора 6;

динамическая ошибка; cw-f аддитивная ошибка амплитудного анализатора 7. Вьфазим полную ошибку амплитудноДискретизатора 1 выражением

15

УОШГ Ui - и

8Х

В момент времени i, амплитудные анализаторы 3 и 7 производят преобразование соответственно старших разрядов и суммарной систематической ошибки. Коды, генерируемые амплитудными анализаторами, равны

D

iU6x-2

Uon

D

От

I

Пл

m -I

30

F -

ААЗ JL

де D- цифровое слово старших

разрядов;

п - число разрядов амплитудного анализатора 3; целая, часть от F; опорное напряжение амплитудного анализатора 3; m - число разрядов амплитуд- 35 ного анализатора 7; опорное напряжение амплитудного анализатора 7. Полученный код ошибки переписыватся в регистр 8 (фиг. 2 з), ключ 2 40 акрывается (фиг. 2 е), группы элеентов И 4 и 9 открываются и цифро- налоговые преобразователи 5 и 10 рди,

оп

АА7

1. Способ аналого-цифрового прео разователя, заключаюш,ийся в том, чт запоминают значение преобразуемого напряжения, преобразуют его в код старших разрядов, осуществляют преоб разование кода старших разрядов в нап ряжение и вычитают последнее из за помненного .значения преобразуемого

новременно формируют соответствующие

аналоговые эквиваленты (фиг. 2 г,к). 45 напряжения, разностное значение нал

Для обеспечения эквивалентности требуется выполнение условия

ряжения преобразуют в код младших разрядов, отличающийся тем, что, с целью повышения точности перед.преобразованием запомненного ,Q значения преобразуемого напряжения в код старших разрядов вычитают из запомненного значения преобразуемого напряжения его текущее значение,одновременно с преобразованием запом-- ненного преобразуемого напряжения в код старших разрядов преобразуют нап ряжение разности между запомненньм и текущим значениями преобразуемого напряжения в код разности запоминают

и

jiil 2п

1о

Н.1ЛА7.

икбг квант цифроаналогового преобразователя 5;

п - число цифроаналогового преобразователя 5;55

Upj - опорное напряжение амплитудного анализатора 7;

U(g - квант цифроаналогового преобразователя 10;

,Q

m - число разрядов цифроаналогового преобразователя 10, При выполнении условия эквивалентности величина компенсирующего сигнала ошибки равна

и.

от

ЭКб

где h - шум квантования цифроаналогового преобразователя 10. Разностный сигнал, из которого формируются младшие разряды

Up Ufcx Uex- 2 иопддз

om oni

on AASJ + . .

2П

О

25

30

35 40В момент времени t, (фиг, 2 ж) по окончании переходных процессов производится стробирование амплитудного дискретизатора 7. Введение коррекции в цикл преобразования приводит к компенсации большинства систематических ошибок, при этом методи- ческая ошибка определяется шумом квантования цифроаналогового преобразователя 10. Для компенсации методических погрешностей необходимо, чтобы выделенная ошибка не выходила за пределы шкалы второй ступени.

Формула изобретен и. я

1. Способ аналого-цифрового преобразователя, заключаюш,ийся в том, что запоминают значение преобразуемого напряжения, преобразуют его в код старших разрядов, осуществляют преобразование кода старших разрядов в напряжение и вычитают последнее из за помненного .значения преобразуемого

напряжения, разностное значение нал

ряжения преобразуют в код младших разрядов, отличающийся тем, что, с целью повышения точности, перед.преобразованием запомненного значения преобразуемого напряжения в код старших разрядов вычитают из запомненного значения преобразуемого напряжения его текущее значение,одновременно с преобразованием запом-- ненного преобразуемого напряжения в код старших разрядов преобразуют напряжение разности между запомненньм и текущим значениями преобразуемого напряжения в код разности запоминают

его, затем одновременно с преобразованием кода старших разрядов в напряжение преобразуют код разности в напряжение разности, а из напряжения разности между запомненным значением преобразуемого напряжения и напряжением, полученным из преобразования кода старших разрядов вычитают напряжение, полученное из преобразования кода разности и полученную разность напряжений используют в качестве разностного значения напряжения при преобразовании его в код младших разрядов.

f5 вой группы, вторые входы которых объединены и являются пятой управляющей шиНой, а выходы подключены к соответствующим входам первого цифроаналого- вого преобразователя, вход стробиротудного анализатора соединены с со- ртветствующими входами регистра с инверсией выходного кода, вход строби2. Устройство аналого-цифрового преобразования, содержащее первый амплитудный анализатор, вход стробиро- вания которого является первой управляющей шиной, а выход является выхо- 20вания которого является управляющей дом старших разрядов выходного кода, шестой шиной, выходы второго ампли- амплитудный дискретизатор, информационный вход которого является шиной преобразуемого напряжения, вход стробирования второй управляющей шиной,а 25рования которого является седьмой уп выход соединен с первым входом анало-равляющей шиной, а выходы соединены о гового сумматора, второй вход которо-с первыми входами соответствуюш,их эле- го подключен к выходу первого цифро-ментов И второй группы, вторые входы аналогового преобразователя, а выход-которых объединены и являются восьмой к информационному входу второго ам- 30управляющей шиной, а выходы через вто- плитудного анализатора, вход строби-рой цифроаналоговый преобразователь рования которого является третьей уп-подключены к четвертому входу анало- равляющей шиной, а выход является вы-гового сумматора, а информационный ходом младших разрядов выходного ко-вход первого амплитудного анапизато- да, отличающееся тем, 35Р соединен с шиной преобразуемого что, с целью повьш1ения точности пре-напряжения.

58А8,

образования, в Hefo введены две группы элементов И соответственно по количеству старших и младших разрядов выходного кода, регистр с инверсией

j выходного кода, второй цифроаналого- вый преобразователь и ключ, информационный вход которого является шиной преобразуемого напряжения, а выход подключен к третьему входу аналоговоfO го сумматора, а управляющий вход является четвертой управляющей шиной, выходы разрядов первого амплитудно1-о анализатора соединены с первьида входами соответствующих элементов И перf5 вой группы, вторые входы которых объединены и являются пятой управляющей шиНой, а выходы подключены к соответствующим входам первого цифроаналого- вого преобразователя, вход стробиро20вания которого является управляющей шестой шиной, выходы второго ампли- тудного анализатора соединены с со- ртветствующими входами регистра с инверсией выходного кода, вход стробивания которого является управляющей шестой шиной, выходы второго ампли-

рования которого является седьмой уп равляющей шиной, а выходы соединены о с первыми входами соответствуюш,их эле- ментов И второй группы, вторые входы которых объединены и являются восьмой управляющей шиной, а выходы через вто- рой цифроаналоговый преобразователь подключены к четвертому входу анало- гового сумматора, а информационный вход первого амплитудного анапизато- Р соединен с шиной преобразуемого напряжения.

uUoui dun

w разрядов

I Д «-гл

a ошибки

to f tz

7

Фиг. 2

Составитель В. Махнанов редактор Г. Гербер Техред А.Кравчук Корректор А. Зимокосов

Заказ 1А65/55 Тираж 902Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, А

3

LJ

Т

(период преобраэоЗаний)

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1987 |

|

SU1548845A2 |

| Цифроаналоговый преобразователь | 1988 |

|

SU1547069A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1983 |

|

SU1221751A1 |

| Преобразователь напряжения в код | 1980 |

|

SU961135A1 |

| Устройство цифроаналогового преобразования | 1987 |

|

SU1547067A1 |

| Двухдекадный двоично-десятичный цифроаналоговый преобразователь | 1987 |

|

SU1571764A1 |

| Цифроаналоговый преобразователь | 1987 |

|

SU1538254A1 |

| Устройство широкодиапазонного логарифмического аналого-цифрового преобразования | 1988 |

|

SU1571763A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1181144A1 |

Изобретение относится к измерительной технике и может быть использовано для прецизионного аналого-цифрового преобразования. Цель изобре-- тения - повышение точности аналогоцифрового преобразования. Это достигается дополнением двухступенчатого цикла аналого-цифрового преобразования процедурой ; выделения значения суммарной систематической ошибки преобразователя и самонастройки без использования эталонного значения, До- полнительная процедура совмещена во времени с циклом прямого и обратного преобразования старших разрядов входного сигнала, причем выделение суммарной математической ошибки и ее кодирование осуществляет вторая ступень преобразователя, а самонастройка производится уравновешиванием выделенной ошибки на входе второй ступени,. Устройство для реализации способа содержит амплитудный дискретизатор 1, ключ 2, амплитудные анализаторы 3 и 7, две группы элементов И 4 и 9, циф- роаналоговые преобразователи 5 и 10, регистр 8, 2 з,п, ф-лы, 2 ил. i (Л с со о СП 00 00

| Шпяндин В.М, Цифровые измерительные устройства, -М,: Высшая школа, 1981, с, 38-41, Балакай В,Г, и др | |||

| Интегральные схемы АЦП и ЦАП,-М,: Энергия, 1978, с, 76-77, рис, 1-24, |

Авторы

Даты

1987-04-23—Публикация

1985-03-04—Подача