1

1361

Изобретение относится к измери- тельной технике и предназначено для измерений амплитуд широкополосных динамических сигналов.

Цель изобретения - расширение диа пазона допустимых скоростей измене- НИН входного сигнала.

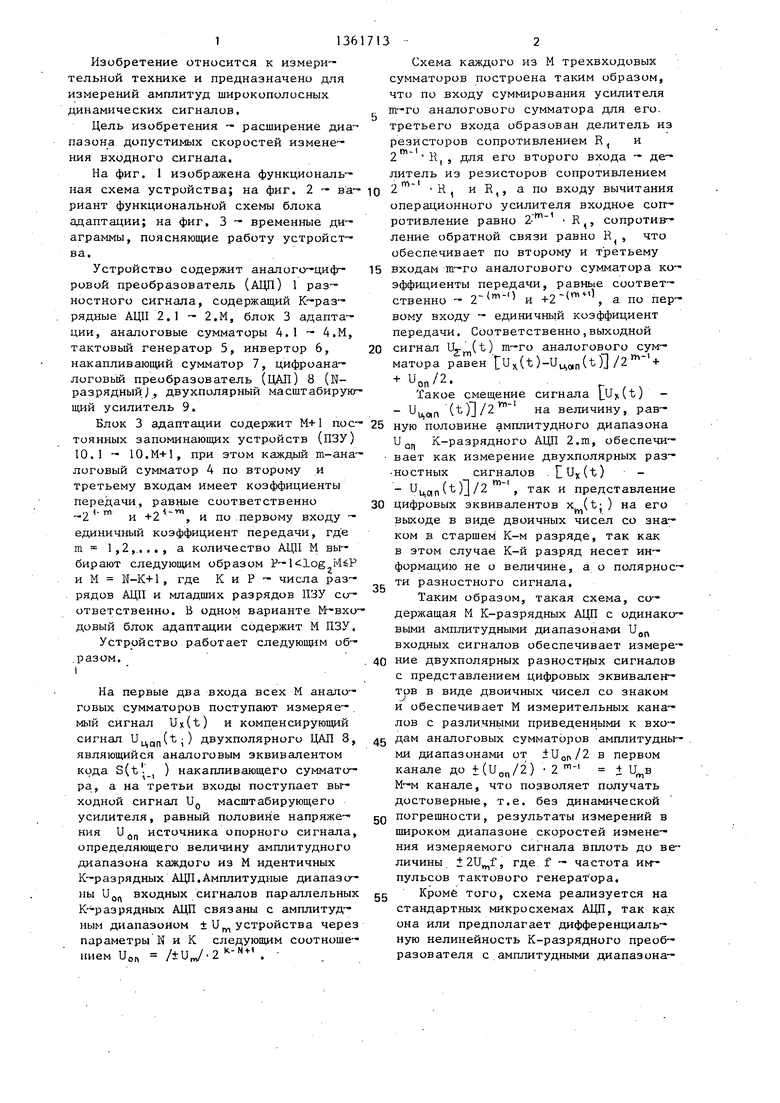

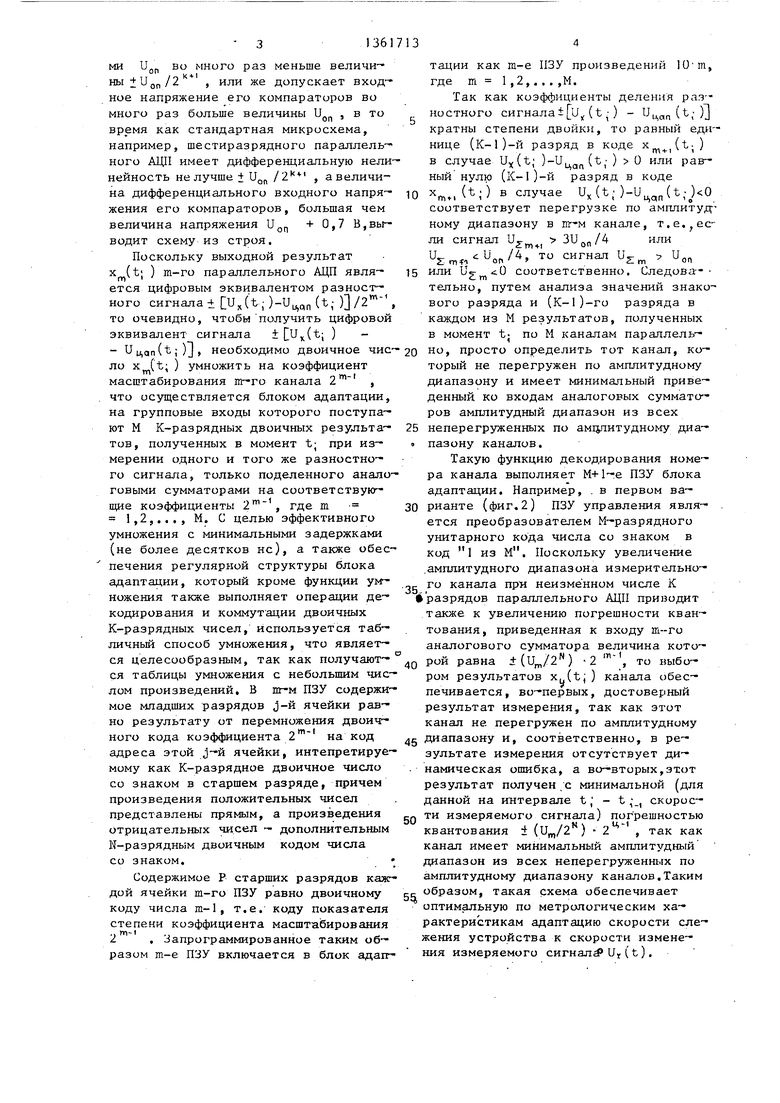

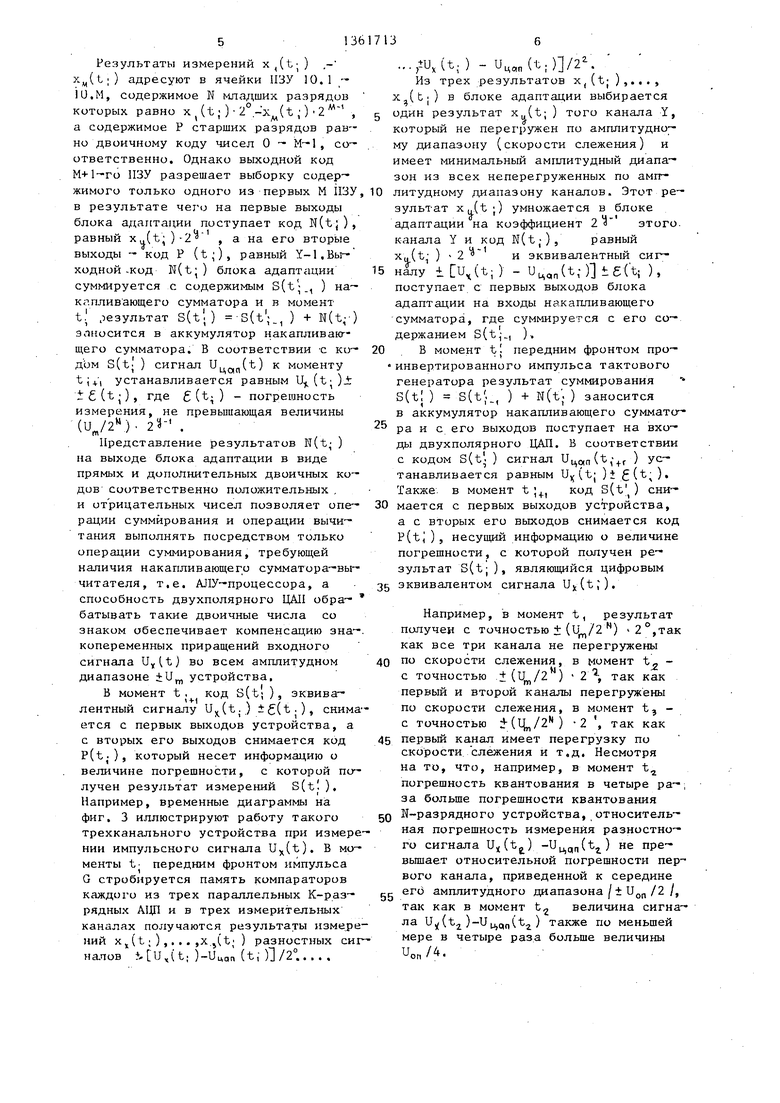

На фиг. 1 изображена функциональ ная схема устройства; на фиг. 2 вариант функциональной схемы блока адаптации; на фиг. 3 - временные диаграммы, поясняющие работу устройст- ва.

Устройство содержит аналого-цифровой преобразователь (АЦП) 1 разностного сигнала, содержащий К-раз- рядные АЦП 2.1 - 2.М, блок 3 адаптации, аналоговые сумматоры 4.1 - 4.М, тактовый генератор 5, инвертор 6, накапливаюцщй сумматор 7, цифроаналоговый преобразователь (ЦАП) 8 (N- paзpядный, двухполярный масштабирующий усилитель 9.

Блок 3 адаптации содержит М+1 постоянных запоминающих устройств (ПЗУ) 10.1 - 10.М+1, при этом каждый т-ана логовый сумматор 4 по второму и третьему входам имеет козффициенты Передачи, равные соответственно -2 и +2, и по первому входу -

единичный коэффициент передачи, где m 1,2,...., а количество АЦИ М выбирают следующим образом МбР и М W-K+1, где К и Р - числа разрядов АЦП и младших разрядов ПЗУ соответственно. В одном варианте довый блок адаптации содержит М ПЗУ. Устройство работает следующим об- .разом. I .

На первые два входа всех М аналоговых сумматоров поступают измеряе- . мый сигнал Uiclt) и компенсируюш;ий сигнал ,(t;) двухполярного ЦАП 8, являющийся аналоговым эквивалентом кода S(t ., ) накапливающего сумматора, а на третьи входы поступает выходной сигнал UQ масштабирующего усилителя, равный половине напряжения UQ источника опорного сигнала, определяющего величину амплитудного диапазона каждого из М идентичных К-разрядных АЦП.Амплитудные диапазоны UQI входных сигналов параллельных К-разрядных АЦП связаны с амплитудным диапазоном ±U устройства через параметры N и К следующим соотношением Uon /±Uj-2 .

13 -2

Схема каждого из М трехвходовых сумматоров построена таким образом, что по входу суммирования усилителя

. т-го аналогового сумматора для его.

третьего входа образован делитель из

резисторов сопротивлением R и R, , для его второго входа - делитель из резисторов сопротивлением

-Н, и R,, а по входу вычитания операционного усилителя входное сопротивление равно { сопротивление обратной связи равно R, что обеспечивает по второму и третьему

5 входам т-го аналогового сумматора коэффициенты передачи, равньге соответственно - и а по первому входу - единичнь1й коэффициент передачи. Соответственно,выходной

0 сигнал ) m-ro аналогового сумматора равен )-Uu,o(n( t Л/2

+ Uon/2.

Такое смещение сигнала LU,i(t)

- и

цап

(t)l/2

m-i

на величину, рав

5

5 ную половине амплитудного диапазона

UQ К-разрядного АЦП 2.т, обеспечи- вает как измерение двухполярных раз- ностных сигналов . EUx(t) - Um,(t)J/2 , так и представление

0 цифровых эквивалентов х (t- ) на его выходе в виде двоичных чисел со знаком в старшем К-м разряде, так как в этом случае К-й разряд несет информацию не о величине, а о полярности разностного сигнала.

Таким образом, такая схема, содержащая М К-разрядных АЦП с одинаковыми амплитудными диапазонами Ug входных сигналов обеспечивает измере-

0 ние двухполярных разностных сигналов с представлением цифровых эквивалентов в виде двоичных чисел со знаком и обеспечивает М измерительных каналов с различными приведенными к вхо-

g дам аналоговых сумматоров амплитудными диапазонами от iUop/2 в первом канале до ±(/2} 2 - 1 М-М канале, что позволяет получать достоверные, т.е. без динамической

Q погрешности, результаты измерений в широком диапазоне скоростей изменения измеряемого сигнала вплоть до величины , где f - частота импульсов тактового генератора.

gg Кроме того, схема реализуется на стандартных микросхемах АЦП, так как она или предполагает дифференциальную нелинейность К-разрядного преобразователя с амплитудными диапазона-

ми Ugj, ВО много раз меньше величи Hbij:Uon/2 , или же допускает входное напряжение его компараторов во много раз больше величины и , в то время как стандартная микросхема, например, шестиразрядного параллель- ного АЦП имеет дифференциальную нелинейность не лучше ± U , а величина дифференциального входного напряжения его компараторов, большая чем величина напряжения U +0,7 В,выводит схему из строя.

Поскольку выходной результат X (t| ) m-ro параллельного АЦП является цифровым эквивалентом разностного сигнала и,(ti)-Uy,gn(t; ) очевидно, чтобы получить цифровой эквивалент сигнала ± U(t; ) - и цап (t; )J , необходимо двоичное число x(t; ) умножить на коэффициент масштабирования т-го канала , что осуществляется блоком адаптации, на групповые входы которого поступают М К-разрядных двоичных результатов, полученных в момент t; при измерении одного и того же разностного сигнала, только поделенного аналоговыми сумматорами на соответствующие коэффициенты , где m 1,2,.,., М. С целью эффективного умножения с минимальными задержками (не более десятков не), а также обеспечения регулярной структуры блока адаптации, который кроме функции умножения также выполняет операции декодирования и коммут ации двоичных К-разрядных чисел, используется таб- личньш способ умножения, что является целесообразным, так как получаются таблицы умножения с небольшим числом произведений, В пг-м ПЗУ содержимое младших разрядов J-и ячейки равно результату от перемножения двоичного кода коэффициента на код адреса этой j-й ячейки, интепретируе- мому как К-разрядное двоичное число со знаком в старшем разряде, причем произведения положительных чисел представлены прямым, а произведения отрицательных чисел - дополнительным N-разрядным двоичным кодом числа со знаком.

Содержимое Р старших разрядов кажг дои ячейки т-го ПЗУ равно двоичному коду числа т-1, т.е. коду показателя степени коэффициента масшта(5ирования 2 . Запрограммированное таким образом т-е ПЗУ включается в блок адагг

тации как т-е ПЗУ произведений 10 т, где ш 1,2,...,М.

Так как коэффициенты деления раз ностного сигнала± и (t;) - U (t,) кратны степени двойки, то равный единице (К-1)-й разряд в коде в случае Uy(t; )-Uцg„(t; ) О или равный нулю (К-1)-й разряд в коде

0 .. (;) в U,(t;)-U(t, соответствует перегрузке по амплитудному диапазону в т-м канале, т.е.если сигнал , Зидп/4 или сигнал и , и„„

5 или соответственно. Следова-- тельно, путем анализа значений знако-- вого разряда и (К-1)-го разряда в каждом из М результатов, полученных в момент tj по М каналам параллель-

0 но, просто определить тот канал, который не перегружен по амплитудному диапазону и имеет минимальный приведенный ко входам аналоговых сумматоров амплитудный диапазон из всех

5 неперегруженных по амцпитудному диа- пазону каналов.

Такую функцию декодирования номера канала выполняет М+1-е ПЗУ блока адаптации. Например, . в первом ва0 рианте (фиг,2) ПЗУ управления является преобразователем М-разрядного унитарного кода числа со знаком в код 1 из м. Поскольку увеличение .амплитудного диапазона измерительноg го канала при неизменном числе К разрядов параллельного АЦП приводит также к увеличению погрешности квантования, приведенная к входу т-го аналогового сумматора величина кото-

0

рой равна +(и„/2) -2 , то выбором результатов x,(tj ) канала обеспечивается, во-первых, достоверный результат измерения, так как зтот канал не. перегружен по амплитудному

g диапазону и, соответственно, в результате измерения отсутствует ди- . намическая ошибка, а во-вторых,этот результат получен с минимальной (для данной на интервале t, - t ,, скорое-

Q ти измеряемого сигнала) погрешностью квантования 1 () 2 , так как канал имеет минимальный амплитудный диапазон из всех неперегруженных по амплитудному диапазону каналов.Таким образом, такая схема обеспечивает оптимальную по метрологическим характеристикам адаптацию скорости слежения устройства к скорости изменения измеряемого сигнал U, (t).

Результаты измерений x,(t;) .- X,(L;) адресуют в ячейки ПЗУ 10.1 - 1L),M, содержимое N младших разрядов которых равно х (t; ) 2°.-x(t;) , а содержимое Р старших разрядов равно двоичному коду чисел О - M-l, соответственно. Однако выходной код M+l-го ПЗУ разрешает выборку содер-

жимого только одного из первых М ПЗУ, 10 литудному диапазону каналов. Этот ре-

в результате чего на первые выходы блока адаптации поступает код N(t;) , равный Xj,(t; ) , а на его вторые выходы - код Р (t;), равный У-1,Вьгзультат 3Ci,(t ;) умножается в блоке адаптации на коэффициент 2 « этого. канала Y и код N(t;)s равный u( fc, ) 2 ° и эквивалентный сип

ходной-код N(t; ) блока адаптации 15 налу (t;) - Uu,qn (t,) t (t; ), суммируется с содержимым S(t;, ) на- поступает с первых выходов блока

адаптации на входы накапливающего сумматора, где суммируется с его содержанием s(t,-, ).

ш,его сумматора. В соответствии -с. ко- 20 В момент t передним фронтом про-

инвертированного импульса тактового генератора результат суммирования S(t ) S(t;., ) + N(t; ) заносится

каплив ающего сумматора и в момент t( результат S(t;) -S(t ;, ) + N(t-) заносится в аккумулятор накапливаю- ш,его сумматора. В

дЬм S(t| ) сигнал ) к моменту t;Vi устанавливается равным U(t;)± i(tj), где 6(t) - погрешность измерения, не превьшающая величины (и„/2.). .25

Представление результатов N(t ) на выходе блока адаптации в виде прямых и дополнительных двоичных кодов соответственно положительных , и отрицательных чисел позволяет one- 30 мается с первых выходов устройства.

в аккумулятор накапливающего сумматора и с его выходов поступает на входы двухполярного ЦДЛ. В соответствии с кодом S(t ) сигнал Uцo,г,(t, ) У танавливается равным U)((tj )i fCt,). Также, в момент t ;, код S(t ) снирации суммирования и операции вычитания выполнять посредством только операции суммирования, требующей наличия накапливающего сумматора-вы- читателя, т.е. АЛУ-процессора, а способность двухполярного ЦА11 обра- батывать такие двоичные числа со знаком обеспечивает компенсацию зна-. копеременных приращений входного сигнала Uy(t) во всем амплитудном диапазоне ±U устройства.

В момент t, код S(t;), эквивалентный сигналу U(t;} ±6(t.) снимается с первых выходов устройства, а с вторых его выходов снимается код P(t. ) который несет информацию о величине погрешности, с которой получен результат измерений S(tJ). Например, временные диаграммы на фиг. 3 иллюстрируют работу такого трехканального устройства при измерении импульсного сигнала U(t). В моменты t- передним фронтом импульса G стробируется память компараторов

а с вторых его выходов снимается код P(ti ), несущий информацию о величине погрешности, с которой получен результат S(t; ), являющийся цифровым 35 эквивалентом сигнала Uj((t;).

Например, в момент t, результат получен с точностью ±() «2°,так как все три канала не перегружены

40 по скорости слежения, в момент t, - с точностью ± () 2 так как первый и второй каналы перегружены по скорости слежения, в момент t, - с точностью () -2 , так как

45 первый канал имеет перегрузку по скорости слежения и т.д. Несмотря на то, что, например, в момент t, погрешность квантования в четыре ра- за больше погрешности квантования

5Q N-разрядного устройства, относительная погрешность измерения разностного сигнала U(tj.) -Uцд„(t) не пре- вьш1ает относительной погрешности пер вого канала, приведенной к середине

каждого из трех параллельных К-раз- 55 амплитудного диапазона/± , рядных А1ДП и в трех измерительных каналах получаются результаты измерений Xj (t ;),... ,X.,(t; ) разностных СИГ

налов 5-tU,(t; )-ицс.п (ti )1/2°

так как в момент t величина сигна ла U(t.2 )-Um,(t.2) также по меньшей мере в четыре раза больше величины Uon/4.

...;и, (t; ) - и,„(;)/2.

Из трех результатов x,(t; ),..., X (t|) в блоке адаптации выбирается один результат ) того канала Y, который не перегружен по амплитудному диапазону (скорости слежения) и имеет минимальный амплитудный диапазон из всех неперегруженных по амп-

мается с первых выходов устройства.

в аккумулятор накапливающего сумматора и с его выходов поступает на входы двухполярного ЦДЛ. В соответствии с кодом S(t ) сигнал Uцo,г,(t, ) У танавливается равным U)((tj )i fCt,). Также, в момент t ;, код S(t ) сниа с вторых его выходов снимается код P(ti ), несущий информацию о величине погрешности, с которой получен результат S(t; ), являющийся цифровым 35 эквивалентом сигнала Uj((t;).

Например, в момент t, результат получен с точностью ±() «2°,так как все три канала не перегружены

40 по скорости слежения, в момент t, - с точностью ± () 2 так как первый и второй каналы перегружены по скорости слежения, в момент t, - с точностью () -2 , так как

45 первый канал имеет перегрузку по скорости слежения и т.д. Несмотря на то, что, например, в момент t, погрешность квантования в четыре ра- за больше погрешности квантования

5Q N-разрядного устройства, относительная погрешность измерения разностного сигнала U(tj.) -Uцд„(t) не пре- вьш1ает относительной погрешности первого канала, приведенной к середине

55 амплитудного диапазона/± ,

амплитудного диапазона/± ,

так как в момент t величина сигнала U(t.2 )-Um,(t.2) также по меньшей мере в четыре раза больше величины Uon/4.

7 ,13

Формула изобретения I . Следящий аналого -цифровой преобразователь, содержащий последова- тельно соединенные аналого-цифровой преобразователь разностного сигнала, накапливающий сумматор, цифроанало- говый преобразователь, выход которого соединен с первым входом аналого- цифрового преобразователя разностно- го сигнала, второй вход которого является входной шиной, а третий вход соединен с выходом тактового генератора, выходы накапливающего суммато ра являются первой выходной шиной, отли ч ающи йся тем, что, с целью расширения диапазона допустимых скоростей изменения входного сигнала, введен инвертор, выход которого соединен с тактовым входом на- капливающего сумматора, вход соединен с выходом тактового генератора и является второй выходной шиной, третьей выходной шиной являются вторые выходы аналого-цифрового преобра- зователя разностного сигнала, выполненного на М аналого-цифровых преобразователях, М аналоговых сумматорах, блоке адаптации, масштабирующем усилителе, вход которого объединен пер- выми входами.аналого-цифровых преобразователей, аналоговых сумматоров и является шиной опорного сигнала, а выход соединен с вторыми входами аналоговых сумматоров, третьи и чет- вертые входы которых соответственно- объединены и являются вторым и третьим входами аналого-цифрового

8

преобразователя разностного сигнала, третьим входом которого являются объединенные вторые входы аналого- цифровых преобразователей, третьи входы которых соединены с выходами соответствующих аналоговых сумматоров, а выходы соединены с соответствующими группами входов блока адаптации, первые и вторые выходь которо го являются первыми и вторыми выходами аналого-цифрового преобразователя

разностного сигнала.

I

2. Преобразователь по п.I, о т - личающийся тем, что блок адаптации выполнен на (М+1)-м постоянном запоминающем устройстве N- младших и Р-старших разрядов, М постоянных запоминающих устройств соответственно объединены и являются первыми и вторыми выходами блока адаптации соответственно, входы разрешения выборки соединены с соответствующими выходами (М+1)-го постоянного запоминающего устройства, вход разрешения выборки которого является шиной логической единицы,.первый адресный вход которого объединен с К-м адресным входом первого постоянного запоминающего устройства, а с второго по Hй объединены с соответствующими (К-1)-ми адресными входами с второго по М-й постоянных запоминающих устройств, адресные входы постоянных запоминаюпщх устройств с первого по М-и являются входами соответствующих групп блока ад аптации.

tit, it if ijt } tst s tft s iitr titf

и„

u,, -

Редактор П.Гереши

Составитель И.Романова Техред М.Дидык

Заказ 6303/56 Тираж 900Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Корректор И.Муска

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Двухтактный аналого-цифровой преобразователь | 1985 |

|

SU1336236A1 |

| Устройство аналого-цифрового преобразования | 1988 |

|

SU1501268A2 |

| Устройство аналого-цифрового преобразования | 1987 |

|

SU1559405A2 |

| БЫСТРОДЕЙСТВУЮЩИЙ МНОГОФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА В КОД ДЛЯ УСТРОЙСТВ ЭЛЕКТРОМЕХАНОТРОНИКИ | 1994 |

|

RU2094945C1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1282327A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1398093A1 |

| Функциональный преобразователь угла поворота вала в код | 1985 |

|

SU1309314A1 |

| Устройство для измерения угла сдвига фазы синусоидальных напряжений | 1982 |

|

SU1064227A1 |

Изобретение относится к измерительной технике, предназначено для измерений амплитуд широкополосных динамических сигналов и позволяет рас- ширить диапазон допустимых скоростей изменения входных сигналов. Для этого в преобразователь, содержащий.тактовый генератор 5, N-разрйдный накапливающий сумматор 7, двуполярный цифг- роаналоговый преобразователь 8, аналого-цифровой преобразователь 1 разностного сигнала (АЦПР), введен инвертор 6, а АЦПР выполнен на М параллельных К разрядных аналого-цифровых преобразователях 2, аналоговых сумматорах 4, блоке 3 адаптации, масштабирующем усилителе 9. При этом т-й аналоговый сумматор 4 имеет по первому и второму входам коэффициенты передачи, равные соответственно и +2 1-1П а по третьему входу - единичный коэффициент передачи, где m 1,2,.,,,МиМ K+i-K.l з.п. ф-лы,3кл I (Л

| Балакай В.Г | |||

| и др | |||

| Интегральные схемы АЦП и ЦАП | |||

| М.: Энергия,1978 | |||

| Преобразователи информации в ана- лого -цифровых вычислительных устрой - ствах и системах | |||

| Под ред | |||

| Г.М.Петрова | |||

| М.: Машиностроение, 1973, с | |||

| Ножевой прибор к валичной кардочесальной машине | 1923 |

|

SU256A1 |

Авторы

Даты

1987-12-23—Публикация

1985-08-27—Подача