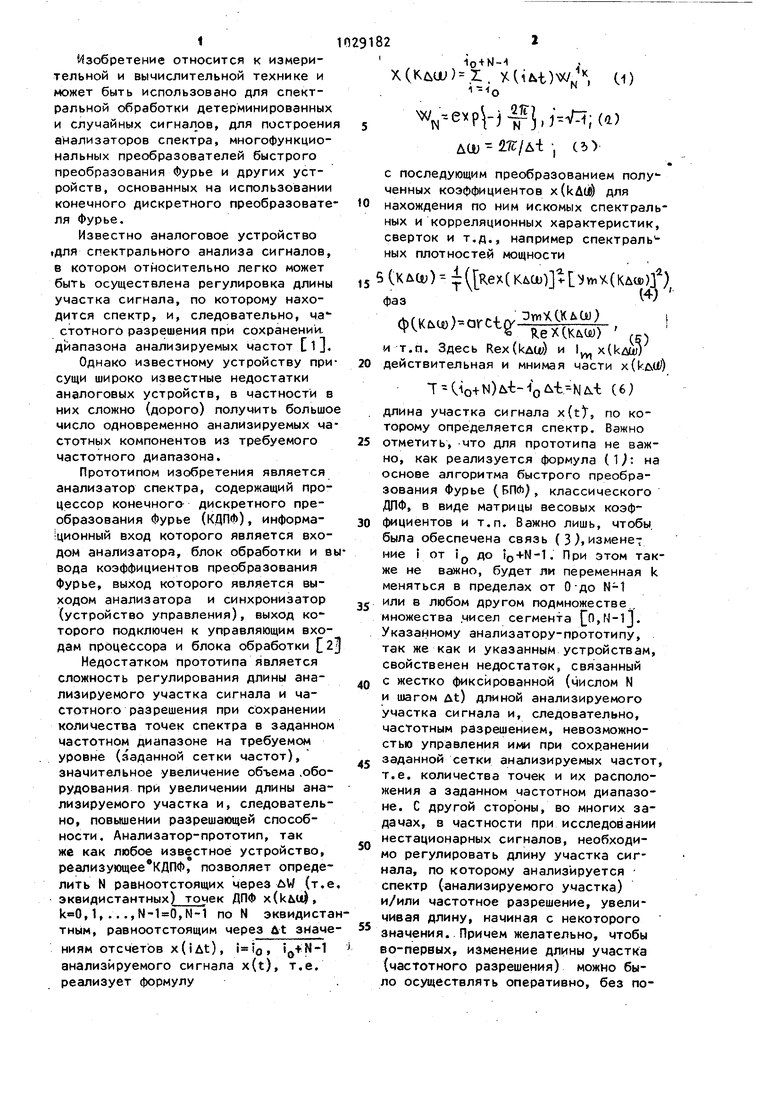

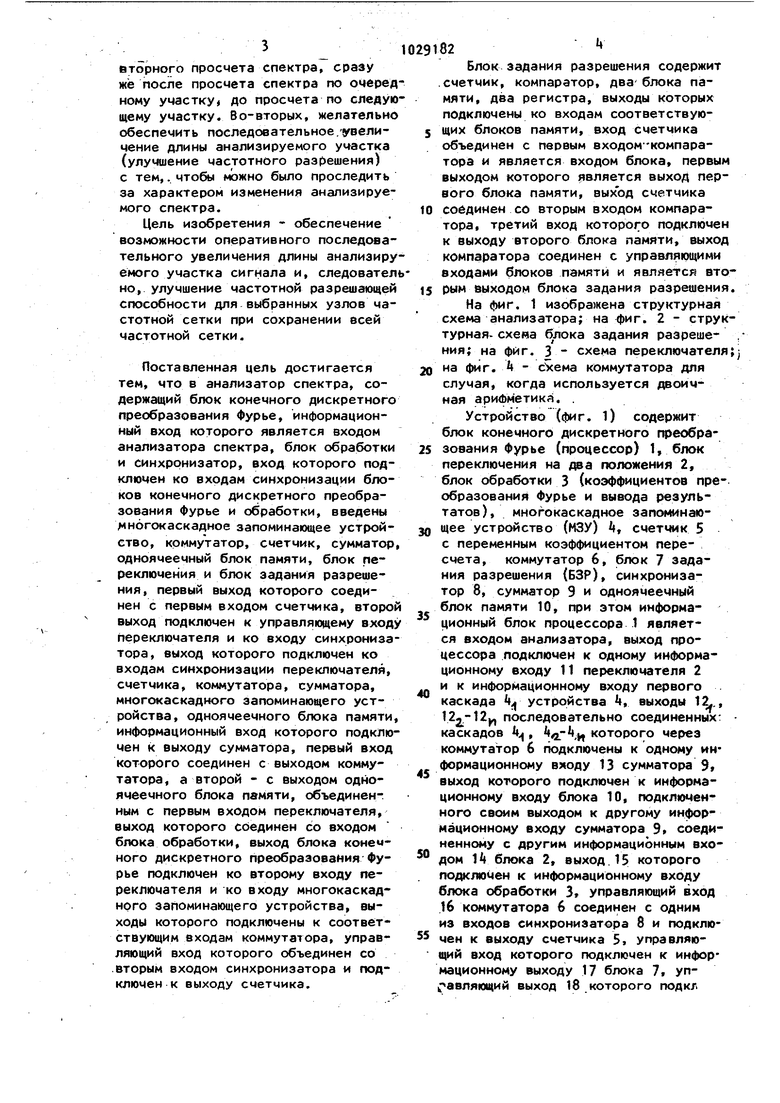

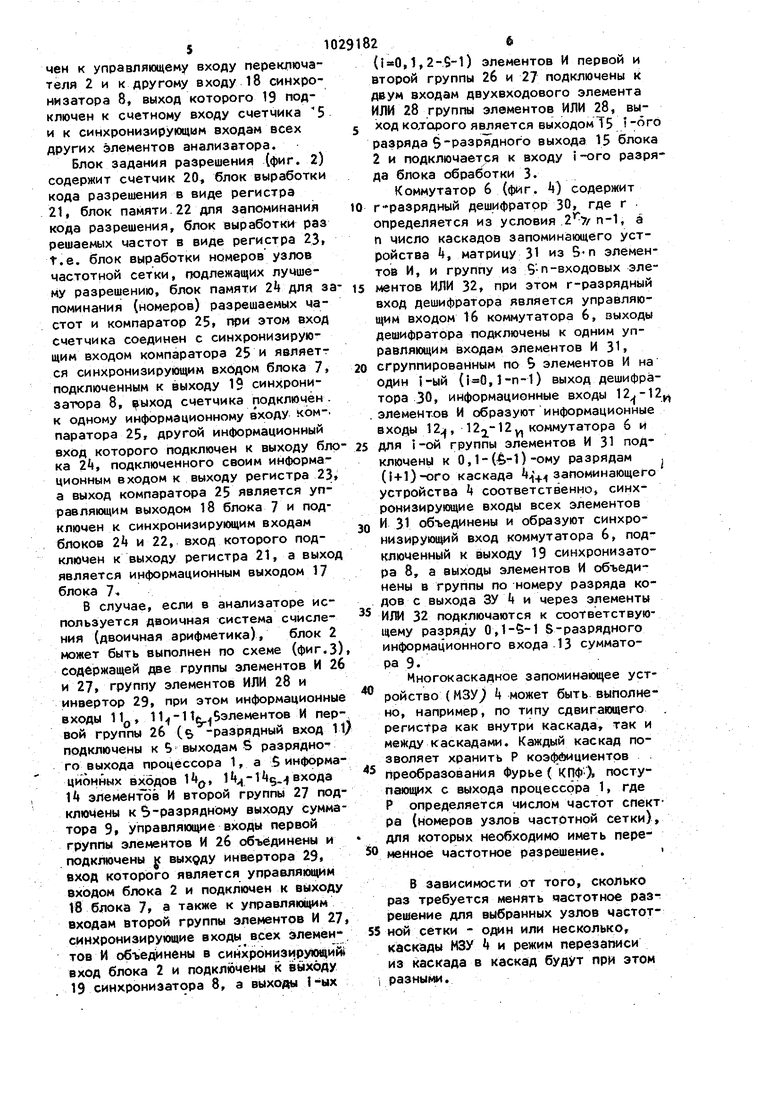

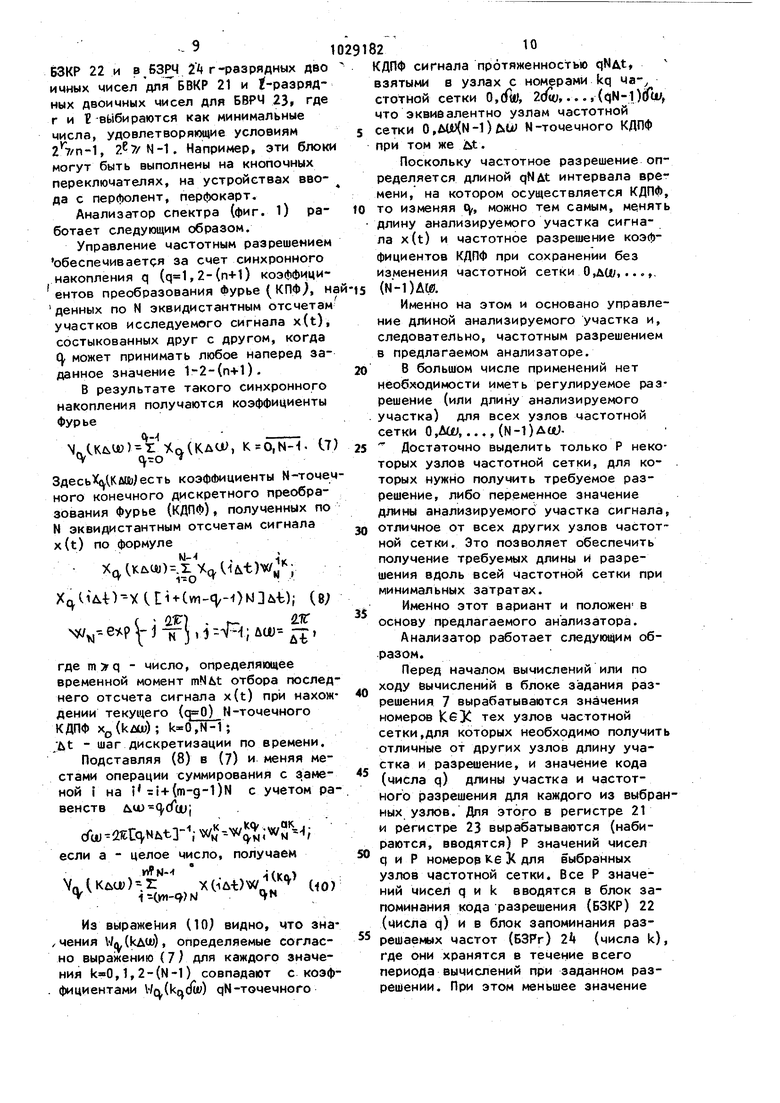

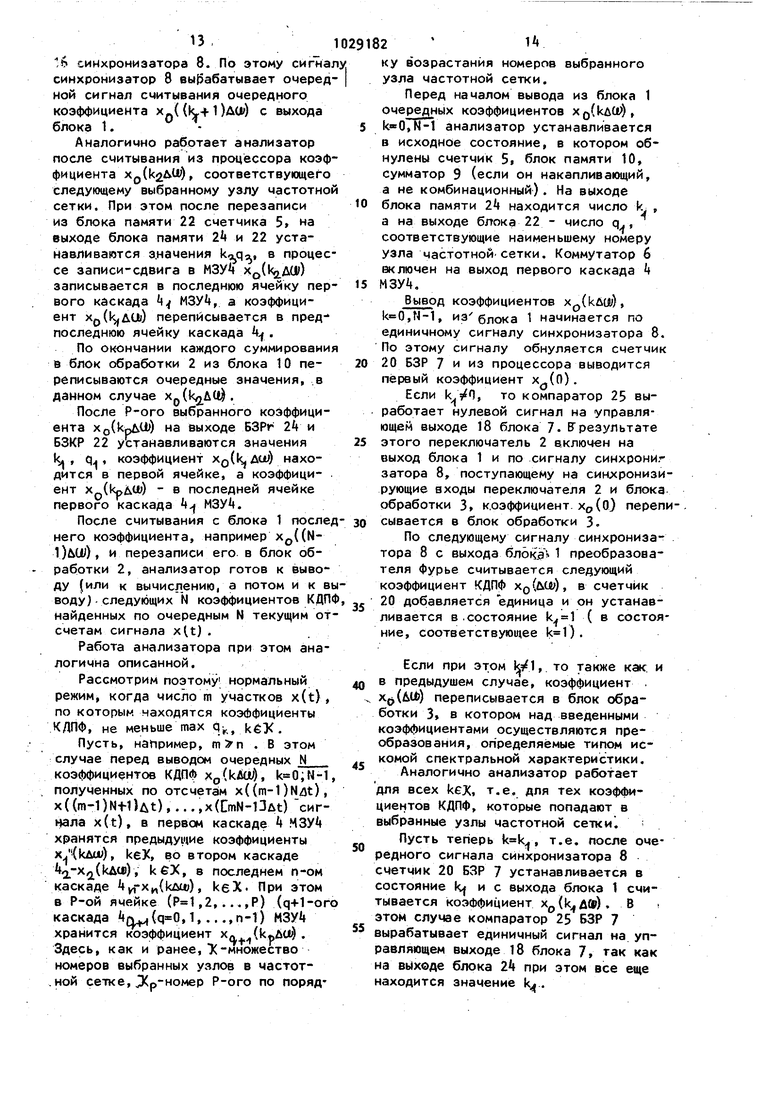

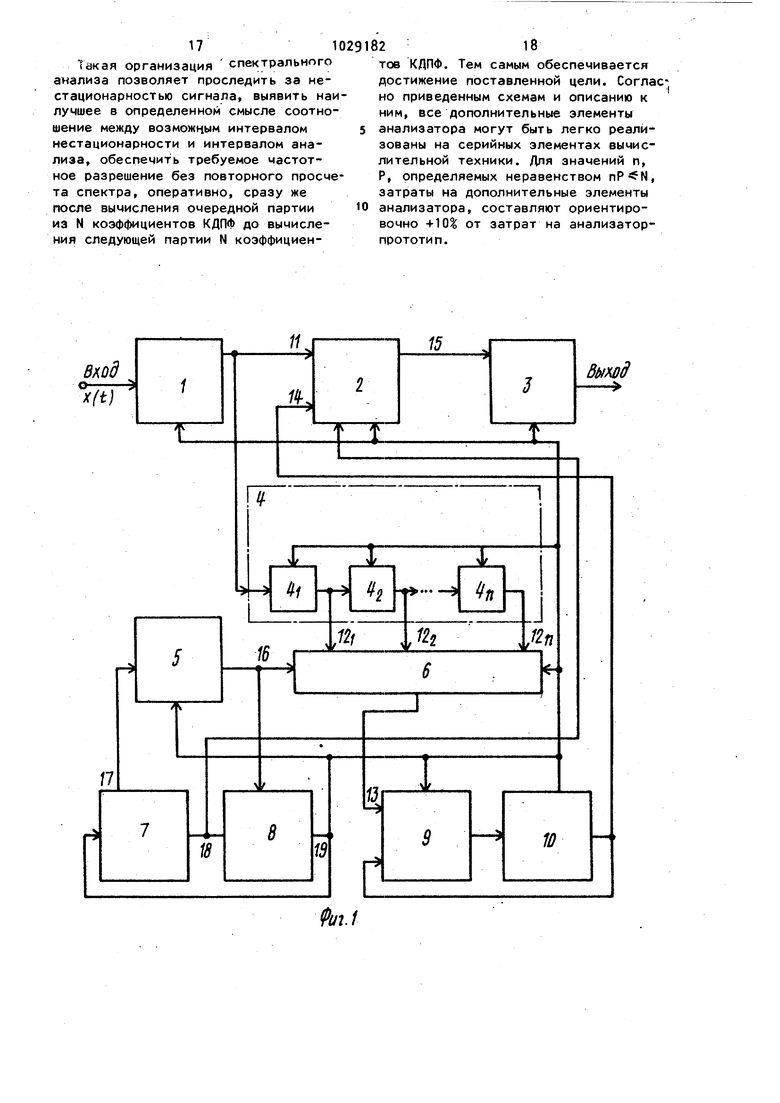

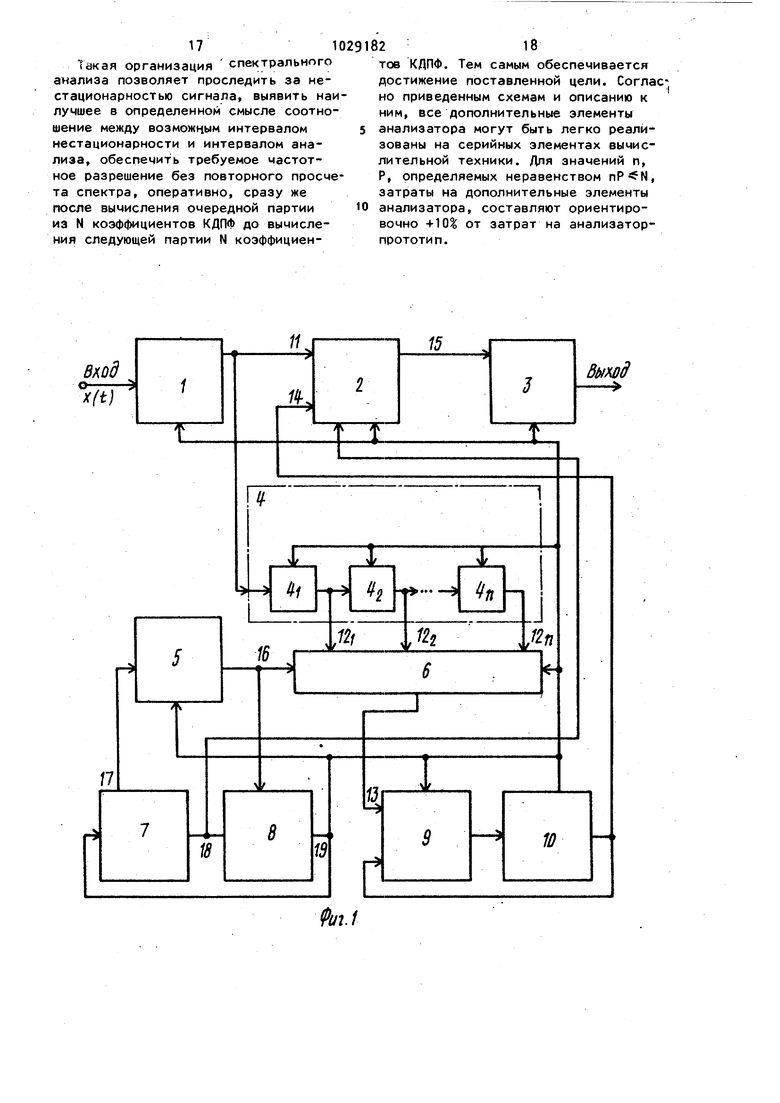

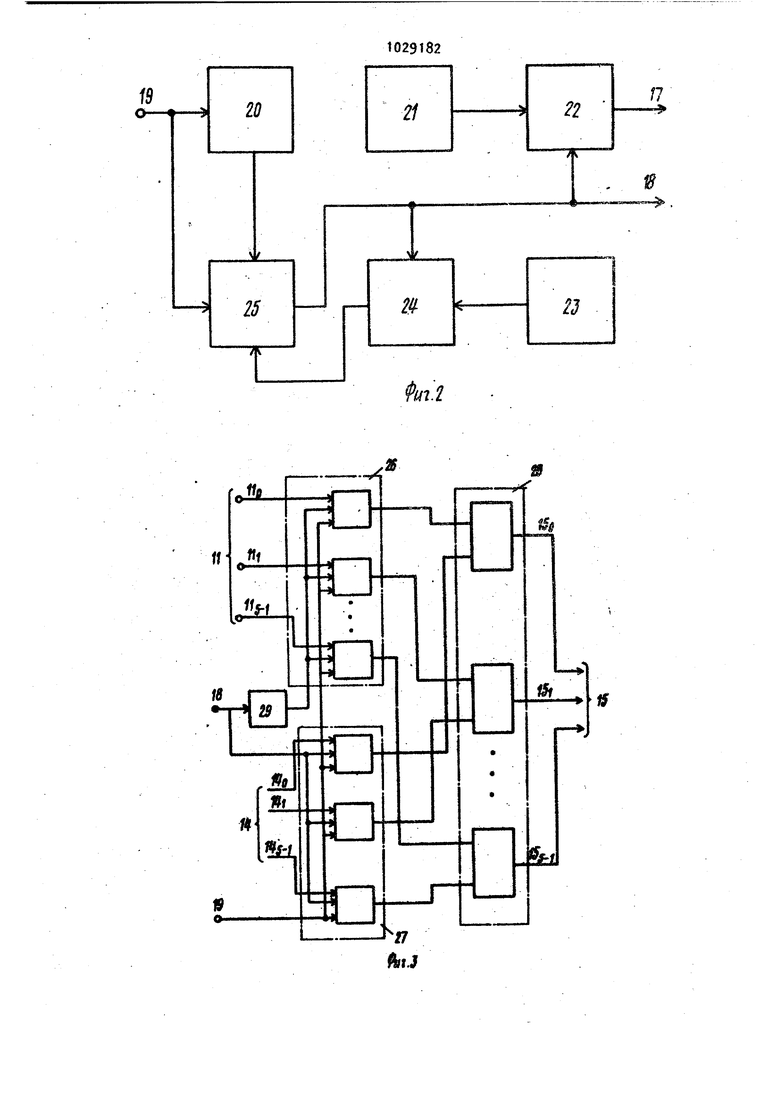

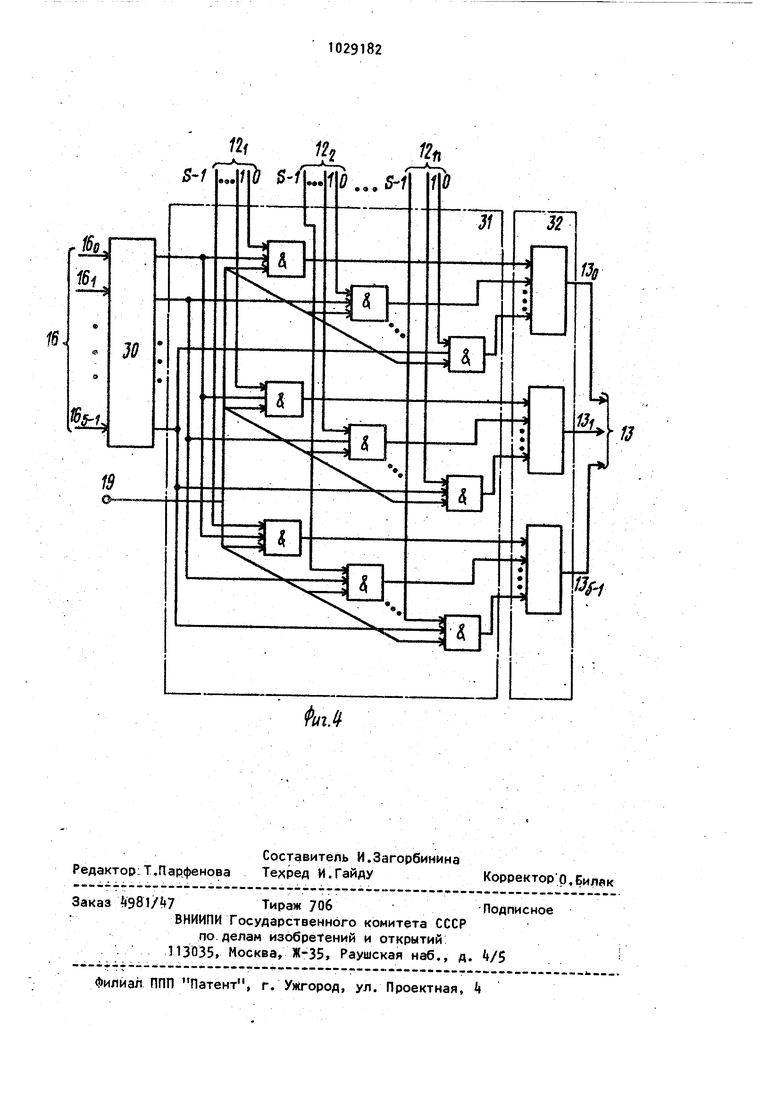

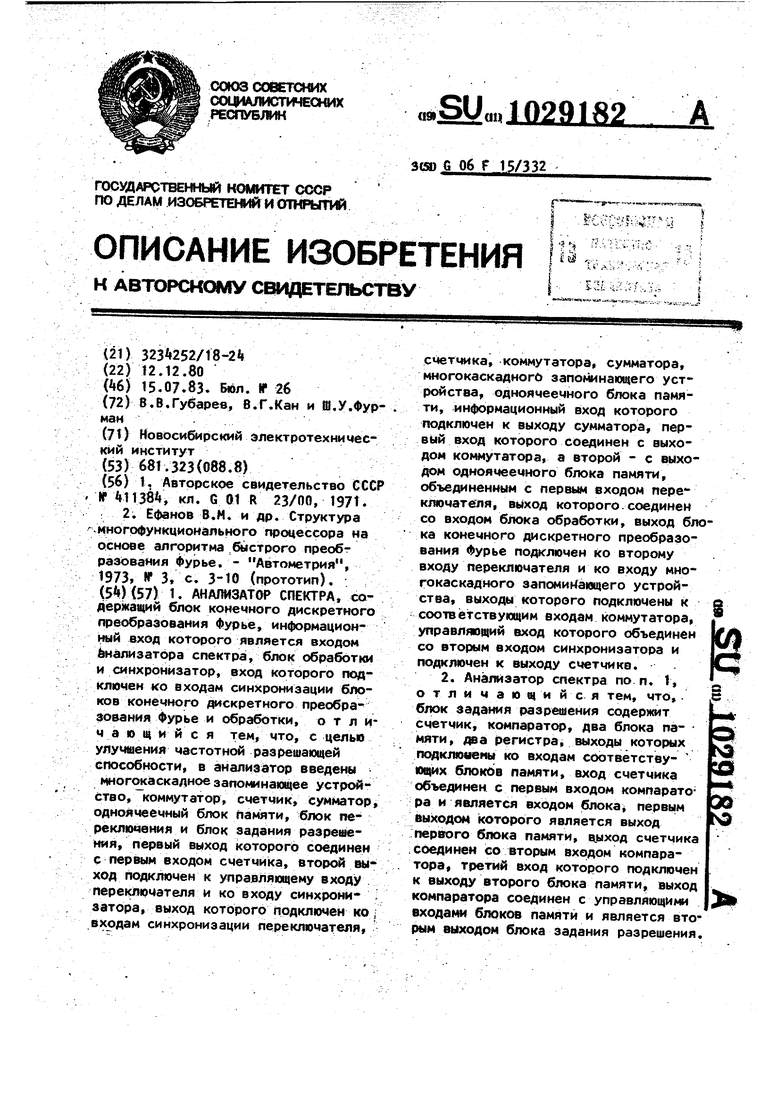

1 Изобретение относится к измерительной и вычислительной технике и может быть использовано для спектральной обработки детерминированных и случайных сигналов, для построения анализаторов спектра, многофункциональных преобразователей быстрого преобразования Фурье и других устройств, основанных на использовании конечного дискретного преобразователя Фурье, Известно аналоговое устройство ,для спектрального анализа сигналов, в котором относительно легко может быть осуществлена регулировка длины участка сигнала, по которому находится спектр, и, следовательно, ча стотного разрешения при сохранений, диапазона анализируемых частот l. Однако известному устройству при сущи широко известные недостатки аналоговых устройств, в частности в них сложно (дорого) получить большо число одновременно анализируемых ча стотных компонентов из требуемого частотного диапазона. Прототипом изобретения является анализатор спектра, содержащий процессор конечного дискретного преобразования Фурье (КДПФ), информационный вход которого является входом анализатора, блок обработки и в вода коэффициентов преобразования Фурье, выход которого является выходом анализатора и синхронизатор (устройство управления), выход которого подключен к управляющим входам процессора и блока обработки 2 Недостатком прототипа является сложность регулирования длины анализируемого участка сигнала и частотного разрешения при сохранении количества точек спектра в заданном частотном диапазоне на требуемом уровне (заданной сетки частот), значительное увеличение объема .оборудования при увеличении длины анализируемого участка и, следовательно, повышении разрешающей способности. Анализатор-прототип, так же как любое известное устройство, реализующее КДПФГ позволяет определить N равноотстоящих через/iW (т.е эквидистантных) точек ДПФ x(k&u, ,1,,..,,N-1 по N эквидиста тным, равноотстоящим через At зиаче ниям отсчетов x{iAt), . анализируемого сигнала x(t), реализует формулу 2 .. X(Kuai).2:. %(iH)X)C/J, )ir5,:i-V ;(a) ДШ-2.7t/A-t , () с последующим преобразованием полученных коэффициентов x(ku(f) для нахождения по ним искомых спектральных и корреляционных характеристик, сверток и т,д., например спектральных плотностей мощности СКЛСи) Цяех( КЛШ) (Kut)J) АячW ). т.п. Здесь Rex(kAU/) и 1 x(kuuO действительная и мнимая части x(kuUJ) T-Cio-t-N)-t-1o. (6) длина участка сигнала x(t), по которому определяется спектр. Важно отметить, что для прототипа не важно, как реализуется формула ( на основе алгоритма быстрого преобразования Фурье (БПЛ), классического ДПФ, в виде матрицы весовых коэффициентов и т.п. Важно лишь, чтобы, была обеспечена связь (3),измене7 ние i от ip до to+N-1, При этом также не важно, будет ли переменная k меняться в пределах от О-до N-1 или в любом другом подмножестве., множества .чисел сегмента n,N-1j, Указанному анализатору-прототипу, так же как и указанным устройствам, свойственен недостаток, связанный с жестко фиксированной (числом N и шагом At) длиной анализируемого участка сигнала и, следовательно, частотным разрешением, невозможностью управления ими при сохранении заданной сетки анализируемых частот, т.е. количества точек и их расположения а заданном частотном диапазоне. С другой стороны, во многих задачах, в частности при исследовании нестационарных сигналов, необходимо регулировать длину участка сигнала, по которому анализируется спектр (анализируемого участка) и/или частотное разрешение, увеличивая длину, начиная с некоторого значения. Причем желательно, чтобы во-первых, изменение длины участка (частотного разрешения) можно было осуществлять оперативно, без повторного просчета спектра, сразу же после просчета спектра по очеред ному участку, до просчета по следую щему участку. Во-вторых, желательно обеспечить последовательное/увеличение длины анализируемого участка (улучшение частотного разрешения) с тем,. чтобы можно было проследить за характером изменения анализируемого спектра. Цель изобретения - обеспечение возможности оперативного последовательного увеличения длины анализиру емого участка сигнала и, следовател но, улучшение частотной разрешающей способности для выбранных узлов частотной сетки при сохранении всей частотной сетки. Поставленная цель достигается тем, что в анализатор спектра, содержащий блок конечного дискретного преобразования Фурье, информационный вход которого является входом анализатора спектра, блок обработки и синхронизатор, вход которого подключен ко входам синхронизации блоков конечного дискретного преобразования Фурье и обработки, введены многокаскадное запоминающее устройство, коммутатор, счетчик, сумматор одноячеечный блок памяти, блок переключения и блок задания разрешения, первый выход которого соединен с первым входом счетчика, второ выход подключен к управляющему вход переключателя и ко входу синхрониза тора, выход которого подключен ко входам синхронизации переключателя, счетчика, коммутатора, сумматора, многокаскадного запоминающего устройства, одноячеечного блока памяти информационный вход которого подключен к выходу сумматора, первый вход которого соединен с выходом коммутатора, а второй - с выходом одноячеечного блока памяти, объединен-, ным с первым входом переключателя, выход которого соединен со входом блока обработки, выход блока конечного дискретного преобразования Фурье подключен ко второму входу переключателя и ко входу многокаскадного запоминающего устройства, выходы которого подключены к соответствующим входам коммутатора, управляющий вход которого объединен со .вторым входом синхронизатора и подключен к выходу счетчика. 82 Блок задания разрешения содержит .счетчик, компаратор, два- блока памяти, два регистра, выходы которых подключены ко входам соответствующих блоков памяти, вход счетчика объединен с первым входом-компаратора и является входом блока, первым выходом которого является выход первого блока памяти, выхЪд счетчика соединен со вторым входом компаратора, третий вход которого подключен к выходу второго блока памяти, выход компаратора соединен с управляющими входами блоков памяти и является вторым выходом блока задания разрешения. На фиг. 1 изображена структурная схема анализатора; на фиг. 2 - структурная- схеиа блока задания разрешения; на фиг. 3 - схема переключателя;; на фиг. - сУема коммутатора для случая, когда используется двоичная арифметика. . Устройство (фиг. 1) содержит блок конечного дискретного преобразования Фурье (процессор) 1, блок переключения на два положения 2, блок обработки 3 (коэффициентов преобразования Фурье и вывода результатов), многокаскадное запоминающее устройство (МЗУ) А, счетчик 5 с переменным коэффициентом пересчета, коммутатор 6, блок 7 задания разрешения (БЗР), синхронизатор 8, сумматор 9 и одноячеечный блок памяти 10, при этом информационный блок процессора 1 является входом анализатора, выход процессора подключен к одному информационному входу 11 переключателя 2 и к информационному входу первого каскада , устройства k, выходы 12.., 122,-12 последовательно соединенных: каскадов k , «(Чи которого через коммутатор 6 подключены к одному информационному входу 13 сумматора 9 выход которого подключен к информационному входу блока 10, подключенного своим выходом к другому информационному входу сумматора 9 соединенному с другим информационным входом 14 блока 2, выход.15 которого подклю 4ен к информационному входу блока обработки 3 управляющий вход 16 коммутатора 6 соединен с одним из входов синхронизатора 8 и подключен к выходу счетчика 5, управляющий вход которого подключен к информационному выходу 17 блока 7, уп,равляющий выход 18 которого подкг 10 чем к управлящеку входу переключателя 2 и к другому входу 18 синхронизатора 8, выход которого 19 подключен к сметному входу счетчика 5 и к синхронизирующий входам всех других элементов анализатора. Блок задания разрешения (фиг. 2) содержит счетчик 20, блок выработки кода разрешения в виде регистра 21, блок памяти.22 для запоминания кода разрешения, блок выработки раз решаемых частот в виде регистра 23, Т.е. блок выработки номеров узлов частотной сетки, подлежащих лучшему разрешению, блок памяти 2 для за поминания (номеров) разрешаемых частот и компаратор 25, при этом вход счетчика соединен с синхронизирующим входом компаратора 25 и являетг ся синхронизирующим входом блока 7 подключенным к выходу 19 синхронизатора 8, счетчика подключён . к одному информационному входу ком-, паратора 25, другой информационный вход которого подключен к выходу блр ка 2k, подключенного своим информационным входом к выходу регистра 23, а выход компаратора 25 является управляющим выходом 18 блока 7 и подключен к синхронизирующим входам блоков 2 и 22, вход которого подключен к выходу регистра 21, а выход является информационным выходом 17 блока 7 В случае, если в анализаторе используется двоичная система счисления (двоичная арифметика), блок 2 может быть выполнен по схеме (фиг.3) содержащей две группы элементов И 26 и 27, группу элементов ИЛИ 28 и инвертор 29, при этом информационные входы HQ, 11 -1и 5элементов И первой группы 26 (с, -разрядный вход 1l) подключены к S выходам S разрядного выхода процессора 1, а .5 информационных входов , входа 1 элементов И второй группы 27 подключены к S-разрядному выходу сумматора 9 управляющие входы первой группы элементов И 2б объединены и подключены выходу инвертора 29. вход которого является управляющим входом блока 2 и подключен к выходу 18блока 7, а также к управляюи им входам второй группы элементов И 27, синхронизирующие входы всех элементов И объединены в синхронизирующий вход блока 2 и подкл1бчены к 1эыхдду 19синхронизатора 8, а выходы Ных 26 , 1,2-S-1) элементов И первой и второй группы 26 и 27 подключены к двум входам двухвходового элемента ИЛИ 28 группы элементов ИЛИ 28, выход кодарого является выходомТ5 i-oro разряда 5-разря1Дного выхода 15 блока 2 и подключает :я к входу i -ого разряда блока обработки 3. Коммутатор 6 (фиг. k) содержит г разрядный дешифратор 30. где г определяется из условия 2 п-1, а п число каскадов запоминающего устройства , матрицу 31 из 5П элементов И, и группу из 9-п-входовых элементов ИЛИ 32, при этом г-разрядный вход дешифратора является управляющим входом 16 коммутатора 6, аыходы дешифратора подключены к одним управляющим входам элементов И 31, сгруппированным по 9 элементов И на один i-ый (,1-n-1) выход дешифратора 30 информационные входы , элементов И образуют информационные входы 12, коммутатора 6 И для i-ой группы элементов И 31 подключены к О,l-(fe-l)-ому разрядам (1+1)-ого каскада 4;{+ запоминающего устройства k соответственно, синхронизирующие входы всех элементов И 31 объединены и образуют синхронизирующий вход коммутатора 6, подключенный к выходу 19 синхронизатора 8, а выходы элементов И объединены в группы по номеру разряда кодов с выхода ЗУ Ц и через элементы ИШ 32 подключаются к соответствующему разряду 0,1-5-1 S-разрядного информационного входа 13 сумматора 9. Многокаскадное запоминающее устройство ( может быть выполнено, например, по типу сдвигающего регистра как внутри каскада, так и между каскадами. Каждый каскад позволяет хранить Р коэф(Ьициентрв Преобразования Фурье (КПФ), поступающих с выхода процессора 1, где Р определяется числом частот спектра (номеров узлов частотной сетки), для которых необходимо иметь переменное частотное разрешение. В зависимости от того, сколько раз требуется менять частотное разрешение для выбранных узлов частотной сетки - или несколько, каскады МЗУ k и режим перезаписи из каскада в каскад будут при этом разны. Если разрешение требуется менять один раз на каждые N вычисленных коэффициентов преобразования Фурье (КПФЛ то каскады МЗУ k выполняют ся без перезаписи и на каждый синх ронизирующий сигнал, поступающий на синхронизирующий вход МЗУ k с выхода -19 синхронизатора 8, в каска де происходит сдвиг содержимого на одну ячейку влево, запись в последнюю Р-ую ячейку первого каскада цтекущего КПФ из блока 1, перезапись содержимого первой ячейки j-pro. каскада k в последнюю ячейку каска .и потеря содержимого первой ячейки последнего каскада 4 НЗУ |. Если разрешение требуется менять несколы о раз на одно текущее вычис ление N, то каскады НЗУ k строятся с обратной связью, позволяющей, соде жимому ячеек каскада циркулировать в каскаде столько раз, сколько раз необходимо изменять разрешение. При этом на выходе последней Р-ой ячейк каскада всегда должно быть знамен ние КПФ, соответствующие ближайюаму в текущем счете узлу частотной сетки, подлежащему переменному част ному разрешению. Перезапись из каск да в каскад .во время циркуляции не произёодится. Перезапись из каскадов в каскад осуществляется по окончании цирку;ляции сразу во всех ячейках либово время последней циркуляции после довательно со сдвигом из ячейки в ячейку. В качестве второго, по ряду.ас- пектов более предпочтительного, варианта можно предложить реализовать МЗУ k вместе с-коммутатором 6 в аиде запоминающего, устройства со. стра ничной организацией памяти. В этом случае путем должной орг;анизации режима записи и считывания можно по Пучить переменные значения Р и п, некоторые дополнительные возможност по улучшению частотного разрешения, точности и т.д. Одноячеечный блок памяти 10 аналогичен одной ячейке каскада МЗУ k и так же, как ячейка любого каскада МЗУ М, позволяет хранить 9-разрядные двоичные числа. В качестве блока 10 может использован, например, регистр. При этом предполагается а сумматоре 9 осу« ествлять округление результатов до 5 разрядов. Если же округле1«1е не производится (что позволяет повысить точность результатов спектрального анализа), то разрядность блока . 10, входа k и выхода 15 блока 2, а также разрядность блока обработки 3 должны быть увеличены. На конструкции, схеме анализатора и принципе его работы это не сказывается и эффекты округления (или неокругления) в сумматоре 9 в дальнейшем не учитываются. Блок 1 конечного дискретного преобразования Фурье и блок 3 обработки повторяют аналогичные блоки, описанные для пpoт otипa. Счетчик с переменным коэффициентом 5 предназначен для суммирования единичных сигналов, поступающих на его с«4етный вход с выхода 10 синхронизатора 8, до значения q« 1,2-п, поступающего на его управляю« й вход с выхода 17 блока 7 определяющего длину анализируемого участка сигнала, частотное разрешение и положение коммутатора 6. Он может быть выполнен любым из известных в вычислительной технике методов, позволяющих работать в прямом коде. Например, он может быть выполнен в виде о чного суммирую щего двоичного счетчика, счетный счет которого является счетным входом, а выход - выходом счетчика с переменным коэфициентом пересчета S, и сравнения кодов, один (регистровый) вход которой является управляющим входом счетчика 5, второй подключен к выходу двоичного счетчика, а выход подключен к.шине обнуления двоичного счетчика. Блок памяти t предназначен для хранения Р номеров, выбранных для улучшения разрешения узлов частотной сетки (разрешаемых частот).. Компаратор 25 - это обычная схема срагвнения кодов с синхрож13ирующимвыходом (с элементом И на выходе, на один вход которой подается сигнал с выхода собственно схемы сравнения, а на второй - сигнал синхронизации). Счетчик 20 - это обычный двоичный счетчик, позволяющий считать , от 0 до М-1, где N - количество узлов астотной сетки, т.е. количество вычисляемых с помощью процессора 1 коэффициентов преобразованип Фурье. Регистры 21 и представляют собой устройства выработки и ввода в БЗКР 22 и в БЗРЧ 2 г-разрядных дво ичных чисел для БВКР 21 и t-разрядных двоичных чисел для БВРЧ 23 где г и IE-вУбираются как минимальные числа, удовлетворякнцие условиям 2 7/n-l, .7/N-1. Например, эти блоки могут быть выполнены на кнопочных переключателях, на устройствах ввода с перфолент, перфокарт Анализатор спектра (фиг. 1) ра- to ботает следующим образом. Управление частотным разрешением обеспечиваетря за счет синхронного , накопления q (,2-(n-H) коэффициентов преобразования Фурье (КПф), н денных по N эквидистантным отсчетам участков исследуемого сигнала x(t), состыкованных друг с другом, когда ( может принимать любое наперед заданное значение 1-2-(пч-1). В результате такого синхронного накопления получаются коэффициенты Фурье N (Кй,Ш). ((КД) KsOiN- iT ЗдесьХй(,КШ);есть коэффициенты N-точеч ного конечного дискретного преобразования Фурье (КДПФ), полученных по N эквидистантным отсчетам сигнала X (t) по формуле - ((So)-.(, )X(.ti()W3&t)i (8; ( - №) . tху/ --ет р - J irj 11 -тН; лсу где - число, определяющее временной момент mN&t отбора послед него отсчета сигнала x(t) при нахож дении текущего (q О) Н-точечного КДПФ XpXkiw); k-0,N-1; - шаг дискретизации по времени. Подставляя (8) в (7) и меняя местами операции суммирования с заменой I на ri + (m-g-1)N с учетом ра венств lO cj-cTijUj сГш-aitCq-Ni., если a - целое число, получаем )-r ) l-Cwi- JNl Ч Из выражения (10) видно, что значения V/((kAui), определяемые согласно выражению (7) для каждого значе ния ,1,2-(N-l) совпадают с коэффициентами V/ft(kcjc(w) qN-точечного 5 КДПФ сигнала протяженностью , взятыми в узлах с номерами kq частотной сетки D,rfttJ, 2(w,.. .,{qN-ll)olu, что эквивалентно узлам частотной сетки 0,М1КМ-1)йШ N-точечного КДПФ при том же iit. Поскольку частотное разрешение определяется длиной qNAt интервала времени, на котором осуществляется КДПФ, то изменяя с, можно тем самым, менять длину анализируемого участка сигнала x(t) и частотное разрешение коэффициентов КДПФ при сохранении без изменения частотной сетки 0,ди/,...,. (N-l)At0. Именно на этом и основано управление длиной анализируемого участка и, следовательно, частотным разрешением в предлагаемом анализаторе. 8 большом числе применений нет необходимости иметь регулируемое разрешение (или длину анализируемого участка) для всех узлов частотной сетки О ,Ла,..., (N-1) A«J Достаточно выделить только Р некоторых узлов частотной сетки, для которых нужно получить требуемое разрешение, либо переменное значение длины анализируемого участка сигнала, отличное от всех других узлов частотной сетки. Это позволяет обеспечить получение требуемых длины и разрешения вдоль всей частотной сетки при минимальных затратах. Именно этот вариант и положен- в основу предлагаемого анализатора. Анализатор работает следующим образом. Перед началом вычислений или по У вычислений в блоке задания раз 7 вырабатываются значения номеров )Сб1К тех узлов частотной сетки,для которых необходимо получить отличные от других узлов длину участка и разрешение, и значение кода ( q) длины участка и частотного |эазрешения для каждого из выбранных узлов. Для этого в регистре 21 и регистре 23 вырабатываются (набираются, вводятся) Р значений чисел q и Р номероэ б X для выбранных узлов частотной сетки. Все Р значений чисел q и k вводятся в блок запоминания кода разрешения (БЗКР) 22 (числа q) и в блок запоминания разрешаемых частот (БЗРг) 2А (числа k), где они хранятся в течение всего периода вычислений при заданном разрешении. При этом меньшее значение ( записывается в первую ячейку BSPi 2, а соответствующее ему число q-q. в первую ячейку БЗКР 22, второе по значению число k д. и соответствующее ему число qX записываются во вторые ячейки БЗРЧ 2 и B3RP 2 и т.д., наибольшее значение kj и соответствующее ему значение qp записываются в последние, Р-ые ячейки БЗРЧ 2 и БЗКР 22 соответственно. Перед sanycKOM анализатора обнуляются многокаскадное (МЗУ) k и блок памяти JO, сумматор 9, счетчик 5. На выходе блока 2k находится число k, а на выходе блока 22 - число q,,. Коммутатор 6 включен на выход первого каскада k, МЗУ , а блок 2 - на выход блока. 1. Нормальный режим работы анализаТора начинается после вычисления блоком 1 q-oro набора коэффициентов КДПФ с момента запуска анализатора, т.е. после веыполнения N-точечного КДПФ над отсчетами xfCq-OWAt,..., xC(qN-1)AO. После вычисления первых N коэффициентов КДПА по отсчетам х(р), х(д1),..., х(М-1)д1 по сигналу синхронизатора 8 из процессора выводится первый коэффициент Х(у(0) и обнуляется счетчик 20 блика . Если нулевой узел частотной сетки не попадет в число выбранных узлов, т.е. , то компрратор 25 выработает нулевой сигнал на блоке 18, пе реключатель 2 включен на выход блока 1 и коэффициент X (о) переписан в блок обработки 3. По следующему сигналу синхронизатора 8 с выхода блока 1 считывается следующий коэффициент КДПф x CuttC) в счетчик 20 добавляется единица и он установится в состояние, соответству ющее kel. Если при этом , то так же как и в предыдущем случае, коэффициент Х0(Ш) переписывается в блок обработки 3. Аналогичным образом работает анализатор для всех k вплоть до а яакже для всех keX, т.е. для тех коэ(1к|)ициентс1В КДПФ, котбрые попадают в невыбранные узлы частотной сетки, . Пусть теперь k«k, В этом случае после очередного сигнала с выхода 19 синхронизатора 8 с выхода блока 1 считывается коэффициент Xj.j(, а счетчик 20 устанавливается в состо ние Ц, т.е. в состояние, соответ12 2 ствующее Kj - Компаратор 25 вырабатывает единичный сигнал, так как на выходе блока 2k все еще находится знаяение k. По этому сигналу из блока памяти 22 в счетчик 5 с переменным коэффициентом пересчета переписывается число q к адресам блоков 2k и 22 добавляется единица, переключатель 2 включается на выход блока 10 и единичный сигнал поступает на вход 18 : синхронизатора 8. В результате этого в СПКП 5 устанавливается коэффициент пересчета, равный q, Сам же счетчик 5 при этом обнулен, т.е. находится в состоянии д«0. На выходе блоков 2 и 22 устанавливаются значения k и , синхронизатор 8 вырабатывает сигнал записи-сдвига МЗУ , по которому коэффициент переписывается с блока 2 в последнюю Р-ую ячейку первого кас KJaдa k МЗУ Ч. По окончании перезаписи из синхронизатора 8 на синхронизирующий вход, коммутатора 6 пода ется сигнал считывания, по которому X0(kiAU)) с выхода первого каскада k МЗУ4 через коммутатор 6 поступает на вход 13 сумматора 9. Поскольку с выхода блока 10 в этом случае по дается нулевой сигнал, на выходе сумматора 9 получается значение ))« которое записывается в ОЗУ to и через переключатель 2 переписывается в блок обработки 3. После этого синхронизатор 8 подает единичный сигнал на синхронизиРУ1ПЩИЙ вход счетчика 5. Если , то счетчик 5 устанавливается в состояние «1, в результате чего коммутатор 6 подключает вход 13 сумматора 9 к выходу второго каскада k МЗУ. Поскольку с выхода этого i каскада поступает нулевой сигнал, а т: выхода блока памяти 10 x( на выходе сумматора 9 получается результат Хо(); который записывается в блок 10 и переписывается в-блок обработки 3. Так продолжается до тех пор, пока на счетный вход счетчика 5 с выхода синхронизатора 8 не поступит очерёдной (с начала считывания коэффициента X () с выхода процессора) ф-ый сигнал, по которому счетчик 5 устанавливается в нулевое состояние С)вО, коммутатор б подключается к выходу первого каскада ( МЗУ4 и нулевой сигнал счетчика 5 поступает на вход 1ь синхронизатора 8. По этому сигнал синхронизатор В вы{ абатывает очеред ной сигнал считывания очередного коэффициента х-( (lc 1 )ди;) с выхода , и 1 блока 1. Аналогично работает анализатор после считывания из процессора коэф фициента x.Q( соответствующего следующему выбранному узлу частотной сетки. При этом после перезаписи из блока памяти 22 счетчика 5 на выходе блока памяти 2 и 22 устанавливаются з.начения , в процес се записи-сдвига в МЗУ4 Xo(.A(W) записывается в последнюю ячейку пер вого каскада k МЗУ, а коэффициент Xp()) переписывается в пред последнюю ячейку каскада А. По окончании каждого суммировани в блок обработки 2 из блока 10 переписываются очередные значения, .в данном случае Xp((t, После Р-ого выбранного коэффициента Xo() на выходе БЗРг 24 и БЗКР 22 устанавливаются значения Ц., q,, коэффициент ) находится в первой ячейке, а коэффициент X (kpAUj) - в последней ячейке первого каскада kjf МЗУ4. После считывания с блока 1 после него коэффициента, например х((Н1)&(jW), и перезаписи его в блок обработки 2, анализатор готов к выводу |или к вычислению/а потом и к в воду)- следующих N коэффициентов КДП найденных по очередным N текущим от счетам сигнала xU) Работа анализатора при этом аналогична описанной. Рассмотрим поэтому нормальный режим, когда число m участков x(t), по которым находятся коэффициенты КДПФ, не меньше max 0/., keX. Пусть, например, . В этом случае перед выводом очередных JN коэффициентов КДПФ X(,(), k 0;N-1 полученных по отсчетам x((m-1)N/it), x((m-1)Nt1)At),... ,x(CmN-l3ut) сигнала x{t), в первом каскаде МЗУ хранятся предыдущие коэффициенты xY(kAtw), keX, во втором каскаде .,(k&a), k€X, в последнем п-ом каскаде -XMikutw), keX. При этом в Р-ой ячейке (,2,... ,Р) (q-fl-or каскада (v,,1,.. .,п-1) МЗУ хранится коэффициент Хл . .(kftiU;) . Здесь, как и ранее, (-множество номеров выбранных узлов в мастот.ной сетке, р-номер Р-ого по поряд ку возрастания номеров выбранного узла частотной сетки. Перед началом вывода из блока 1 очередных коэффициентов XQ(kACl), ,N-l анализатор устанавливается в исходное состояние, в котором обнулены счетчик 5 блок памяти 10, сумматор 9 (если он накапливающий, а не комбинационный). На выходе блока памяти 2k находится число k; , а на выходе блока 22 - число q., соответствующие наименьшему номеру узла частотнойсетки. Коммутатор б включен на выход первого каскада k MSyit, Вывод коэффициентов x(ku(l;), ,N-1, изблока 1 начинается по единичному сигналу синхронизатора В. По этому сигналу обнуляется счетчик 20 БЭР 7 и из процессора выводится первый коэффициент х(0). Если k.yn, то компаратор 25 выработает нулевой сигнал на управляющем выходе 18 блока 7. В результате этого переключатель 2 включен на выход блока 1 и по сигналу синхрониг затора В, поступающему на синхронизирующие входы переключателя 2 и блока обработки 3, коэффициент. Хо(о) переписывается в блок обработки 3. По следующему сигналу синхронизатора 8 с выхода 1 преобразователя Фурье считывается следующий коэффициент КДПФ ), в счетчик 20 добавляется единица и он устанавливается в .состояние k l ( в состоя. - / ние, соответствующее ). Если при этом k 1, то также как. и в предыдущем случае, коэффициент . Xjj(iU)) переписывается в блок обработки 3 в котором над введенными коэффициентами осуществляются преобразования, определяемые типом искомой спектральной характеристики. Аналогично анализатор работает для всех keX, т.е. для тех коэффициентов КДПФ, которые попадают в выбранные узлы частотной сетки1 Пусть теперь ., т.е. после очеедного сигнала синхронизатора 8 четчик 20 ВЗР 7 устанавливается в остояние Ц и с выхода блока 1 счиывается коэффициент Хр (k дйг) .В . этом случае компаратор 25 БЭР 7 ырабатывает единичный сигнал на упавляющем выходе 18 блока 7, так как а вь1ходе блока 2k при этом все еще аходится значение k . 15 ,1 По этому сигналу из блока памяти 2 в сметчик перезаписывается число (j, , определяющее число участков л, по которым находится коэффициент КДПФ, для выбранного узла частот ной сетки с номером Ц( . К блоков памяти 22 и 2.k добавляется единица, переключатель 2 включен (по сигналу управляющего вхо да) на выход ОЗУ 10 и единичный сиг нал поступает по/шине 18 на вход синхронизатора 8. В результате этого в счетчике 5 у тановлен коэффициент пересчета, равный q. Сам жесчетчик 5 при этом находится в нулевом состоянии . На выходе БЗРГ 2 и БЗКР 22 устанавл ваются следующие по порядку номеров з/«ачения kjj, q. Синхронизатор 8 вырабатывает сигнал записи-сдвига в МЗУ, по которому коэффициент Хр(ЦД(1)) переписывается из блока 1 в последнюю ячейку первого каскада k МЗУ, коэффициенты xx CkpAOiJ для ,3,... Р переписываются из ячеек (д+1 )-ых каскадов 4д4-МЗУ в {Р-1)-ыё ячейки, а коэффициенты (k|A№) переписываются из первой (q4-i)-oro каскада в последнюю ячейку (q-J-2)-oro каскада МЗУ. Коэффициент x,,() при этом потерян, вытолкнут из п-ого каскада. Таким образом на вцходе (q+1)-opo каскада МЗУЙ (,1,..., п-1) после записи сдвига в МЗУ хранятся коэффи циенты Xn(). По окончании перезаписи из синх ронизатора 8 на синхронизирующие входы коммутатора 6, сумматора 9 и блока 10 подается единичный сигнал, по которому ) с выхода первого каскада ц. iisyif через коммутатор 6 поступает на вход 13 сумматора 9 просуммируется с содержимым блока 10 (в данном случае 0) и результат Суммирования запишется в блок 10. После .этого по сигналу синхронизатора 8, поступающему на синхронизирующие вхо ды переключателя 2 и блока обработки 3 содержимое блока 10, т. е. х ( k Ad) переписывается в блок обработки 3, ;в котором над данным коэффициентом XgCk) проводится необходимая .обработка и вывод результата. Затем синхронизатор 8 подает еди;нйчный сигнал на синхронизирующий (счетный) вход СПКП 5. Если q.jil, то СПКП 5 устанавливается в состояние , в результате чего коммута-. 82 : тор 6 подключаетсвход t3 сумматора 9 к выходу второго каскада k МЗУ, Поскольку в это время в ОЗУ 10 хранится результат предыдущего сумг 1рования, а именно ), то после суммирования, аналогично описанному, в ОЗУ 10 хранится а в блок обработки переписывается сумма Хр( x,j(kjia|), первое слагаемое которой соответствует последним N отсчетам сигнала x(t), а второе слагаемое - предшествующим им М от- счетам., Так продолжается работа анализатора вплоть до установки СПКП 5 в состояние -1. В результате в ОЗУ 10 в блокобраех тки 3 поступает 4П - значение суммы х (kM)).. .). -- - ( При этом в блок обработки поступают коэффициенты КДПФ, получаемые по последовательно увеличивающимся на участкам сигнала x(t) с обратным счетом времени. После сцедующего сигнала синхронизатора 8, поступающего на счетный вход СПКП 5, счетчик 5 устанавлива-v ется в нулевое состояние д«0, коммутатор 6 поделючается вновь к выходу первого каскада k МЗУ, и нулевой сигнал СПКП 5 поступает на вход синхронизатора 8 по шине 16 .По этоиу .сигналу синхронизатор 8 вырабатывает очередной сигнал считывания очередного коэффициента X (P f1jfia) с выхода процессора 1. . Аналогично работает анализатор при других keX . Таким образом для выбранных узлов частотной Сетки обеспечивается последовательное увеличение длины . участка сигнала x(t) , по которому анализируется спектр: вначале вычисляются, об{ абатываются и выводятся коэффициенты КДПФ) найденные по. участку Om-l)NAt, (Ш-1)мЗ сигнала x(t), затем КДПФ, найденные в тех ле узлах частотной сетки, но на-участке Пго-2)МЛ1, (mN-Oat, и т.д,, наконец , найденные на участке )Ndt, (nW-l)Atl, где q знаяение, заданное для данного выбранного узла частотной сетки Поскольку частотное разрешение определяется длиной у«)астка, по которому анализируется спектр сигнала, это приводит автоматически к последовательному улучшению разрешения согласно длинам участков NAt, 2H&t,.I qNAtv.Такая организация спектрального анализа позволяет проследить за нестационарностью сигнала, выявить наилучшее в определенном смысле соотношение между возможным интервалом нестационарности и интервалом анализа, обеспечить требуемое частотное разрешение без повторного просчета спектра, оперативно, сразу же после вычисления очередной партии из N коэффициентов КДПФ до вычисления следующей партии N коэффициентов КДПФ. Тем самым обеспечивается достижение поставленной цели. Соглано приведенным схемам и описанию к ним, все дополнительные элементы анализатора могут быть легко реализованы на серийных элементах вычислительной техники. Для значений п, Р, определяемых неравенством , затраты на дополнительные элементы анализатора, составляют ориентировочно +10 от затрат на анализаторпрототип.

W О-

20

11

22

21

-3

| название | год | авторы | номер документа |

|---|---|---|---|

| Анализатор мгновенного спектра | 1979 |

|

SU849225A1 |

| Анализатор спектра | 1979 |

|

SU851280A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Устройство для вычисления спектра сигналов | 1989 |

|

SU1667102A1 |

| Устройство для решения дифференциальных уравнений в частных производных | 1990 |

|

SU1734103A1 |

| Способ анализа спектра сигналов и устройство для его осуществления | 1988 |

|

SU1573432A1 |

| Статистический анализатор | 1985 |

|

SU1280395A1 |

| Устройство для быстрого преобразования Фурье | 1983 |

|

SU1130872A1 |

| Анализатор спектра Фурье | 1984 |

|

SU1226486A1 |

| Статистический анализатор | 1986 |

|

SU1354211A1 |

15

2(1fj

/2f

12,

та

Пп

13

Авторы

Даты

1983-07-15—Публикация

1980-12-12—Подача