Изобретение относится к цифровой вычислительной технике и может быть использовано при решении дифференциальных уравнений в частных производных параболического типа, например при решении диффузионного уравнения Фоккера-План- ка.

Известно устройство для решения дифференциальных уравнений в частных произ- водных, реализующее конечно-разностную схему.

Недостатком устройства является низкое быстродействие. Решение подобной задачи на ЭВЦМ ЕС-1022 методом конечно-разностных схем на время п 1 (время безразмерное ti a t) с шагом по времени г 2 занимает около 70 мин,

Известно оптическое вычислительное устройство, предназначенное для решения дифференциальных уравнений в частных производных параболического типа, в котором взятие частной производной по временной координате осуществляется на основе разностной схемы Эйлера, а взятие частных производных по пространственным координатам осуществляется в частотной области умножением получаемого Фурье-образа на q-ю степень j о). Данное устройство обеспечивает высокое быстродействие, однако трудно реализуемо на практике (так как применяемые оптические элементы - динамические транспаранты, Фурье-преобразующие элементы, процес- соры пространственно-частотной фильтрации и др. - устройства дорогостоящие, громоздкие, большие сложности возникают при их юстировке, настройке и т.д.). Кроме того, использование вышеназванных опти- ческих элементов вносит также большие погрешности в вычисления. Например, погрешности, возникающие только в оптических процессорах пространственно-частотной фильтрации, достигают нескольких единиц и даже десятка процентов,

Наиболее близким по технической сущности к предлагаемому является устройство для решения дифференциальных уравне- ний в частных производных, содержащее N- канальные (где N - размер аппроксимирующей сетки по пространственной координате) блоки (группы): коммутатор, блок регистров, первый, второй и третий блоки умножителей, первый и второй блоки быстрого преобразования Фурье, первый и второй блоки умножителей комплексных чисел, блок сумматоров комплексных чисел,

блок обратного быстрого преобразования Фурье, блок накапливающих сумматоров, блок элементов И, а также блок памяти и блок управления, причем первые информационные входы коммутатора и блока элементов И являются информационным входом устройства, выход коммутатора подключен к входу блока регистров, выход которого соединен с первыми входами первого и второго блоков умножителей, вторые входы которых подсоединены соответственно к первому и второму выходам блока памяти, выходы первого и второго блоков умножителей соединены соответственно с входами первого и второго блоков быстрого преобразования Фурье, выходы которых соединены с первыми входами соответственно первого и второго блоков умножения комплексных чисел, вторые входы которых соединены соответственно с третьим и четвертым выходами блока памяти, выходы первого и второго блоков умножителей комплексных чисел соединены соответственно с первым и вторым входами блока сумматоров комплексных чисел, выход которого соединен с входом обратного быстрого преобразования Фурье, выход которого подключен к первому входу третьего блока умножителей, второй вход третьего блока умножителей соединен с пятым выходом блока памяти, выход третьего блока умножителей соединен с первым входом блока сумматоров-накопителей, второй вход которого подключен к выходу блока элементов И, выход блока сумматоров-накопителей соединен с вторым входом коммутатора и является также выходом устройства, первый управляющий выход блока управления подключен к управляющему входу коммутатора и второму входу блока элементов И, второй, третий и четвертый выходы блока управления соединены соответственно с первым, вторым и третьим управляющими входами блока памяти.

Недостатком устройства является низкая точность численного интегрирования дифференциальных уравнений в частных производных вследствие того, что используемая по временной координате разностная схема Эйлера является схемой первого порядка точности.

Цель изобретения - повышение точности решения дифференциальных уравнений в частных производных за счет использования для вычисления частной производной по временной координате разностной схемы Рунге-Кутта четвертого порядка точности,

Поставленная цель достигается тем, что в устройство, содержащее N-канальные блоки: коммутатор, регистр, первый, второй и третий умножители, первый и второй блоки быстрого преобразования Фурье, пер- вый и второй умножители комплексных чисел, сумматор комплексных чисел, блок обратного преобразования Фурье, накапливающий сумматор, а также блок регистров и блок микропрограммного управления, введен второй коммутатор, причем выходы с первой по четвертую групп блока регистров подключены соответственно к первым информационным входам групп второго умножителя, первого умножителя комплексных чисел и первого умножителя комплексных чисел, выходы пятой группы блока регистров подключены к первым информационным входам группы накапливающего сумматора и к информационным входам первой группы первого коммутатора, выходы которого подключены соответственно к информационным входам регистра, выходы которого подключены к вторым информационным входам группы первого умножителя и к вто- рым информационным входам группы второго умножителя, выходы которого подключены соответственно к входам второго блока быстрого преобразования Фурье, выходы первого умножителя под- ключейы соответственно к входам первого блока быстрого преобразования Фурье, выходы первого и второго блоков быстрого преобразования Фурье подключены соответственно к вторым информационным вхо- дам групп первого и второго умножителей комплексных чисел, выходы которых подключены соответственно к первому и второму информационным входам группы сумматора комплексных чисел, выходы ко- торого подключены соответственно к входам блока обратного преобразования Фурье, выходы которого подключены к информационным входам второй группы первого коммутатора и к первым информационным входам группы третьего умножителя, выходы которого подключены к вторым информационным входам группы накапливающего сумматора, выходы которого подключены к выходам результата уст- ройства и к информационным входам третьей группы первого коммутатора, вход запуска устройства подключен к входу режима блока микропрограммного управления, первый выход которого подключен к первому управляющему входу первого коммутатора и к первому входу записи/считывания блока регистров, второй выход блока микропрограммного управления подключен ко входу записи/считывания регистра и ко

второму входу записи/считывания блока регистров, третий и четвертый выходы блока микропрограммного управления подключены соответственно к третьему входу записи- считывания блока регистров и к второму управляющему входу первого коммутатора, пятый выход блока микропрограммного управления подключен к четвертому входу записи-считывания блока регистров и к первому управляющему входу второго коммутатора, выход которого подключен к вторым информационным входам группы третьего умножителя, шестой выход блока микропрограммного управления подключен к пятому входу записи-считывания блока регистров и к второму управляющему входу второго коммутатора, седьмой выход блока микропрограммного управления подключен к шестому входу записи-считывания блока регистров и ктретьему управляющему входу второго коммутатора, восьмой выход блока микропрограммного управления подключен к четвертому управляющему входу второго коммутатора и к седьмому входу записи-считывания блока регистров, выходы с первого по четвертый которого подключены соответственно к информационным входам с первого по четвертый второго коммутатора, девятый выход блока микропрограммного управления подключен к третьему управляющему входу первого коммутатора и к управляющему входу накапливающего сумматора.

Введение дополнительного блока (коммутатора) позволяет получать более точное решение уравнения Фоккера-Планка

aw (x.t) .(x)W(x.t)

+ LW(x,t), (1)

где W(x, t) - одномерная плотность вероятности скалярного марковского процесса x(t) (искомая функция);

Ki(x) - стационарный коэффициент сноса;

Ка(х) - стационарный коэффициент диффузии;

Ц } - оператор Фоккера-Планка.

Рекуррентное представление (1) на основе метода Рунге-Кутта имеет вид

Wm+i(x) Wm(x) + (x) + 2 К2(х) + 2 Кз(х)

+ ВД,(2)

т 0, 1, 2

где Wm(x) и Wm+i(x) - значения функции W(t, х) соответственно на m-м и (т+1)-м шагах вычислений;

Ki(x), (i 1,4)- коэффициенты, подлежащие определению, которые в соответствии с уравнением (1) вычисляются следующим образом:

К1(х) (х) (3)

K2(x) L{Wm(x) + L Щ& Т4

K3(x) L{Wm(x)} + L гг

ОД L{Wm(x)} + ЦКз(х)} г. Путем несложных преобразований с учетом свойства линейности оператора Фокке- ра-Планка итерационный алгоритм (2) приводится к виду

Wm+l(x) 2 LV Wm (x) ,(4)

V 0Vft.

где LM {Wm(x) - L{LVl}{Wm(x)}} L {L {WmM}} и т.д.;

(x}} Wm(x), (x)} L{W4x);

L{ 1}{L{1}{Wm(x)}} Wm(x).

С помощью теоремы отсчетов Котельни- кова и представления функции Wm(x) совокупность N отсчетов по пространственной координате уравнение (4) может быть записано следующим образом:

w- hbS|bP%U{(ib4w

KftHwin(nb)-jkuuFllw kt(nhlWni(«hD,

m.0.1,2,...,

n 0,N-l , k O.N-( ,

где n - номер отсчета-функции Wm(x) no пространственной координате х;

h - шаг дискретизации Wm(x) по пространственной координате х;

Рдпф и Рдпф - операторы прямого и обратного дискретного преобразования Фурье (ДПФ), которые для произвольной функции g(nh) и ее спектрального аналога G(k Aw) определяются парой взаимнообрат- ных преобразований:

FAnVh))exp( п-о /

(HTHQ((ifk

где k - номер отсчета спектрального аналога функции g(nh);

До - шаг дискретизации ее по пространственной частоте.

Так, например, для нахождения Wi(nh) по формуле (4) с учетом (5) необходимо выполнить следующие вычисления:

) М

T«LW{we((nhf}4

Л4

0

5

0

5

0

5

0

5

0

5

-Н , rAeL Hb F fijik F blW.lnh.

-i oW iHweinhio.

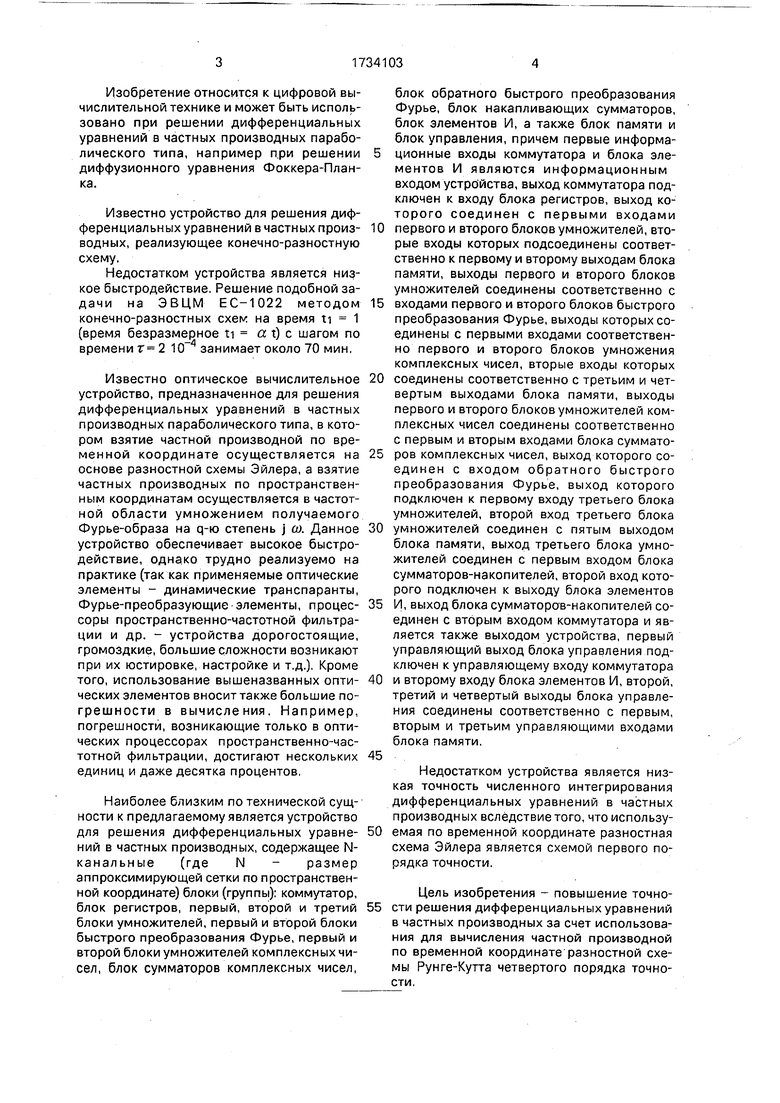

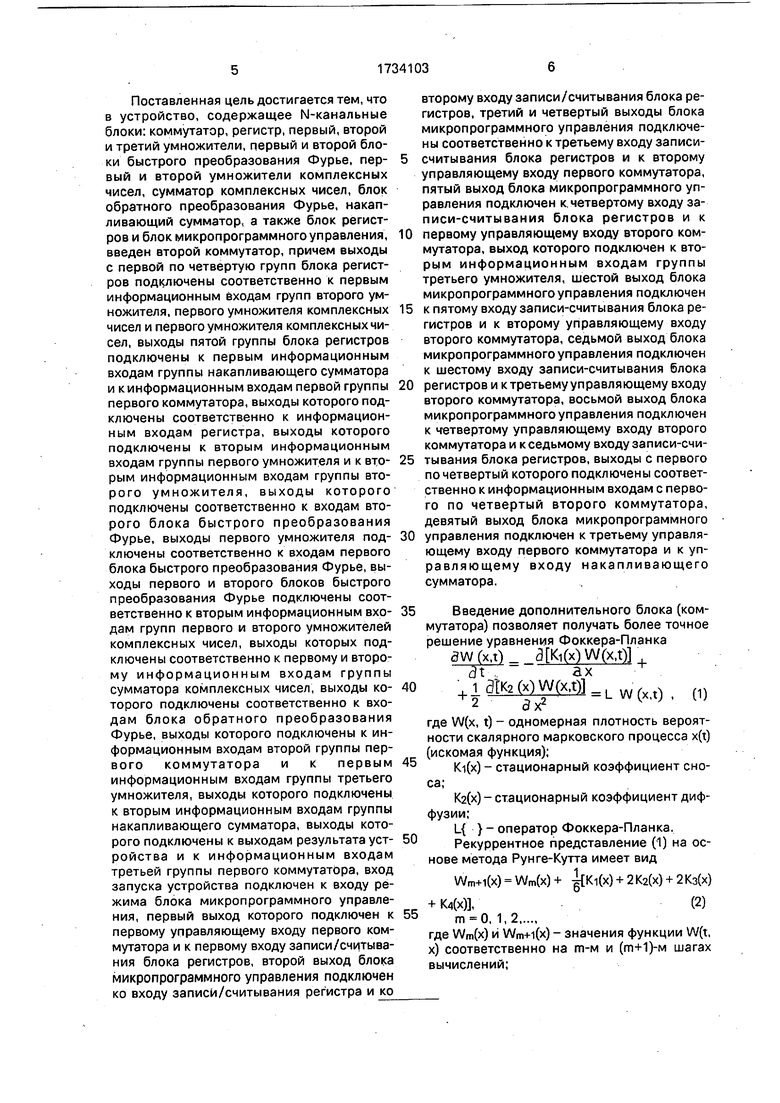

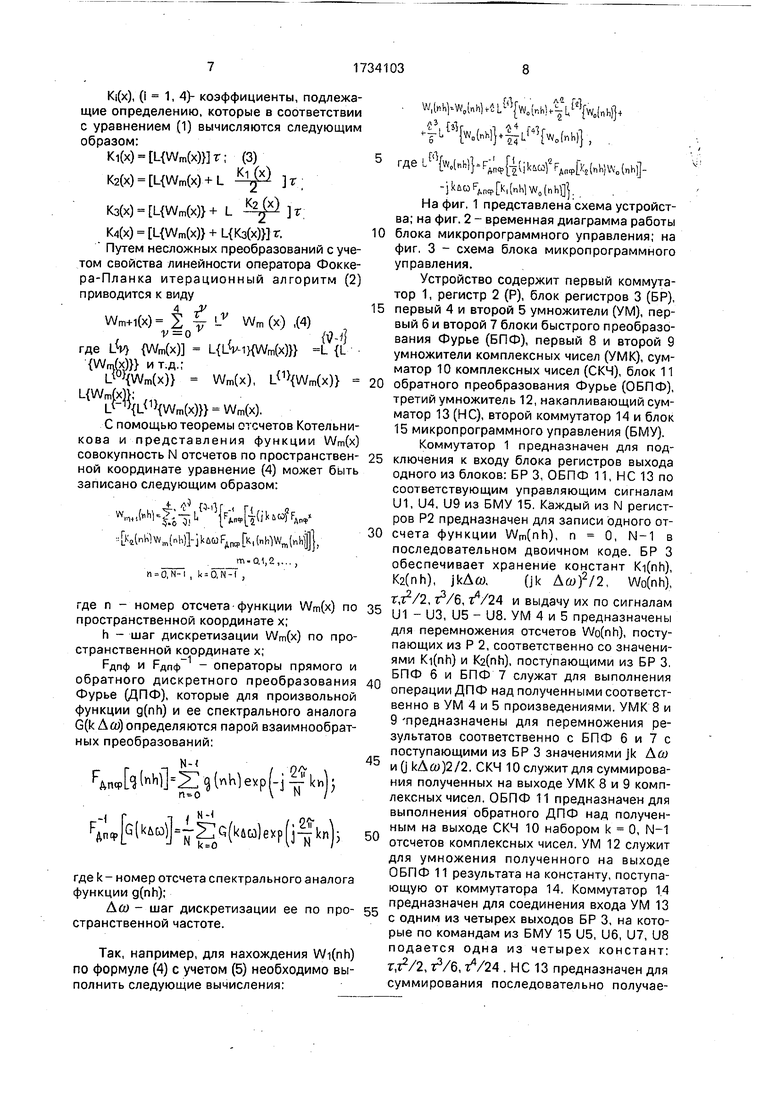

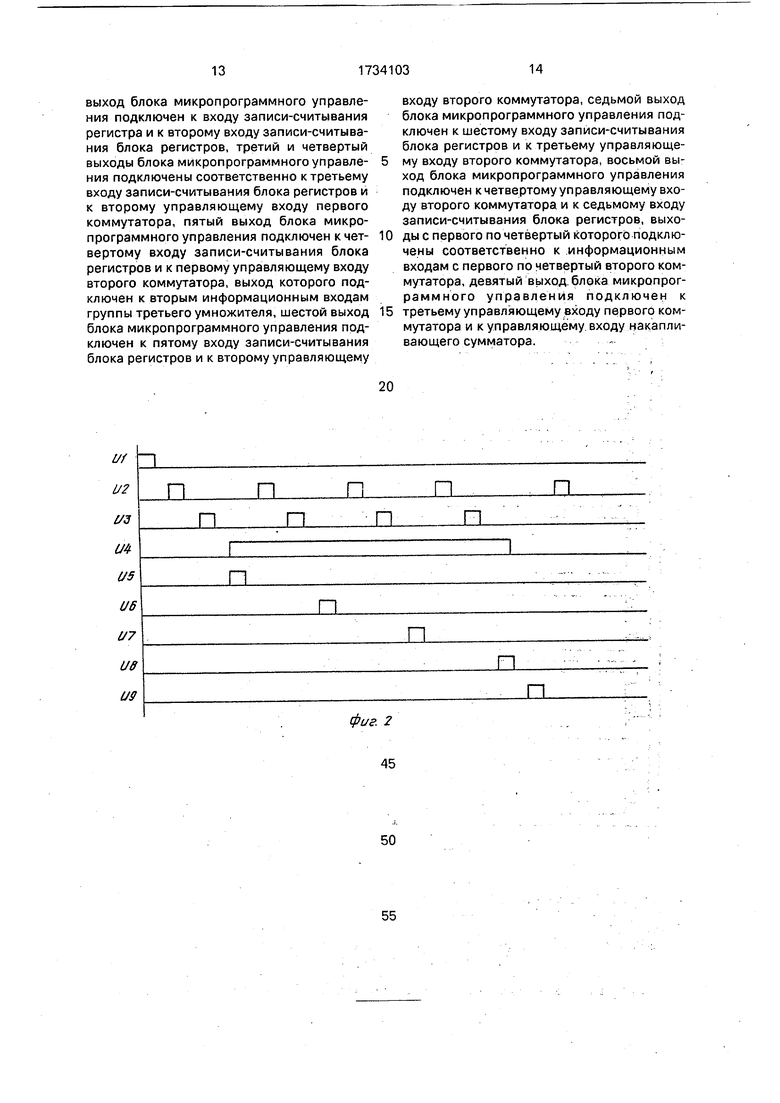

На фиг. 1 представлена схема устройства; на фиг. 2 - временная диаграмма работы блока микропрограммного управления; на фиг. 3 - схема блока микропрограммного управления.

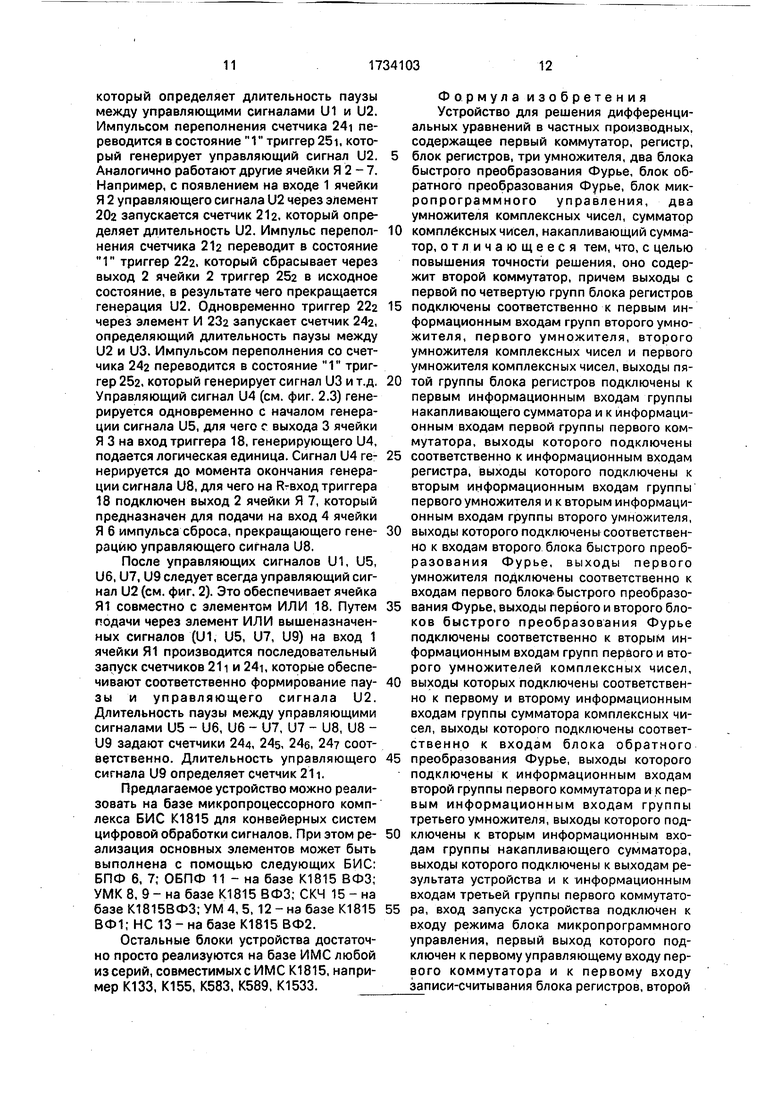

Устройство содержит первый коммутатор 1, регистр 2 (Р), блок регистров 3 (БР), первый 4 и второй 5 умножители (УМ), первый 6 и второй 7 блоки быстрого преобразования Фурье (БПФ), первый 8 и второй 9 умножители комплексных чисел (УМК), сумматор 10 комплексных чисел (СКЧ), блок 11 обратного преобразования Фурье (ОБПФ), третий умножитель 12, накапливающий сумматор 13 (НС), второй коммутатор 14 и блок 15 микропрограммного управления (БМУ).

Коммутатор 1 предназначен для подключения к входу блока регистров выхода одного из блоков: БР 3, ОБПФ 11, НС 13 по соответствующим управляющим сигналам U1, U4, U9 из БМУ 15. Каждый из N регистров Р2 предназначен для записи одного отсчета функции Wm(nh), n О, N-1 в последовательном двоичном коде. БР 3 обеспечивает хранение констант Ki(nh), K2(nh), jkAtt), (jk Aw)2/2, Wo(nh),

т,, , zV24 и выдачу их по сигналам U1 - U3, U5 - U8. УМ 4 и 5 предназначены для перемножения отсчетов Wo(nh), поступающих из Р 2, соответственно со значениями Ki(nh) и K2(nh), поступающими из БР 3. БПФ 6 и БПФ 7 служат для выполнения операции ДПФ над полученными соответственно в УМ 4 и 5 произведениями. УМК 8 и 9 предназначены для перемножения результатов соответственно с БПФ 6 и 7 с поступающими из БР 3 значениями jk Aft) n(jkAcy)2/2. СКЧ 10 служит для суммирования полученных на выходе УМК 8 и 9 комплексных чисел. ОБПФ 11 предназначен для выполнения обратного ДПФ над полученным на выходе СКЧ 10 набором k О, N-1 отсчетов комплексных чисел. УМ 12 служит для умножения полученного на выходе ОБПФ 11 результата на константу, поступающую от коммутатора 14, Коммутатор 14 предназначен для соединения входа УМ 13 с одним из четырех выходов БР 3, на которые по командам из БМУ 15 U5, U6, U7, U8 подается одна из четырех констант:

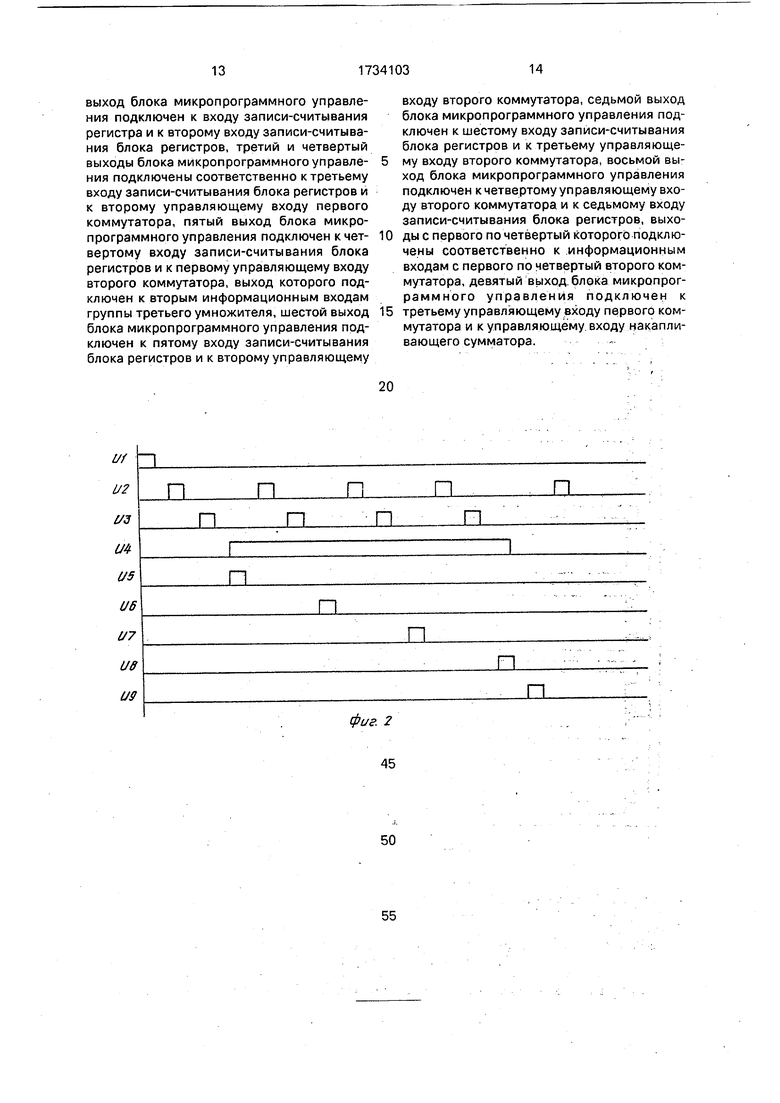

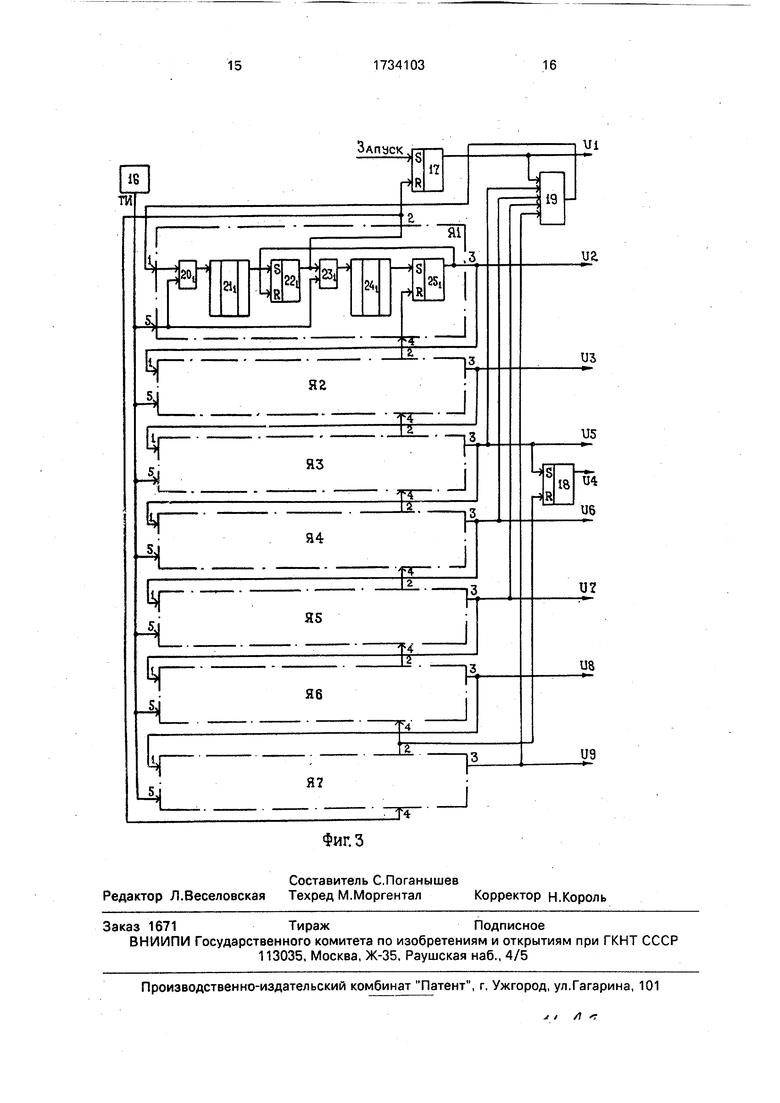

r,TV2, гУб, //24 . НС 13 предназначен для суммирования последовательно получавмых друг за другом слагаемых выражения (8). БМУ 15 собран на основе набора триггеров, счетчиков, логических элементов И или ИЛИ (см. фиг. 3) и предназначен для выработки в соответствии с временной диаграммой (фиг. 2) управляющих сигналов U1 - U9.

Устройство работает следующим образом.

В исходном состоянии все триггеры и счетчики блоков находятся в нулевом состоянии, во всех разрядах всех регистров записаны нули, в БР 3 записаны константы: Ki(nh), K2(nh), jkAcy, (jkAw)2/2, Wo(nh),

т,, гУб, //24.

По сигналу Запуск БМУ 15 генерирует управляющий сигнал U1, который подается в коммутатор 1, в результате чего вход Р2 подключается к пятому выходу БР 3, а также в БР 3, в результате чего исходная Wo(nh) переписывается с пятого выхода БР 3 в Р2. Одновременно значения Wo(nh) переписываются в НС 13, который находится в режиме суммирования с накоплением. Затем по сигналу U2, поступающему на второй управляющий вход БР 3 и на управляющий вход Р2, с второго и первого выходов БР 3 в БУМ 4 и 5 соответственно выдаются значения Ki(nh) и Ка(пЬ) для перемножения с поступающим из переводимого сигналом U2 в режим считывания Р 2 значением Wo(nh). Результаты умножения с каждого из блоков УМ 4 и УМ 5 поступают соответственно в БПФ 6 и 7 для выполнения операций ДПФ. С выходов БПФ 6 и 7 по N спектральных комплексных коэффициентов с каждого поступают на вторые входы УМК 8 и 9, на первые входы которых по управляющему сигналу U3 из БМУ 15 с четвертого и третьего выходов БП 3 выдаются соответственно константы jk АСУ и (jk Aft))2/2.

Результат умножения из УМК 8 и 9 поступает для поразрядного сложения в СКЧ 10 и далее на входы N точечного ОБПФ 11. Полученное на выходе ОБПФ 11 выражение {Wo(nh)} поступает для записи в Р2 через коммутатор 1, который по управляющему сигналу U4 соединяет выход ОБПФ 11с входом Р 2, а также подается на вход УМ 3 для умножения на константу т, поступающую с шестого выхода БР 3 (в результате подачи на четвертый управляющий его вход сигнала U 5) через коммутатор 14, который по управляющему сигналу U5 из БМУ 15 соединяет шестой выход БР 3 с входом УМ 12. Полученное после перемножения второе слагаемое выражения (8) поступает с выхода УМ 12 на второй вход НС 13, где производится суммирование его с ранее записанным в НС 13 первым слагаемым выражения

(8). Аналогично по управляющим сигналам U2, U3, U4, U6, U7, U8 (см. временную диаграмму фиг. 2) последовательно друг за другом формируются третье, четвертое и пятое слагаемые выражения (8). Отличив состоит в том, что при формировании третьего слагаемого выражения (8) умножение в УМ 12

производится на константу тг/2, поступающую с седьмого выхода БР 3 через коммута- тор 14 при подаче на него и на пятый управляющий вход БР 3 управляющего сигнала U6. При формировании четвертого слагаемого выражения (8) по сигналу U7 с восьмого выхода БР 3 на УМ 12 через коммутатор 14 подается константа г /6. При формировании пятого слагаемого выражения (8) по сигналу U8 с девятого выхода БР 3 на УМ 12 через коммутатор 14 подается

0 константа г4/24. В конце первого шага вычислений в НС 13 сформировано Значение Wi(nh) в соответствии с выражением (8). Второй и последующий шаги вычислений аналогичны первому. Отличие состоит в том,

5 что вместо управляющего сигнала U1 в начале каждого последующего шага выдается управляющий сигнал U9, котррый поступает на управляющий вход НС 13(для перевода его в режим считывания) и на третий управ0 ляющий вход коммутатора f (для подключения выхода НС 13 к входу Р2), в результате чего полученное на предыдущем шаге значение Wm(nh) выдается на выход устройства и одновременно переписывается в Р2 с

5 целью использования его в качестве исходного на (т+1)-м шаге вычислений.

БМУ 15 содержит генератор 16 тактовых импульсов (ГТИ), первый 17 и второй 18 триггеры, элемент ИЛИ 19, с первой по седь0 мую ячейки Я 1 - 7, каждая из которых состоит из первого 20i и второго 23i элементов И, первого 21i и второго 24i счетчиков, первого 22| и второго 25( триггеров (i 1-7) Блок БМУ 15 работает следующим обра5 зом.

По сигналу Запуск триггер 17 переводится в состояние 1 и генерирует управляющий сигнал U1. Одновременно с появлением U1 логическая 1 через эле0 мент ИЛИ 19 и элемент И 20i запускает счетчик 211, который определяет длительность управляющего сигнала U1: импульс переполнения счетчика 211 переводит в состояние 1 триггер 22i, который, в свою

5 очередь, осуществляет сброс триггера 17 в исходное состбяние О. Кроме того, логическая единица с выхода триггера 221 поступает на один из входов элемента И 23ч, разрешая подачу через второй его вход тактовых импульсов с ГТИ 16 на счетчик 24i,

который определяет длительность паузы между управляющими сигналами U1 и U2. Импульсом переполнения счетчика 24i переводится в состояние 1 триггер 251, который генерирует управляющий сигнал U2. Аналогично работают другие ячейки Я 2 - 7. Например, с появлением на входе 1 ячейки Я 2 управляющего сигнала U2 через элемент 202 запускается счетчик 212, который определяет длительность U2. Импульс переполнения счетчика 212 переводит в состояние 1 триггер 222, который сбрасывает через выход 2 ячейки 2 триггер 252 в исходное состояние, в результате чего прекращается генерация U2. Одновременно триггер 222 через элемент И 232 запускает счетчик 242, определяющий длительность паузы между U2 и U3. Импульсом переполнения со счетчика 242 переводится в состояние 1 триггер 252. который генерирует сигнал U3 и т.д. Управляющий сигнал U4 (см. фиг. 2.3) генерируется одновременно с началом генерации сигнала U5, для чего с выхода 3 ячейки Я 3 на вход триггера 18, генерирующего U4, подается логическая единица. Сигнал U4 генерируется до момента окончания генерации сигнала U8, для чего на R-вход триггера 18 подключен выход 2 ячейки Я 7, который предназначен для подачи на вход 4 ячейки Я 6 импульса сброса, прекращающего генерацию управляющего сигнала U8.

После управляющих сигналов U1, U5, U6, U7, U9 следует всегда управляющий сигнал U2 (см. фиг. 2). Это обеспечивает ячейка Я1 совместно с элементом ИЛИ 18. Путем подачи через элемент ИЛИ вышеназначенных сигналов (U1, U5, U7, U9) на вход 1 ячейки Я1 производится последовательный запуск счетчиков 211 и 24i, которые обеспечивают соответственно формирование пау- зы и управляющего сигнала 112. Длительность паузы между управляющими сигналами U5 - U6, U6 - U7, U7 - U8, U8 - U9 задают счетчики 244, 24s, 24e, 24 соответственно. Длительность управляющего сигнала U9 определяет счетчик 21 ч.

Предлагаемое устройство можно реализовать на базе микропроцессорного комплекса БИС К1815 для конвейерных систем цифровой обработки сигналов. При этом реализация основных элементов может быть выполнена с помощью следующих БИС: БПФ 6, 7; ОБПФ 11 - на базе К1815 ВФЗ; УМК 8, 9 - на базе К1815 ВФЗ; СКЧ 15 - на базе К1815ВФЗ; УМ 4, 5, 12 - на базе К1815 ВФ1; НС 13 - на базе К1815 ВФ2.

Остальные блоки устройства достаточно просто реализуются на базе ИМС любой из серий, совместимых с ИМСК1815, например К133, К155, К583, К589, К1533.

Формула изобретения Устройство для решения дифференциальных уравнений в частных производных, содержащее первый коммутатор, регистр,

блок регистров, три умножителя, два блока быстрого преобразования Фурье, блок обратного преобразования Фурье, блок микропрограммного управления, два умножителя комплексных чисел, сумматор

0 комплексных чисел, накапливающий сумматор, отличающееся тем, что, с целью повышения точности решения, оно содержит второй коммутатор, причем выходы с первой по четвертую групп блока регистров

5 подключены соответственно к первым информационным входам групп второго умножителя, первого умножителя, второго умножителя комплексных чисел и первого умножителя комплексных чисел, выходы пя0 той группы блока регистров подключены к первым информационным входам группы накапливающего сумматора и к информационным входам первой группы первого коммутатора, выходы которого подключены

5 соответственно к информационным входам регистра, выходы которого подключены к вторым информационным входам группы первого умножителя и к вторым информационным входам группы второго умножителя,

0 выходы которого подключены соответственно к входам второго блока быстрого преобразования Фурье, выходы первого умножителя подключены соответственно к входам первого блока быстрого преобразо5 вания Фурье, выходы первого и второго блоков быстрого преобразования Фурье подключены соответственно к вторым информационным входам групп первого и второго умножителей комплексных чисел,

0 выходы которых подключены соответственно к первому и второму информационным входам группы сумматора комплексных чисел, выходы которого подключены соответственно к входам блока обратного

5 преобразования Фурье, выходы которого подключены к информационным входам второй группы первого коммутатора и к первым информационным входам группы третьего умножителя, выходы которого под0 ключены к вторым информационным входам группы накапливающего сумматора, выходы которого подключены к выходам результата устройства и к информационным входам третьей группы первого коммутато5 ра, вход запуска устройства подключен к входу режима блока микропрограммного управления, первый выход которого подключен к первому управляющему входу первого коммутатора и к первому входу записи-считывания блока регистров, второй

выход блока микропрограммного управления подключен к входу записи-считывания регистра и к второму входу записи-считывания блока регистров, третий и четвертый выходы блока микропрограммного управления подключены соответственно к третьему входу записи-считывания блока регистров и к второму управляющему входу первого коммутатора, пятый выход блока микропрограммного управления подключен к четвертому входу записи-считывания блока регистров и к первому управляющему входу второго коммутатора, выход которого подключен к вторым информационным входам группы третьего умножителя, шестой выход блока микропрограммного управления подключен к пятому входу записи-считывания блока регистров и к второму управляющему

0

входу второго коммутатора, седьмой выход блока микропрограммного управления подключен к шестому входу записи-считывания блока регистров и к третьему управляющему входу второго коммутатора, восьмой выход блока микропрограммного управления подключен к четвертому управляющему входу второго коммутатора и к седьмому входу записи-считывания блока регистров, выходы с первого по четвертый которого подключены соответственно к информационным входам с первого по четвертый второго коммутатора, девятый выход блока микропрог- раммного управления подключен к третьему управляющему входу первого коммутатора и к управляющему входу накапливающего сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Субоптимальный нелинейный фильтр | 1990 |

|

SU1714618A1 |

| Устройство для решения дифференциальных уравнений в частных производных | 1987 |

|

SU1525715A1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1988 |

|

SU1640710A1 |

| Устройство для реализации двумерного быстрого преобразования фурье | 1983 |

|

SU1142845A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1985 |

|

SU1337904A1 |

| Устройство для быстрого преобразования Фурье | 1983 |

|

SU1130872A1 |

| Цифровой анализатор спектра | 1985 |

|

SU1256044A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1985 |

|

SU1312611A1 |

| Анализатор спектров | 1982 |

|

SU1023341A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано при разработке и конструировании специализированных устройств, предназначенных для решения дифференциальных уравнений в частных производных параболического типа. Цель изобретения - повышение точности решения дифференциальных уравнений в частных производных за счет использования для вычисления частной производной по временной координате разностной схемы Рунге- Кутга четвертого порядка точности. Устройство содержит первый коммутатор 1, регистр 2, блок регистров 3, первый и второй умножители 4 и 5, первый и второй блоки быстрого преобразования Фурье 6 и 7, первый и второй умножители комплексных чисел 8 и 9, сумматор 10 комплексных чисел, блок 11 обратного преобразования Фурье, третий умножитель 12, накапливающий сумматор 13, второй коммутатор 14 и блок 15 микропрограммного управления. 3 ил. СП с VI CJ о со

П

П

П

П

П

П

И

П

П

П

П

П

П

фиг 2

Фиг.З

Составитель С.Поганышев Редактор Л.Веселовская Техред М.МоргенталКорректор н.Король

Заказ 1671ТиражПодписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат Патент, г, Ужгород, ул.Гагарина, 101

| Устройство для решения дифферен-циАльНыХ уРАВНЕНий B чАСТНыХ пРОиз-ВОдНыХ | 1979 |

|

SU807319A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Хуторцев В.В., Таран В.Н | |||

| Использование сплайнов для исследования алгоритмов нелинейной фильтрации | |||

| - Радиотехника и электроника, 1986, т | |||

| Способ очистки нефти и нефтяных продуктов и уничтожения их флюоресценции | 1921 |

|

SU31A1 |

| Клапан с автоматическим запиранием | 1924 |

|

SU2180A1 |

| Оптическое вычислительное устройство | 1983 |

|

SU1144127A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Булычев Ю.Г | |||

| Метод приближенного решения двухмерного уравнения Фоккера- Планка | |||

| - Радиотехника и электроника, 1985, т | |||

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

| Устройство для решения дифференциальных уравнений в частных производных | 1987 |

|

SU1525715A1 |

| Бахвалов Н.С., Жидков Н.П., Кобельков Г.М | |||

| Численные методы | |||

| - М.: Наука, 1987,600 с | |||

| Булычев ЮГ., Погонышев С А | |||

| Метод численного интегрирования многомерного уравнения Фоккера-Планка на основе усеченных алгоритмов быстрого преобразования Фурье | |||

| - Радиотехника и электроника, 1989, т | |||

| Нивелир для отсчетов без перемещения наблюдателя при нивелировании из средины | 1921 |

|

SU34A1 |

| Пневматическая секционная шина | 1923 |

|

SU1241A1 |

| Колошкин Э.П | |||

| и др | |||

| Микропроцессорный комплект БИС для конвейерных систем цифровой обработки сигналов | |||

| - Микропроцессорные средства и системы, 1986, Вып | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

Авторы

Даты

1992-05-15—Публикация

1990-02-28—Подача