(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМА

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой преобразователь координат | 1983 |

|

SU1163322A1 |

| Цифровой функциональный преобразователь (его варианты) | 1981 |

|

SU1019443A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1246091A1 |

| Устройство для передачи и приема данных | 1982 |

|

SU1098104A1 |

| Устройство для формирования изображения на экране телевизионного приемника | 1985 |

|

SU1288751A1 |

| Устройство для сжатия и развертывания информации | 1986 |

|

SU1309070A1 |

| Устройство для возведения в квадрат | 1983 |

|

SU1160404A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Устройство декодирования при воспроизведении цифровой магнитной записи | 1990 |

|

SU1778787A1 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

1

Изобретение относится к вычислительной технике и предназначено для вычисления логарифма при основании два от числа, представленного одиннёщцатиразрядным параллельным двоичным потенциальным кодом, и может быть использовано в цифровых устройствах обнаружения радиолокационных сигналов.

Известно усаройство, содержащее регистр числа, блок памяти, блок деления, схему сравнения, сдвиговый регис тр, регистры результата и блок

управления Г

Недостатком такого устройства является низкое быстродействие.

Наиболее близким к изобретению по технической сущности является устройство, содержащее блок управления, блок сдвига параллельный сумматор, первый элемент ИЛИ и первый элемент -И, причем группа выходов блока управления подключена к первой группе входов блока сдвига, второй, третий, четвертый и пятый элементы И, второй элемент ИЛИ, первый и второй элемент НЕ, дешифратор и шифратор, причем выходы шифратора являются выходами устройства, а входы соединены с группой выходов блока управления.

группа входов устройства подключена к группе входов блока управления и второй группе входов блока сдвига, первый, втЬрой, третий, четвертый . и пятый выходы которого подключены к первым входам первого, второго, третьего, четвертого и пятого разрядов параллельного сумматора,а первый и второй выходы блока сдвига

10 подключены к первому и второму входам дешифратора, третий, четвертый и пятый выходы блока сдвига присоединены к входам первого элемента И, выход которого соединен с первыми

15 входами второго и третьего элементов И и входом первого элемента НЕ, выход которого присоединен к первому входу первого элемента ИЛИ, второй вход которого подключен к перво20му выходу дешифратора, а выхзд первого элемента ИЛИ подключен к второму входу второго разряда параллельного сумматора, вторые входы второго и третьего элементов И подключены к

25 второму и третвуёМу выходам дешифратора, первый и второй вход четвертого элемента И подсоединен к третьему выходу блока сдвига и третьему выходу дешифратора, соответственно,

30 третий выход блока сдвига соединен

С входом второго элемента НЕ, выход оторого подсоединен к первому входу пятого элемента И, второй вход которого подключен к четвертому выходу ешифратора, выход третьего.элемента И подсоэдинен к входу переноса первого разряда сумматора, выходы второГО, четвертого и пятого элементов И подсоединены к. первому, второму, третьему и четвертому входам второго элемента ИЛИ, выход которого соединен с вторым входом второго разряда сумматора, выходы которого являются выходами устройства.

Устройство вычисляет логарифм числа, представленного параллельным двоичным шестиразрядным кодом, в виде трехразрядного кода порядка и пятиразрядного кода мантиссы C2J.

Однако у известного устройства низкая точность вычислений.

Цель изобретения - повышение точности вычисления логарифма числа при основании два, представленного одиннадцатиразрядным двоичным параллельным кодом.

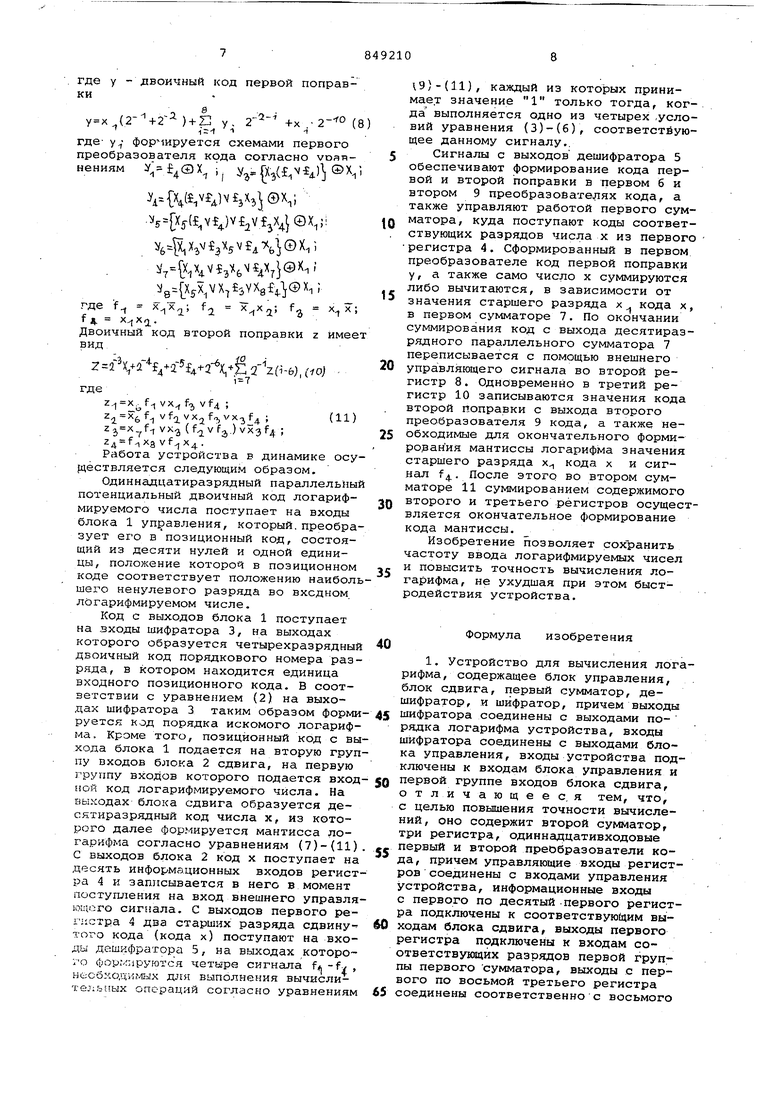

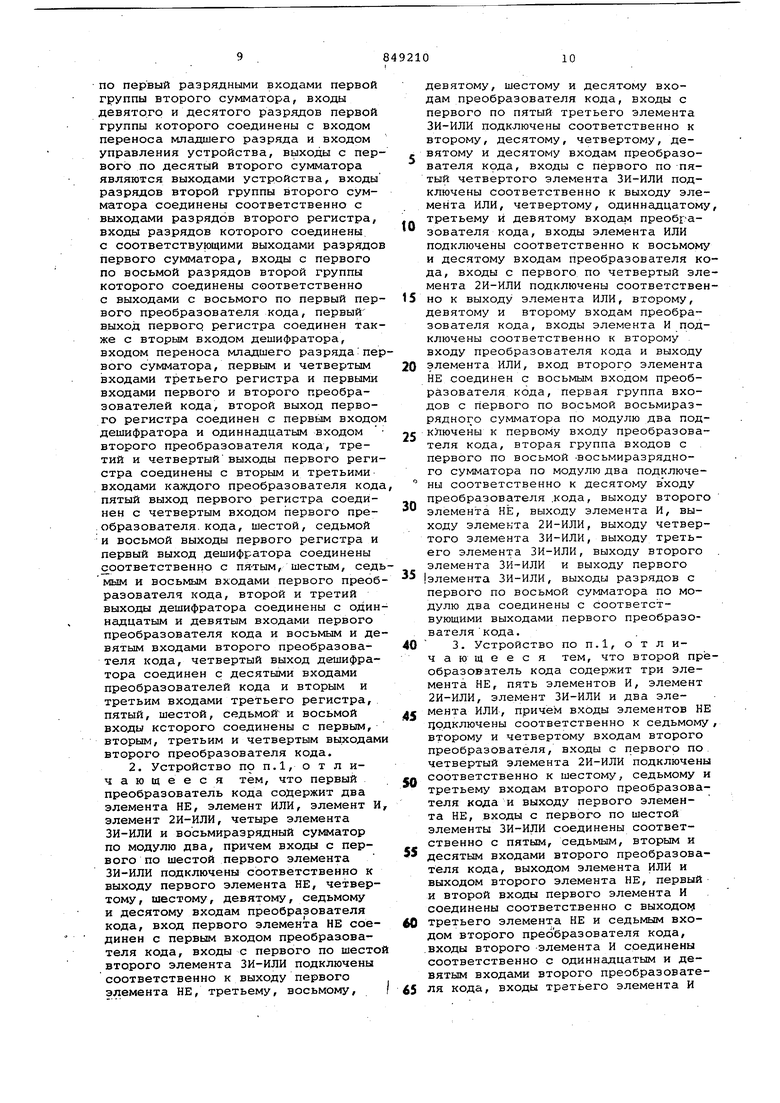

Поставленная цель достигается тем, что в устройство, содержащее блок управления, блок сдвига, первый сумматор, дешифратор и шифратор, причем выходы шифратора соединены с выходами порядка логарифма устройства, входы шифратора соединены с выходами блока управления, входы устройства подключены к входам блокауправления и первой группе входов блока сдвига, дополнительно введены второй сумматор, три регистра, одиннадцативходовые первый и второй преобразова-, тели кода,причем управляющие входы регистров соединены с входами управления устройства, информационные входы с первого по десятый первого регистра подключены к соответствующим выходам блока сдвига, выходы первого регистра подключены к входам соответствующих разрядов первой группы первого сумматора, выходы с первого по восьмой третьего регистра соединены соответственно с восьмого по первый разрядными входами первой группы второго суммат.ора, входы девятого и,десятого разрядов первой группы которого соединены с входом переноса младшего разряда и входом управления устройства, выходы с первого по десятый второго сумматора являются выходами устройства,входы разрядов второй, группы второго сумматора соединены соответственно с выходами разрядов второго регистра, входы разрядов которого соединены с соответствукадими выходами разрядов первого сумматора/ входы с первого по восьмой разрядов второй группы которого соеди.нены соответственно с выходами с восьмого по первый.первого преобразователя кода, первый выход .первого регистра соединен также с вторым входом дешифратора, входом переноса младшего разряда первого су иматора, пе.рвым и четверным входами третьего регистра и первыми входами первого и второго преобра,зователей кода, второ выход первого регистра соединен с первым входом дешифратора и одиннадцатым входом второго преобразователя кода, третий и четвертыйвыходы первого регистра соединены с вторым и (третьим входами каждого преобразователя кода, пятый выход первого регистра соединен с четвертым входом первого преобразователя кода, шес- той, седьмой и восьмой выходы первого регистра и первый выход дешифратора соединены -соответственно с пятым, шестым, седьмым и восьмым входами перйого преобразователя кода, второй и третий выходы дешифратора соединены с одиннадцатым и девятым входами первого преобразователя кода и восьмым и девятым входами второго преобразователя кода, четвертый выход дешифратора соединен с десятым входами преобразователей кода и вторым и третьим-Входами третьего регистра, пятый, шестой, седьмой и восьмой входы которого соединены с первы вторым, третьим и четвертым выходами второго преобразователя кода.

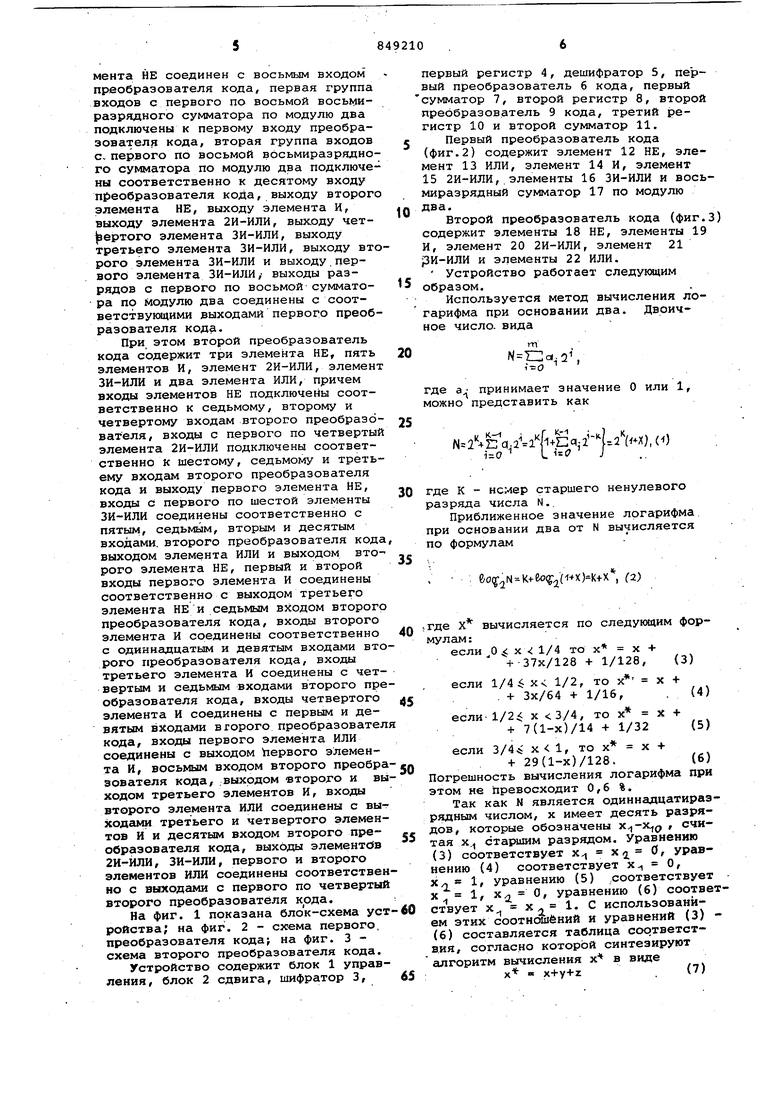

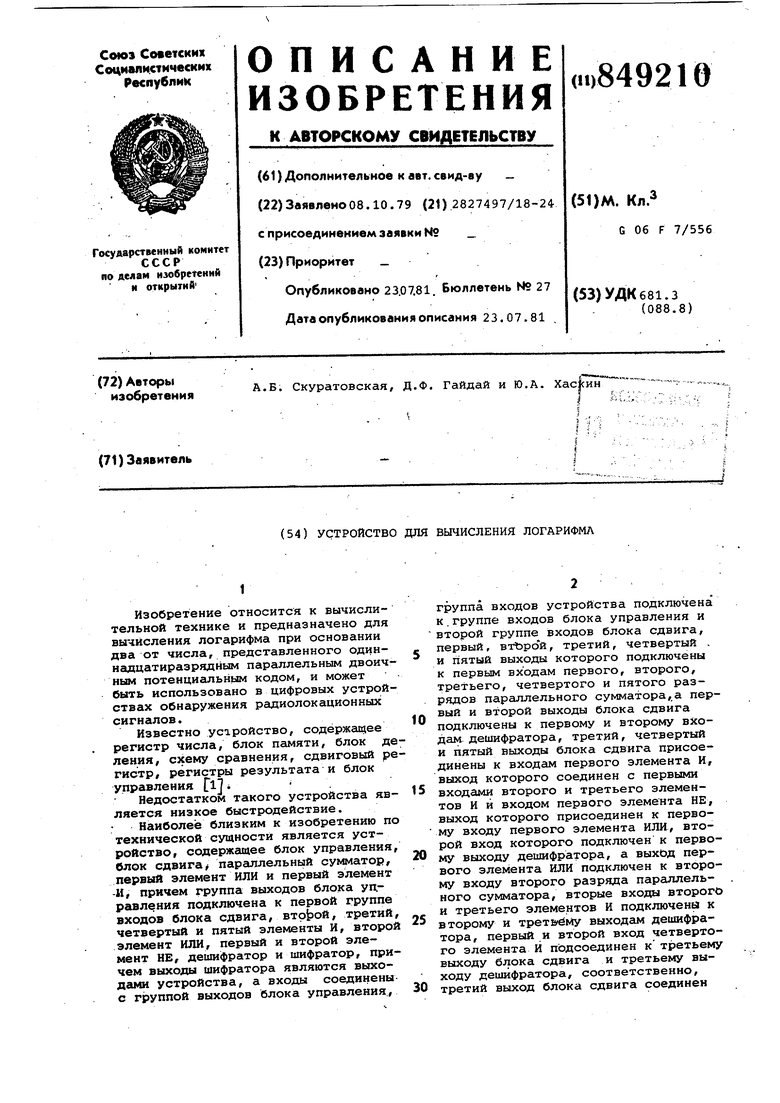

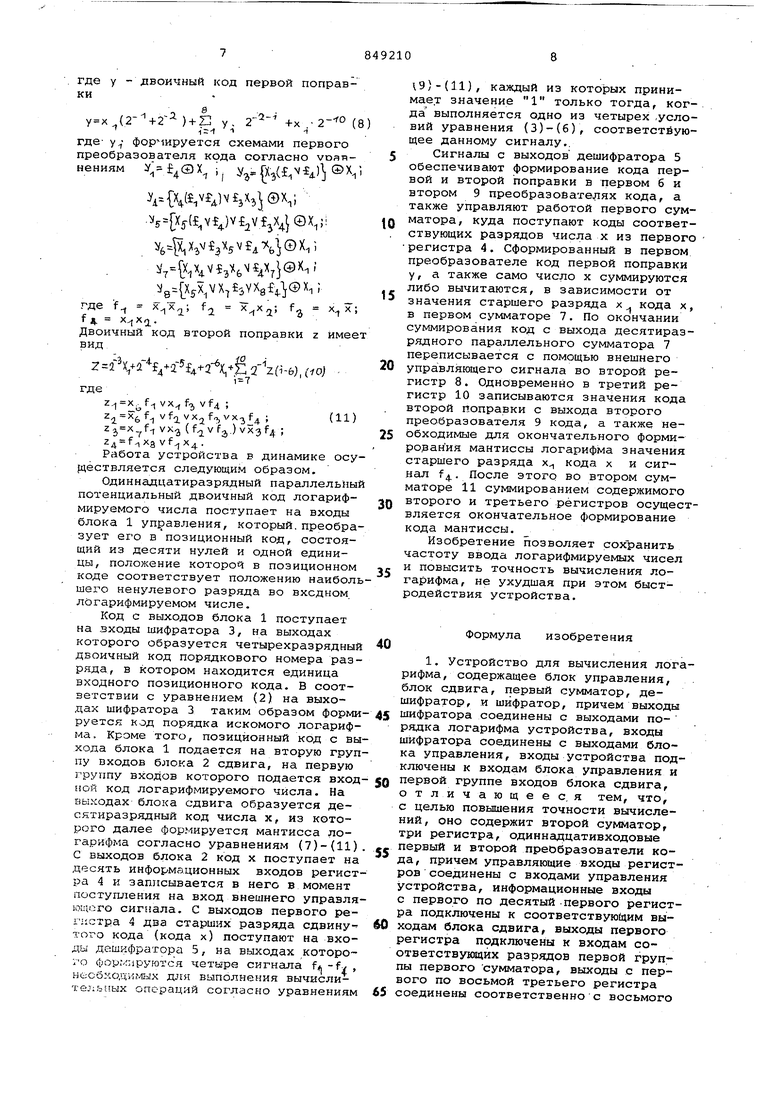

Кроме того, первый преобразовател кода содержит два элемента НЕ, элемент ИЛИ, элемент И, элемент 2И-ИЛИ, четыре элемента ЗИ-ИЛИ и восьмиразрядный сумматор по модулю два, причем входы с первого по шестой первого элемента ЗИ-ИЛИ подключены соответственно к выходу первого элемента НЕ, четвертому, шестому, девятому, седьмому и десятому входам преобразователя кода, вход первого элемента НЕ соединен с первым входом преобразователя кода, входы с первог по шестой второго элемента ЗИ-ИЛИ подключены соответственно к выходу первого элемента НЕ, третьему, восьмому, девятому, шестому и десятому входам преобразователя кода, входы с первого по пятый третьего элемента ЗИ-ИЛИ подключены соответственно к второму, десятому, четвертому, девятому и десятому входам преобразователя кода, входы с первого по пятый четвертого элемента ЗИ-ИЛИ подключены соответственно к выходу элемента ИЛИ, четвертому, одиннадцатому третьему и девятому входам преобразователя кода, входы элемента ИЛИ подключены соответственно к восьмому и десятому входам преобразователя кода, входы с первого по четвертый элемента 2И-ИЛИ подключены соответственно к выходу элемента ИЛИ, второму, девятому и второму входам преобразователя кода, входы элемента И подключены-соответственно к второму входу преобразователя кода и выходу элемента ИЛИ, вход второго элемента HE соединен с восьмым входом преобразователя кода, первая группа входов с первого по восьмой восьмиразрядного сумматора по модулю два подключены к первому входу преобразователя кода, вторая группа входов с, первого по восьмой восьмиразрядно го сумматора по модулю два подключе ны соответственно к десятому входу п ь еобразователя коДа, выходу второг элемента НЕ, выходу элемента И, выходу элемента 2И-ИЛИ, ВЫХ.ОДУ чет ертого элемента ЗИ-ИЛИ, выходу третьего элемента ЗИ-ИЛИ, выходу вто рого элемента ЗИ-ИЛИ и выходу первого элемента ЗИ-ИЛИ/ выходы разрядов с первого по восьмой сумматора по Модулю два соединены с соответствукяцими выходами первого преобразователя кодэ. При этом второй преобразователь кода содержит три элемента НЕ, пять элементов И, элемент 2И-ИЛИ, элемент ЗИ-ИЛИ и два элемента ИЛИ, причем входы элементов НЕ подключены соответственно к седьмому, второму и четвертому входам второго преобразо вателя, входы с первого по четвертый элемента 2И-ИЛИ подключены соответственно к шестому, седьмому и третьему входам второго преобразователя кода и выходу первого элемента НЕ, входы с первого по шестой элементы ЗИ-ИЛИ соединены соответственно с пятым, седьмым, вторым и десятым входами, второго преобразователя кода выходом элемента ИЛИ и выходом второго элемента НЕ, первый и второй входы первого элемента И соединены соответственно с выходом третьего элемента НЕ и седьмым входом второго преобразователя кода, входы второго элемента И соединены соответственно с одиннадцатым и девятым входами вто рого преобразователя кода, входы третьего элемента И соединены с четвертым и седьмым входами второго пре образователя кода, входы четвертого элемента И соединены с первым и девятым входами второго преобразовател кода, входы первого элемента ИЛИ соединены с выходом первого элемента И, восьмым входом второго преобра зователя кода, выходом второго и вы ходом третьего элементов И, входы второго элемента ИЛИ соединены с выходами третьего и четвертого элементов И и десятым входом второго преобразователя кода, выходы элементов 2И-ЙЛИ, ЗИ-ИЛИ, первого и второго элементов ИЛИ соединены соответствен но с выходами с первого по четвертый второго преобразователя кода. На фиг. 1 показана блок-схема уст ройства; на фиг. 2 - схема первого, преобразователя кода; на фиг. 3 схема второго преобразователя кода. Устройство содержит блок 1 управления, блок 2 сдвига, шифратор 3, первый регистр 4, дешифратор 5, первый преобразователь 6 кода, первый сумматор 7, второй регистр 8, второй преобразователь 9 кода, третий регистр 10 и второй сумматор 11. Первый преобразователь кода (фиг.2) содержит элемент 12 НЕ, элемент 13 ИЛИ, элемент 14 И, элемент 15 2И-ИЛИ,.элементы 16 ЗИ-ИЛИ и восьмиразрядный сумматор 17 по модулю два. Второй преобразователь кода (фиг.З) содержит элементы 18 НЕ, элементы 19 И, элемент 20 2И-ИЛИ, элемент 21 рИ-ИЛИ и элементы 22 ИЛИ. Устройство работает следующим образом. Используется метод вычисления логарифма при основании два. Двоичное число, вида m , 2 1-0 где aj принимает значение О или 1, можно представить как ,4i+C,), () 1 0 L где К - номер старшего ненулевого разряда числа N.. Приближенное значение логарифма при основании два от N вычисляется по формулам eO(y2N ,,J(«X)K+X (-2) Где X вычисляется по следующим формулам:если 0 XX 1/4 то х х + + 37Х/128 + 1/128, если 1/4 х 1/2, то . + Зх/64 + 1/16, если-1/2 X 3/4, то х + 7(1-х)/14 + 1/32 если X 1, то X X + 29(1-х)/128 Погрешность вычисления логарифма при этом не превосходит 0,6 %. Так как Л является одиннадцатираэрядным числом, X имеет десять разрядов, которые обозначены , считая х. старшим разрядом. Уравнению (3) соответствует х. х О, уравнению (4) соответствует х-, О, х/ч 1, уравнению (5) соответствует X 1, Xji О, уравнению (6) соответст вует X . С использованием этих соотношений и уравнений (3) (6) составляется таблица соответствия, согласно которой синтезируют алгоритм вычисления х в виде X « x+y+z . (7) где у - двоичный код первой поправки-Ч2 о-З-- , ) + S у, (2 2 +х 1Г| 1 где- формируется схемами первого преобразователя кода согласно .4®. i, нениям i,®X i, У V-W5l A %bi®M .()V 2Vf3X4 ©X,r .5 , /g4x5 vx %VX8f l,®x,;. - --I 2 f 4 . Двоичный код второй поправки z .e 2z(i-6), x, f vx f vf4 ; . - .Z X f VtQ VX i ( ,1 .,,- t ---c Z , vx (,.) vx3f4 24 1X3 , Работа устройства в динамике осу цecтвляeтcя следующим образом. Одиннадцатиразрядный параллельны потенциальный двоичный код логарифмируемого числа поступает на входы блока 1 управления, который.преобра зует его в позиционный код, состоящий из десяти нулей и одной единицы, положение которой в позиционном коде соответствует положению наибол шего ненулевого разряда во вхсдном логарифмируемом числе. Код с выходов блока 1 поступает на входы шифратора 3, на выходах которого образуется четырехразрядны двоичный код порядкового номера раз ряда, в котором находится единица входного позиционного кода. В соответствии с уравнением (2) на выходах шифратора 3 таким образом форм руется код порядка искомого логариф ма. Кроме того, позиционный код с в хода блока 1 подается на вторую гру пу входов блока 2 сдвига, на первую группу входов которого подается вхо ной код логарифмируемого числа. На выходах блока сдвига образуется десятиразрядный код числа X, из которого далее формируется мантисса логарифма согласно уравнениям (7)-(11 С выходов блока 2 код х поступает н десять информационных входов регис ра 4 и записывается в него в момент посгупления на вход внешнего управл сигнала. С выходов первого ре гистра 4 два старших разряда сдвину кода (кода х) поступают на вхо Х1Ы дешифраторгг 5, на выходах которо го фор.хируются четыре сигнала f -f кесбхо. для выполнения вычислите.;Г:.-иых огтераций согласно уравнения 9)-(11), каждый из которых принимает значение 1 только тогда, когда выполняется одно из четырех .условий уравнения (З)-(б), соответствующее данному сигналу.. Сигналы с выходов дешифратора 5 обеспечивают формирование кода первой и второй поправки в первом б и втором 9 преобразователях кода, а также управляют работой первого сумматора, куда поступают коды соответствующих разрядов числа х из первого регистра 4. Сформированный в первом преобразователе код первой поправки у, а также само число х суммируются либо вычитаются, в зависимости от значения старшего разряда х . кода х, в первом сумматоре 7. По окончании суммирования код с выхода десятиразрядного параллельного сумматора 7 переписывается с помощью внешнего управляющего сигнала во второй регистр 8. Одновременно в третий регистр 10 записываются значения кода второй поправки с выхода второго преобразователя 9 кода, а также необходимые для окончательного формирования мантиссы логарифма значения старшего разряда х кода х и сигнал f4,. После этого во втором сумматоре 11 суммированием содержимого второго и третьего регистров осуществляется окончательное формирование кода мантиссы. Изобретение позволяет сохранить частоту ввода логарифмируемых чисел и повысить точность вычисления логарифма, не ухудшая при этом быстродействия устройства. Формула изобретения 1. Устройство для вычисления логарифма, содержащее блок управления, блок сдвига, первый сумматор, дешифратор, и шифратор, причем выходы шифратора соединены с выходами порядка логарифма устройства, входы шифратора соединены с выходами блока управления, входы устройства подключены к входам блока управления и первой группе входов блока сдвига, отличающее с. я тем, что, с целью повышения точности вычислений, оно содержит второй сумматор, три регистра, одиннаддативходовые первый и второй преобразователи кода, причем управляющие входы регистров соединены с входами управления устройства, информационные входы с первого по десятый первого регистра подключены к соответствующим выходам блока сдвига, выходы первого регистра подключены к входам соответствующих разрядов первой группы первого сумматора, выходы с первого по восьмой третьего регистра соединены соответственно с восьмого

по первый разрядными входами первой группы второго сумматора, входы девятого и десятого разрядов первой группы которого соединены с входом переноса младшего разряда и входом управления устройства, выходы с первого по десятый второго сумматора являются выходами устройства, входы разрядов второй группы второго сумматора соединены соответственно с выходами разрядов второго регистра, входы разрядов которого соединены с соответствующими выходами разрядов первого сумматора, входы с первого по восьмой разрядов второй группы которого соединены соответственно с выходами с восьмого по первый первого преобразователя кода, первый выход первогр регистра соединен также с вторым входом дешифратора, входом переноса младшего разряда:первого сумматора, первым и четвертым входами третьего регистра и первыми входами первого и второго преобразователей кода, второй выход первого регистра соединен с первым входом дешифратора и одиннащцатым входом второго преобразователя кода, третий и четвертыйвыходы первого регистра соединены с вторым и третьими входами каждого преобразователя кода пятый выход первого регистра соединен с четвертым входом первого преобразователя, кода, шестой, седьмой и восьмой выходы первого регистра и первый выход дешифратора соединены 0ответственно с пя-тым, шестым, седьмым и восьмым входами первого преобразователя кода, второй и третий выходы дешифратора соединены с одиннадцатым и девятым входами первого преобразователя кода и восьмым и девятым входами второго преобразователя кода, четвертый выход дешифратора соединен с десятыми входами преобразователей кода и вторым и третьим входами третгьего регистра, пятый, шестой, седьмой и восьмой входы которого соединены с первым, вторым, третьим и четвертым выходами второго преобразователя кода.

девятому, шестому и десятому входам преобразователя кода, входы с первого по пятый третьего элемента ЗИ-ИЛИ подключены соответственно к второму, десятому, четвертому, девятому и десятому входам преобразователя крда, входы с первого по пятый четвертого элемента ЗИ-ИЛИ подключены соответственно к выходу элемента ИЛИ, четвертому, одиннадцатому, третьему и девятому входам преобра0зователя кода, входы элемента ИЛИ подключены соответственно к восьмому и десятому входам преобразователя кода, входы с первого по четвертый элемента 2И-ИЛИ подключены соответствен5но к выходу элемента ИЛИ, второму, девятому и второму входам преобразователя кода, входы элемента И подключены соответственно к второму входу преобразователя кода и выходу элемента ИЛИ, вход второго элемента

0 НЕ соединен с восьмым входом преобразователя кода, первая группа входов с первого по восьмой восьмиразрядного сумматора по модулю два подключены к первому входу преобразова5теля кода, вторая группа входов с . первого по восьмой -восьмиразрядного сумматора по модулю два подключены соответственно к десятому входу преобразователя .кода, выходу второго

0 элемента НЕ, выходу элемента И, выходу элемента 2И-ИЛИ, выходу четвертого элемента ЗИ-ИЛИ, выходу третьего элемента ЗИ-ИЛИ, выходу второго элемента ЗИ-ИЛИ и выходу первого

5 элемента ЗИ-ИЛИ, выходы разрядов с первого по восьмой сумматора по модулю два соединены с соответствующими выходами первого преобразователя кода.

0

5 подключены соответственно к седьмому, второму и четвертому входам второго преобразователя, входы с первого по четвертый элемента 2И-ИЛИ подключены соответственно к шестому, седьмому и

0 третьему входам второго преобразователя кода и выходу первого элемента НЕ, входы с первого по шестой элементы ЗИ-ИЛИ соединены соответственно с пятым, седьмым, вторым и

5 десятым входами второго преобразователя кода, выходом элемента ИЛИ и выходом второго элемента НЕ, первый и второй входы первого элемента И соединены соответственно с выходо Третьего элемента НЕ и седьмым вхоОдом второго преобразователя кода, .входы второго элемента И соединены соответственно с одиннадцатым и девятым входами второго преобразователя кода, входы третьего элемента И

5

соединены с четвертым и седьмым входами второго преобразователя кода, входы четвертого элемента И соединены с первым и девятым входами второго преобразователя кода, входы первого элемента ИЛИ соединены с выходом первого элемента И, восьмым входом второго преобразователя кода, выходом второго и выходом третьего элементов И, входы второго элемента ИЛИ соединены с выходами третьего и четвертого элементов И и десятым входом второго преобраэователя кода,выходы

Koff мантией мгарифм

I I I

Т

TfM

I II ITT I I I

Лв числа

элементов 2И-ИЛИ, ЗИ-ИЛИ, первого и второго элементов ИЛИ соединены соответственно с выходами с первого по четвертый второго преобразователя кода.

Источники информации, принятые во внимание при экспертизе 1.- Авторское свидетельство СССР 590733, KJJ. G 06 F 7/38, 1978.

. 2. Авторское свидетельство СССР 448459, кл. G 06 F 7/38, 1974 (прототип). .

I FT

ш

э

k

Фиг. t

Авторы

Даты

1981-07-23—Публикация

1979-10-08—Подача