I

Изобретение относится к вычислительной .технике предназначено для вычисления логарифма при основгмии два от числа, представленного шестиразрядным параллельным двоичньгм потенциальным кодом, и может быть использовано в цифровых устройствах обнаружения радиолокационных сигналов.

Известно цифровое устройство для вычисления логарифма, содержащее регистр, блок сдвига и схему управления, выход которой соединен с управляющими входами регистра и блока сдаига. Кроме того, устройство содержит триггер, схему И, схему ИЛИ, два сумматора и запоминающий блок, причем выход блока сдвига соединен со входом первого сумматора, выход того сумматора соединен со входом схемы ИЛИ, со входом схемы И и первым входом схемы управления, выход схемы ИЛИ соединен со вторым выходом схемы управления и другим входом схемы И, выход схемы И соединен с третьим входом схемы управления, выход которой соединен соответственно с входами управления триггера, запоминающего блока, обоих сумматоров и регистров, а выход

й1««« 4азк сткчай(г «5««1я&ж8йгщ ая .запоминающего блока соединен со входом реШстра, выход которого подключен ко входу второго сумматора 1 и 2.

Известное устройство вычисляет логарифм числа, представленного параллельным двоичным кодом, итерационным способом, в течении несколысих тактов работы. При этом для образования только порядка логарифма требуется столько тактов работы устройства, сколько разрядов в коде логарифмируемого числа.

10

Устройство для вычисления логарифма при основании два от параллельного двоичного кода небольшой разрядности (порядка разрядов) может использоваться в цифровых устройствах обнаружения радиолокационных

15 сигналов. Однако при этом использование известного устройства затруднительно, так как оно обладает низким бьютродействием в силу многотактного режима работы.

Цель изобретения - повьциение быстродей21ствия устройства.

Поставленная цель достигается тем, что в устройство для вычисления .логарифма, содержащее блок управления, блок сдвига, лараллёльный сумматор, первый элемент ИЛИ и первый элемент И, причем группа выходов блока управления подключена к первой группе входов блока сдвига, введены второй, третий четвертьш, пятый элементы И, второй элемент ИЛИ, первый и второй элемент НЕ, дешифратор и шифратор, причем выходы шифратора етляются (1-п)-ми выходами устройства, а входы соединены с грзшпой выходов блока управления, группа входов устройства подключена кгруппе входов блока управления и ко . второй группе входов блока сдвига, первый, второй, третий, четвертый и пятый выходы ко. торого подключены к первым входам первого второго, третьего, четвертого и пятого разрядов параллельного сумматора, а первый и второй выходы блока сдвига подключены к первому и второму входам дешифратора, третий, четвертый и пятый выходы блока сдвига подсоединены ко входам первого элемента И, выход которого соединен с первыми входами втО рого и третьего элементов И и входам первого элемента НЕ, выход которого подсоединен lie первому входу первого элемента ИЛИ, второй вход которого подключен к первому вы.ходу дешифратора, а выход первого элемента ИЛИ подключен ко второму входу второго разряда параллельного сумматора, вторые вхо. ды второго и третьего элементов И подключены ко второму и третьему выходам дешифратора, первый и второй вход четвертого элемента И подключен к третьему выходу блока сдвига и третьему выходу дешифратора соответственно, третий выход блока сдвига соединен со входом второго элемента НЕ,-вьгхЬд которого подсоединен к первому входу пятого элемента И, второй вход которого подключен к четвертому выходу дешифратора, выход третьего элемента И подсоединен ко входу переноса первого разряда сумматора, выходы второго, четвертого и пятого элементов И подсоединены к первому, второму, третьему и четвертому входам второго элемента ИЛИ, выход которого связан со вторьШвхбдрм второго разряда параллельного сумматора, выходы которого являются (п+1) - (п+6)-ми выходами устройства.

Введение в устройство для вычисления логарифма дйполяитё ьных блоков и связей позволяет производить вычисление логарифма при основании два от числа, представленного параллельным шестиразрядным двоичны11Л кодом, в виде параллельного трехразрядного кода порядка логарифма и параллельного пятиразрядного кода мантиссы логарифма за время, не превосходящее время срабатьшания цепочки последовательно включённых десяти элементов И , ИЛИ, НЕ и сумматора, что составляет время.

ggeSaSKe : -:примерно равное одному такту работы известного устройства.

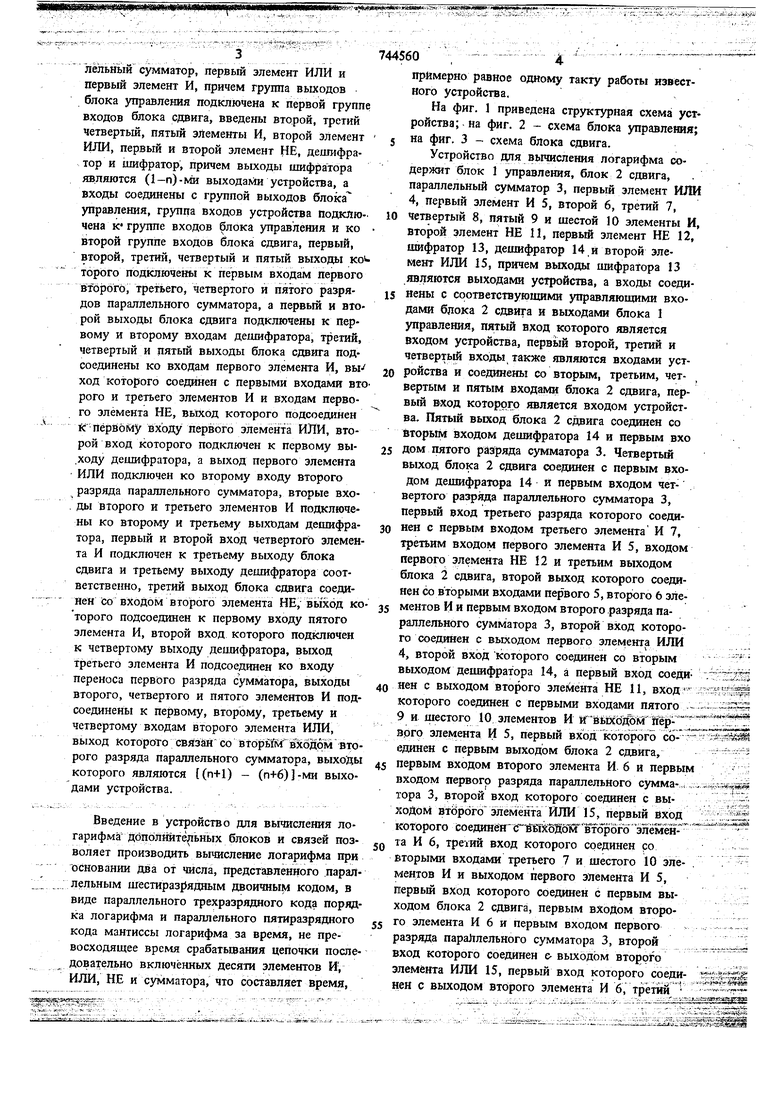

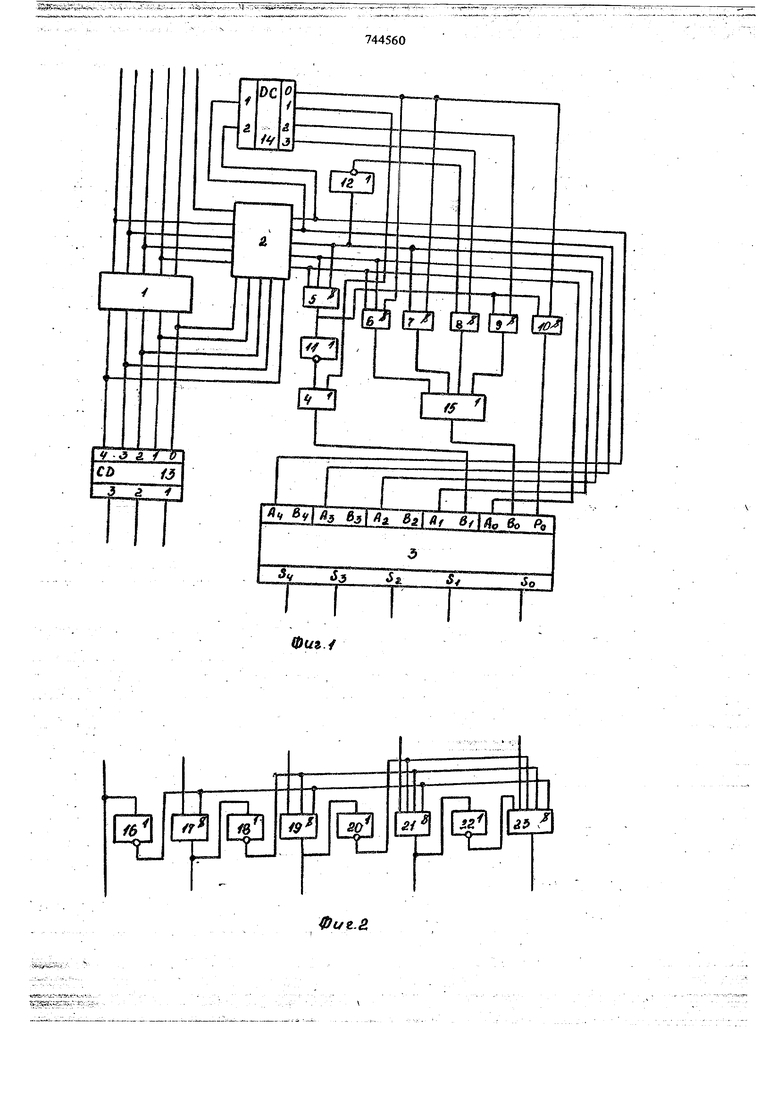

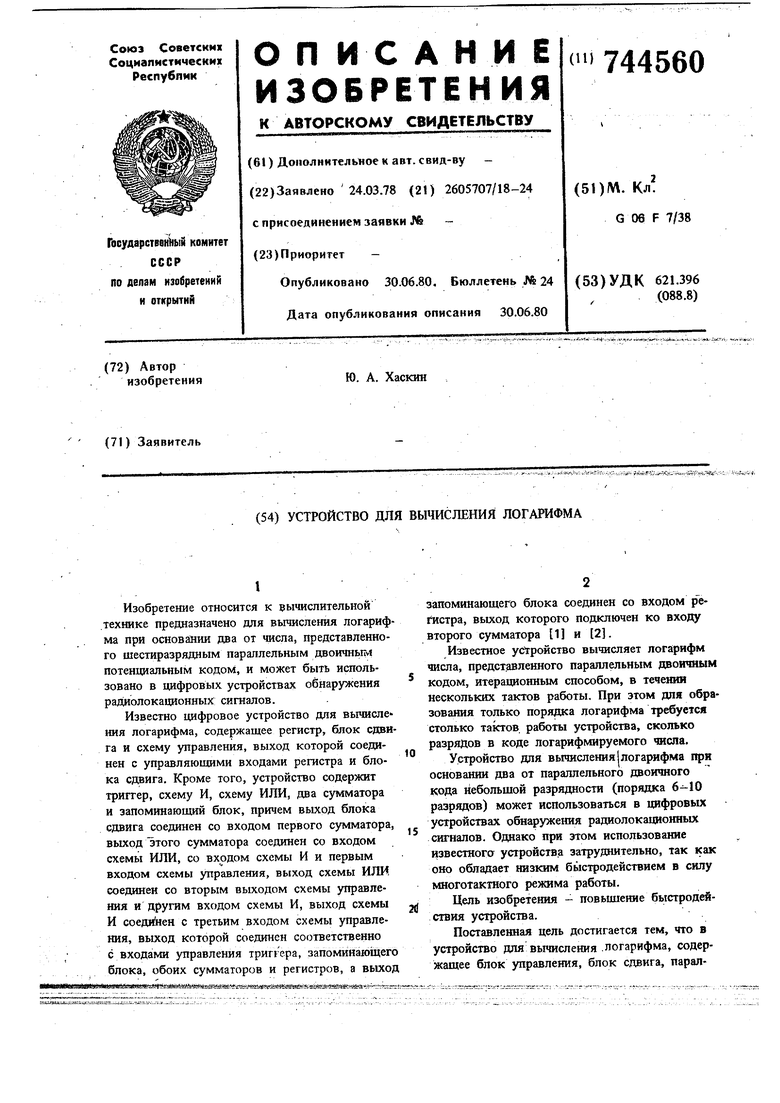

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - схема блока управления; 5 на фиг. 3 - схема блока сдвига.

Устройство для вычисления логарифма содержит блок 1 управления, блок 2 сдвига, параллельный сумматор 3, первый элемент ИЛИ 4, первый элемент И 5, второй 6, третий 7, 10 четвертый 8, пятый 9 и шестой 10 элементы И, второй элемент НЕ 11, первый элемент НЕ 12, шифратор 13, дешифратор 14 и второй элемент ИЛИ 15, причем выходы шифратора 13 являются выходами ус1ройства, а входы соеди5 яены с соответствующими управляющими входами блока 2 сдвига и выходами блока 1 управления, пятый вход которого является входом устройства, первь1Й второй, третий и четвертьй входы также являются входами устройства и соединены со вторым, третьим, четвертым и пятым входами блока 2 сдвига, первый вход которого фляется входом устройства. Пятый выход блока 2 сдвига соединен со вторым входом дешифратора 14 и первым вхо 5 дом пятого разряда сумматора 3. Четвертый выход блока 2 сдвига соединен с первым входом деишфратора 14 и первым входом четвертого разряда параллельного сумматора 3, первый вход третьего разряда которого соеди0 ней с первым входом третьего элемента И 7, третьим входом первого элемента И 5, входом первого элемента НЕ 12 и третьим выходом блока 2 сдвига, второй выход которого соединен со вторыми входами первого 5, второго 6 эле5 ментов И и первым входом второго разряда параллельного сумматора 3, второй вход которого соединен с выходом первого элемента ИЛИ 4, второй вход которого соединен со вторым выходом дешифратора 14, а первый вход соединен с выходом второго элемента НЕ 11, которого соединен с первыми входами пятого 9 и шестого 10 элементов И вы 1лШр- йрго элемента И 5, первый вход которого со- единен с первьлм выходом блока 2 сдвига, 5 первым входом второго элемента И 6 и первым входом первого разряда параллельного сумма-.. . тора 3, второй вход которого соединен с выходом втёрого элемента ИЛИ 15, первый вход которого соединШ Т ЖГхоДо1йТт6рого элёмен- Q la И 6, третий вход которого соединен ро

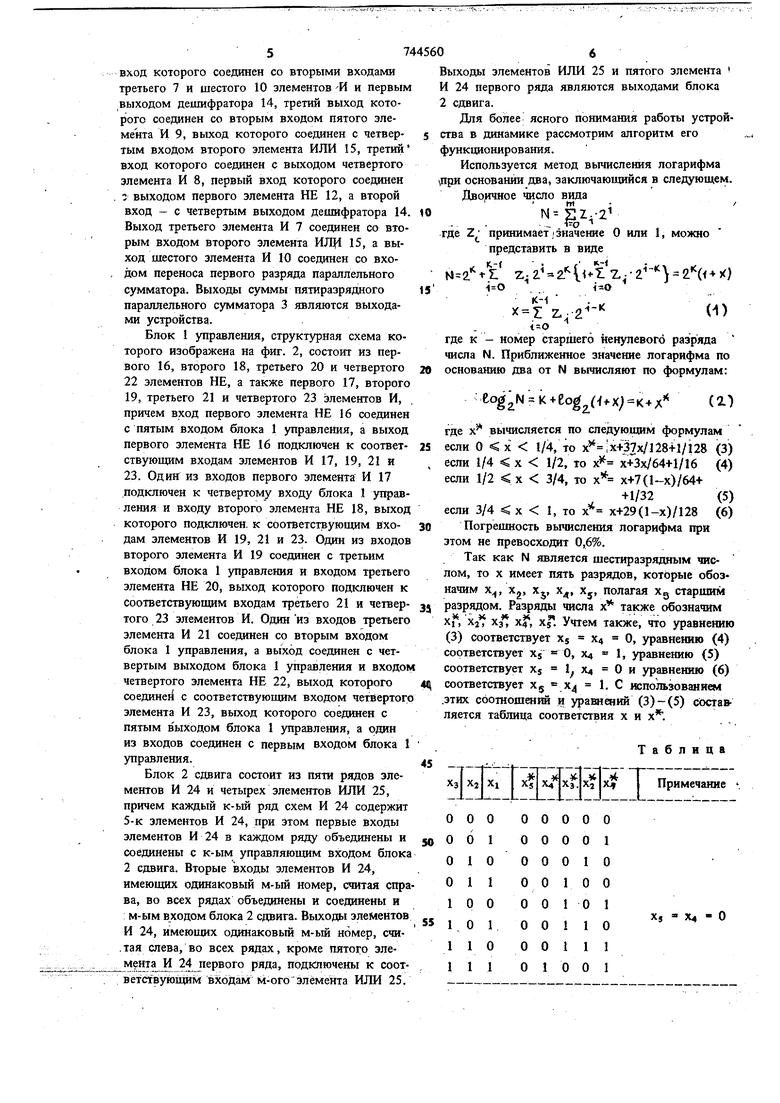

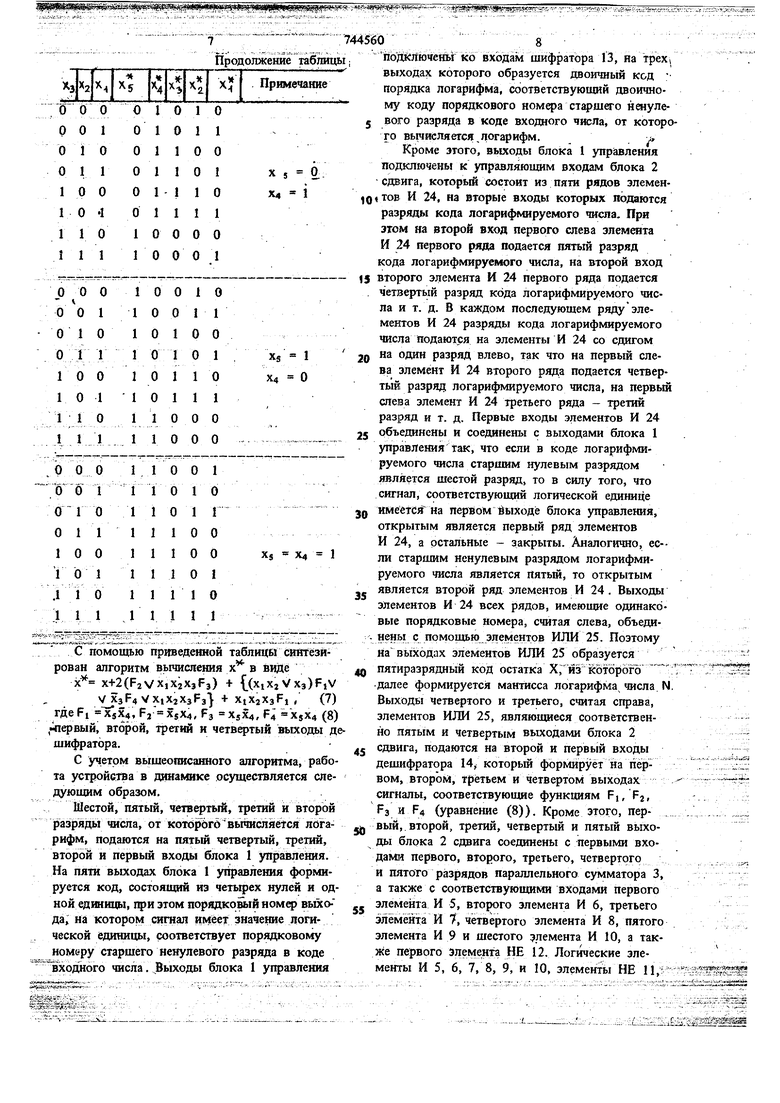

вторыми входами третьего 7 и шестого 10 эле- , ментов И и выходом первого элемента И 5, первый вход которого соединен с первым выходом блока 2 сдвига, первым вХоДом второго элемента И 6 и первым входом первого разряда параллельного сумматора 3, второй вход которого соединен с- выходом второго элемента ИЛИ 15, первый вход которого соеди-iifc. . нен с выходом второго элемента И 6, третий 574 вход которого соединен со вторыми входами третьего 7 и шестого 10 элементов И и первым выходом дешифратора 14, третий выход которого соединен со вторым входом пятого элемента И 9, выход которого соединен с четвертым входом второго элемента ИЛИ 15, третий вход которого соединен с выходом четвертого элемента И 8, первый вход которого соединен 7 выходом первого элемента НЕ 12, а второй вход - с четвертым выходом дешифратора 14. Выход третьего элемента И 7 соединен со вторым входом второго элемента ИЛИ 15, а выход шестого элемента И 10 соединен со входом переноса первого разряда параллельного сумматора. Выходы суммы пятиразрядного параллельного сумматора 3 являются выходами устройства. Блок 1 управления, структурная схема которого изображена на фиг. 2, состоит из первого 16, второго 18, третьего 20 и четвертого 22 элементов НЕ, а также первого 17, второго 19, третьего 21 и четвертого 23 элементов И, причем вход первого элемента НЕ 16 соединен с пятым входом блока 1 управления, а выход первого элемента НЕ 16 подключен к соответствующим входам элементов И 17, 19, 21 и 23. Один из входов первого элемента И 17 подключен к четвертому входу блока 1 управления и входу второго элемента НЕ 18, выход которого подключен, к соответствующим входам элементов И 19, 21 и 23. Один из входов второго элемента И 19 соединен с третьим входом блока 1 управления и входом третьего элемента НЕ 20, выход которого подключен к соответствующим входам третьего 21 и четвертого 23 элементов И. Один из входов третьего элемента И 21 соединен со вторым входом блока 1 управления, а выход соединен с четвертым выходом блока 1 управления и входом четвертого элемента НЕ 22, выход которого соединен с соответствующим входом четвертого элемента И 23, выход которого соединен с пятым выходом блока 1 управления, а один из входов соединен с первым входом блока 1 управления. Блок 2 сдвига состоит из пяти рядов элементов И 24 и четырех элементов ИЛИ 25, причем каждый к-ый ряд схем И 24 содержит 5-к элементов И 24, при этом первые входы элементов И 24 в каждом ряду объединены и соединены с к-ым управляющим входом блока 2 сдвига. Вторые входы элементов И 24, имеющих одинаковый м-ый номер, считая спра ва, во всех рядах объединены и соединены и м-ым входом блока 2 сдвига. Выходы элементов И 24, имеющих одинаковый м-ый номер, счи.тая слева, во всех рядах, кроме пятого элемента И 24 первого ряда, подключены к соответствующим входам ivi-oro элемента ИЛИ 25. 6 ыходы элементов ИЛИ 25 и пятого элемента 24 первого ряда являются выходами блока сдвига. Для более ясного понимания работы устройтва в динамике рассмотрим алгоритм его ункционирования. Используется метод вычисления логарифма ри основании два, заключающийся в следующем. Двоичное число вида in Н-- S2.-2 де Z принимает; значение О или 1, можно представить в виде Z.Z Z(ul4.) 20 ) где к - номер старшего ненулевого разряда числа N. Приближенное значение логарифма по основанию два от N вычисляют по формулам: ,N K + J2 --§,( Х К-«-Л где х вычисляется по следующим формулам если О х 1/4, то x ix-f37Vl28+l/i28(3) если 1/4 X 1/2, то х х+Зх/64+1/16(4) если 1/2 х 3/4, то х (1-х)/64+ +1/32(5) если 3/4 х 1, то х х+29(1-х)/128(6) Погрешность вычисления логарифма при этом не превосходит 0,6%. Так как N является шестиразрядным числом, то X имеет пять разрядов, которые обозначим х, Xg, Xj, Хд, Xj, полагая Xg старшим разрядом. Разряды числа х также обозначим Ул,, Хз xJ, xf. Учтем также, что уравнению (3) соответствует Xs Х4 О, уравнению (4) соответствует Х5 О, Х4 1, уравнению (5) соответствует Xs 1 х« О и уравнению (6) соответствует Xj Х4 1. С использованием .этих соотношетий и уравнений (3)-(5) составляется таблица соответствия х и х. Таблица хз Xj Xi X x/jxf. X xJi I Примечание

744560

Продолжение таблицы;

о о о о о о 1 1

О 1 О

о о 1 1 1 1 о о

о 1 о 1 о 1 о 1

X 5 0

1 о I о 1 Х4

с помощью приведенной таблицы синтезирован алгоритм вьгаисяения х в виде

х x+2(F2VXiX2X3F3) + {(xtXj Ухз)Р,У чПСзР4 VXiXjXsFj} + XtXaXsFi ( (7)

ГДеР «iTsX, , РЗ XsX4, Р4 XsX4 (8)

,41ервый, второй, третий и четвертый выходы дешифратора.

С учетом вышеописанного алгоритма, работа устройства в динамике осуществляется следующим образом.

Шестой, пятый, четвертый, третий и второй разряды числа, от которбгб вычисляется логарифм, подаются на пятый четвертый, третий, второй и первый входы блока 1 управления. На пяти выходах блока 1 управления формируется код, состояиотй из четырех нулей и одной единицы, при этом порядкошй номер выхоДа, на котором сигнал имеет значение логической единицы, соответствует порядковому номеру старщего ненулевого разряда в коде входного числа. Выходы блока 1 управления

-

.- 8

поДКлючеяь ко входам щифратора 13, на трех/ выходах которого образуется двоичный к&д порядка логарифма, соответствующий двоичному коду порядкового нсмфа старшего ненулевого разряда в коде входного числа, от которого вьмисляется, логарифм. Кроме этого, выходы блока 1 управления подключены к управляющим входам блока 2 сдвига, который состоит из пяти рядов элеменOfTOB И 24, на вторые входы которых подаются разряды кода логарифмируемого числа. При этом на второй вход первого слева элемента И 24 первого ряда подается пятый разряд кода логарифмируемого числа, на второй вход

второго элемента И 24 первого ряда подается четвертый разряд кода логарифмируемого числа и т. д. В каждом последующем рядуэлементов И 24 разряды кода логарифмируемого числа Подаются на элементы И 24 со сдигом на один разряд влево, так что на первый слева элемент И 24 второго ряда подается четвертый разряд логарифмируемого числа, на первый слева элемент И 24 третьего ряда - третий разряд и т. д. Первые входы элементов И 24 объединены и соединены с выходами блока 1 управленияТак, что если в коде логарифмируемого числа старшим нулевым разрядом является шестой разряд, то в силу того, что сигнал, соответствующий логической единице имеется на первом йыходе блока управления, открытым является первый ряд элементов И 24, а остальные - закрыты. Аналогично, ее-ли старшим ненулевым разрядом логарифмируемого числа является Пятый, то открытым является второй ряд элементов И 24 . Выходы элементов И 24 всех рядов, имеющие одинаковые порядковые номера, считая слева, объеди- нены с помощью элементов ИЛИ 25. Поэтому на выходах элементов ИЛИ 25 образуется пятиразрядный код остатка Х,йз которого : далее формируетс)9 мантисса логарифма числа N. Выходы Четвертого и третьего, считая справа, элементов ИЛИ 25, являющиеся соответственно пятым и четвертым выходами блока 2 сдвига, подаются на второй и первь{й входы дешифратора 14, который формирует на первом, втором. Третьем и четвертом выходах сигналы, соответствующие функциям FI, Fj, Fa и F4 (уравнение (8)). Кроме этого, пер- . вый, второй, третий, четвертый и пятый выходы блока 2 сдвига соединены с первыми входами первого, второго, третьего, четвертого и пятого разрядов параллельного сумматора 3, а также с соответствующими входами первого элемента И 5, второго элемента И 6, третьего элемента И 7, четвертого элемента И 8, пятого элемента И 9 и шестого элемента И 10, а также первого элемента НЕ 12. Логические элемен:гы И 5, 6, 7, 8, 9, и 10, элементы НЕ 11,: 12, элементы ИЛИ 14 и 15 объединены таким образом, что на выходах элементов ИЛИ 4, ИЛИ 15 и И 10 формируется трехразрядный код поправки, который, суммируясь с кодом Х образует код мантиссы логарифма на вь1ходах румматора 3. Для этого вход элемента И 10 подключен ко входу переноса первого разряда сумматора 3, выход элемента ИЛИ 15 - ко второму входу первого разряда сумматора 3,. выход элемента ИЛИ 4 - ко второму входу третьего разряда сумматора 3. Таким образом, введение в устройство вычисления логарифма новых схем и связей позволяет в течение времени, равному одному такту работы известного устройства, формировать код логарифма при основании два в виде трехразрядного кода порядка и пятиразрядного кода мантиссы числа, представленного шестиразрядаым двоичным параллельным кодом. Дл этой же цели в известном устройстве требует-: ся в среднем не менее десяти тактов работы. В силу этого, предлагаемое устройство обладает более высоким быстродействием. Формула изобретения Устройство для вычисления логарифма, содержащее блок управления, блок сдвига, параллельный сумматор, первый элемент ИЛИ и первый элемент И, причем группа выходов блока управления подключена к первой группе входов блока сдвига, отличающее с я тем, что, с целью повышения быстродейстВИЯ, оно содержит второй, третий, четвертый, пятый элементы И, второй элемент ИЛИ, первый и второй элементы НЕ, дешифратор и шифратор, причем выходы шифратора являются (1-п)-ми выходами устройства, а входы соединены с группой выходов блока управления, группа входов устройства подключена к группе входов блока управления и ко второй руппе входов блока сдвига, первый, второй, ретий, четвертый и пятый выходы которого одключены к первым входам первого, второго, третьего, четвертого и пятого разрядов параллельного сумматора, а первый и второй выходы блока сдвига подключены к первому И второму входам дешифратора, третий, четвертый и пятый выходы блока сдвига подсоединены ко входам первого элемента И, выход которого соединен с первыми входами второго и третьего элементов И и входам первого элемента НЕ, выход которого подсоединен к первому входу первого элемента ИЛИ, второй вход которого подключен к первому; выходу дешифратора, а выход первого элемента ИЛИ подключен ко второму входу второго разряда параллельного сумматора, вторые входы второго и третьего элементов И подключены ко второму и третьему выходам дешифратора, первый и второй вход четвертого элемента И подсоединены к третьему выходу блока сдвига и третьему выходу дешифратора соответственно, третий выход блока сдвига соединен со вхо-. дом второго элемента НЕ, выход которого . подсоединен к первому входу пятого элемента И, второй вход которого подключен к четвертому выходу дешифратора, выход третьего элемента И подсоединен ко входу переноса первого разряда сумматора, выходы второго, четвертого и пятого элементов И подсоединены к первому, второму, третьему и четвертому входам второгоэлемента ИЛИ, выход которого связан со вторым входом второго разряда параллельного сумматора, выходы которого яв;Ляются {(п+1) -()-ми выходами устройства. Источники информации, принятые во внимание при экспертизе 1.Мельников А. А. и др. Обработка частотных и временнь1х импульсных сигналов. Энергия, 1976, с. 81-110. 2.Авторское свидетельство СССР N 448459, кл. G 06 F 7/38, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления логарифмачиСлА | 1979 |

|

SU849210A1 |

| Устройство для вычисления логарифма числа | 1979 |

|

SU860067A1 |

| Логарифмирующее устройство | 1976 |

|

SU634272A1 |

| Устройство для логарифмирования | 1982 |

|

SU1030800A1 |

| Генератор векторов | 1981 |

|

SU1010646A1 |

| Устройство для вычисления функции @ =2 @ | 1981 |

|

SU1057942A1 |

| Цифровой функциональный преобразователь (его варианты) | 1981 |

|

SU1019443A1 |

| Устройство для логарифмирования | 1980 |

|

SU959072A1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| Специализированный процессор | 1977 |

|

SU734705A1 |

И

Фиг.&

Авторы

Даты

1980-06-30—Публикация

1978-03-24—Подача