11474686

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах.

Целью изобретения является повышение быстродействия.

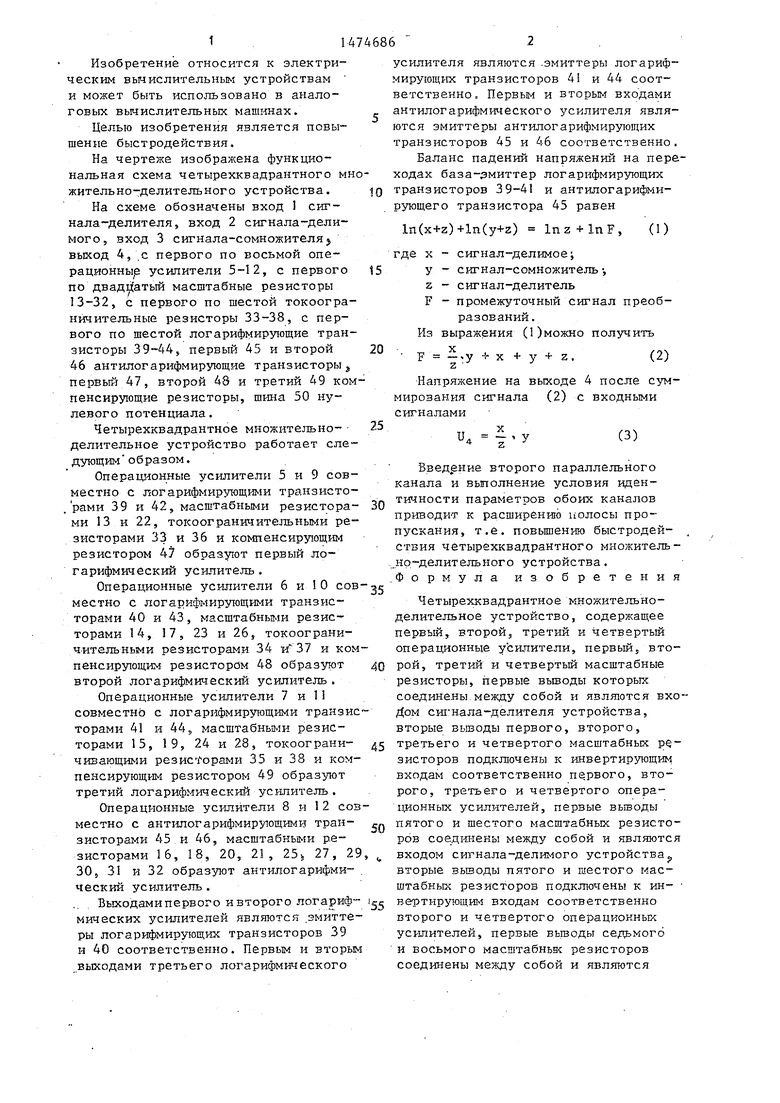

На чертеже изображена функциональная схема четырехквадрантного мноитель но-делитель ног о устройства.tO

На схеме обозначены вход 1 сигала-делителя, вход 2 сигнала-дели- ог о, вход 3 сигнала-сомножителяj выход 4, с первого по восьмой операционные усилители 5-12, с первого 15 о двадцатый масштабные резисторы 13-32, с первого по шестой токоогра- ничительные резисторы 33-38, с первого по шестой логарифмирующие транзисторы 39-44$ первый 45 и второй20 46 антилогарифмирующие транзисторыг первый 47, второй 48 и третий 49 компенсирующие резисторы, шина 50 нулевого потенциала.

Четырехквадрантное множительно- 25 делительное устройство работает следующим образом.

Операционные усилители 5 и 9 совместно с логарифмирующими транзисто- рами 39 и 42, масштабными резистора- 30 ми 13 и 22, токоограничительными резисторами 33 и 36 и компенсирующим резистором 47 образуют первый логарифмический усилитель.

Операционные усилители 6 и 10 сов-35 местно с логарифмирующими транзисторами 40 и 43, масштабными резисторами 14, 17, 23 и 26, токоограничительными резисторами 34 и 37 и компенсирующим резистором 48 образуют второй логарифмический усилитель.

Операционные усилители 7 и 11 совместно с логарифмирующими транзис торами 41 и 44, масштабными резисторами 15, 19, 24 и 28, токоограни- чивающими резисторами 35 и 38 и компенсирующим резистором 49 образуют третий логарифмический усилитель.

Операционные усилители 8 и 12 совместно с антилогарифмирующими тран- зисторами 45 и 46, масштабными резисторами 16, 18, 20, 21, 25s 27, 29 30s 31 и 32 образуют антилогарифмический усилитель.

Выходами первого и второго логариф- мических усилителей являются эмиттеры логарифмирующих транзисторов 39 и 40 соответственно. Первым и вторым выходами третьего логарифмического

усилителя являются эмиттеры логарифмирующих транзисторов 4 и 44 соответственно. Первым и вторым входами антилогарифмического усилителя являются эмиттеры антилогарифмирующих транзисторов 45 и 46 соответственно.

Баланс падений напряжений на переходах база-змиттер логарифмирующих транзисторов 39-41 и антилогарифми- рующего транзистора 45 равен

ln(x+z)+ln(y+z) Inz + lnF, (1)

где х - сигнал-делимое;

у - сигнал-сомножитель-, z - сигнал-делитель F - промежуточный сигнал преобразований. Из выражения (1)можно получить

F - У+x+y+z.(2)

Z

Напряжение на выходе 4 после суммирования сигнала (2) с входными сигналами

U U л

(3)

Введение второго параллельного канала и выполнение условия идентичности параметров обоих каналов приводит к расширению полосы пропускания, т.е. повышению быстродействия четырехквадрантного множитель- но делительного устройства. Формула изобретения

Четырехквадрантное множительно- делительное устройство, содержащее первый, второй, третий и четвертый операционные усилители, первый, второй, третий и четвертый масштабные резисторы, первые выводы которых соединены между собой и являются вхо Дом сигнала-делителя устройства, вторые выводы первого, второго, третьего и четвертого масштабных резисторов подключены к инвертирующим входам соответственно первого, второго, третьего и четвертого операционных усилителей, первые выводы пятого и шестого масштабных резисторов соединены между собой и являются входом сигнала-делимого устройства«, вторые выводы пятого и шестого масштабных резисторов подключены к инвертирующим входам соответственно второго и четвертого операционных усилителей, первые выводы седьмого и восьмого масштабных резисторов соединены между собой и являются

входом сигнала-сомножителя устройства, вторые выводы седьмого и восьмого масштабных резисторов подключены к инвертирующим входам соответственно третьего и четвертого операционных усилителей, первый вывод девятого масштабного резистора подключен к инвертирующему входу четвертого операционного усилителя, первый, второй и третий логарифмирующие транзисторы, коллекторы которых соединены с инвертирующими входами соответственно первого, второго и третьего операционных усилителей, первый антилогарифмирующий транзистор, коллектор которого подключен к инвертирующему входу четвертого операционного усилителя, эмиттер третьего логарифмирующего транзистора соединен с эмиттером первого антилогарифмирующего транзистора, базы первого и второго логарифмирующих транзисторов подключены к шине нулевого потенциала, отличающееся тем, что, с целью повышения быстродействия, в него введены с пятого по восьмой операционные усилители, с десятого по двенадцатый масштабные резисторы, с первого по шестой токоограничи- тельные резисторы, первый, второй и третий компенсирующие резисторы, четвертый, пятый и шестой логарифмирующие транзисторы, второй антилогарифмирующий транзистор, причем выход первого операционного усилителя через первый токоограничительный резистор соединен с эмиттером первого логарифмирующего транзистора, с первым выводом первого компенсирующего резистора и с базами первого и второго антилогарифмирующих транзисторов, выход второго операционного усилителя через второй токоограничительный резистор подключен к эмиттеру второго логарифмирующего транзистора, к первому выводу второго компенсирующего резистора и к базе третьего логарифмирующего транзистора, выход третьего операционного усилителя через третий токоограничительный резистор соединен с эмиттером третьего логарифмирующего транзистора и с первым выводом третьего компенсирующего резистора, выход пятого операционного усилителя подключен к второму выводу первого компенсирующего резистора, а через чет0

5

0

5

0

5

0

5

0

5

вертый токоограничительный резистор соединен с эмиттером четвертого логарифмического транзистора, коллектор которого соединен с инвертирующим входом пятого операционного усилителя, выход шестого операционного усилителя подключен к второму выводу второго компенсирующего резистора, а через пятый токоограничительный резистор соединен с эмиттером пятого логарифмирующего транзистора, коллектор которого подключен к инвертирующему входу шестого операционного усили- теляд. выход седьмого операционного усилителя соединен с вторым выводом третьего компенсирующего резистора, а через шестой токоограничительный резистор подключен к эмиттеру шестого логарифмирующего транзистора, коллектор которого соединен с инвертирующим входом седьмого операционного усилителя, эмиттер шестого логарифмирующего транзистора соединен с эмиттером второго антилогарифмирующего транзистора, коллектор которого подключен к инвертирующему входу восьмого операционного усилителя, выход которого является выходом устройства и соединен с вторым выводом девятого масштабного резистора, база шестого логарифмирующего транзистора соединена с базой третьего логарифмирующего транзистора, первый вывод первого масштабного резистора через десятый масштабный резистор подключен к инвертирующему входу пятого операционного усилителя, первый вывод четвертого масштабного резистора соединен с первыми выводами одиннадцатого, двенадцатого и тринадцатого масштабных резисторов,первый вывод шестого масштабного резистора соединен с первыми выводами четырнадцатого и пятнадцатого масштабных резисторов, первый вывод восьмого масштабного резистора подключен к первым выводам шестнадцатого и семнадцатого масштабных резисторов, вторые выводы тринадцатого, пятнадцатого и семнадцатого масштабных резисторов соединены с инвертирующим входом восьмого операционного усилителя, а через восемнадцатый масштабный резистор соединены с выходом восьмого операционного усилителя, к неинвертирующему входу которого подключены первые выводы девятнадцатого и двадцатого масштабных ре514746866

зисторов, второй вывод девятнадцатогоцатого масштабных резисторов соедимасштабного резистора соединен с вы-нены с инвертирующим входом седьмого

ходом четвертого операционного усили-операционного усилителя, базы четвертеля, вторые выводы одиннадцатого итого и пятого логарифмирующих транчетырнадцатого масштабных резисторовзисторов и второй вывод двадцатого

подключены к инвертирующему входумасштабного резистора подключены к

шестого операционного усилителя,шине нулевого потенциала. вторые выводы двенадцатого и шестнад

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1987 |

|

SU1539798A1 |

| Множительно-делительное устройство | 1987 |

|

SU1543426A1 |

| Вычислительное устройство | 1985 |

|

SU1282163A1 |

| Вычислительное устройство | 1987 |

|

SU1462364A1 |

| Логарифмическое вычислительное устройство | 1987 |

|

SU1543425A1 |

| Устройство регулирования уровня сигнала | 1982 |

|

SU1104653A1 |

| Аналоговое логарифмическое вычислительное устройство | 1982 |

|

SU1095198A1 |

| Устройство с регулируемым усилением | 1988 |

|

SU1741257A1 |

| Устройство усиления | 1985 |

|

SU1338001A1 |

| Аналоговое логарифмическое вычислительное устройство | 1983 |

|

SU1137486A2 |

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах. Целью изобретения является повышение быстродействия. Четырехквадрантное множительно-делительное устройство имеет входы сигнала-делителя 1, сигнала-делимого 2 и сигнала-сомножителя 3, выход 4 и содержит операционные усилители 5-12, масштабные резисторы 13-32, токоограничительные резисторы 33-38, логарифмирующие транзисторы 39-44, антилогарифмирующие транзисторы 45 и 46, компенсирующие резисторы 47-49, шину нулевого потенциала 50. Работа устройства основана на реализации логарифмического алгоритма взятия антилогарифма от алгебраической суммы логарифмов сигналов. 1 ил.

| Патент США № 4004141, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Патент США № 3940603, кл, 235-196, опублик | |||

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

Авторы

Даты

1989-04-23—Публикация

1987-07-08—Подача