со со со со

4:

Изобретение относится к контрольи о-измерительной технике и может ыть использовано для контроля логиеских блоков средств ЦВТ.

Наиболее близким к предлагаемоу является устройство для контроля огических блоков, содержащее блок правления, блок памяти, соеди{1енм ный рходом с первым выходом блока правления, а выходами - с первыми ходами блока упра.вления, регистр теста, выходы которого соединены соответственно с первыми входами: элементов сравнения и первыми входам и элементов коммутации, вторые ходы которых соединены с третьими выходами блока управления, третьи с- выводами крнтролируемого блока и с вторыми входами соответствующих элементов сравнения, выходы которых соединены с входами блока управления, генератор импульсов, триггер, счетчик, дешифратор, первый эяемент И и по числу входов регистра теста - вторые элементы И, первые

входы которых соединены с соответствующими выходами блока записи информации, вторые входы с соответствующими выходами дешифратора, выходы - с входами регистра теста, первые .входы дешифратора подключены к первым выходам счетчика, второй вькод которого соединен с третьими входами элементов, сравнения и первым в содом триггера, второй вход которого .соеди-нён с первым выходом блока управления, третий вход - с четвертым выхо.п дом бЛока управления, а выход - с; первым входом элемента И, второй вход которого подключен к выходу генератора импульсов, а выход - к ; входу счетчика и второму входу дешифратора 1 .

Недостатком известного устройства является низкое быстродействие, обусловленное тем, что наборы контролирукйцего теста осуществляется на штеккерном наборном поле ,вручную, при этом допускаются иоГбки. Указанные ошибки приводят к значительному количеству остановов при контроле по неверным текстам и дополнительным затратам времени

на отыскание ошибок в тесте.

Цель изобретения - повышение быстродействия устройства.

Указанная цел% достигается тем, что устройство для контроля-логических блоков, содержащее блок управления, блок памяти, соединенный входом, с первым выходом блока управления а выходами - с первыми входами блока записи, второй вход которого соединен с. вторым выходом блока управления, регистр теста, выходы которого соединены

с первыми входами элементов сравнения и первыми входами элементов коммутации, вторые входы которых соединены с третьими выходами блока управления, третьи - с выв.одами :контролируемого блока и с вторыми входами соответствующих-..- элементов ср.авнения, выходы которых соединены с входами блока управления, reft нератор импульсов, триггер, счетчик дешифратор, первый элемент И и по числу входов регистра теста вторые элементы И, первые входы которых соединены с соответствующими вы одами блока записи информации, влорые входы - с соответствующимивыходами дешифратора, выходы - с входами регистра теста, первые входы дешифратора подключены к первым выходам счетчика, второй выход которого соединен- с третьими входами элементов сравнения и первым входом триггера, второй вход которого соединен с первым выходом блока управления, третий вход с четвертым выходом блока управления, а выход - с первым входом первого элемента И, второй вход которого подключен к выходу генератора импульсов, а выход - ко входу счетчика .и второму входу дешифратора, введены буферный регистр, первый преобраз.ователь кодов, перфоратор, второй блок памяти, считыватель, второй преобразователь кодов, соединенный выходами с входами блока записи, входом - с выходом сч.итывателя, первый вход которого подключен к первому выходу блока управления и первому входу перфоратора, второй вход - к выходу второго I блока памяти, соединенного входом с выходом перфоратора, второй вход которого соединен с выходом первого преобразователя кодов, третий вход с вторым выходом счетчика и первым входом буферного регистра, подключенного вторыми входами к выходам

регистра теста, а выходом - к входу первого преобразователя кодов.

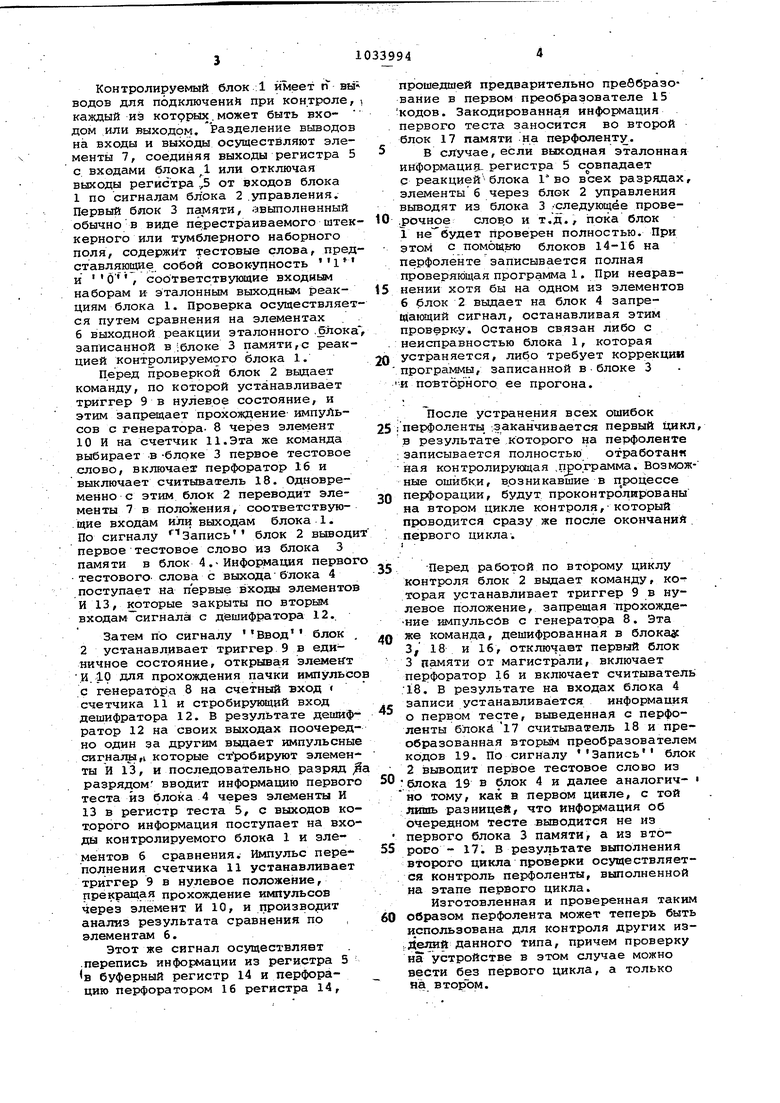

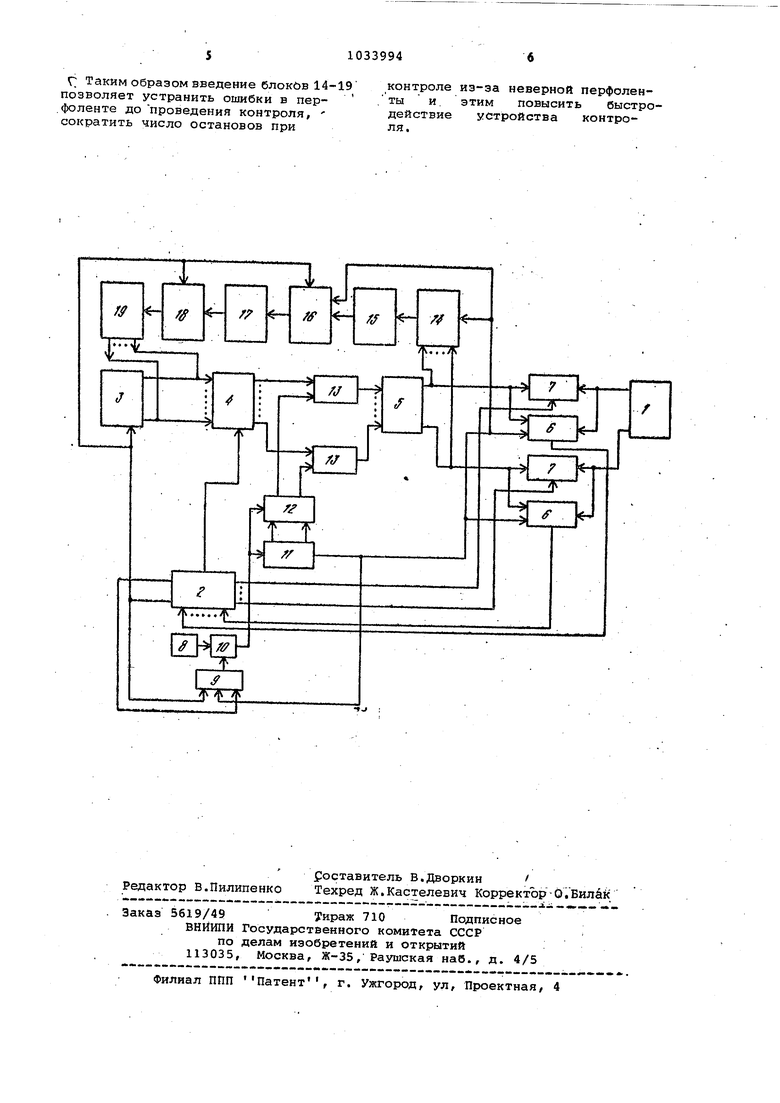

На чертеже приведена блок-схема устройства; для контроля логического блока.

Устройство содержит блок 2 Управления, первый блок 3 памяти, блок

4 записи, регистр 5 теста, элементы б сравнения, элементы 7 коммутации, 1ене ратор 8 импульсов, триггер Э, первый элемен г 10 И, счетчик 11, дешифратор 12- вторые элементы И 13,

буферный регистр 14, первый преобразователь 15 кодов,перфоратор 16, второй блок 17 памяти, считьиэат1ель 18, второй преобразователь 19 кодов. Устройство работает следующим

образом.

Контролируемый блок ;1 имеет п вы водов для подключений при контроле, каждый из КОТ9РЫХ.может быть вхо- дом или выходом, разделение выводов на входы и выходы осуществляют элементы 7, соединяя выходы регистра 5 с. входами блока 1 или отключая выходы регистра ,5 от входов блока

1по сигналам блока 2 .управления. Первый блок 3 памяти, авыполненный обычно в виде перестраиваемого штеккерного или тумблерного наборного поля, содержит тестовые слова, представляющие собой совокупность и б , соответствующие входньаи наборам и эталонным выходным реакциям блока 1. Проверка осуществляется путем сравнения на элементах . б выходной реакции эталонного .блока записанной в ;блоке 3 памяти,с реакцией контролируемого блока 1,

Перед проверкой блок 2 выдает команду, по которой устанавливает триггер 9 в нулевое состояние, и этим запрещает прохождение- импуЛьсов с генератора- 8 через элемент 10 И на счетчик 11.Эта же команда выбирает .в-блоке 3 первое тестовое -СЛОВО, включаем перфоратор 16 и выключает считывассель 18. Одновременно с этим блок 2 переводит элементы 7 в положения, соответствую.щие входам или выходам блока 1. По сигналу Запись блок 2 выводи первое тестовое слово из блока 3 памяти в блок 4.-Информация первог тестового слова с выхода блока 4 поступает на первые входаа элементов И 13, которые закрыты по вторым входам сигнала с дешифратора 12,.

Затем по сигналу Ввод блок

2устанавливает триггер 9 в единичное состояние, открывая элемент

И. 10 для прохождения пачки импульсо .с генератор.а 8 на счетный вход счетчика 11 и стробирующий вход дешифратора 12, В результате дешифратор 12 на своих выходах поочередно один за другим вьщает импульсные сигнада,1 которые стробируют элемен- ты И 13, и последовательно разряд разрядом вводит информацию первого теста из блока 4 через элементы И 13 в регистр теста 5, с выходов которого информация поступает на входы контролируемого блока 1 и элементов б сравнения. Импульс переполнения счетчика 11 устанавливает триггер 9 в нулевое положение, прекращая прохождение импульсов через элемент И 10, и производит анализ результата сравнения по элементам б.

Этот же сигнал осуществляет .перепись информации из регистра 5 в буферный регистр 14 и перфорацию перфоратором 16 регистра 14,

прошедшей предварительно преббразование в первом преобразователе 15 кодов. Закодированная инфopvIaция первого теста заносится во второй

блок 17 памяти на перфоленту. в случае, если выходная эталонная информацией регистра 5 совпадает с реакциейблока 1 во вЪех разрядах, элементы 6 через блок 2 управления выводят из блока 3 /следующее проверочн е слов.о и т.д., пока блок

1 не будет проверен полностью. При этом с помощь-ю блоков 14-16 на перфоленте записывается полная проверяющая программа 1. При неаравнении хотя бы на одном из элементов 6 блок 2 выдает на блок 4 запрещающий сигнал, останавливая этим проверк-у. Останов связан либо с неисправностью блока 1, которая устраняется, либо требует коррекции программы, записанной в - блоке 3 -и повторного ее прогона.

После устранения всех ошибок перфоленты .заканчивается первый цикл, в результате которого на перфоленте записывается полностью отработаня на я контролирующая .программа. Возможные ошибки, возникавшие в п роцессе перфорации, будут проконтролированы на втором цикле контроля,-который проводится сразу же после окончания

первого цикла.

I

-Перед работой по второму циклу контроля блок 2 выдает команду, которая устанавливает тригге1р 9 в нулевое положение, запрещая прохождение импульсов с генератора 8, Эта

ж команда, дешифрованная в блокад 3, 18 и 16, отключает первый блок 3 памяти от магистрали, включает перфоратор 16 и включает считыватель 18. В результате на входах блока 4

записи устанавлива ется информация

о первом тесте, выведенная с перфоленты блоки 17 считыватель 18 и преобразованная BTOpbiM преобразователем кодов 19. По сигналу Запись блок 2 выводит первое тестовое слово из блока 19 в блок 4 и далее аналогич- но тому, как а первом цинле, с той лишь разницей, что информация об очередном тесте вьшодится не из первого блока 3 памяти, а из второго - 17. в результате выполнения

второго цикла проверки осуадествляет. ся контроль перфоленты, выполненной на этапе первого цикла.

Изготовленная и проверенная таким 0 образом перфолента может теперь быть и спользована для контроля других из.Йелий данного типа, причем проверку на устройстве в этом случае можно вести без первого цикла, а только на вторЪм.

Г Таким образом введение блокйв 14-19 позволяет устранить ошибки в пер.фоленте до проведения контроля, сократить число остановов при

контроле иэ-эа неверной перфоленты и. этим повысить быстродействие устройства контроля.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для изготовления и контроля полнокодовой перфоленты | 1983 |

|

SU1118555A1 |

| Устройство для подготовки информации на перфоленте | 1977 |

|

SU684549A1 |

| Устройство для регистрации данных по табельному учету | 1982 |

|

SU1027746A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Устройство для тестового контроля блоков радиоэлектронной аппаратуры | 1980 |

|

SU905887A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для диагностики логических блоков | 1983 |

|

SU1095182A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для контроля логических блоков | 1980 |

|

SU868763A1 |

| Графический дисплей с контролем | 1984 |

|

SU1249526A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ.БЛОКОВ ПО ав. св. № 868763, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены буферный регистр, первый преобразователь кодов, перфоратор, второй блок памяти, считыватель, второй преобразователь кодов,соединенный выходами с вxoдa в блока записи ,входом с выходом Гсчитывателя, первый вход которого подключен, к первому выходу блока управления и-первому входу перфоратора, второй вхрд - к выходу второго блока памяти, соединенного входом с выходом перфоратора, второй вход которого соединен с выходом первого преобразователя кодов, третий вход - с вTopbw выходом счетчика и первым входсм буферного perHCTpS/ подключенного вторыми входами к выходам регистра теста, а выходом- к входу первого преобразо- , , вателя кодов.(Л с

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля логических блоков | 1980 |

|

SU868763A1 |

| С, 01F 11/04, 1982 | |||

| (прототип). | |||

Авторы

Даты

1983-08-07—Публикация

1982-03-25—Подача