Изобретение относится к контрольно-измерительной технике .и.может быть использовано для контроля блоков радиоэлектронной аппаратуры.

Известно устройство для тестового контроля цифровых узлов ЦВМ, содержащее блок памяти, блок ввода, регистр тестов, схемы .сравнения, индикаторы и формирователи входных сигналов 1 .

Недостатком известного устройства является низкое быстродействие при контроле цифровых блоков, содержащих большое число однотипных ячеек, например полупроводниковых многоадресных оперативных запоминающих устройств. Низкое быстродействие обусловлено большими затратами времени на задание программы контроля, состоящей из большого числа одинаковых программ для каждой из цифровых ячеек памяти, задаваемых по разным адресам ячеек.

Наиболее близким техническим решением к изобретению является устройство для контроля цифровых узлов, содержащее блок ввода, блок памяти, регистр настройки, коммутатор входов и выходов, блок сравнения и блок управления, причем первый вход

блока ввода соединен с первыми входами блока памяти и регистра -настроПки, второй вход - с первым входом блока управления, первый, второй и третий выходы которого соединены со входом блока ввода, вторым входом блока памяти и.,вторым входом регистра настройки соответственно-, выход блока памяти соединен с первыми входами блока сравнения и первого коммутатора входов и выходов, второй вход которого подключен к выходу регистра настройки, выход - к второму входу блока сравнения и выводу контролируемого блока, а выход блока сравнения соединен со вторым входом блока управления 2.

Недостатком этого устройства является низкое быстродействие при

20 контроле блоков, состоящих из однотипных цифровых ячеек, имеющих однородную структуру, тестовую программу которых можно представить в виде общей многократно повторяющейся части-программы контроля одной ячейки и переменной, меняющейся от цикла к циклу части-программы управления, адресующей программу контроля.

Цель изобретения - повышения быстродействия устройства.

Поставленная цель достигается тем, что в устройство для тестового контроля блоков радиоэлектронной аппаратуры, содержащее блок ввода, соединенный первым входом с первыми входами блока памяти и регистра настройки, вторым - с первым входбм блока управления, первый, второй и третий выходы которого подключены ко входу блока ввода, ко второму входу блока памяти и второму входу регистра настройки соответственно , выход блока памяти соединен с первыми входами блока сравнения и первого .коммутатора, второй вход которого соединен с выходом регистра настройки, выходы - с выводами контролируемого блока и со вторым входом блока сравнения; выход которого соединен со вторым входом блока управления, введены счетчик второй коммутатор, дешифратор, задатчик адресов, программный блок, блок контактных элементов, регистр адреса, соединенный своим выходом с третьим входом первого коммутатора, а входами - с первыми выходами дешифратора, второй выход которого соединен с третьим входом блока управления, входы - с выходами второго коммутатора, первый и вторые входы которого соединены соответственно с выходом блока контактных элементов и выходами счетчика, соединенного входом с четвертым выходом .блока управления вход блока контактных элементов.соединен с первым выходом программного блока, соединенного вторым и входом с входом и выходом задатчика адресов соответственно.

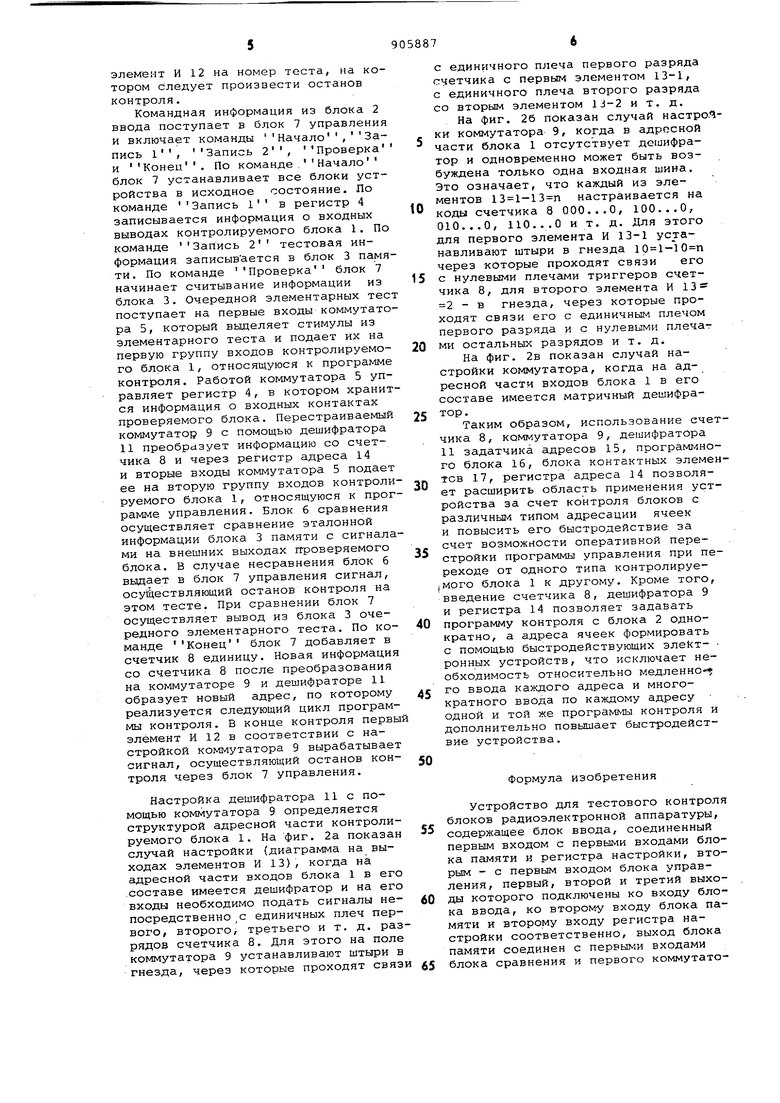

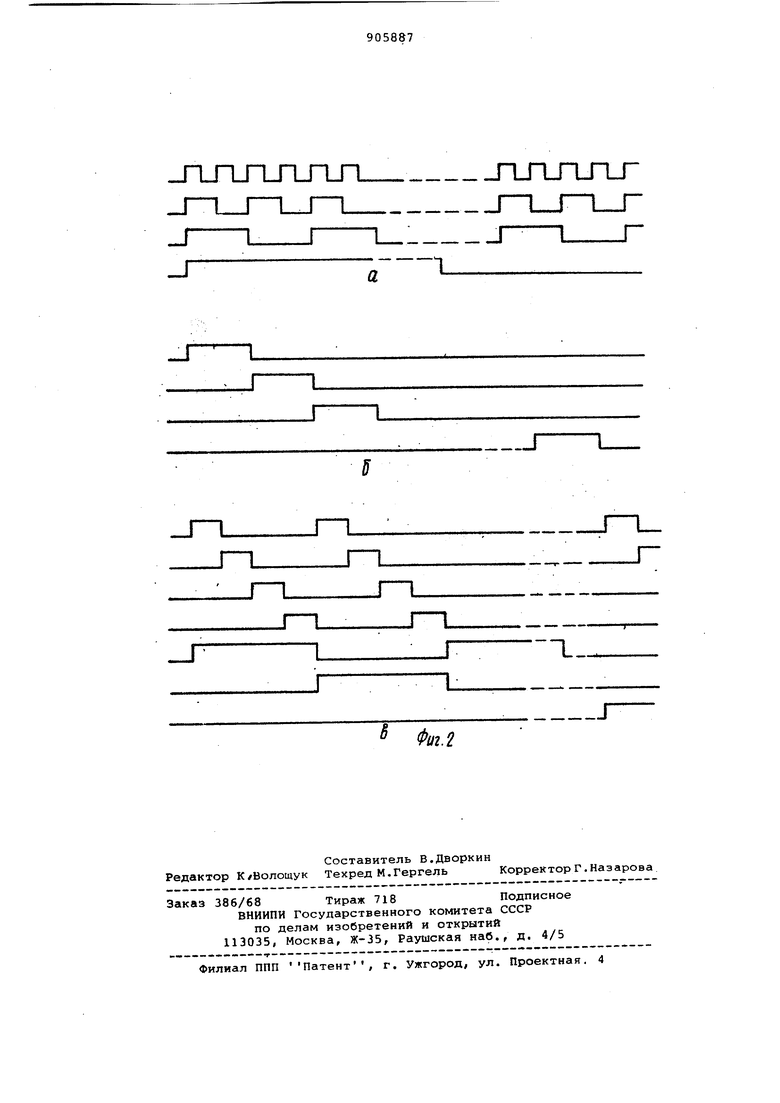

Ка фиг. 1 приведена блок-схема устройства для тестового контроля блоков радиоэлектронной аппаратуры; на фиг. 2 - временные диаграммы.

Устройство для контроля блоков 1 содержит блок 2 ввода, блок .3 памяти регистр 4 настройки, коммутатор 5 входов и выходов, блок 6 сравнения, .7 управления, счетчик 8, коммутатор 9f содержащий гнезда дешифратор 11, содержащий первый 12 и вторые элементы И, регистр 14 адреса, задатчик 15 адресов, програг/лу1ный блок 16, блок 17 контактных элементов. На фиг. 2 приведены временные диаграь-Й Ш на выходах вторых элементов И дешифратора 11 для разных типов проверяемых блоков. Блок 2 ввода предназначен для ввода с перфоленты тестовой информации, информации о входных (выходных) контактах к командной информации. Блок -3 памяти предназначен для хранения и выдачи тестовой информации. Регистр 4 настройки, разрядность которого равна числу вьаводов контролируемого блока 1, служит для управления коммутатором 5, осуществляющим передачу

сигналов на входы контролируемого блока 1. Блок 6 сравнения предназначен для сравнения кодов эталонов с сигналами на выводах контролируемого блока. Блок 7 управления организует работу всех блоков устрой.ства, т. е. управляет записью информации из блока 2 ввода в блок 3 памяти и регистр 4 настройки, управляет работой счетчика 8, который служит для получения информации

0номере цикла программы контроля. Коммутатор 9, содержащий коммутационные гнезда обеспечивае перестройку программы управления при переходе от одного типа контролируемого блока к другому. Дешифратор 11

с помощью первого элемента И 12 формирует сигнал, управляющий остановом контроля на заданном номере цикла программы контроля, а с помощью вторых элементов И .обеспечивает формирование информации программы управления, меняющейся от цикла к циклу. Регистр 14 адреса предназначен для передачи .информации программы управления с дешифратора. 11 через коглмутатор 5 на адресные входы контролируемого блока 1, а задатчик 15 адресов, выполненный,например, в виде тестовых таблиц - для записи программы управления. Программный блок 16 обеспечивает установку контактирующих штырей из блока 17 контактных элементов в гнезда коммутатора 9 в соответствии с адресами контактов, полученнЕлми с задатчика 15.

Устройство работает следующим образом.

Контроль блока 1 осуществляется с помощью программы, состоящей из последовательности элементарных тестов, разрядность которых равна числу выводов контролируемого блока 1. Каждый элементарный тест включает в себя входные стимулы и эталоны выходных реакций. Входные стимулы совокупность сигналов, одновременно подаваемых на входные выводы, поступают к ним двумя путями: первая часть стимулов, касающаяся программы контроля, поступает из блока 3 памяти через коммутатор 5, вторая часть стимулов, касающихся Программы управления, поступает на блок

1с регистра адреса 14 через коммутатор 5.

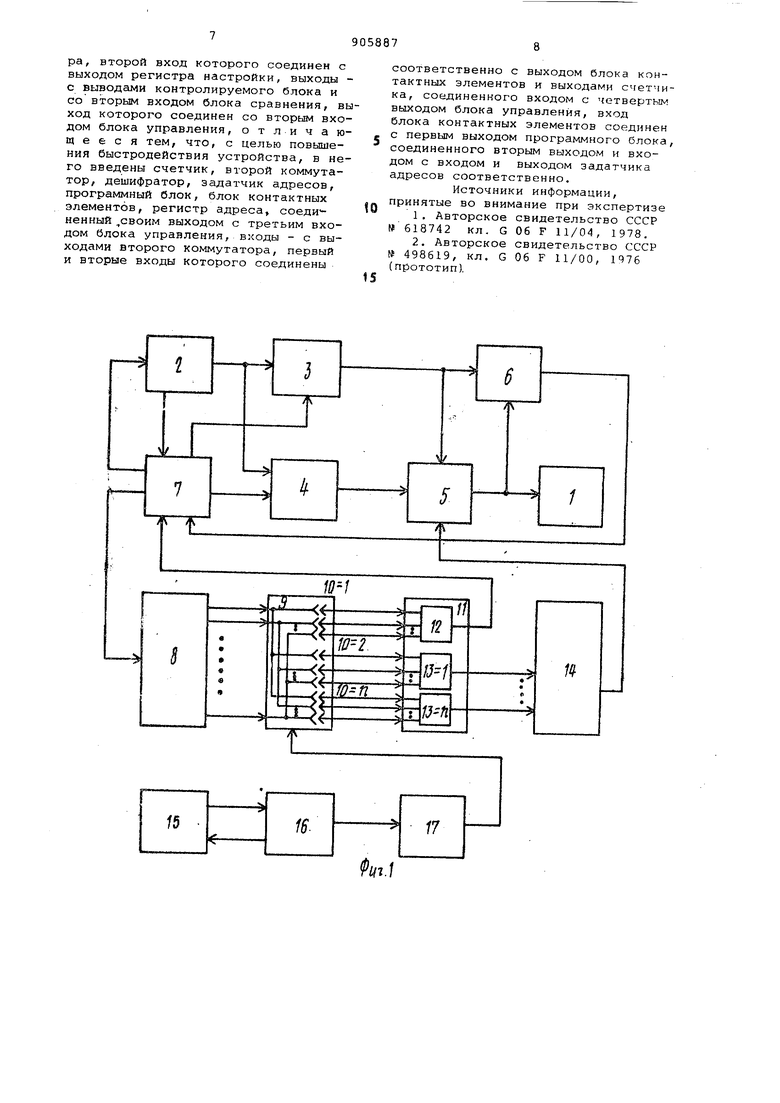

Перед началом работы блок 16 в соответствии с тестовой таблицей задатчика 15 адресов, установкой штырей из блока 17 в гнезда коммутатора 9 настраивает программу управления, поступающую в блок 1 через вторые выходы элемента И дешифратора 11, через регистр адреса 14 и коммутатор 5. Алалогично блок 16 настраивает с помощью коммутатора 9 первый элемеит И 12 на номер теста, на котором следует произнести останов контроля. Командная информация из блока 2 ввода поступает в блок 7 управления и включает команды Начало,Запись 1, Запись 2, Проверка и Конец. По команде Начало блок 7 устанавливает все блоки устройства в исходное состояние. По команде Запись 1 в регистр 4 записывается информация о входных выводах контролируемого блока 1. По команде Запись 2 тестовая информация записывается в блок 3 памя ти. По команде Проверка блок 7 начинает считывание информации из блока 3. Очередной элементарных тес поступает на первые входы коммутато ра 5, который выделяет стимулы из элементарного теста и подает их на первую группу входов контролируемого блока 1, относящуюся к программе контроля. Работой коммутатора 5 управляет регистр 4, в котором хранит ся информация о входных контактах проверяемого блока. Перестраиваемый коммутатор 9 с помощью дешифратора 11 преобразует информацию со счетчика 8 и через регистр адреса 14 и вторые входы коммутатора 5 подает ее на вторую группу входов контроли руемого блока 1, относящуюся к прог рамме управления. Блок б сравнения осуществляет сравнение эталонной информации блока 3 памяти с сигнала ми на внешних выходах Проверяемого блока. В случае несравнения блок б выдает в блок 7 управления сигнал, осуЦ1ествляющий останов контроля на этом тесте. При сравнении блок 7 осуществляет вывод из блока 3 очередного элементарного теста. По команде Конец блок 7 добавляет в счетчик 8 единицу. Новая информация со счетчика 8 после преобразования на коммутаторе 9 и дешифраторе 11 образует новый адрес, по которому реализуется следующий цикл программы контроля. В конце контроля первы элемент И 12 в соответствии с настройкой коммутатора 9 вырабатывает сигнал, осуществляющий останов контроля через блок 7 управления. Настройка дешифратора 11 с помощью коммутатора 9 определяется структурой адресной части контролируемого блока 1. На фиг. 2а показан случай настройки (диаграмма на выходах элементов И 13), когда на адресной части входов блока 1 в его .составе имеется дешифратор и на его входы необходимо подать сигналы непосредственно , с единичных плеч первого, второго, третьего и т. д. разрядов счетчика 8. Для этого на поле коммутатора 9 устанавливают штыри в гнезда, через которые проходят связи с единичного плеча первого разряда счетчика с первым элементом 13-1, с единичного плеча второго разряда со вторым элементом 13-2 и т. д. На фиг. 26 показан случай настроЯки коммутатора 9, когда в адресной части блока 1 отсутствует дешифратор и одновременно может быть возбуждена только одна входная шина. Это означает, что каждый из элементов настраивается на коды счетчика 8 000...О, 100...О, 010...О, 110...О и т. д. Для этого для первого элемента И 13-1 устанавливают штыри в гнезда lp l-iO n через которые проходят связи его с нулевыми плечами триггеров счетчика 8, для второго элемента И 13 2 - в гнезда, через которые проходят связи его с единичным плечом первого разряда и с нулевыми плечаг ми остальных разрядов и т. д. На фиг. 2в показан случай настройки коммутатора, когда на адресной части входов блока 1 в его составе имеется матричный дешифратор. Таким образом, использование счетчика 8, коммутатора 9, дешифратора 11 задатчика адресов 15, програм1.1ного блока 16, блока контактных элементов 17, регистра адреса 14 позволяет расширить область применения устройства за счет контроля блоков с различным типом адресации ячеек и повысить его быстродействие за счет возможности оперативной перестройки программы управления при переходе от одного типа контролируеМого блока 1 к другому. Кроме того, введение счетчика 8, дешифратора 9 и регистра 14 позволяет задавать программу контроля с блока 2 однократно, а адреса ячеек формировать с помощью быстродействующих элеКт- ронных устройств, что исключает необходимость относительно медленно- го ввода каждого адреса и многократного ввода по каждому адресу одной и той же программы контроля и дополнительно повышает быстродействие устройства. Формула изобретения Устройство для тестового контроля блоков радиоэлектронной аппаратуры, содержащее блок ввода, соединенный первым входом с первыми входами блока памяти и регистра настройки, вторым - с первым входом блока управления, первый, второй и третий выходы которого подключены ко входу блока ввода, ко второму входу блока паяти и второму входу регистра настройки соответственно, выход блока памяти соединен с первыми входами блока сравнения и первого коммутатоpa, второй вход которого соединен с выходом регистра настройки, выходы с выводами контролируемого блока и со вторым входом блока сравнения, в ход которого соединен со вторым вхо дом блока управления, отличаю щееся тем, что, с целью повышения быстродействия устройства, в не го введены счетчик, второй коммутатор, дешифратор, задатчик адресов, программный блок, блок контактных элементов, регистр адреса, соеди ненный ,своим выходом с третьим входом блока управления, входы - с выходами второго коммутатора, первый и вторые входы которого соединены соответственно с выходом блока контактных элементов и выходами счетчика, соединенного входом с четвертым выходом блока управления, вход блока контактных элементов соединен с первым выходом программного блока, соединенного вторым выходом и входом с входом и выходом задатчика адресов соответственно. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР № 618742 кл. G 06 F 11/04, 1978. 2.Авторское свидетельство СССР № 498619, кл. G 06 F 11/00, 1976 (прототип). гъ1гг1л г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1262504A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1003090A1 |

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

| Устройство для контроля логических блоков | 1978 |

|

SU734694A1 |

| Устройство для задания тестов | 1983 |

|

SU1168951A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Устройство для контроля логических блоков | 1980 |

|

SU868763A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для контроля логических блоков | 1982 |

|

SU1033994A2 |

-j

-jn

I

T.

г

Фи2.2

Авторы

Даты

1982-02-15—Публикация

1980-05-30—Подача