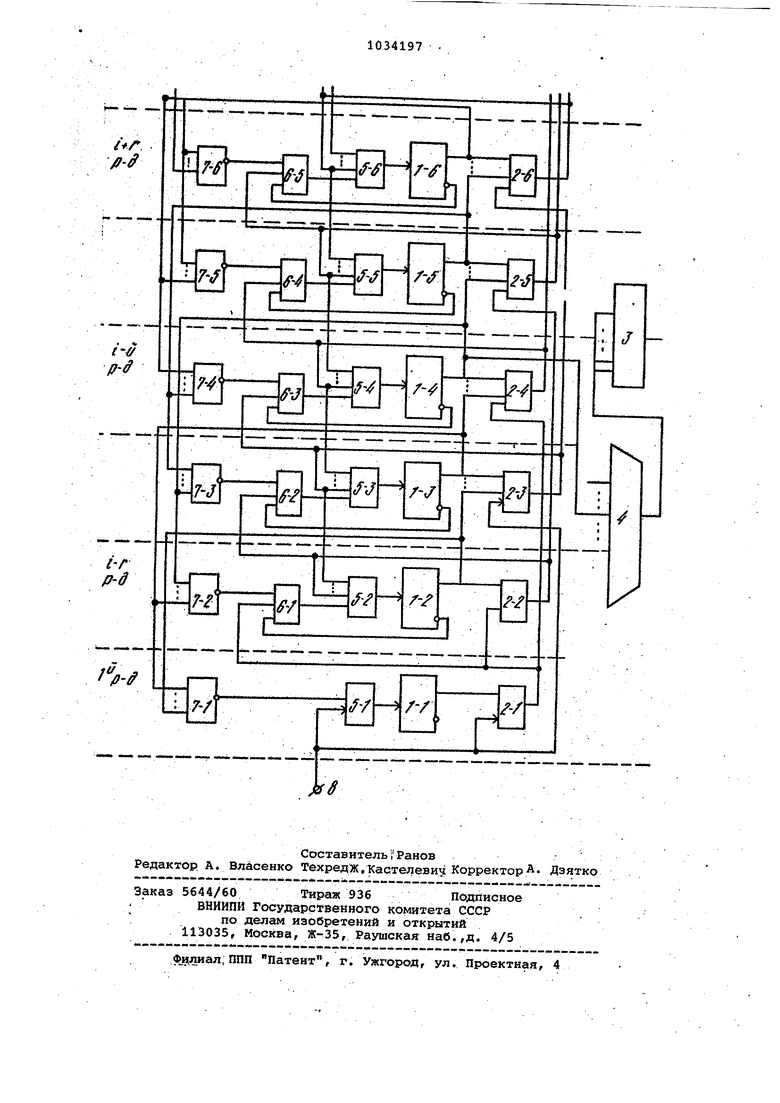

Изобйет евие относится к 8ы(числительной технике и .Л1ожет быть использовано при построении цифровы}4 устройств помщР-Щтр иврй обработки информации. . Известен двоичный счетчик с после довательным переносом, содержащий в каждом разряде триггер со счетным входом и элемент И, причем единичный выход триггера соединен с одним из входов элемента И, второй вход элемента И соединен со счетной управ ляющей шиной (1. Недостаток приведенного счетчика заключается в том, что он не позволя ет обнаруживать определенные виды ош бок, возникающие в результате неисправной работы устройства, Известен двоичнйй счетчик с последовательным переносом для работы в Фибоначчиевых системах счисления, содержащий входную шину,дешифратор полных состояний, многовходовый элемент ИЛИ, а в каждом i-M разряде, .кроме первого, счетный триггер, дв§ элемента И, элемент ИЛИ, прямой выход счетного триггера соединен с одним из входов дешифратора полных состояний и с первым входом первого элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход и выход которого соединены соот ветственно с выходом второго элемента И и с тактовым входом счетного триггера, инверсный выход которого соединен с первым входом второго элементами, второй вход которого сое динен с выходом первого элемента И предыдущего разряда, второй вход пе вого элемента И соединен с выходом первого элемента И соответствующего Младшего разряда, г. других входов второго элемента И соединены с ин- . версными выходами счетных триггеров последующихг разрядов, выходы Дешифратора полных состояний соединены с входами многовходового элемента ИЛИ, первый разряд содержит счетный триггер,два элемента Ни элемент ИЛ выход которого соединен с тактовым входом счетного т риггера, прямой и инверсный выходы которого соединены соответственно с. первыми входами первого и второго элементов И С2. Недостаток приведенного прототипа заключается в том, что он ограни чивает функциональные возможности . помехоустойчивых счетчиков, использующих избыточные.(г , Р) системы счи ления, допуская изменения лишь характеристичвскогб параметра Р и не позволяет производить функцию счета при изменении характеристического параметра г . Цель изобретения - расширение функциональных возможностей, за1ключающееся в выполнении дополнител ной функции помехоустойчивого счета импульсов в {г,1 ) системе счисления, при сохранении функции помехоустой- чивого счета в Фибрначчиевой системе счисления. г Поставленная «ель достигается тем, что в двоичном счетчике с последовательным переносом, преимущест- венно для работы в {г,1) системе счисления, содержащем входную шину, дешифратор полных состояний, многовходовый элемент ИЛИ, а в каждом i-M разряде, кроме первого, счетный триггер, два элемента И, элемент:ИЛИ, прямой выход счетного триггера соединен с одним из входов дешифратора полных состояний и с первым входом первого элемента И, выхОд которого соединен с первым входом элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом второго элемента И и с тактовым входом счетного триггера, инверсный выход которого соединен с первым входом второго элемента И, второй вход которого соединен с выходом первого элемента И |предыдущего разряда, второй вход первого элемента И соединен с выходом первого элемента И соответствующего младшего разряда, выходы дешифратора полных сбстояний соединены с входами многовходового элемента ИЛИ, первый разряд содержит счетный триггер, элемент И и элемент ИЛИ, выход которого соединен с тактовым входом счетного триггера, прямой выход которого соединен с первым входом элемента И, в каяодый 1-й разряд введен элемент И-НЕ, г входов которого соединены с прямыми выходами счетных триггеров последующих г разрядов, а выход элемента И-НЕ соединен с третьим входом второго элемента И, с. третьего по входы. элемента ИЛИ соединены соответственно с выходами первых элементов И с i+1 по Л (г-1) разрядов с третьего по г+1-й входы первого элемента И соединены соответственно с прямыми выходами счетных триггеров с .1-1 по -(г-1) разрядов в первом разряде, выход элемента И-НЕ соединен с первым входом элемента ИЛИ, второй вход которого соединен с входной шиной/ с вторым входом элемента И с одним из входов первого элемента и соответствующего старшего разряда. На чертеже изображена структурная электрическая схема предлагаемого счетчика. Двоичный счетчик с последовательным переносом содержит :счетные триггеры 1-1 4 1-6, элемент 2-1 2-6 и элемент 3 ИЛИ, дешифратор 4 полных состояний, вторые элементы 5-1 - 5-6 ИЛИ, элементы 6-1 - 6-5 И, элементы 7-1 - 7-6 И-НЕ, входную шину 8. .. Элементы 7-1 И-НЕ, 5-1 ИЛИ, 2-1 И и счетный триггер 1-1 составляют первый разряд. Элементы 7-2 И-НЕ, 5-2 ИЛИ, 6-1, 2-2 ТЛ и счетный триггер 1-2 составляют 1-г-й разряд. Элементы 7--4 И-НБ, 5-4 ИЛИ, 6-3, 2-4 И и счетный триггер 1-4 составляют i-и разряд. Элементы 7-6 И-НЕ, 5-6 ИЛИ, 6-5, 2-6 И н счетный триггер 1-6 составляют i + i-И разряд. Элементы 7-3 И-НЕ, 5-3 ИЛИ, 6-2, 2-3 И и счетный триггер 1-3 составляют разряд с номером между i-r-тым и i-тым. Элементы 7-5 И-НЕ, 5-5 ИЛИ 6-Л, 2-5 И и счетный триггер 1-5 составляют разряд с номером между i-M и i+r-M. На чертеже для каждого 1-го разрада элемента, например 7-4 И-НЕ соединены с прямыми выходами сметных триггеров с по 1-6 соответственно старших разрядов с i+1 по i+г-й. Инверсные выходы счетных триггеров 1-2 - 1-6 соединены соответственно с первыми входами элементов 6-1 - , выхо,ды которых соединены соответственно с первыми входами элементов 5-2 - 5-6 ИЛИ, выходы элементов 5-1 5-6 ИЛИ соединены соответственно с тактовыми входами счетных триггеров 1-1 - 1-6, прямые выходы которых сое динены соответственно с первыми входами элементов 2-1 - 2-6 И и с входами дешифратора 4полных состояний выходы которых соединены с входами многовходового элемента,-3 ИЛИ, прямые выходы счетных триггеров 1-2 1-5 соединены соответственно с вторы ми входами элементов 2-3 - 2-6 И, выходы элементов 7-1 - 7-6 И-НЕ (Соединены соответственно с первым входом, элемента 5-1 ИЛИ и вторыми входами элементов 6-1. - 6-5 И, треть входы которых соединены соответственно с выходами элементов 2-1 - . 2-5 И, выходы элементов 2-2 - 5-6 И соединены соответственно с вторыми .входами элементов 5-2 - 5-6 ИЛИ, третьи входы элементов 5-2 - 5-5 ИЛИ соединены соответственно с выходами элементов 2-3 - 2-6 И, третьи входы; элементов 2-6 - 2-4 И соединены соот ветственно с выходами элементов 2-3 2-1 И, третий вход элемента 2-3 - 2-ь1 разряда и вторые входы элементов 2-f 2-1 И соединены соответственно с вхо ной шиной 8, с выходом элемента 2-1 И и с входной шиной 8, которая соединена с вторым входомэлемента :5-1 ИЛИ. . Принцип помехоустойчивой работы счетчика при изменении характеристических параметров г основан на формировании в процессе счета строго определённых комбинаций, которые являются разрешенными для конкретно заданного значения параметра г и опредеЬяеМыё следующим рекурентным соотношением: , В.. в.ч- ...+б..2+в..р i +P-f-i I r,-f РЧ- 2, ; .., г i, 3 , .. .; ..,...,... „, , В. .v- Ор 1; 2;в5 + 3, P+i, .. -, Р+г Здесь г - максимальное количестBQ единиц, находящихся в соседних двоичных разрядах числа и.образующих разрешенную группу единиц, а параметр Р указывает на минимальное количество нулей между разрешенными группами единиц. При г п и система (г, Р) является классической двоичной, так , как при общем числе двоичных разрядов, равном г., содержит только одну группу разрешенных единиц, весовые коэффициенты которых равны степени двойки. ПРИ и , 2, ... получаем известные Фибоначчиевые системы счисления. Случай и Р-1,2, ... соответствует системам счисления (г, Р), занимакнцих промежуточное положение между классической и Фибоначчиевой системами счисления и предназначенные для построения помехоустойчивых устройств и сквозного контроля информационно-вычислительных систем. Пусть ., тогдд при из соотношения (1) получаем соответствующие значения ВЕСОВЫХ коэффициентов (В) и разрешенные комбинации в интервале натуральных чисел (приведенных в качестве примера) от О до 24 (таблица) ... 6 5 4 3 2 1 О ...24 13 74211 00 О 10 i 100 2 110 3 1000 4 101 О 5 1 1 О о . Как видно из таблицы, в приведе ном интервале чисел двоичные ком нации ,.1110 7, ... 11100 13, .. 101110 20 и т.д. являются запрещ ными (избыточными) Для данной си темы счисления. . Очевидно/ что при максимал ная разрешенная комбинация ...011101110..., при и . 0111001110..., при г р,и Р 0111...111 цифр Для упрощения задачи конструи вания счетчика для любой систе:мы счисления при конкретном задании характеристического параметра вос пользуемся выходными булевыми, фу циями логических- элементов, f. F - i - порядковый номер разряда счетчика; k обозначает первую циф элемента на схеме, для-которого о деляется выходная функция. Выходные функции для каждого 1-го разряда определяются следующ рекурентными соотношениями ; т.,,лт.л...лт.,

(2;

ff-fS(ffvff v...vfn(-);

f2 (T. .AT-Cv -lOAff-C -)

ПДцставляя конкретные значения харак- з теристического параметра в выражени,и ( 2), получаем соответствующую конфигурацию счетчика.. Определим в качестве примера входные функции соответствующих элементов четвертого

60 разряда при ,

(т.е. входы элемента И-НЕ четвертого разряда необходимо соединить с единичными выходами 5

ЗдесБ и далее для описания состояний элементов счетчика при поступлении текущего сигнала +1Сч, по шине 8, примем следующую запись:

1-й +1Сч: ff(5-l)l, Т(1-1)1;

2-й +1Сч: f(5-l)l, Т(1-1)0; f2(2-l) f|(6-2) f|(, Т(1-2)1 2

3-й +1Сч: ff(5-l)l, Т(1-1)1; 4-й +1Сч ff(5-l)l, Т(1-1)0;

ff(2-l)f|(.2-2) f|(5-2)l, , Т(1-2)0; ,. : f (6-2) f з(5-3)1,Т(1-3)1; 5-й +1Сч: то же, что 1-й +1Сч триггеров пятого и шестого разрядов) - Т Т э f (. входы первого элемента И четвертого разряда необходимо соединить с единичными выходами данного и младдаего разрядов и с выходом перв.ого элемента И перво .го разряда) . f f f - (т.е. 4 Ч Э входы второ-. го элемента И четвертого разряда необходимо соединить с выходами элемента И-НЕ ИНулевым выходом триггера данного разряда и первого элемента И третьего, разряда). На структурной схеме дана полная конфигурая первых шести разрядов предлагаемого счетчика с указанием мест рекурентности связей для люби-, го значения параметра. Для описания работы счетчика воспользуемся соответствующими выходными булевыми функциями и таблицей (так как значение нулевого разряда при всех разрешенных комбинациях равно нулю, то при построении счетчика он во внимание не принимается). Предположим, что в исходном состоянии на единичных выходах триггеров будут нулевые значения сигналов (т(1-1)- Т(1-6)0, выходные функции элементов И-НЕ будут иметь значение логической единицы f(7-l) + )l, выходные функции первых элементов И будут иметь значение логического нуля f (2-1)+ f2(2-6)0. При подаче на вход элемента 5-1 сигнала +1Сч на шине .8 выходная функция f примет значение .единицы, так как ff +lC4A-,|i|j- y- Л тТТ-зТ Единичным значением этой функции в счетчик будет занесен код логической единицы. Выходн-ая функция элемента 2-1 И останется нулевой, так как в предыдущий момент времени триггер 1-1 находился в нулевом состояf2НИИ, т.е. тТ1-17л+1Сч б-й +1СчГ то же, что 2-й +1Сч 7-й +lC4i fj(7-l))0: ,f|(2-3)f f(5-3)ff(5-2) - ТГ1-2)0; f|(6-3)f4(5-4)1,T(l-4) 8-й +1Сч: то же, что 1-й +1Сч 4 12-й +1Сч: то же, что и 1-ый +1Сч, сохранив при этом предыд шее состояние счетчика ...1100, fl(7-2)0,f7 f .(7-1)1 2 13-й +1Сч: f|.(5-l)l.. Т(1-1)0; f(2-l)f2(2-4)f(5-4) f|(5-3)lf . T{l-3)T(i-4)0; f|{6-4)f|{5-5)l,T(l-5) 14-й +1Сч: то же, что и 1-й +1Сч 23-й +1Сч: то же, что и 1-й +1Сч, сохранив при этом предаад щее состояние счетчика ...11010, f(7-3)0, (7-2)l ff(5-l)l, Т (1-1)0 24-й +1Сч: f(2-l) f|(2-2) f(5-2 1, Т (1-2) fii2-2)f|(2-5)f5(5-5) f(5-4)l, . - Т(1-5)Т(1-4)0, f|(6-5)f|(5-6)i, Tvl-6)l и т.д. Если в результате неисправной работы оборудования на выходе счетчика появится одна из запрещенных комбинаций (для нашего примера ..., 1110, 0111.,.1111,. ...), то на всех выходах дешифратора 7 полных состояний будут нулевые сигналы и-на выходе элемента 3 ИЖ будет зафиксирован сигнал ошибки. Аналогично производится построение и -рассматривается работа rt разрядного помехоустойчивого счетчика с последовательным переносом при rao66iA значении характеристического параметра п7о4. Таким рбразом, использование нового элемента и связей, рассчитываемых с помощью рекурентных соотношений (2), для конкретно заданного параметра пбзволя ет расширить функциональные возможности устройства по сравнению с прототипом, при этом выбор характеристических параметров позволяет разработчику изменять технические характеристики счетчика, что является качественно новым показателем при разработке подобных цифровых устройств и тем самым увеличивает эффективность использования цифровых устройств при помехоустойчивой обработке информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня | 1977 |

|

SU714394A1 |

| Цифровой нелинейный масштабирующий преобразователь | 1981 |

|

SU1057953A1 |

| М-тактный счетчик | 1979 |

|

SU966916A1 |

| Устройство для деления чисел в системе остаточных классов | 1985 |

|

SU1287152A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОГО ОПРЕДЕЛЕНИЯ ИНТЕГРАЛЬНЫХ ОЦЕНОК ГРАФИКОВ | 1972 |

|

SU332464A1 |

| Двоичный счетчик с контролем ошибок | 1981 |

|

SU970704A1 |

| Устройство для задержки импульсов | 1979 |

|

SU822331A1 |

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| Аналого-цифровой преобразователь в кодах с естественной избыточностью | 1986 |

|

SU1381698A1 |

| Устройство для преобразованиячАСТОТы B КОд | 1979 |

|

SU794727A1 |

ДВОИЧНЫЙ СЧЕТЧИК С ПОСЛЕДОВАТЕЛЬНЫМ ПЕРЕНОСОМ, преимущественно для работы в (г , 1 ) системе счисления, содержащий входную шинуу дешифратор полных состояний, многовходовый элемент ИЛИ, а в каждом i-M разряде, кроме первого, счетный триггер, два элемента И-, элемент ИЛИ, прямой выход счетного триггера соединен с одним из входов дешифратора полных состояний и с первым входом первого элемента И, выход которого соединен с первым входом элемента HJte, второй вход и выход которого соединены соответственно с выходом второго элемента И и с тактовым входом счет ного триггера, инверсный выход которого соединен с первым входом второго элемента И, второй вход которого соединен с выходом первого элемента И j предыдущего разряда, второй вход первого элемента И соединен с выходом первого элемента И соответствующего младаего разряда, выходы дешифратора полных состояний соединены с входами-многовходового элемента ИЛИ, первый разряд содержит счетный триггер, элемент И и элемент ИЛИ, выход которого соединен с тактовым входом счетного триггера, прямой выход которого соединен с первым входом элемента И, о т л и ч а ю щ и и с я тем, что, с целью расширения функциональных возможностей, в каждый i-й разряд введен элемент И-НЕ, г входов .которого соединены с прямыми выходами счетных триггеров последующих. if разрядов, а выход элемента И-НЕ соединен с третьим входом второго эле-, мента И, с третьего по (г+1)-1 входал элемента ИЛИ соединены соответст.венно с выходами первых элементов И с i-fl по i+(r-1) paзpядoв с третье-2 го по (г+1)-й входыпервого элемента И соединены соответственно с прямыми, выходами .счетных триггеров с 1-1 по i-(г-1 ) разрядов в первом СдЭ 4iii разряде, выход элемента И-НЕ спеди- . нен с первым входом элемента ИЛИ, i второй вход которого соединен с BXOR ной шиной, с вторым входом элеменCD |та Икс одним из входов первого Ч элемента И.соответствующего старшего разряда.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Букреев И.Н | |||

| и др | |||

| Микро- ; электронные схемы цифровых устройств, М | |||

| , Сов | |||

| радио, 1973, с | |||

| Рогульчатое веретено | 1922 |

|

SU142A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Двоичный счетчик с последовательным переносом | 1976 |

|

SU577682A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-08-07—Публикация

1982-03-22—Подача