единены с входами первого эпемента ИЛИ выход которого соединен с первыми входами первого и второго элементов И, вторые входы которых являются первым и вторым входами формирователя импульсов, выходы первого и второго элементов И соединены с первыми входами пep вогои второго триггеров, вторые входы которых соединены с выходами первого и второго элементов задержки, выходы триггеров соединены с первыми входами третьего и четвертого элементов И, вторые входь которых являются третьим входом формирователя импульсов, третьи входы третьего и четвертого элементов И являются соответственно первым и

. вторым входами формирователя импульсов выходы третьего и четвертого элементов И соед 1нены с входами элементов задержки и входами второго элемента ИЛИ, выход которого является вторым выходом формирователя импудьсов, и второй входы элемента-1И-ИЛИ соедишны с исходами триггеров, третий вход эпемента И-ИЛИ является четвертым входом формирователя импульсов.

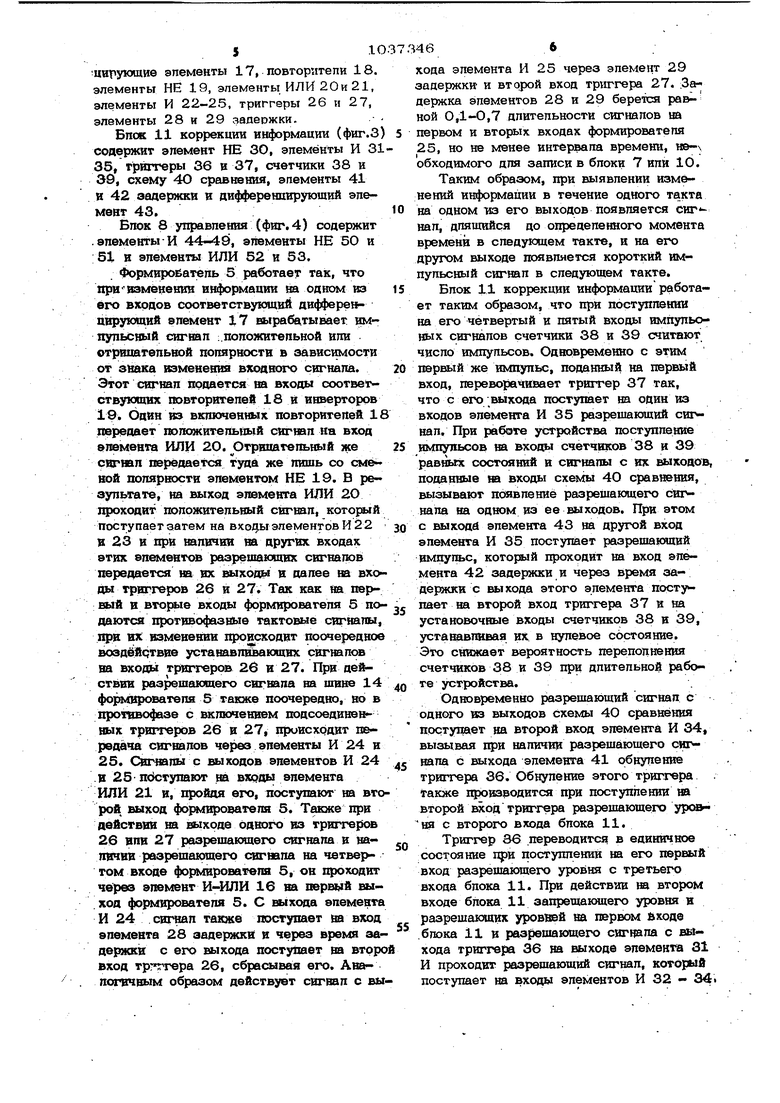

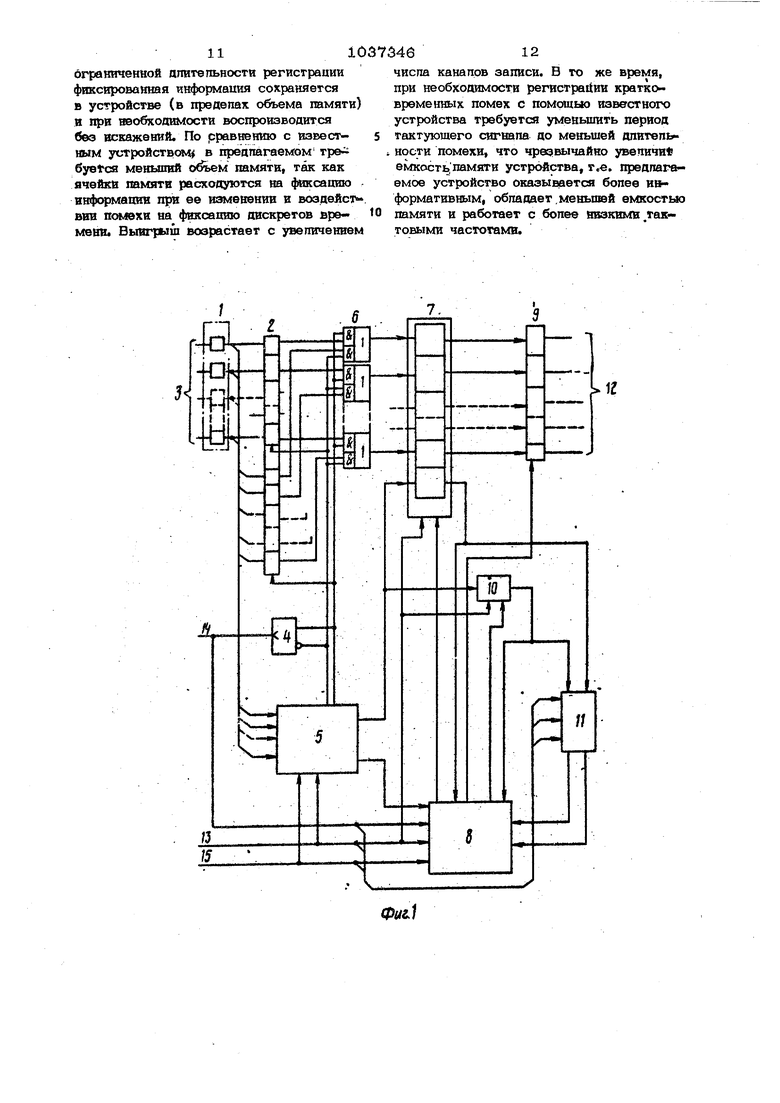

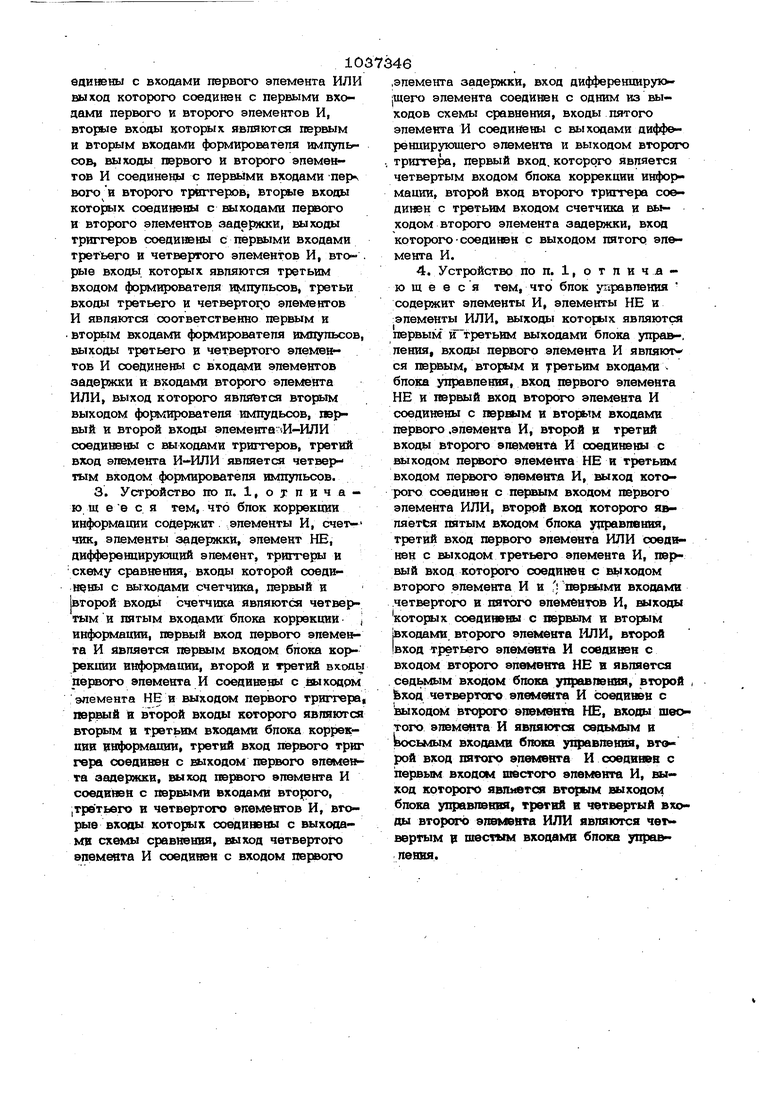

3. Устройство поп. l,ojnH4a - ю щ е е с я тем, что блок коррекции информации содержит. элементы И, счетчик, элементы задержки, элемент НЕ, дифференцирующий элемент, триггеры и

схему сравнения, входы которой соединены с выходами счетчик а, первый и 1второй входы счетчвда являются четвертым и пятым входами блока коррекции информации, первый вход первого элемента И {Является первым входом блока коррекции информации, второй и третий входы первого элемента И соединены с выходом эпемента НЕ и выходом первого триггера первый и второй входы которого являются вторым в третьим входами блока коррекции информации, третий вход первого триг гера соединен с выходом первого впемес та задержки, лход пецпаого элемента И соединен с первыми входами второго, ,третьего и четвертого эпемевтов И, вторые вхооы которых соединены с выходами схемы сравнения, выход четвертого впемента И соединен с входом первого

.элемента задержки, вход дифферешшруюртего элемента соединен с одним вз вьтходов схемы сравнения, входы пятого элемента И соединены с выходами дифференцирующего элемента и выходом второго триггера, цервый вход, которого является четвертым входом блсжа коррекции информации, второй вход второго триггера соединен с третьим входом счетчика и выходом второго элемента задержки, вход которого-соединен с выходом пятого элемента И.

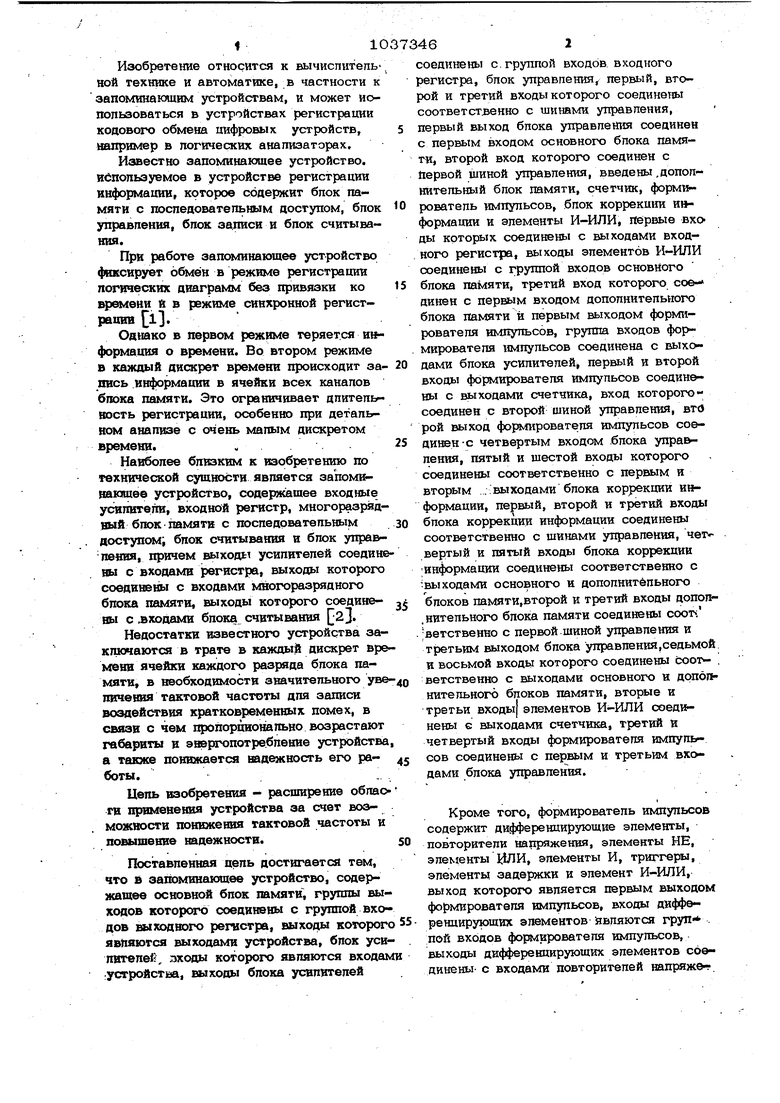

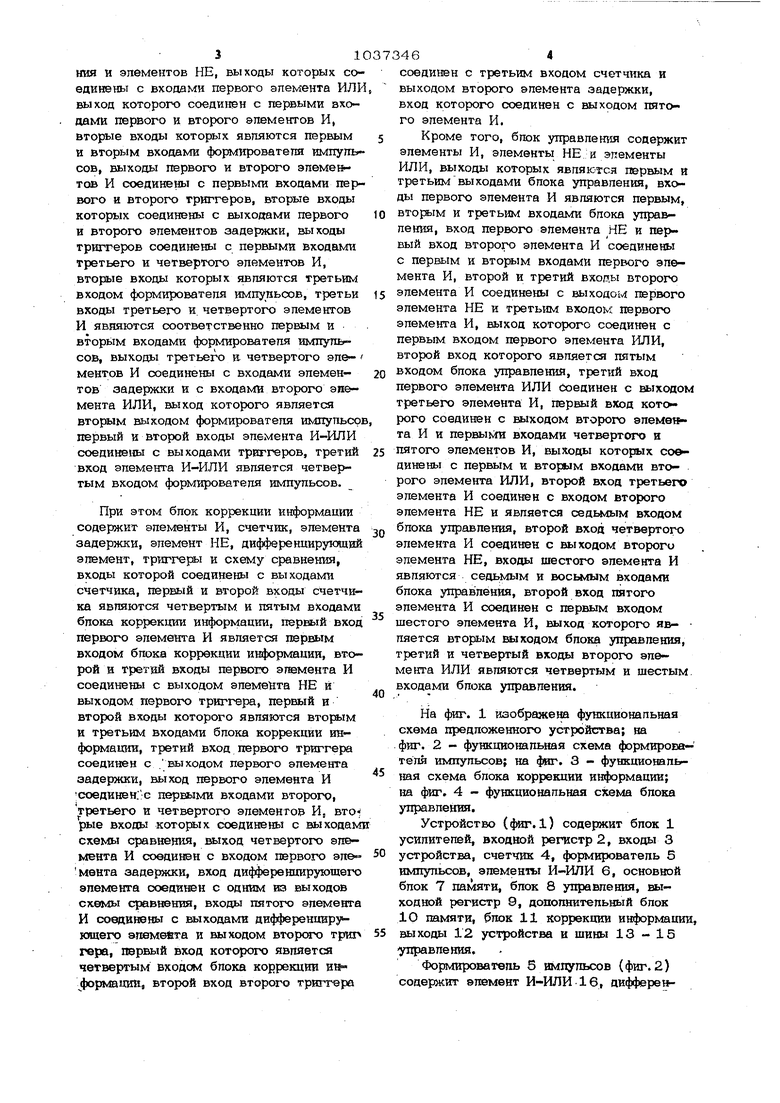

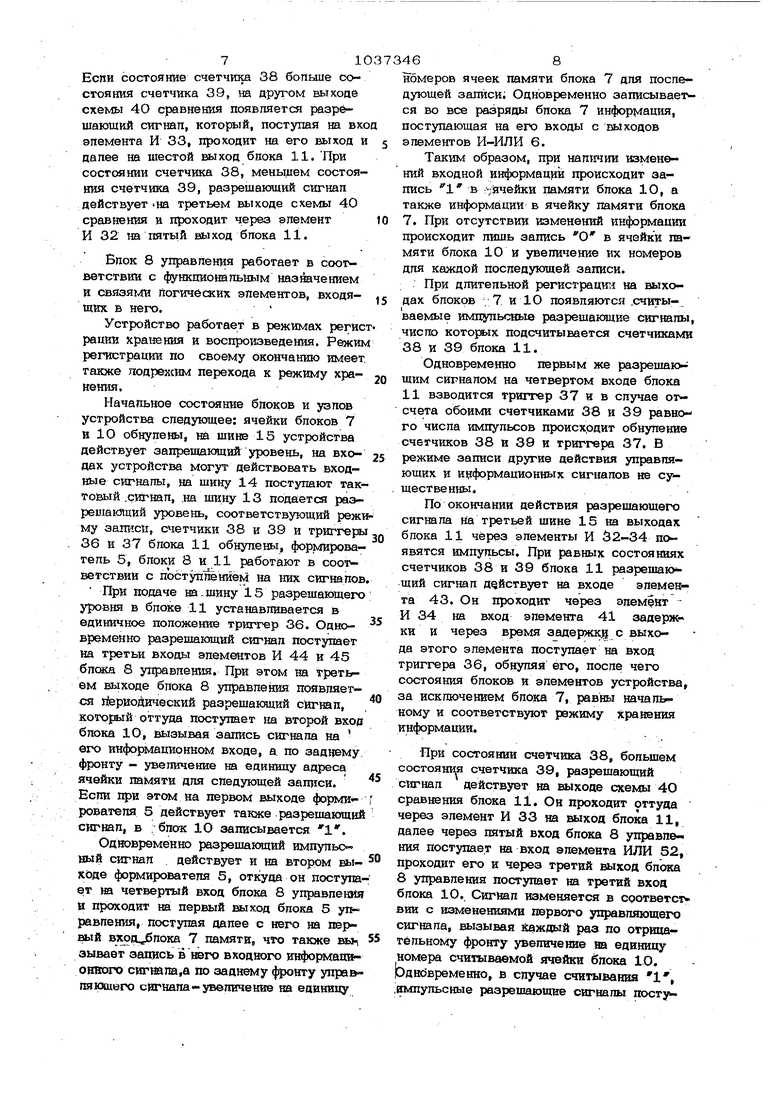

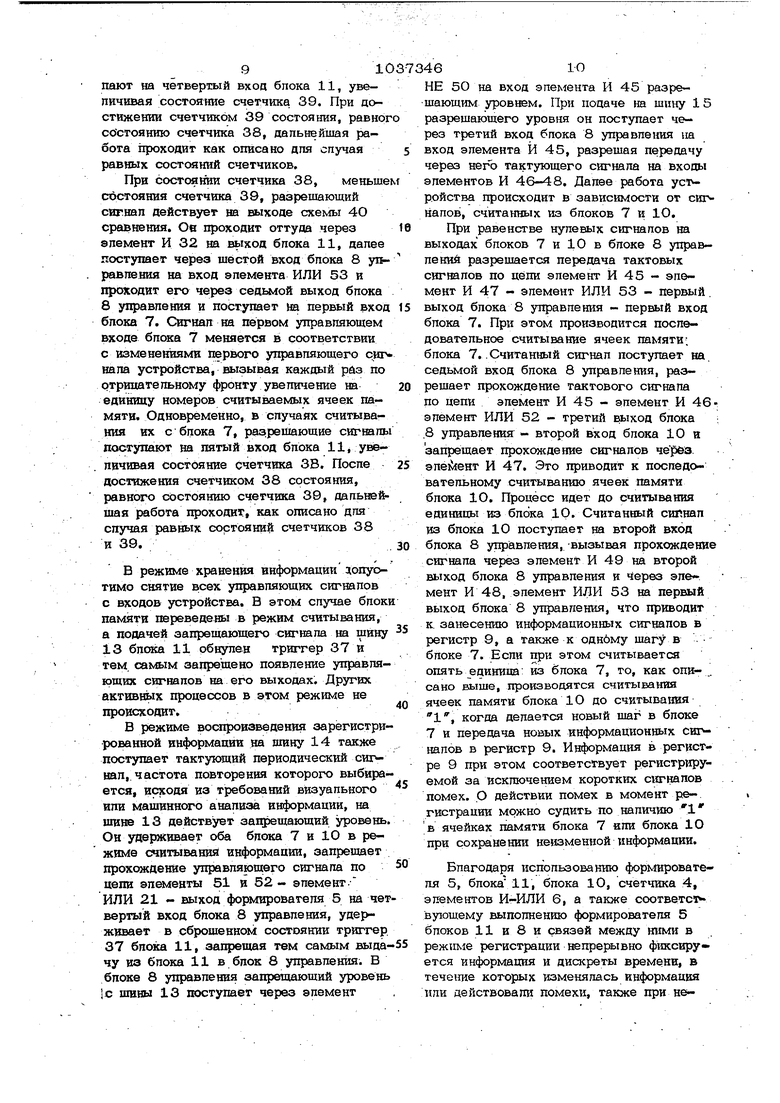

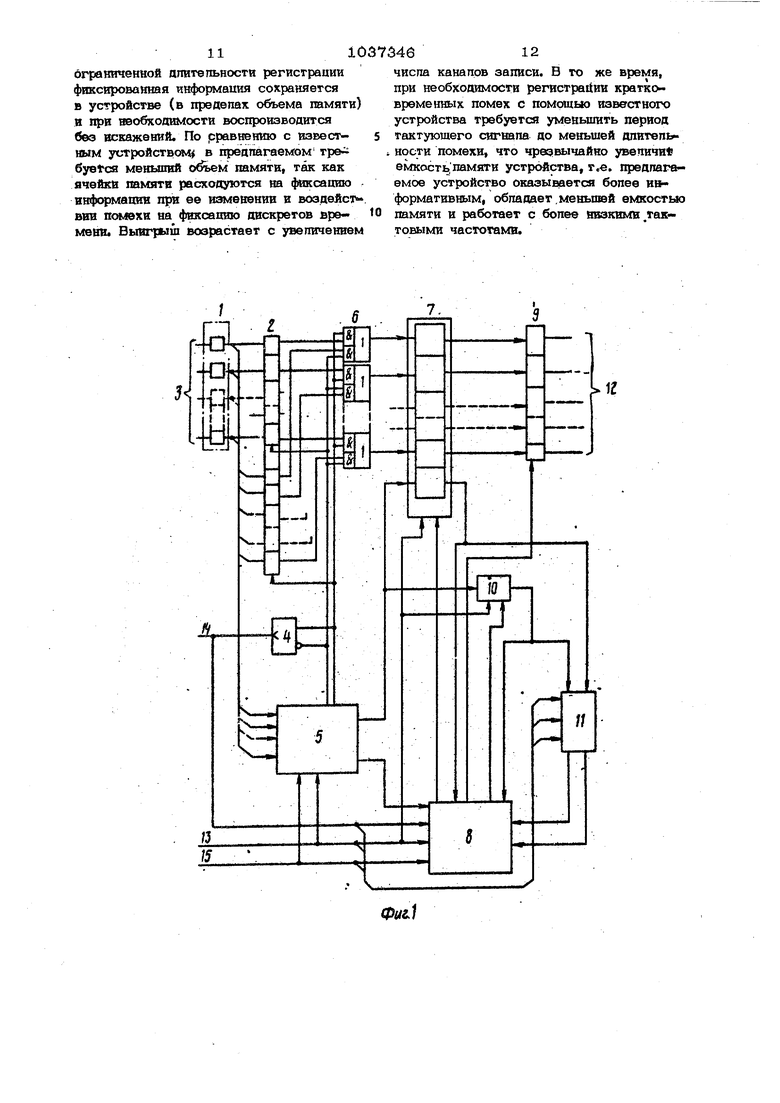

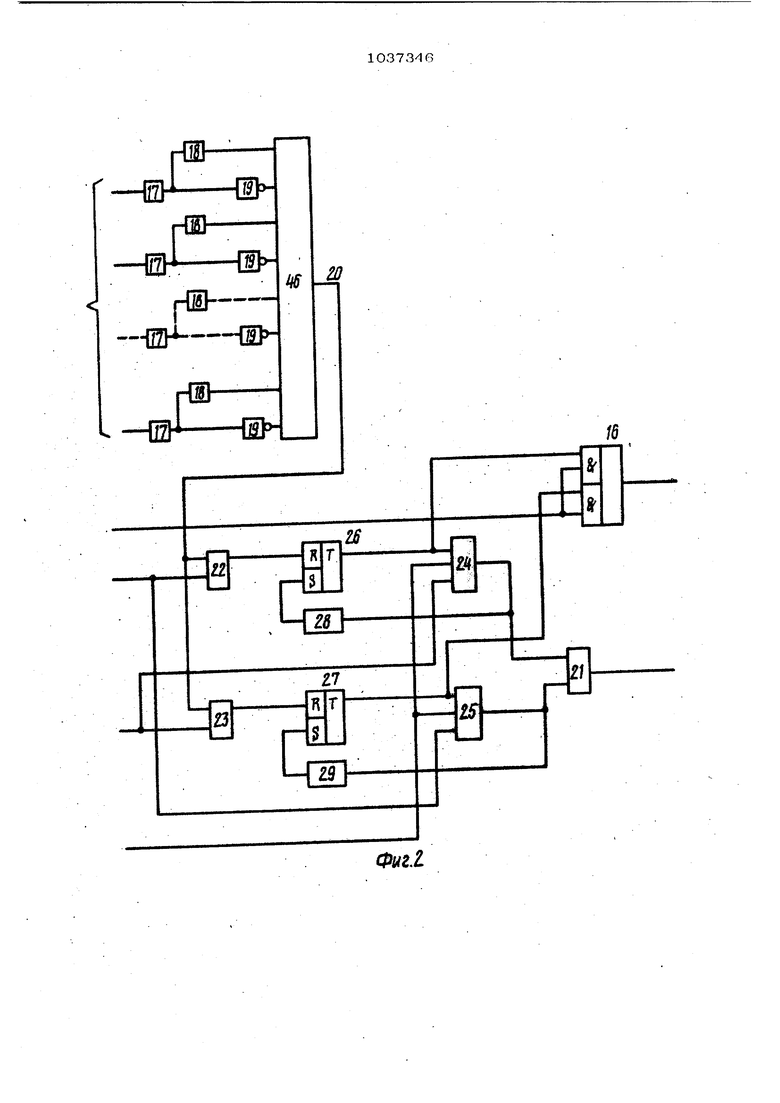

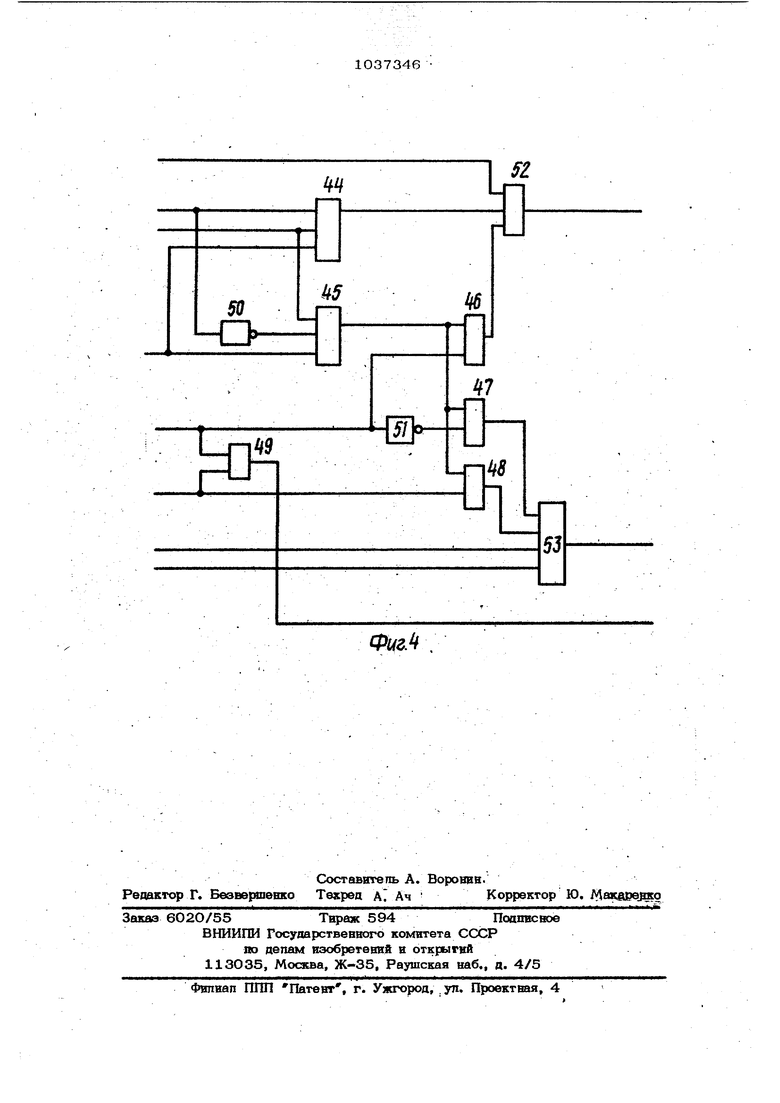

4. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что блок утфавпения содержит элементы И, элементы НЕ и элементы ИЛИ, выходы которых являются первым й гретьим выходами блока . ления, входы первого элемента И являют ся первым, вторым и третьим входами блока управления, вход первого элемента НЕ и первый вход второго элемента И соединены с первым и вторым входами первого.элемента И, второй и третий входы второго элемента И соединены с вь1 ходом первого элемента НЕ и третьим входом первого эпемента И, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого является пятым входом блока управления, третий вход первого эпемента ИЛИ соединен с выходом третьего элемента И, первый вход которого схюдинен с выходом второго элемента И и ; перолми входами .четвертого и пятого элементов И, выходы которых соединены с первым и вторым |входами. второго элемента ИЛИ, второй вход третьего элемента И соединен с входом второго НЕ в является седьмым входом блока улрешпевня, второй , fexofl четвертого эпемвита И соединен с выходом второго эдамевта НЕ, входы шесу того элемента И являются седьмым и восьмым входами блока управления, второй вход пятого эпемевта И соедвнев с первым входом шестого алемевта И, выход которого явпиется вторим выходом блока управлеввя, третвй в четвертый входы второго элемевта ИЛИ являются чет вертым в шестым входами блока управлеввя. 110 Изобретение относится к вычиспитепь ной технике и автоматике, в частности к запоминающим устройствам, и может иопопьзоваться в устройствах регистрации кодового обмена цифровых устройств, например в логических анализаторах. Известно запоминающее устройство, нбпопьзуемое в устройстве регистрации информации, которое содержит блок памяти с последовательным доступом, блок управления, блок записи и блок считывания. При работе запоминающее устройство фиксирует обмен в режиме регистрации погнческих диаграмм без привязки ко Ц)емени и в режиме синхронной регистрации . Однако в первом режиме теряется информация о времени. Во втором режиме в каждый дискрет времени происходит запись информации в ячейки всех каналов блока памяти. Это ограничивает длительгкость регистрации, особенно при детальном анализе с очень малым дискретом времени... Наиболее близким к изобретению по технической сущности является запоминающее устройство, содерхшщее входные усилители, входной регистр, многоразрядный блок памяти с последовательным доступом; блок считывания и блок управпвуия, причем выходы усилителей соедине ны с входами регистра, выходы которого соединены с входами многоразрядного блока памяти, выходы которого соединены с .входами блока считывания j23. Недостатки известнохю устройства заключаются в трате в каждый дискрет вре мени ячейки каждого разряда блока памяти, в необходимости значительного уве ranewa тактовой частоты для записи воздействия кратковременных помех, в связи с чем пропорционально возрастают габариты и энергопотребление устройства а также понижается надежность его работы. Цепь изобретения - расширение облаоги применения устройства за счет возможности понижения тактовой частоты и повышение надежности. ГЬставленная цель достигается тем, что в запоминающее устройство, содержащее основной блок памяти , группы выходов которого соединены с группой входов выходного регистра, выходы которого явпяются выходами устройства, блок усилвтелей, зходы которого являются входам устройстка, выходы блока усилителей 462 соединены с.группой входов, входного регистра, блок управпения первый, второй и третий входы которого соединены соответственно с шинами управ пения, первый выход блока управления соединен с первым входом основного блока памяти, второй вход которого соединен с Первой шиной управления, введены .дополнительный блок памяти, счетчик, форм№рователь импульсов, блок коррекции и формации и элементы И-ИЛИ, входы которых соединены с выходами входного регистра, выходы элементов И-ИЛИ соединены с группой входов основного блока памяти, третий вход которого соединен с первым входом дoпoлнитeль югo блока памяти и первым выходом формирователя импульсов, группа входов формирователя импульсов соединена с выходами блока усилителей, первый и второй входы формирователя импульсов соединены с выходами счетчика, вход которогосоединен с второй шиной управления, вто рой выход фо1жп1рователя импульсов соединен-с четвертым входом .блока управления, пятый и шестой входы которого соединены соответственно с первым и вторым ...выходами блока коррекции информации, первый, второй и третий входы блока коррекции информации соединены соответственно с шинами управления, чет вертый и пятый входы блока коррекции Информации соединены соответственно с выходами основного и дополнительного блоков памяти,второй и третий входы допол.нительного блока памяти соединены соот-; ветственно с первой шиной управления и третьим выходом блока управления .седьмой и восьмой входы которого соединены соот- . ветственно с выходами основного и дополнительного блоков памяти, вторые и элементов И-ИЛИ соедитретьи входы нены е выходами счетчика, третий и четвертый входы формирователя импул сов соединены с первым и третьим входами блока управления. Кроме того, формирователь импульсов содержит дифференцирующие элементы, повторители напряжения, элементы ME, элементы ИЛИ, элементы И, триггеры, элементы задержки и элемент И-ИЛИ, выход которого является первым выходом формирователя импульсов, входы дифференцирующих элементов йвляются груп пой входов формирователя импульсов, выходы дифференцирующих элементов соединены-с входами повторителей напряже-ния и элементов НЕ, выходы которых соединены с входами первого апемента ИЛИ выход которого соединен с первыми входами первого и второго элементов И, вторые входы которых являются первым и вторым входами формкроватепя импупь сов, выходы первого и второго элементов И соединены с первыми входами первого и второго триггеров, вторые входы которых соединены с выходами первого и второго элементов задержки, выходы триггеров соединены с первыми входами третьего и четвертого элементов И, вторые входы которых являются третьим входом формирователя импупьсов, третьи входы третьего и. четвертого элементов И явяяются соответственно первым и вторым входами формирователя импульсов, выходы третьего и четвертого элементов И соединены с входами элементов задержки и с входами второго эиемента ИЛИ, выход которого является вторым выходом формирователя импульсо 1юрвый и второй входы элемента И-ИЛИ соединены с выходами триггеров, третий вход элемента И-ИЛИ является четвертым входом формирователя импульсов. При этом блок коррекции информации содержит элементы И, счетчик, элемента задержки, элемент НЕ, дифференцирующий элемент, триггеры и схему сравнения, входы которой соединены с выходами счетчика, первый и второй входы счетчика являются четвертым и пятым входами блока коррекции информации, первый вход первого элемента И является первым входом блока коррекции информации, второй и третий входы первого элемента И соединены с выходом элемента НЕ и выходом первого триггера, первый и второй входы которого являются вторым И третьим входами блока коррекции информации, третий вход первого триггера соединен с .выходом первого элемента задержки, выход первого элемента И соединен;с первыми входами второгч), третьего и четвертого элементов И, вто рые входы которых соединены с выходам схемы сравнения, выход четвертого элемента И соедииэн с входом первого эле мента задержки, вход дифференцирующего элемента соединен с одним вэ выходов сравнения, входы пятого элемента И соединены с выходами дифференцирующего эпемейта и выходом вторсях) три1 гера, первый вход которого является четвертым входом блока коррекции информации, второй вход второго триггера соединен с третьим входом счетчика и выходом второго элемента задержки, вход которого соединен с выходом пятого элемента И. Кроме того, блок управления содержит элементы И, элементы НЕ и элементы ИЛИ, выходы которых являются первым и третьимвыходами блока управления, входы первого элемента И являются первым, вторым и третьим входами блока управления, вход первого элемента НЕ и первый вход второго элемента И соединены с первым и BTop.iM входами первого элемента И, второй и третий входы второго элемента И соединены с выходом первого элемента НЕ и третьим входом первого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого является пятым входом блока управления, третий вход первого элемента ИЛИ Соединен с выходом третьего элемента И, первый вход которого соединен с выходом второго элемента И и первыми входами четвертого н пятого элементов И, выходы которых соединены с первым и вторым входами второго элемента ИЛИ, второй вход третьего элемента И соединен с входом второго элемента НЕ и является седьмым входом блока управления, второй вход четвертого элемента И соединен с выходом второго элемента НЕ, входы шестого элемента И являются и восьмым входами блока управления, второй вход пятого элемента И соединен с первым входом шестого элемента И, выход которого является вторым выходом блока управления, третий и четвертый входы второго элемента ИЛИ являются четвертым и шестым, входами блока управления. На фиг. 1 изображена функциональная схема предложенногхэ устройства; на фиг- 2 - функциональная схема формирователя импульсов; на фиг. 3 - функциональная схема блока коррекции информации; на фиг. 4 - функциональная схема блока управления. Устройство (фиг. 1) содержит блок 1 усилителей, входной регистр 2, входы 3 устройства, счетчик 4, формирователь 5 импульсов, элементы И-ИЛИ 6, основной блок 7 памяти, блок 8 управления, выходной регистр 9, дополнительный блок 10 памяти, блок 11 коррекции информации, выходы 12 устройства и шины 13-15 управления. Формирователь 5 импупьсов (фиг. 2) содержит элемент И-ИЛИ 16, диффере 510цигуюшие эпементьт 17, повгорнтепи 18. элеменгы НЕ 19, элементы ИЛИ 20и 21, элементы И 22-25, триггеры 26 и 27, элементы 28 и 29 запеожки. Бпок 11 коррекции информации (фиг.З содержит эпемент НЕ ЗО, элементы И 31 35, грйггеры 36 и 37, счетчики 38 и 39, схему 4О сравнения, элементы 41 и 42 задержки и дифференцирующий эпемент 43, Бпок 8 управления (фиг. 4) содержит . элементы-И 44-49, элементы НЕ 50 и 51 в элементы ИЛИ 52 и 53. . Формиробатель 5 работает так, что прнизменении информации на одном из его входов соответствующий днффере пврующий элемент 17 вырабатывает; импульсный сигнал :.положительной или отршштельной полярности в завис11мости от знака изменения входнотч) сигнала. Этот сигнал подается ш входы соответствующих повторитепей 18 Н инверторов 19. Один из включенных повторителей 18 Передает положительный сигнал на вход элемента ИЛИ 2О. ргрш1атепьнь1й же сигнал передается же лишь со сменой полярности элементом НЕ 19. В результате, на выход элемента ИЛИ 2О проходит положительный сигнал, который поступает затем на вхоцы элементов И 22 В 23 и при наличии на других входах этих элементов разрешающих сигналов передается на их вакоаа н далее ш входы триггеров 26 и 27. Так как На перилй и вторые входы формирователя 5 подаются противофазнью тактовые сигналы, ярк ия: изменении щюисходит поочередное воздёйдтвие устанавливающих сигналсж на Bxoobi триггеров 26 и 27. При действии разрешеисядего сигнала на шине 14 формирователя 5 также поочередно, но в протввофазе с включением подсоединен ных триггеров 26 и 27, происходит передача сигналов через элементы И 24 ти 25. Сигналы с выходов элементов И 24 .В 25-пс гтупают на входы элемента ИЛИ 21 и, пройдя его, поступают на вто рой, выход фо1жщроватепя 5. Также при действии на выходе одного из триггеров 26 нли 27 разрешающего сигнала и налвчви разрешающего сигнала на четвертом входе формирователя 5, он проходит эпемент И-ИЛИ 16 на первый выход формирователя 5. С выхода элемента И 24 сигнал также поступает на вход элемента 28 задержке и через время задержки с его выхода поступает на второ вход трг-гтера 26, сбрасывая его. Аналогичным образом действует сигнал с вы 466 хода эпемента И 25 через эпемент 29 задержки и второй вход триггера 27. Задержка эпементов 28 и 29 берется равной О,1-0,7 длительности сигнапов на первом и вторых входах формирователя 25, но не менее интервала времени, нв- обходимого дпя записи в бпоки 7 или 10. Таким образом, при выявлении изменений информации в течение одного такта на одном из его выходов появляется сиг-нал, длящийся до определенного момента времени в следующем такте, и на его другом выходе появляется короткий импульсный сигнал в следующем такте. Бпок 11 коррекции информации работает таким образом, что при поступленнн на его четвертый и пятый входы импульоных сигналов счетчики 38 и 39 считают число импульсов. Одновременно с этим первый же импульс, поданный на первый вход, переворачивает триггер 37 так, что с его выхода поступает на один из входов элемента И 35 разрешающий . При работе устройства поступление импульсов на входы счетчи1к в 38 и 39 paBfibtx состояний и сигналы с их выходов, поданные на входы схемы 40 сравнения, вызывают появление разрешающего сигнала на одном из ее выходов. При атом с шлходд элемента 43 на другой вход элемента И 35 поступает разрешакяций импульс, который проходит на вход элемента 42 задержки и через время задержки с выхода этого элемента посту пает на второй вход триггера 37 и на установочные входы счетчиков 38 и 39, устанавгшвая их в нулевое состояние. Это снижает вероятность перепотхнения счетчиков 38 и 39 при дпитепьной работе устройства. Одновременно разрешающий сигнал с одного вз выходов Схемы 4О сравнения поступает на второй вход элемента И 34, вызывая при наличии разрешающего сигнала с выхода элемента 41 обнуление триггера 36. Обнуление этого триггера Также производится при поступлении на второй юсод триггера разрешающего урсшня с второго входа блока 11. Триггер 36 переводится в единичное состояние при поступлении на его первый вход разрешающего уровня с третьего входа блока 11. При действии на втором входе блока 11 запрещающего уровня и разрешающих уровней на первом входе бпока 11 и разрешающего сигнала с выхода триггера 36 на выходе элемента 31 И проходит разрешающий сигнал, который поступает на входал элементов И 32 - 34« Еспи состояние счетчика 38 бопыие состояния счетчика 39, на другом выходе схемы 4О сравнения появляется разрешающий сигнап, который, поступая на вхо элемента И 33, проходит на его выход и дапее на шестой выход б дока 11. При состоянии счетчика 38, меньшем состояния счетчика 39, разрешающий сигнап действует «на третьем выходе схемы 40 сравнения в проходит через элемент И 32 на пятый выход блока 11. Бпок 8 управления работает в соответствии с (функциональным назначением и связя1,ш Логических элементов, входящюс в него. Устройство работает в режимах регист рации хранения и воспроизведения. Режим регистрации по своему окончанию имеет. также лодрехсим перехода к режиму хранения. Начальное состояние блоков и узлов устройства следующее: ячейки блоков 7 И 10 обнулены, на шине IS устройства действует запрещающий уровень, на входах устройства могут действовать входные сигналы, на шину 14 поступают тактовый .сигнал, .на шину 13 подается разрешакпций уровень, соответств5гющий режи му записи, счетчики 38 и 39 и триггеры 36 и 37 блока 11 обнулены, формирователь 5, блоки 8 и 11 работают в соответствии с поступлением на них сигналов При подаче на.шину 15 разрешающего уровня в блоке 11 устанавливается в единичное положение триггер 36. Одш временно разрешающий сигнал поступает на третьи входы элементов И 44 и 45 блока 8 управления. При этом на третьем выходе блока 8 управления появляется йериодический разрешающий сигнап, который оттуда поступает на второй вход блока 10, вызывая запись сигнала на его информационном входе, а по заднему, фронту - увеличение на единицу адреса ячейки памяти для следующей зашгси. Если при этом на первом выходе форми роватепя 5 действует также разрешающий сигнал, в : блок 10 записывается I. Одновременно разрешающий импульсный сигнал действует и на втором выхьде формирователя 5, откуда он поступа ет ва четвертый вход блока 8 управления и проходит на первый выход блока 5 управления, поступая далее с него на первый вхра.я)блока 7 памятИв что также зывает запись в него входного информата онного сигшла,а по заднему фронту управ лянхцего сиг нала-увеличение на единицу номеров ячеек памяти блока 7 для последующей записи; Одновременно записывается во все разряды блока 7 информация, поступающая на его входы с выходов элементов И-ИЛИ 6. Таким образом, при наличии изменений входной информац 1И происходит запись 1 в :-;йчейки памяти блока 10, а также информации в ячейку памяти блока 7. При отсутствии изменений информации происходит лишь запись О в ячейки памяти блока 10 и увеличение их номеров для каждой последующей записи. . При длительной регистраци:л на выходах блоков .7 и 10 появляются .счИтываемые импульснью разрешающие сигналы, число которых подсчитывается счетчиками 38 и 39 блока 11. Одновременно первым же разрешаю-: щим сигналом на четвертом входе блока 11 взводится триггер 37 и в случае отсчета обоими счетчиками 38 и 39 равного числа импульсов происходит обнуление счетчиков 38 и 39 и триггера 37. В режиме записи другие действия управляющих и информационных сигналов не существенны. По окончании действия разрешающего сигнала На третьей шине 15 на выходах блока 11 через элементы И 32-34 появятся импульсы. При равных состояниях счетчиков 38 и 39 блока 11 разрешаю щий сигнал действует на входе элеме та 43. Он проходит через элем|нт И 34 на вход элемента 41 задержки и через время задеpKKg с выхода этого элемента поступает на вход триггера 36, обнуляя его, после чего состояния блоков и элементов устройства, за исключением блока 7, равны началь ному и соответствуют режиму хранения информации. При состоянии счетчика 38, большем состояния счетчика 39, разрешающий сигнал действует на выходе схемы 40 сравнения блока 11. Он проходит оттуда через элемент И 33 на выход блока 11, далее через пятый вход блока 8 управления поступае.т на вход элемента ИЛИ 52, проходит его и через третий выход блока 8 управления поступает на третий вход блока 10. Сигнал изменяется в соответствии с изменениями первого управляющего сигнала, вызывая каждый раз по отршштбльному фронту увеличение ш единицу номера считываемой ячейки блока 10. Рднбвременно, в случае считывания , .импульсные разрешающие сигналы посту пают на четвертый вход блока 11, увепичивая состояние счетчика 39. При цостижетга счетчиком 39 состояния, равно состоянию счетчика 38, дальнейшая работа проходит как описано дпя спучая равных состояний счетчиков. При состоянии счетчика 38, меньше состояния счетчика 39, разрешающий сигнал действует на выходе схемы 4О сравнения. Ое проходит оттуда через элемент И 32 на вь1ход блока 11, далее поступает через шестой вход блока 8 у№ давления на вход элемента ИЛИ 53 и проходит его через седьмой выход блока 8 управления и поступает на первый вход блока 7. Сигнал на первом управляющем входе блока 7 меняется в соответствии с изменентЕШМИ первого управляющего сиг нала устройства, вызывая каждый риз по отрицательному фронту увеличение на единицу номеров считываемых ячеек памяти. Одновременно, в случаях считывания их с блока 7, разрешающие сигналы поступают на пятый вход блока 11, увеличивая состояние счетчика ЗВ. После достижения счетчиком 38 состояния, равного состоянию счетчика 39, дальней шая работа проходит, как описано дпя спучая равных состояний счетчиков 38 и 39. В режиме хранения информации допустимо снятие Bicex управляющих сигналов с входов устройства. В этом случае блок памяти переведены в режим считывания, а подачей запрещающего сигнала на шину 13 блока 11 обнулен триггер 37 и тем. самым запрещено появление управляющих сигналов на его выходах. Других активных процессов в этом режиме не происходит. В режиме воспроизведения зарегистри рованной информации на шину 14 также поступает тактующий периодический сигнал, частота повторения которого выбира ется, исходя из требований визуального или машинного анализа информации, на шине 13 действует запрещающий уровень Он удерживает оба блока 7 и 10 в режиме считывания информации, запрещает Прохождение управляющего сигнала по цепи элементы 51 и 52 - элемент. ИЛИ 21 - выход формирователя 5 на чет вертый вход блока 8 управления, уде1 живает в сброшенном состоянии триггер 37 блока 11, заюфещая тем самым выда чу из блока 11 в блок 8 управления. В блоке 8 управления запрещающий уровень 1с шины 13 поступает через элемент НЕ 5О на вход эпемента И 45 разрешающим уровнем. При подаче на шииу 1 5 разрешающего уровня он поступает через третий вход блока В управления im вход элемента И 45, разрешая передачу через негЪ тактующего сигнала на входы элементов И 46-48. Далее работа усч ройства происходит в зависимости от сигналов, считанных из блоков 7 и 10. При равенстве нулевых сигналов на выходах блоков 7 и 10 в блоке 8 управления разрешается передача тактовых сигналов по цепи элемент И 45 - элемент И 47 - элемент ИЛИ 53 - первый выход блока 8 управления - первый вход блока 7. При этом производится последовательное считывание ячеек памяти; блока 7. .Считанный сигнал поступает на седьмой вход блока 8 управления, разрешает прохождение тактового сигнала по цепи элемент И 45 - элемент И 46элемент ИЛИ 52 - третий Е(ыход блока .8 управления - второй вход блока 10 и запрещает пррхохсдение сигналов чербз. элейент И 47. Это приводит к последовательному считыванию ячеек памяти блока 10. Процесс идет до считывания единицы из блока 10. Считанный сиг.нал из блока 10 поступает на второй вход блока 8 управления, вызывая прохождение сигнала через элемент И 49 на второй выход блока 8 управления и через элемент И 48, элемент ИЛИ 53 на первый выход блока 8 управления, что приводит к. занесению информационных сигналов в регистр 9, а также к однбму шагу в блоке 7. Если при этом считывается опять единица: из блока 7, то, как опи- . сано выше, производятся считывания ячеек памяти блока 10 до считывания 1, когда делается новый шаг в блоке 7 и передача новых информационных сигналов в регистр 9. Информация в регистре 9 при этом соответствует регистрируемой за исключением коротких сигналов помех. .О действии помех в момент ре-, гистрации можно судить по наличию в ячейках памяти блока 7 или блока 10 при сохранении некименной информации. Благодаря использованию формирователя 5, блока 11, блока 10, счетчика 4, элементов И-ИЛИ 6, а также соответст вутощему выполнению формирователя 5 блоков 11 и 8 и связей между ними в режиме регистрации непрерывно фжсируется информация и дискреты времени, в течение которых изменялась информация или действовали помехи, также при неогрвниченной апигепьности регистрации фиксированная информация сохраняется в устройстве (в предепах объема памяти) и при необходимости воспроизводится без искажений. По рравнению с известным устройствся в преапагаемом тре буеГся меньший ойъем памяти, так как ячейки памяти расходуются на фиксацию информации при ее изменении и воадейсг ВИИ помехи на фиксацию дискретов вре меня. Выигрыш возрастает с увеличением

числа каналов записи. В то же время, при необходимости регистрации кратковременных помех с помощью известного устройства требуется уменьшить период тактуюшего сигнала до меньшей дпитепьности помехи, что чрезвычайно увепичи1 емкость,памяти устройства, т.е. предлагав емое устройство оказывается более и формативным, обладает,меньшей емкостыо амяти и работает с более Шюкимй,тактовыми частотами.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля электронной вычислительной машины | 1981 |

|

SU1019451A1 |

| Устройство для считывания графической информации | 1982 |

|

SU1048493A1 |

| Способ обнаружения границ слов и устройство для его осуществления | 1989 |

|

SU1631580A2 |

| Устройство для многоканальной записи-воспроизведения информации | 1985 |

|

SU1273992A1 |

| Устройство сжатия информации | 1980 |

|

SU942109A2 |

| Логический анализатор | 1987 |

|

SU1476474A1 |

| Устройство для обмена информацией между аналоговой и цифровой вычислительными машинами | 1990 |

|

SU1755372A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Аппарат магнитной записи | 1982 |

|

SU1064312A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

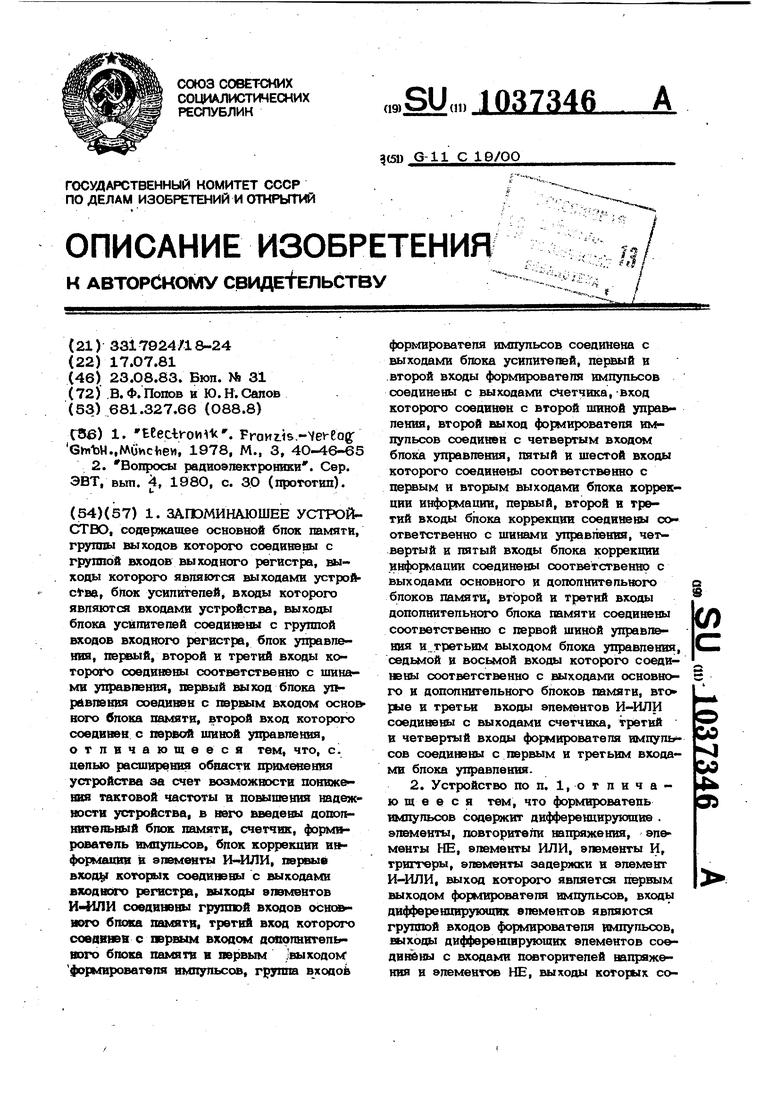

1. ЗАГОМИНАЮШЕЕ УСТРОЙСТВО, содержащее основной блок памяти, группы выходов которого соединены с группой входов выходного регистра, выходы которого являются выходами устройcfs, блок усилителей, входы которого являются входами устройства, выходы блока усилителей соединены с группой входов входного регистра, блок управления, первый, второй и третий входы которого соединены соответственно с шинами управления, первый выход блока у1ь рйвпения соединен с первым входом основного блока памяти, второй вход которого соединен с первой шиной управления, отличающееся тем, что, с. целью расширения обоасти применения устройства за счет возмож1юсти понижения тактовой частоты и повышения надеж ности устройства, в нехю введены дополнительный блок памяти, счетчик, формирователь импульсов, блок коррекции и формапии и элементы , вход%1 которых соединены с выходами входного регистра, выходы апэментов соединены группой входов основного блока памяти, третий вход которого сюеавнев с первым входом дополнительиого блока памяти и первым /выходом формирователя импульсов, группа входов формирователя импульсов, соединена с выходами блока усилитетюй, первый и .второй входы формирователя импульсов соединены с выходами счетчика,-вход которого соединен с второй щиной управления, второй выход формирователя импульсов соединен с четвертым входом блока управления, пятый и шестой входы которого соединены соответственно с первым и вторым выходами блока коррекции информации, первый, второй и третий входы блока коррекции соединены соответственно с шинами управления, четвертый и пятый входы блока коррекции информации соединены соответственно с выходами основного и дополнительного блоков памяти, второй и третий входы дополнительного блока памяти соединены соответственно с первой шиной управл ния и.третьим выходом блока управления, седьмой и восьмой вхооы которого соединены соответственно с выходами основного и дополнительного блоков памяти, вто рые и третьи входы элементов И-ИЛИ соединены с выходами счетчика, третий 00 и четвертый входы формирователя импуль сов соединены с первым и третьим входа00 4 ми блока утфавления. 2. Устройство поп. l,oтличaЭд ю щ е е с я тем, что формирователь импульсов содержит дифференцирующие . элементы, повторители напряжения, элементы НЕ, элементы ИЛИ, элементы И, триггеры, этюьюнты задержки и элемент И-ИЛИ, выход которого является первым выходом формирователя импульсов, входы дифференпируюитх елементов являются группой входов формирователя импульсов, выходы дифференцирующих элементов совди{ ны с входами повторителей напряжения и элементов НЕ, выходы которых со

7,

1г

Фиг2

Фиг,3

Фиг.

Авторы

Даты

1983-08-23—Публикация

1981-07-17—Подача