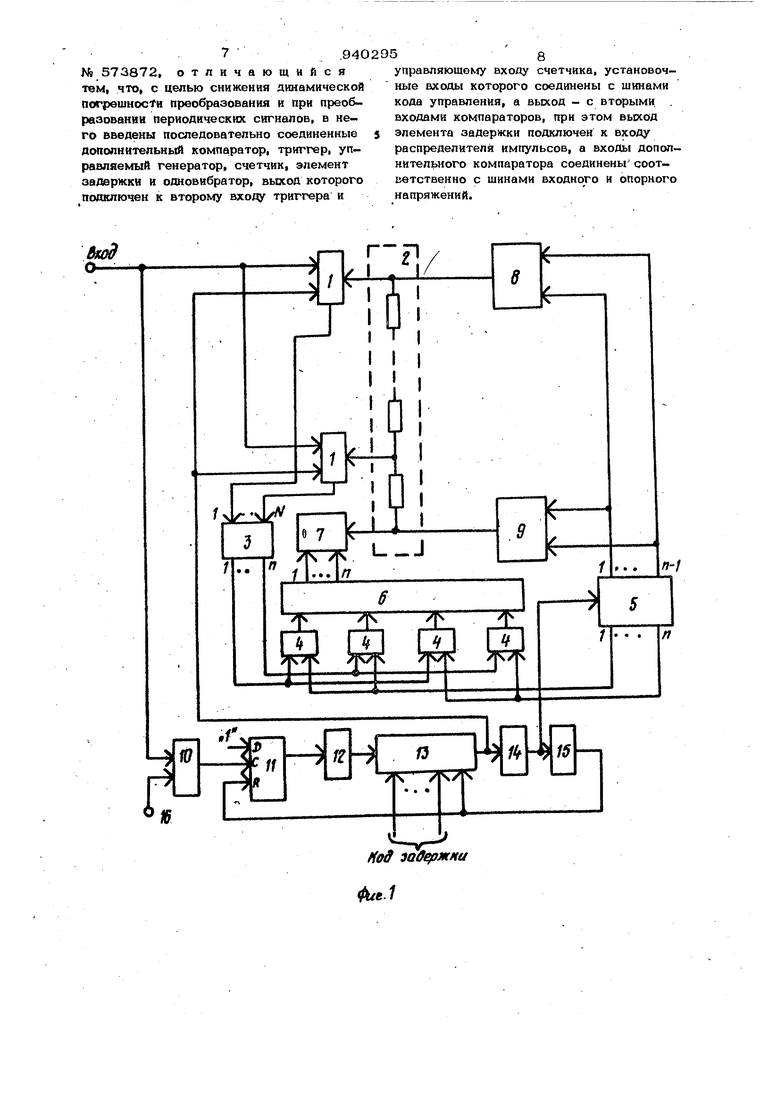

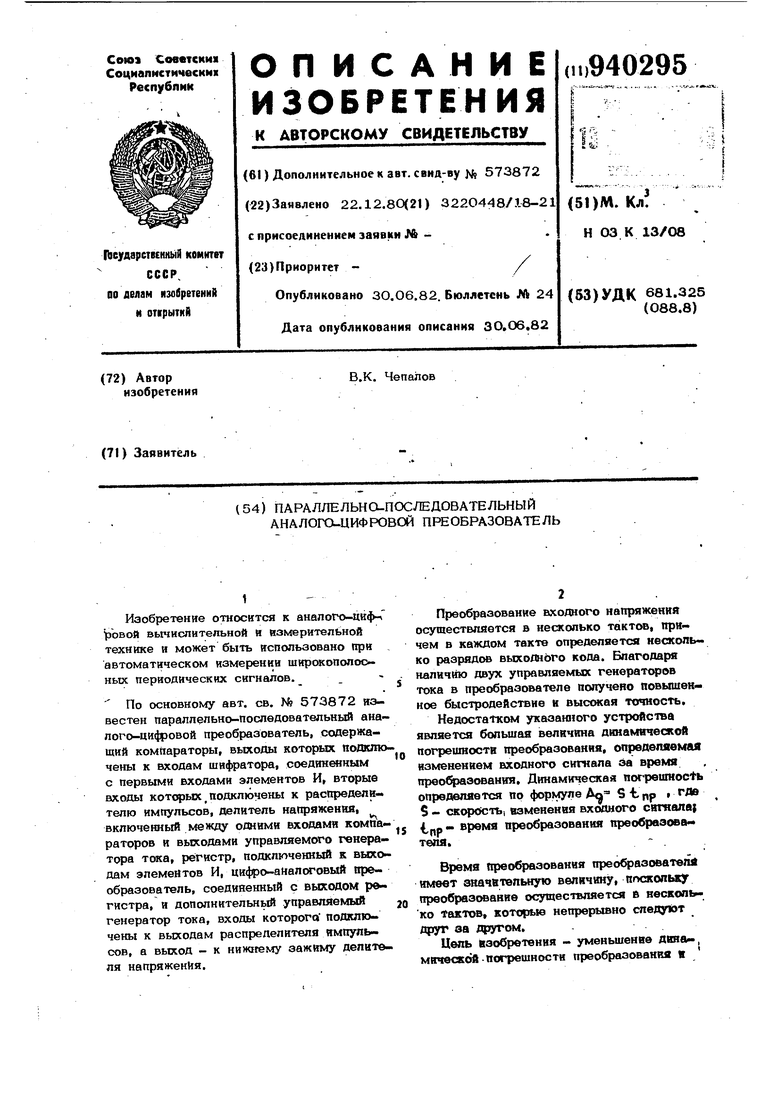

Изобретение относится к аналого-цнф-Г tJOBOfl вычислительной и измерительной технике и может быть использовано при автоматическом измерении широкополосных периодических сигналов. По основному авт. св. № 573872 известен параллельно-последовательный аналого-цифровой преобразователь, содержащий компараторы, выходы которых подклю чены к входам шифратора, соединенным с первыми входами элементов И, вторые входы которых, подключены к распредели.- телю импульсов, делитель напряжения, включенный между одними входами компараторов и выходами управляемого генератора тока, регистр, подключенный к выходам элементов И, цифро-аналоговый преобразователь, соединенный с выходом регистра, и дополнительнь1й управляемый генератор тока, входы которого подключены к вьиодам распределителя импульсов, а выход - к нимагему зажиму делителя напряжения. Преобразование входного напряжения осуществляется в несколько тактов, причем в каждом такте определяется несколько разрядов выходного кода. Благодаря налич1по двух управляемых генераторов тока в преобразователе получено повышенное быстродействие и высокая точность. Недостатком указанного устройства является большая величина динамической погрешности преобразования, определяемая изменением входного сигнала за время прео(зованш. Динамическая norpeuraoctb определяется по формуле До в -Ьцр где S - скорс стЬ| изменения входного сигнала} время преобразования преобразовав теля.Время преобразования преобразователи имеет значительную величину, поскопьку преобразование осуществляется в нескопько Тактов, которые непрерывно следзпот друг за другом. Цель изобретения - уменьшение двяа, мической-погрешности преобразования V 3 94029 при .преобразовании периодических сигны ° Указанная цель достигается тем, что в параллельно-последовательный аналогоцифровой преобразователь введены после-$ дрватеЛьно соединенные дополнительный компаратор, триггер, управляемый генератор, счетчик, элемент задержки и одноиибратор, выход которого подключен к второму входу триггера и управляюше-10 му входу счетчика, установочные входы которого соединены с шинами кода управления,.а выход - с вторыми входами компараторов, при этом выход элемента задержки подключен к входу распределите-,5 ля импульсов, а входы дополнительного компаратора соединены соответстоенно с шинами входного и опорного напряжений. Техническая сущность предлагаемого устройства заключается в снижении дина-JQ мической погрешности преобразования за счет того, что разные таКты преобразования осуществляются в разных периодах входного сигнала. Компараторы в предлагаемом устройств „ ве имеют дополнительный вход опроса. При этом компаратор изменяет свое состояние только при наличии импульса по входу опроса, таким образом можно зафиксировать состояние компаратора в определенный момент времени, т.е. п 5оизвес- ти сравнение в определенной точке преобразуемого сигнала. На фиг. 1 изображена функциональная. схема предлагаемого преобразователя; на фиг. 2 - времешые диаграммы. . Преобразователь содержит N компаратоп ров 1, делитель 2 напряжения, шифратор 3, элементы И 4, распределитель 5 импульч сов, регистр 6, цифро-аналоговый преобразователь (ЦАП) 7, управляемые генераторы 8 и 9 тока, дополнительный компаратор 1О, триггер 11, управляемый генератор 12, счетчик 13, элемент 14 задержки, одновибратор 15, вход 16 опорного напряжения (цепи начальной установки регистра 6, распределителя 5 импульсов, счетчика 13, триггера 11 условно не показаны). В исходном состоянии-триггеры регистра 6 находятся в состоянии О, соответственно, и вькодное напряжение ЦАП 7 тоже равно нулю. Генераторы 8 и 9 тока вырабатывают максимальные по величине токи, причем последние равны. между собой и противоположны по направ- лению. Под воздействием токов генераторов 8 и 9, протекающих через делитель 2, пороги срабатывания компараторов 1 54 устанавливаются такими, что весь диапазон изменения вх|рдной величины окааы-. вается разбитым на 2 зон, где h число параллельно определяемых двоичных разрядов. Пороги срабатывания компараторов при этом образуют шкалу Ш1 (фиг. 2а). При превышении периодическим вход ным сигналом (фиг. 2а) опорного уровня синхронизации Von,на выходе дополнитель„ого компаратора Ю формируется импульс„ый сигнал (фиг. 26), поступающий на динамический вход С р- триггера 11. На вход D-триггера постоянно подается уровень логической I. При поступлении „а вход С переднего фронта сигнала (фит. 26), на выходе триггера 11 устанав„ивается уровень логической , которым запускается управляемый генератор 12, йа выходе которого формируется послодовательность импульсов (фиг. 2в). в счетчик 13 предварительно заносит я код задержки, величина которого опрёделяет задержку момента преобразования входного сигнала относительно момента превышения входным сигналом опорного уровня. Код задержки подается на устаковочные входы счетчика 13 постоянно, запись в него осуществляется импульсом, поступающим на вход занесения счетчика. При поступлении на счетный вход счетчика 13 (М-к)-го импульса с управляемогогенератора 12 (гдеМ-полная ем-, кость счетчика 13; к - предварительно занесенный код) на выходе счетчика 13 формируется импульс переполнения (фиг, 2г), поступающий на входы опроса компараторов 1 и на вход элемента 14 задерж и. В результате по импульсу (фиг. 2г) момент времени t-i происходит сравнение сигнала (фиг. 2а) со шкалой Ш1, компараторами 1 фиксируется единичный который шифратором 3 преобразуется в двоичный код старших разрядов выходн:ого кода, С выхода элемента 14 задержки задержагаый импульс (фиг. 23) поступает на вход распределителя 5 импульсов и вход одновибратора 15. При поступлении на вход импульса (фиг. 23) распределитель 5 импульсов выдает по первым выходам импульсы, которыми через элемент И 4 заносится в регистр 6 код старщих разрядов н переключаются токи управляемых генераторов 8 и 9 тока. Токи генераторов 8 и 9 тока уменьшаются в N + 1 раз, вследствие чего падение напряжения на резисторах делителя 2 уменьшается во столько же раз. Поскольку в регистр 6 занесен код старших разрядов, на выходе ЦАП 7 устанавливается напряжение соответствующее коду старших разрядов. После окончания переходных процессов, вызванных переключениями, пороги срабатывания компараторов 1 образуют шкалу Ш 2 (фиг, 2а) для определения младших разрядов выходного кода. Элемент 14 задержки необходим для того, чтобы занесение информации в регистр 6 через элементы И 4 происходило после установ ления информации на выходе шифратора 3, т,е, для компенсации задержки в цепя компараторов 1 и шифратора 3, При поступлении импульса (фиг.2-г;) с выхода элемента 14 задержки одновибратор 15 формирует импульс (фиг.26), поступающий на вход ЯВ-трнггера 11, Длительность импульса одновибратора 15 выбирается такой, чтобы она была боль- ше времени установления шкалы Ш2, которое определяется временем переключения управляемых генераторов 8 и 9 тока и временем установления выходного напряжения ЦАП 7. Импульс (фиг.26), присутствующий на входе RD-триггера 1 устанавливает на его выходе уровень логического О, в результате чего прекра щается генерация импульсов генераторов 12 (фиг,2б), и импульсом, поступающим на вход занесения счетчика 13 с выхода одновибратора 15, в счетчик 13 вновь заносится код задержки. Кроме того, импульсом (фиг;26) триггер 11 блокируется, т.е. во время действия импульса триг гер 11 не реагирует на поступление импульсов (фиг.2) на динамический вход С, и уровень О на вхбде управляемого генератора остается неизменным. Наличие блокировки запуска триггера i 1 обесвечивает определение младших разрядов выходного кода только После того, как окончатся переходные процессы установления шкалы Ш2. Из фиг.2 следует, что при периоде повторения входного сигнала. (фиг.2а) меньше длительности импульса (фиг,26) (т.е., если время установления шкалы Ш больше периода следования входного преобразуемого сигнала) очередной импуя иходного сигнала пропускается и определение младших разрядов производится в третьем по счету периоде входного сигнала Этим обеспечивается зашита преобразовател от сбоев,которь1е могугвоаннкнуть при высо кой частоте повторения входного сигнала и 1фивести к существенной ошибке в определении результирующего кода. После окончания импульса (фиг.2) преобразователь снова готои к следующему такту преобразования, .который протекает аналогично первому , п|эи этом производят сравнение напряжения точки А Б момент времени Ь/2 со шкалой Ш2 и определение младших разрядов вькошого кода. В общем случае тактов преобразования может быть нескольку, их количество определяется разряднортью выходного кода и числом Ы/(сомпараторов. Роль распределителя 5 импульсов при этом сводится к тому, что при поступлении первого импульса с выхода элемента 14 задержки он формирует управляющие импульсы по первым выхода м, при поступлении второго импульса формируются управляющие импульсы по вторым выходам и так палее. Последнимупраиляющим импульсом заносится . код младших разрядов и триггеры младших разрядов регистра О, которые не связаны с цифро-аналоговым преобрюоопателем 7 (число разрядов НЛП 7 на И меньше чиола разрядов регистра 6). Управляемые генераторы 8 и О тока при этом но коммутируются, поскольку п последнем такте нет необходимости формирования следующей шкалы. . Таким образом, благодаря впедонию дополнительного компаратора, триггера, ; . управляемого генератора, счетчика, элемента задержки и олнопибратора реализуется стробоскопический режим работы аналого-цифрового прообразопателя, при котором опрос компараторов, т.е. фиксация одиннчного кода компараторов, производится всегда в одной и той же точке периодического сигнала (точка А на фиг.20). Изменение состояний ЦАП и генераторов тока производится в течение времени между двумя импульсами опроса, поэтому время установления ЦАП и управляемых генераторов тока не вносит вклада в динамическую погрешность преобразования. Динамическая погрешность преобраз( вания мгновенного значения сигнала практически определяется толькЪ апертурной погрешностью компараторов. Благодаря наличию блокировки запуска преобразователя импульсом одновибратора можно иопользовать менее быстродействующие, зато более простые и более точ1:ые ци4 ро-аналоговый прообраоопатель и управляемые генераторы тока. Формула изобретения Параллельно-последопа тельный анало го-цифровой преобразователь по авт. св.

№573872, отличающийся теМ| что, с целью снижения динамической погрешности преобразования и при преобрааовании периодических сигналов, в него введены последовательно соединенные дополнительный компЕ1ратор, триггер, управляемый генератор, счетчик, элемент задержки и одновибратор, выход которого подключен к второму входу триггера и

управляющему входу счетчика, установочные входы которого соединены с шинами кода управления, а выход - с вторыми. . входами компараторов, при этом выход элемента задержки подключен к входу распределителя импульсов, а входы дополнительного компаратора соединены соответственно с шинами входного и опорного напряжений.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1181144A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С КОРРЕКЦИЕЙ СЛУЧАЙНОЙ ПОГРЕШНОСТИ | 1991 |

|

RU2024193C1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1339890A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Устройство аналого-цифрового преобразования | 1989 |

|

SU1647894A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1297225A1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Логарифмический преобразователь напряжения в код | 1979 |

|

SU917337A1 |

| Параллельно-последовательный преобразователь напряжения в код | 1982 |

|

SU1039027A2 |

Код фut

iS

Авторы

Даты

1982-06-30—Публикация

1980-12-22—Подача