11

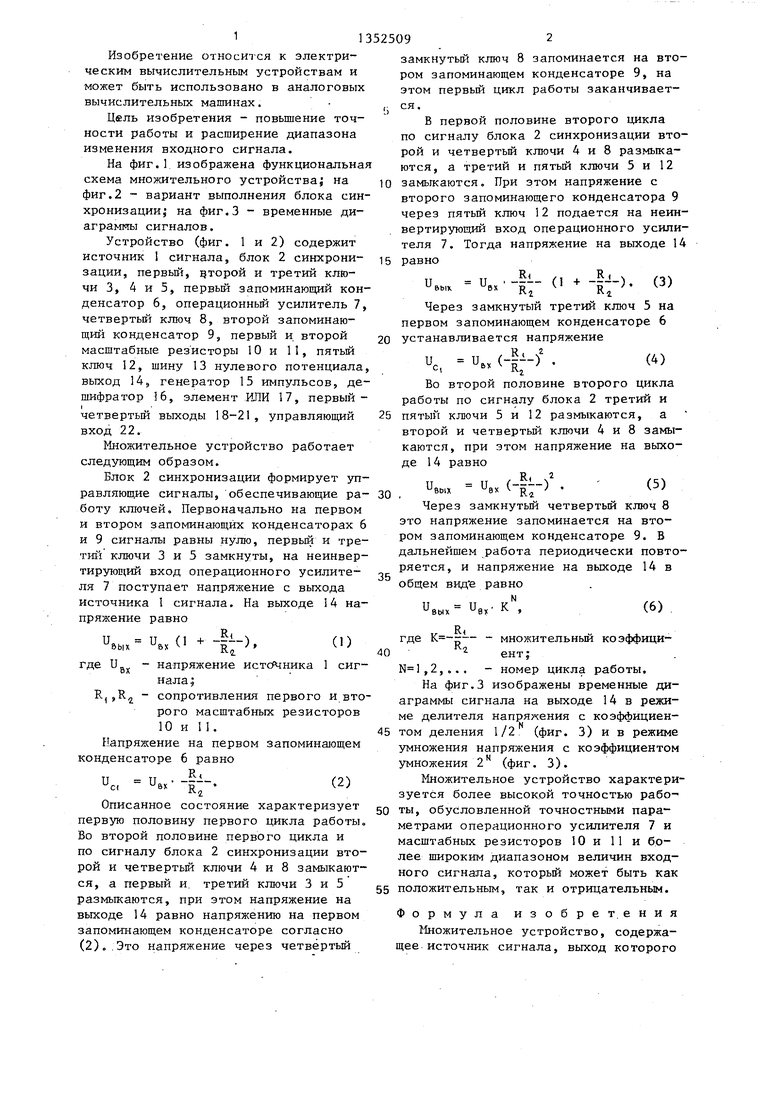

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах.

Цель изобретения - повьшение точности работы и расширение диапазона изменения входного сигнала.

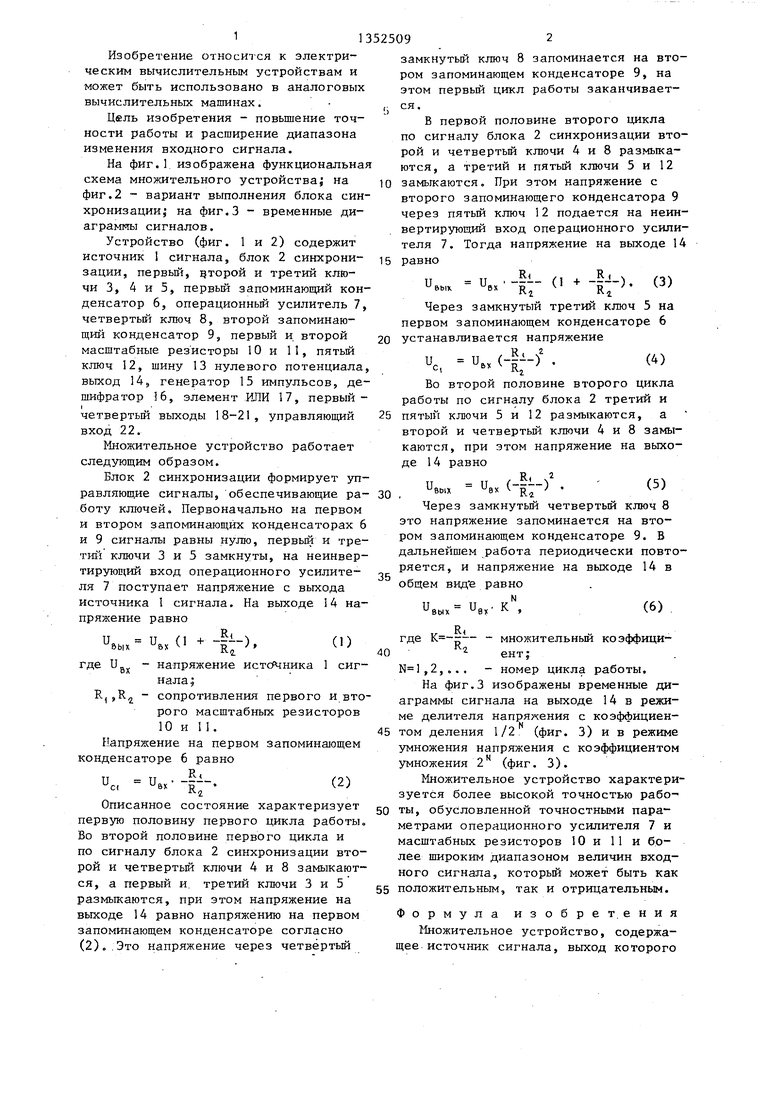

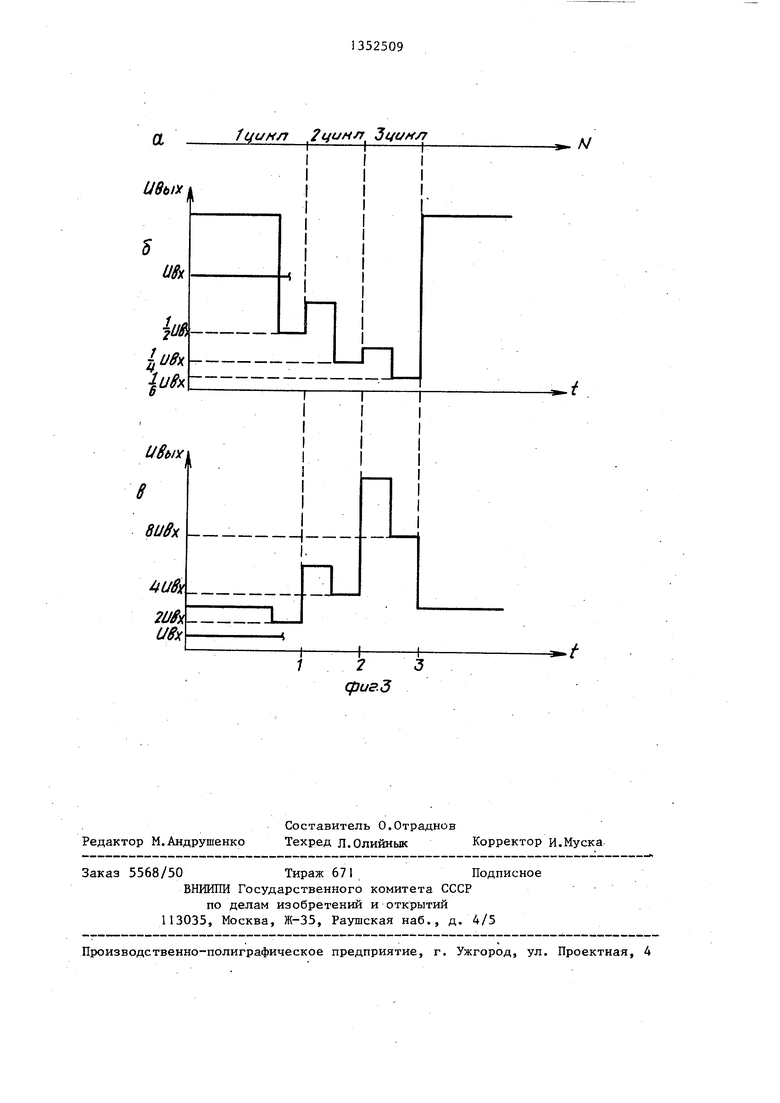

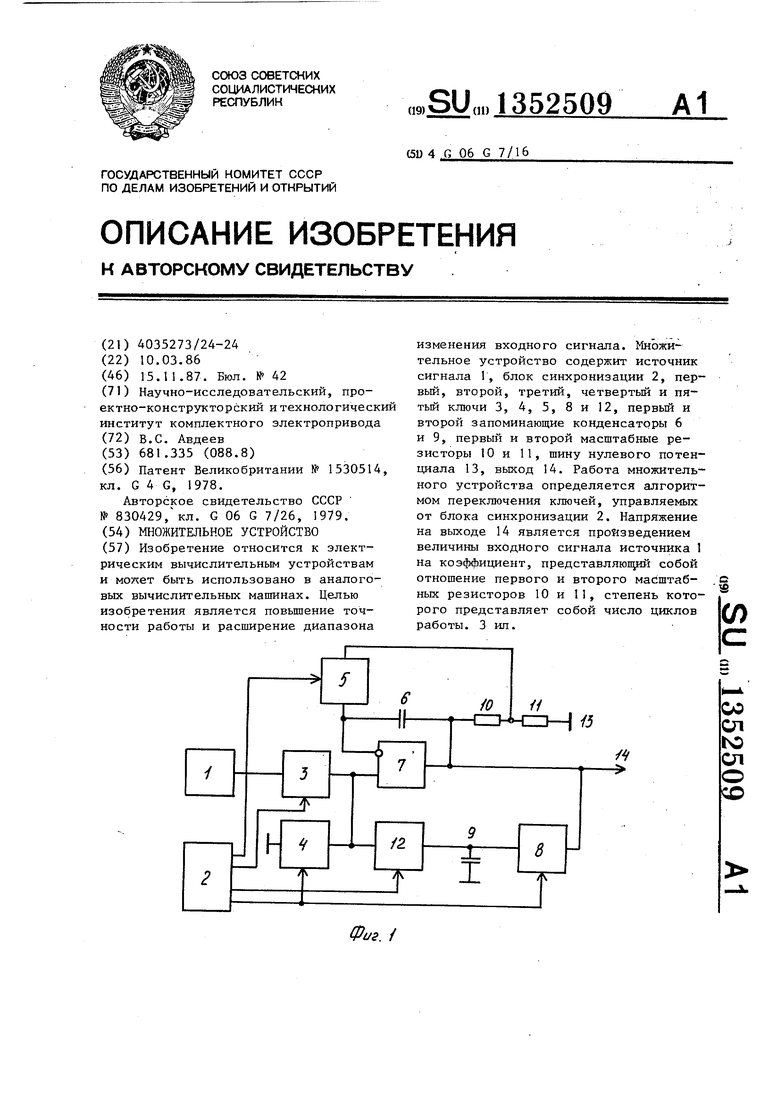

На фиг.1 изображена функциональна схема множительного устройства на фиг.2 - вариант выполнения блока синхронизации; на фиг.З - временные диаграммы сигналов.

Устройство (фиг. 1 и 2) содержит источник 1 сигнала, блок 2 синхронизации, первьш, второй и третий ключи 3, 4 и 5, первьй запоминающий конденсатор 6, операционньй усилитель 7, четвертый ключ 8, второй запоминающий конденсатор 9, первый и. второй масштабные резисторы 10 и 11, пятьй ключ 12, шину 13 нулевого потенциала выход 14, генератор 15 импульсов, дешифратор 16, элемент ИЛИ 17, первый - четвертьй выходы 18-21, управляющий вход 22.

Множительное устройство работает следующим образом.

Блок 2 синхронизации формирует управляющие сигналы, обеспечивающие ра- боту ключей. Первоначально на первом и втором запоминающих конденсаторах 6 и 9 сигналы равны нулю, первый и третий ключи 3 и 5 замкнуты, на неинвертирующий вход операционного усилителя 7 поступает напряжение с выхода источника 1 сигнала. На выходе 14 напряжение равно

и.ь,,, (1

де и

&

R

(1)

Вх

напряжение истсЛника 1 сигнала I

R,,R2 сопротивления первого и второго масштабных резисторов 10 и II.

Напряжение на первом запоминающем онденсаторе 6 равно R,

с, и,,.

(2)

Описанное состояние характеризует первую половину первого цикла работы. Во второй половине первого цикла и по сигналу блока 2 синхронизации второй и четвертьй ключи 4 и 8 замыкаются, а первый и. третий ключи 3 и 5 размыкаются, при этом напряжение на выходе 14 равно напряжению на первом запоминающем конденсаторе согласно (2),. Это напряжение через четвертьй

0

5

замкнутьй ключ 8 запоминается на втором запоминающем конденсаторе 9, на этом первьй цикл работы заканчивается.

В первой половине второго цикла по сигналу блока 2 синхронизации второй и четвертьй ключи 4 и 8 размыкаются, а третий и пятьй ключи 5 и 12 замыкаются. При этом напряжение с второго запоминающего конденсатора 9 через пятьй ключ 12 подается на неинвертирующий вход операционного усилителя 7. Тогда напряжение на выходе 14

равно

т.т

(3)

и.

и.

i

Ri

Rj)

R,

6ЫХ ex

Через замкнутый третий ключ 5 на первом запоминающем конденсаторе 6 устанавливается напряжение

и.

р

RJ

(4)

Во второй половине второго цикла работы по сигналу блока 2 третий и пятый ключи 5 и 12 размыкаются, а второй и четвертьй ключи 4 и 8 замыкаются, при этом напряжение на выходе 14 равно

(-1;-). (5)

Через замкнутьй четвертьй ключ 8 это напряжение запоминается на втором запоминающем конденсаторе 9. В альнейшем работа периодически повторяется, и напряжение на выходе 14 в общем вид е равно

N

вых

к

(6)

где К

Si

R.

- множительньй коэффициV/)

ент; ,2,... - номер цикла работы.

На фиг.З изображены временные диаграммы сигнала на выходе 14 в режиме делителя напряжения с коэффициентом деления 1/2 (фиг. 3) и в режиме З множения напряжения с коэффициентом умножения 2 (фиг. 3).

Множительное устройство характеризуется более высокой точностью работы, обусловленной точностными параметрами операционного усилителя 7 и масштабных резисторов 10 и 11 и более широким диапазоном величин входного сигнала, которьй может быть как

положительным, так и отрицательным.

ормула изобрет.ения Множительное устройство, содержаее источник сигнала, выход которого

3 - 1352509

подключен к информационному входу первого ключа, второй ключ, выход ко-: торого соединен с шиной нулевого потенциала, третий ключ, выход которого g подключен к инвертирующему входу операционного усилителя и к первой обкладке первого запоминающего конденсатора, вторая обкладка которого соения входного сигнала, в него введены первый и второй масштабные резисторы причем выход первого ключа соединен с информационным входом второго ключа и с неинвертирующим входом операционного усилителя, к выходу которого подключен первый вывод первого масштабного резистора, второй вывод

динена с выходом операционного усили- ю которого соединен с информационным теля и с информационным входом четвертого ключа, выход которого подключен к первой обкладке второго запоминающего конденсатора и к информационвходом третьего ключа и через второй масштабный резистор - с шиной нулево го потенциала, выход пятого ключа подключен к неинвертирующему входу

ному входу пятого ключа, блок синхро- 15 операционного усилителя, вторая обнизации, первый и второй вькоды которого подключены соответственно к управляющим входам четвертого и пятого ключей, выход операционного усилителя является выходом множительного уст-.. ройства, отличающееся тем, что, с целью повьш1ения точности работы и расширения диапазона измене20

кладка второго запоминающего конден сатора соединена с шиной нулевого потенциала, третий и четвертый выходы блока синхронизации подключены к уп равляющим входам соответственно пер вого и третьего ключей, а первый вы ход блока синхронизации соединен с управляющим входом второго ключа.

ния входного сигнала, в него введены первый и второй масштабные резисторы, причем выход первого ключа соединен с информационным входом второго ключа и с неинвертирующим входом операционного усилителя, к выходу которого подключен первый вывод первого масштабного резистора, второй вывод

которого соединен с информационным

входом третьего ключа и через второй масштабный резистор - с шиной нулевого потенциала, выход пятого ключа подключен к неинвертирующему входу

операционного усилителя, вторая об

кладка второго запоминающего конденсатора соединена с шиной нулевого по тенциала, третий и четвертый выходы блока синхронизации подключены к управляющим входам соответственно первого и третьего ключей, а первый выход блока синхронизации соединен с управляющим входом второго ключа.

фиг.2

Редактор М.Андрушенко

Составитель О.Отрадной

Техред Л.Олийнык Корректор И.Муска

Заказ 5568/50Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1101848A1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1042036A1 |

| Рекурсивное вычислительное устройство | 1988 |

|

SU1522264A1 |

| Устройство для интегрирования сигнала | 1988 |

|

SU1571623A1 |

| Интегратор | 1983 |

|

SU1088017A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU830584A1 |

| Устройство для решения дифференциальных уравнений | 1980 |

|

SU1339594A1 |

| Аналоговое множительно-делительное устройство | 1989 |

|

SU1640717A1 |

| Аналоговое запоминающее устройство | 1985 |

|

SU1320847A1 |

| Интегрирующее устройство | 1983 |

|

SU1105903A1 |

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах. Целью изобретения является повьшение точности работы и расширение диапазона изменения входного сигнала. Множительное устройство содержит источник сигнала 1, блок синхронизации 2, первый, второй, третий, четвертый и пя- тьй ключи 3, 4, 5, 8 и 12, первый и второй запоминающие конденсаторы 6 и 9, первый и второй масштабные резисторы 10 и 11, шину нулевого потенциала 13, выход 14. Работа множительного устройства определяется алгоритмом переключения ключей, управляемых от блока синхронизации 2. Напряжение на вьгходе 14 является произведением величины входного сигнала источника 1 на коэффициент, представляюпрт собой отношение первого и второго масштабных резисторов 10 и 11, степень которого представляет собой число циклов работы. 3 ил. i (Л ь ел tsD СЛ О ;О . /

| Узел крепления триангеля | 1987 |

|

SU1530514A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Функциональный преобразовательНАпРяжЕНия | 1979 |

|

SU830429A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-11-15—Публикация

1986-03-10—Подача