Изобретение относится к вычислительной технике и может быть использовано для фильтрации результатов измерений физического параметра в условиях нарушений в каналах связи.

Известен фильтр Калмана, содержащий вычитатель, усилитель, интегратор, первый, второй матричные умножители, два сумматора, генератор стационарного случайного процесса.

Однако данное устройство не позволяет оценивать состояния объектов, описываемых динамической моделью, а также не учи- тывает возможные нарушения в канале связи, приводящие к потере устойчивости фильтрации.

Наиболее близким к предлагаемому по технической сущности является фильтр Калмана, содержащий вычитатель, первый вход которого является входом фильтра, после- довательно соединенные первый умножитель, первый сумматор и интегратор, выход которого является выходом устройства, второй умножитель, выход которого соединен с инверсным входом первого сумматора, третий умножитель, выход которого соединен с выходом интегратора, второй сумматор, делитель, квадратор, первый, второй синусные преобразователи, косинусный преобразователь, дополнительный интегра- тор, четвертый-восьмой умножители, блок памяти, первый выход которого соединен с первыми входами четвертого и шестого умножителей, второй выход блока памяти соединен с первым входом второго сумматора, а третий выход блока памяти подключен к второму входу третьего умножителя и первому входу пятого умножителя, причем входы первого синусного и косинусного преобразователей подключены к выходу первого интегратора, выход первого синусного преобразователя соединен с вторым входом первого сумматора, а с первым входом второго умножителя - через делитель, выход косинусного преобразователя соеди- нен с вторым входом пятого умножителя и первым входом седьмого умножителя, выход которого соединен с вторым входом второго сумматора, а выход пятого умножителя соединен с вторым входом четвертого умно- жителя и первым входом восьмого умножителя, выход которого через квадратор

подключен к второму входу шестого умножителя, выход которого соединен с инверсным входом второго сумматора, выход которого соединен через дополнительный интегратор с вторыми входами второго, седьмого и восьмого умножителей и третьим входом четвертого умножителя, выход которого подключен к первому входу первого умножителя, второй вход которого соединен с выходом вычитателя, второй вход которого соединен через второй синусный преобразователь с выходом третьего умножителя.

Данное устройство не позволяет оценивать наблюдаемые данные в условиях возможных нарушений в канале связи (передачи данных), приводящих к значительному увеличению шумовой составляющей наблюдаемого вектора.

Цель изобретения - повышение точности фильтрации в условиях действия помех при априорно известных вероятностях появления аномальных измерений.

Указанная цель достигается тем, что в цифровой фильтр, содержащий последовательно соединенный первый вычитатель, первый умножитель и первый сумматор, блок памяти, первый выход которого подключен к первому входу второго сумматора, второй выход - к первым входам второго и третьего умножителей, а третий выход - к первым входам четвертого и пятого умножителей, первый делитель, выход которого подключен к первому входу шестого умножителя, а также седьмой и восьмой умножители и квадратор при этом выход второго умножителя соединен с первым входом первого вычитателя, второй и третий вычитате- ли, третий-седьмой сумматоры, девятый- пятнадцатый умножители, второй-пятый делители, первый и второй экспоненциальные преобразователи, первый и второй инверторы, блок извлечения квадратного корня, первый, второй и третий элементы задержки, триггер, счетчик, блок элементов И и элемент И, причем квадратор, второй делитель, первый инвертор, третий делитель, первый экспоненциальный преобразователь и одиннадцатый умножитель включены последовательно между выходом первого вычитателя и вторым входом шестого умножителя, пятый делитель, блок извлечения квадратного корня, девятый и десятый умножители и третий сумматор включе- ны последовательно между выходом второго сумматора и входом первого делителя, пятнадцатый умножитель, пятый сум- матор, четвертый делитель и второй экспоненциальный преобразователь включены последовательно между первым выходом блока памяти и вторым входом десятого умножителя, выход второго сумматора сое- динен с вторым входом третьего делителя, выход пятого сумматора подключен к второму входу пятого делителя, выход одиннадцатого умножителя подключен к второму входу третьего сумматора, выход третьего вычитателя подключен к второму входу девятого умножителя, выход шестого умножителя соединен с первым входом седьмого умножителя и третьим входом первого умножителя, через четвертый сумматор - с первым входом восьмого умножителя и через второй вычитатель с третьим входом седьмого умножителя, выход которого подключен к первому входу двенадцатого умножителя, второй вход которого объединен с вторыми входами первого, седьмого и восьмого умножителей и подключен к выходу четырнадцатого умножителя, а третий и четвертый входы объединены и подключены к выходу первого вычитателя, при этом второй выход блока памяти подключен к первому входу тринадцатого умножителя, второй вход которого соединен с выходом восьмого умножителя, а выход - через второй инвертор с первым входом седьмого сумматора, четвертый выход блока памяти подключен к первому входу шестого сумматора, второй вход которого соединен с выходом пятого умножителя, а выход - с вторыми входами второго и пятого суммато- ров и третьим входом восьмого умножителя, пятый выход блока памяти подключен к второму входу одиннадцатого умножителя и входу третьего вычитателя. шестой выход блока памяти подключен к второму входу пятнадцатого умножителя, седьмой выход блока памяти подключен к первому входу четырнадцатого умножителя, второй вход которого соединен с выходом третьего умножителя, второй вход которого объединен через второй элемент задержки с вторым входом пятого умножителя и подключен к выходу седьмого сумматора, второй вход которого соединен с выходом двенадцатого умножителя, адресные входы блока памят подключены к соответствующим выходам счетчика, вход считывания - к выходу третьего элемента задержки, вход которого объединен со счетным входом счетчика и входом разрешения блока элементов И и подключен к выходу элемента И, первый вход которого подключен к шине тактовых импульсов, а второй вход - к выходу триггера, нулевой вход триггера подключен к выходу старших разрядов счетчика, единичный вход объединен с установочным входом счетчика и подключен к шине импульсов запуска, второй вход блока элементов И является информационным входом цифрового фильтра, выход подключен к второму входу первого вычитателя, выход первого сумматора соединен через последовательно включенные первый элемент задержки и четвертый умножитель с вторым входом второго умножителя и является информационным выходом цифрового фильтра.

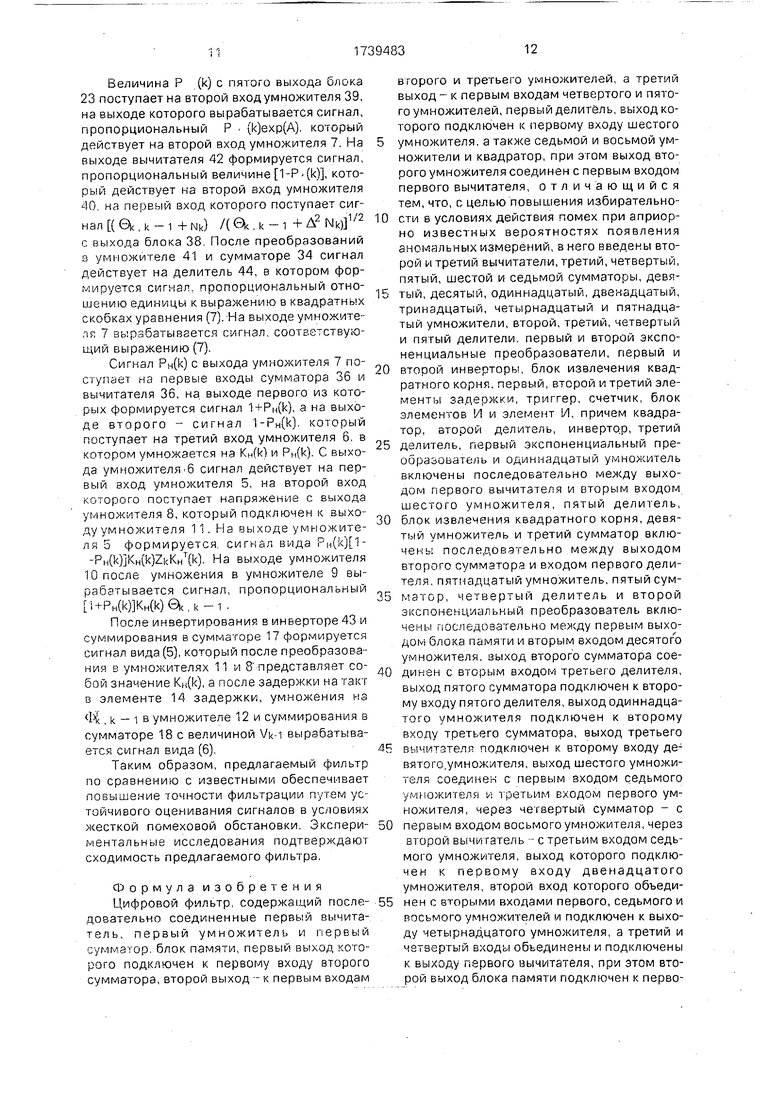

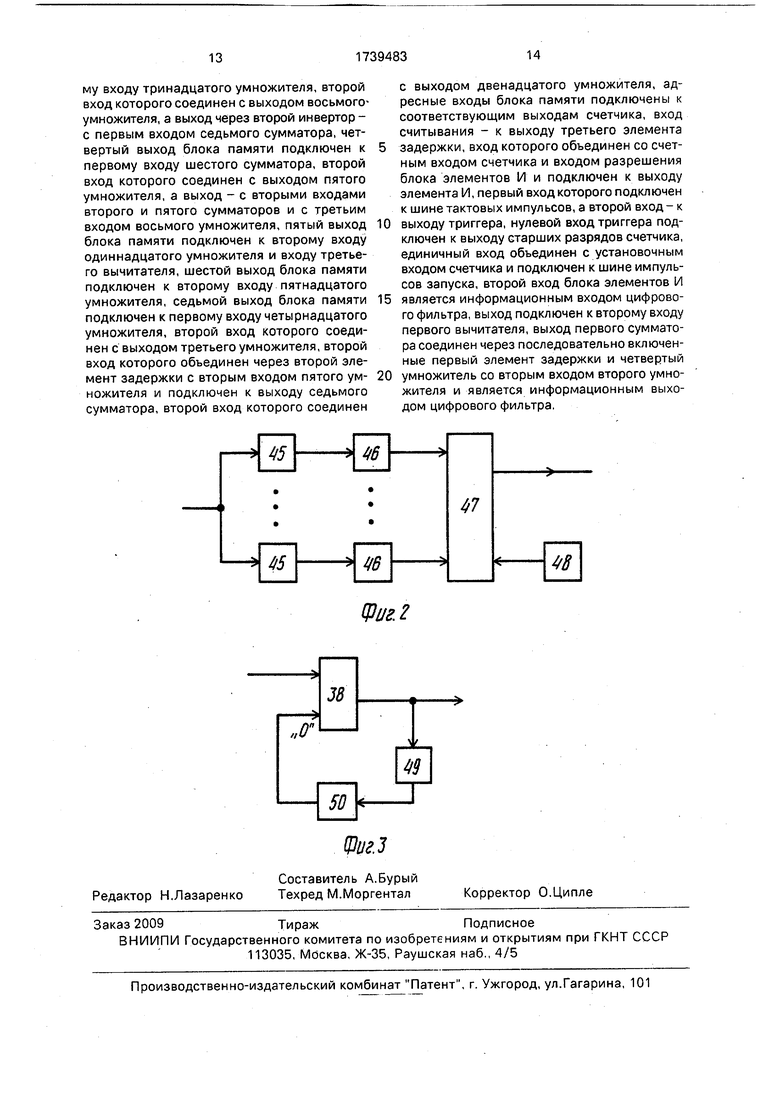

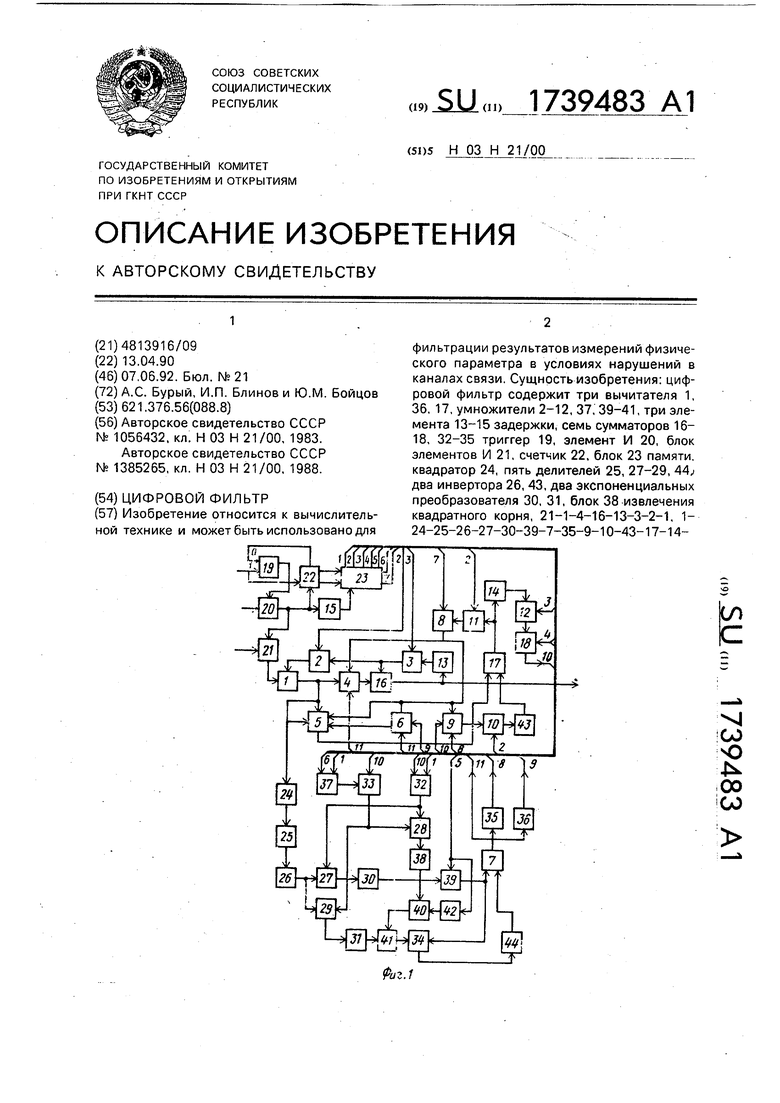

На фиг. 1 представлена функциональная схема устойчивого фильтра; на фиг. 2 - функциональная схема экспоненциального преобразователя; на фиг. 3 - функциональная схема блока извлечения корня квадратного.

Устойчивый фильтр содержит первый вычитатель 1, второй умножитель 2, четвертый 3, первый 4, двенадцатый 5, седьмой 6, шестой 7, четырнадцатый 8, восьмой 9, тринадцатый 10, третий 11 и пятый 12 умножители, третий 13, второй 14 и первый 15 элементы задержки, первый 16, седьмой 17 и шестой 18 сумматоры, триггер 19, элемент И 20, блок 21 элементов И, счетчик 22, блок 23 памяти, квадратор 24, второй делитель 25, первый инвертор 26, третий 27, пятый 28 и четвертый 29 делители, первый 30 и второй 31 экспоненциальные преобразователи, второй 32, пятый 34 и четвертый 35 сумматоры, второй вычитатель 36, пятнадцатый умножитель 37, блок 38 извлечения квадратного корня, одиннадцатый 39, девятый 40 и десятый 41 умножители, третий вычитатель 42, второй инвертор 43 и первый делитель 44.

Экспоненциальный преобразователь содержит блоки 45 возведения в степень группы, весовые блоки 46 группы, сумматор 47 и регистр 48 числа. Входы блоков 45 являются входом преобразователя 30 (31), а выход сумматора 47 -- его выходом. Преобразование осуществляется согласно выра00 хп жения --, величина поступает на

п 1П

входы блоков 45, число которых выбирается из требуемой точности. В регистре 48 хранится заранее записанная в него единица, которая также используется для функционирования сумматора 35, вычитателя 36 и делителя 25 (эта взаимосвязь на фиг. 1 не показана).

В блоке извлечения квадратного корня установка в О перед началом работы производится по дополнительному входу, а в каждом такте работы - через элемент ИЛИ 49 и элемент 50 задержки (фиг, 3), необходи- мый для обеспечения времени передачи информации с блока 38 на последующие элементы устройства.

Умножители могут быть выполнены в соответствии с известным, причем трех- и более входовые умножители представляют собой последовательное соединение двух и более умножителей, когда результат умножения двух сомножителей умножается на третье, а потом на 4-е число. Блок 23 памяти представляет собой объединение семи ОЗУ, каждое из которых выполнено на микросхеме К 155 РУ 2, в которых хранится массив соответствующих параметров, объем которого соответствует объему оцениваемого массива измерительной информации.

Единичный вход триггера 19, являющийся входом запуска фильтра, соединен с устойчивым входом счетчика 22, выход старшего разряда которого подключен к ну- левому входу триггера 19, прямой выход которого соединен с разрешающим входом элемента И 20, первый вход которого подключен к шине тактовых импульсов устройства, а выход соединен через элемент 15 задержки с входом считывания, а через счетный вход, оставшиеся выходы счетчика 22, -с адресными входами блока 23, первый выход которого подключен к первому входу умножителя 37 и первому входу сумматору 32, второй выход - к соответствующим входам умножителей 2, 11 и 10, третий выход - к первым входам умножителей 3 и 12, четвертый выход - к первому входу сумматора 18, пятый выход к второму входу умножите- ля 39 и входу вычитателя 42, шестой выход - к первому входу умножителя 37, седьмой выход через умножитель 8 - к второму входу умножителя 4, вторым входам умножителей 6 и 9 и умножителя 5, третий и четвертый входы которого соединены с выходом вычитателя 1, первым входом умножителя 4, входом квадратора 24, первый вход- с выходом умножителя 6, а выход через сумматор 17, умножитель 11 - с вторым входом умножи- теля 8. Выход сумматора 17 через элемент 14 задержки, умножитель 12, сумматор 18 подключен к второму входу сумматора 33, второму входу сумматора 32, третьему входу умножителя 9, выход которого через умно- житель 10. инвертор 43 соединен с первым входом сумматора 17. Разрешающий вход блока 21 элементов И подключен к выходу элемента И 20, а информаторный вход является информационным входом фильтра. Выход блока 21 подключен к второму входу вычитателя 1, первый вход которого соединен с выходом умножителя 2, второй вход которого подключен к выходу умножителя 3 и второму входу сумматора 16, первый вход которого соединен соответственно с выходом умножителя 4, а выход - с входом элемента 13 задержки, выход которого подключен к второму входу умножителя 3. Выход сумматора 16 является информационным выходом фильтра. Выход квадратора 24 через делитель 25, инвертор 26 соединен с входами делителей 27 и 29, выходы которых подключены соответственно к входам преобразователей 30 и 31. Выход умножителя 37 через сумматор 33 соединен с вторым входом делителя 29 и вторым входом делителя 28, первый вход которого подключен к выходу сумматора 32, второму входу делителя 27, а выход через блок 38, умножители 40 и 41, сумматор 34, делитель 44 и умножитель 7 - к третьему входу умножителя 4, первому входу умножителя 6, -ретий вход которого соединен с выходом вычитателя 36, вход которого подключен к выходу умножителя 7, а через сумматор - к первому входу умножителя 9. Выход преобразователя 30 соединен с вторым входом умножителя 7 и вторым входом сумматора 34. Выход преобразователя 31 подклюнен к второму входу умножителя 41.

В формализованном виде алгоритм фильтрации может быть представлен следующими уравнениями состояния и наблюдения:

x(k+1) l5k + i.kx|k) + Vk;(1)

g(k)Hkx(k)f Ok He(2)

где х n-мернь и вектср состояния системы;

Ф- переходная (пхп) матрица;

V - вектор гауссовских шумов возмущений с нулевым средним;

g - m-мерный вектор наблюдений;

Н - матрица наблюдений системы; v- гауссовы шумы измерений; Ok- случайная величина, причем «k 1 с вероятностью Pk соответствует нормальной работе канала измерений и «k A(A 1) с вероятностью 1Pk при отказах, связанных с пропаданием полезного сигнала.

Оценка вектора состояния системы х определяется нормальной хн и аномальной составляющими хи;

x(k)XH(k)PH(k)+x (k)1-PH(k), (3) но с учетом общего выражения для оценки (4) и того, что при А 1 коэффициент усиления фильтра стремится к 0, имеем

x(k)x(k,k-1)+PH(k)KH(k) Z (k.k-1), (4)

где Z(k, k-1)g(k)-Hkx(k,k-1) - характеризует обновляющий процесс в фильтре; KH(k) 6kT HkT - коэффициент усиления фильтра при нормальном функционировании. 0k - ковариационная матрица погрешностей фильтрации определяется по формуле

а е, k -1 n-pH(k)KH(k)Hk е.k -1 +

+ PH(k)1-PH(k)KH(k)ZkKHT(k),(5)

rAeZk Z(k, k-1)ZT(k, k-1);

©k , k - 1 С1 . k - 1 ©k - 1 (K k k - 1 + + Vk-1,(6)

где Vk-1 - ковариационная матрица шумов возмущений.

Вероятность нормального функционирования канала измерений оценим как апостериорную вероятность

Рн() Р (k)e p,,(k)eA

+

Qk.k -1 +Nk

0k , k - 1 + A2 Nk

,Уг

(1 - P (k) exp

| irg(k4J-x(k.k-itf|1-1 m

1 n0Г I )

2 0k. k - 1 + A2 Nk

где A- -I g(k)-x(k, k-1)2/ Эк. k - 1

P (k) - апостериорная вероятность того, что

Nk - ковариационная матрица шумов измерений.

С учетом выражений (1)-(7) фильтр работает следующим образом. В блоке 23 памяти перед началом работы записаны значэния матриц N, Н, Ф. V. которые снимаются соответственно с первой, второй, третьей, четвертой групп выходов, а с пятого, шестого, седьмого выходов - величины

вероятностей Р , коэффициента А2 и матрицы .

Импульс запуска поступает на запускающий вход устройства, чем является иход 1 триггера 19, устанавливает в О счетчик 22. Напряжение с прямого выхода триггера 19 действует на разрешающий вход элемента И 20, после чего тактовые импульсы с

0

5

входа тактовых импульсов устройства через элемент И 20 проходят на счетный вход счетчика 20 и на разрешающий вход блока 21 элементов И, обеспечивая поступление входного сигнала g(k) в параллельном двоичном коде на первый вход вычитателя 1. При подсчете I импульсов сигналом с выхода старшего разряда счетчика 22 сбрасывается в О триггер 19, С помощью других выходов счетчика 22 обеспечивается адресный выбор соответствующих данных с блока 23 на каждый 1-й момент (,1) времени. Считывание данных с блока 23 производится по импульсу с выхода элемента 15 задержки, в котором происходит задержка тактового импульса на время, необходимое для срабатывания счетчика 22. На первый вход вычитателя 1 поступает сигнал, пропорциональный выражению Нкх (k, k-1) с выхода 0 умножителя 2, на который поступают сигнал из блока 23 памяти и сигнал x(k, k-1) с выхода умножителя 3. На выходе вычитателя 1 формируется сигнал Z(k, k-1), который поступает на первый вход умножителя 4 и на третий и четвертый входы умножителя 5, причем третий вход умножителя 5 так заком- мутирован с выходом вычитателя 1, чтобы его выходной Z был представлен в транспонированном виде. С выхода вычитателя 1 сигнал преобразуется в квадраторе 24. На третий вход умножителя 4 поступает сигнал PH(k) с выхода умножителя 7, а на второй - сигнал соответствующий KH(k) с выхода умножителя 8. Таким образом, на выходе сумматора 16 получаем сигнал вида (4). На выходе квадратора 24 формируется сигнал g(k)-x (k, k-1), который делится на два делителем 25, инвертируется инвертором 26. На выходе сумматора 32 формируется сигнал вида Ok. k - 1 + Nk, который поступает в делитель 27, где вырабатывается сигнал, пропорциональный параметру А. На выходе сумматора 33 формируется сигнал вида

©к , k - 1 + A2 Nk, причем параметр А2 поступает на соответствующий вход умножителя 37 с шестого выхода блока 23.

5

0

5

0

5

На первый вход делителя 29, как и на вход делителя 27, поступает сигнал вида g(k)-x (k, k-1)2/2 , а на второй вход делителя 29 - сигнал с выхода сумматора 33. Таким образом, на выходе преобразователя 31 формируется сигнал вида

fl2/,fc

exp{- g(k)-x (k, k-1)f/ В . k - 1 + A2 ,

а на выходе преобразователя 30 сигнал ехр(А), поступающий на первый вход умножителя 39.

Величина Р (k) с пятого выхода блока 23 поступает на второй вход умножителя 39, на выходе которого вырабатывается сигнал, пропорциональный Р (к)ехр(А). который действует на второй вход умножителя 7. На выходе вычитателя 42 формируется сигнал, пропорциональный величине 1-P-(k)j, который действует на второй вход умножителя 40, на первый вход которого поступает сигнал ( 6k , k - 1 + Nk) /(6k , k - 1 + Л2 Nk)1/2 с выхода блока 38, После преобразований а умножителе 41 и сумматоре 34 сигнал действует на делитель 44, в котором формируется сигнал, пропорциональный отношению единицы к выражению в квадратных скобках уравнения (7). На выходе умножителя 7 вырабатывается сигнал, соответствующий выражению (7).

Сигнал Рн(к) с выхода умножителя 7 по- оупает на первые входы сумматора 36 и вычитателя 36, на выходе первого из которых формируется сигнал 1+Pn(k), а на выходе второго - сигнал 1-PH(k). которым поступает на третий вход умножителя 6. в котором умножается на KH(k) и Pn(k). С выхода умножителя 6 сигнал действует на первый зход умножителя 5, на второй вход которого поступает напряжение с выхода умножителя 8, который подключен к выходу умножителя 11. На выходе умножителя 5 формируется сигнал вида PH(k)1- -PH(k)KH((k). На выходе умножителя 10 после умножения в умножителе 9 вырабатывается сигнал, пропорциональный Рн(к)Кн(к) Q, k - 1 .

После инвертирования в инверторе 43 и суммирования в сумматоре 17 формируется сигнал вида (5), который после преобразования в умножителях 11 и 8 представляет собой значение Кц(), а после задержки на такт в элементе 14 задержки, умножения на

Ф(с, k - 1 в умножителе 12 и суммирования в сумматоре 18 с величиной Vk-1 вырабатывается сигнал вида (6).

Таким образом, предлагаемый фильтр по сравнению с известными обеспечивает повышение точности фильтрации путем устойчивого оценивания сигналов в условиях жесткой помеховой обстановки. Экспериментальные исследования подтверждают сходимость предлагаемого фильтра.

Формула изобретения Цифровой фильтр, содержащий последовательно соединенные первый вычита- тель. первый умножитель и первый сумматор, блок памяти, первый выход которого подключен к первому входу второго сумматора, второй выход - к первым входам

второго и третьего умножителей, а третий выход - к первым входам четвертого и пятого умножителей, первый делитель, выход которого подключен к первому входу шестого

умножителя, а также седьмой и восьмой умножители и квадратор, при этом выход второго умножителя соединен с первым входом первого вычитателя, отличающийся тем, что, с целью повышения избирательно0 сти в условиях действия помех при априорно известных вероятностях появления аномальных измерений, в него введены второй и третий вычитатели, третий,четвертый, пятый, шестой и седьмой сумматоры, девя5 тый, десятый, одиннадцатый, двенадцатый, тринадцатый, четырнадцатый и пятнадцатый умножители, второй, третий, четвертый и пятый делители, первый и второй экспоненциальные преобразователи, первый и

0 второй инверторы, блок извлечения квадратного корня, первый, второй и третий элементы задержки, триггер, счетчик, блок элементов И и элемент И, причем квадратор, второй делитель, инвертор, третий

5 делитель, первый экспоненциальный преобразователь и одиннадцатый умножитель включены последовательно между выходом первого вычитателя и вторым входом шестого умножителя, пятый делитель,

0 блок извлечения квадратного корня, девятый умножитель и третий сумматор включены последовательно между выходом второго сумматора и входом первого делителя, пятнадцатый умножитель, пятый сум5 матор, четвертый делитель и второй экспоненциальный преобразователь включены последовательно между первым выходом блока памяти и вторым входом десятого умножителя, зыход второго сумматора сое0 динен с вторым входом третьего делителя, выход пятого сумматора подключен к второму входу пятого делителя, выход одиннадцатого умножителя подключен к второму входу третьего сумматора, выход третьего

5 вычитзтеля подключен к второму входу девятого.умножителя, выход шестого умножителя соединен с первым входом седьмого умножителя л третьим входом первого умножителя, через четвертый сумматор - с

0 первым входом восьмого умножителя, через второй вымогатель - с третьим входом седьмого умножителя, выход которого подключен к первому входу двенадцатого умножителя, второй вход которого объеди5 нен с вторыми входами первого, седьмого и восьмого умножителей и подключен к выходу четырнадцатого умножителя, а третий и четвертый входы объединены и подключены к выходу первого вычитателя, при этом второй выход блока памяти подключен к первому входу тринадцатого умножителя, второй вход которого соединен с выходом восьмого- умножителя, а выход через второй инвертор - с первым входом седьмого сумматора, четвертый выход блока памяти подключен к первому входу шестого сумматора, второй вход которого соединен с выходом пятого умножителя, а выход - с вторыми входами второго и пятого сумматоров и с третьим входом восьмого умножителя, пятый выход блока памяти подключен к второму входу одиннадцатого умножителя и входу третьего вычитателя, шестой выход блока памяти подключен к второму входу пятнадцатого умножителя, седьмой выход блока памяти подключен к первому входу четырнадцатого умножителя, второй вход которого соединен с выходом третьего умножителя, второй вход которого объединен через второй элемент задержки с вторым входом пятого умножителя и подключен к выходу седьмого сумматора, второй вход которого соединен

с выходом двенадцатого умножителя, адресные входы блока памяти подключены к соответствующим выходам счетчика, вход считывания - к выходу третьего элемента

задержки, вход которого объединен со счетным входом счетчика и входом разрешения блока элементов И и подключен к выходу элемента И, первый вход которого подключен к шине тактовых импульсов, а второй вход- к

выходу триггера, нулевой вход триггера подключен к выходу старших разрядов счетчика, единичный вход объединен с установочным входом счетчика и подключен к шине импульсов запуска, второй вход блока элементов И

является информационным входом цифрового фильтра, выход подключен к второму входу первого вычитателя, выход первого сумматора соединен через последовательно включенные первый элемент задержки и четвертый

умножитель со вторым входом второго умножителя и является информационным выходом цифрового фильтра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для прогнозирования длительности производственных операций | 1990 |

|

SU1781685A1 |

| Устройство для нахождения экстремумов | 1985 |

|

SU1287180A1 |

| Фильтр Калмана | 1987 |

|

SU1385265A1 |

| Устройство для сжатия информации | 1982 |

|

SU1056249A1 |

| Устройство для распознавания прямого края объекта | 1988 |

|

SU1716549A1 |

| Цифровой измеритель показателей качества электрической энергии трехфазной сети | 1988 |

|

SU1633368A1 |

| Устройство для определения закона распределения случайной величины | 1986 |

|

SU1425713A1 |

| Цифровой квадратичный интерполятор | 1985 |

|

SU1290354A1 |

| ЦИФРОВОЙ РАДИОПЕЛЕНГАТОР | 1999 |

|

RU2149419C1 |

| Устройство для передачи телеметрической информации | 1983 |

|

SU1126993A1 |

Изобретение относится к вычислительной технике и может быть использовано для фильтрации результатов измерений физического параметра в условиях нарушений в каналах связи. Сущность изобретения: цифровой фильтр содержит три вычитателя 1, 36, 17, умножители 2-12, 37, 39-41, три элемента 13-15 задержки, семь сумматоров 16- 18, 32-35 триггер 19, элемент И 20, блок элементов И 21, счетчик 22, блок 23 памяти, квадратор 24, пять делителей 25, 27-29, 44; два инвертора 26, 43, два экспоненциальных преобразователя 30, 31, блок 38 извлечения квадратного корня, 21-1-4-16-13-3-2-1, 1- 24-25-26-27-30-39-7-35-9-10-43-17-14

9 и г. 2

| Регуляризованный фильтр Калмана | 1982 |

|

SU1056432A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Фильтр Калмана | 1987 |

|

SU1385265A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-06-07—Публикация

1990-04-13—Подача