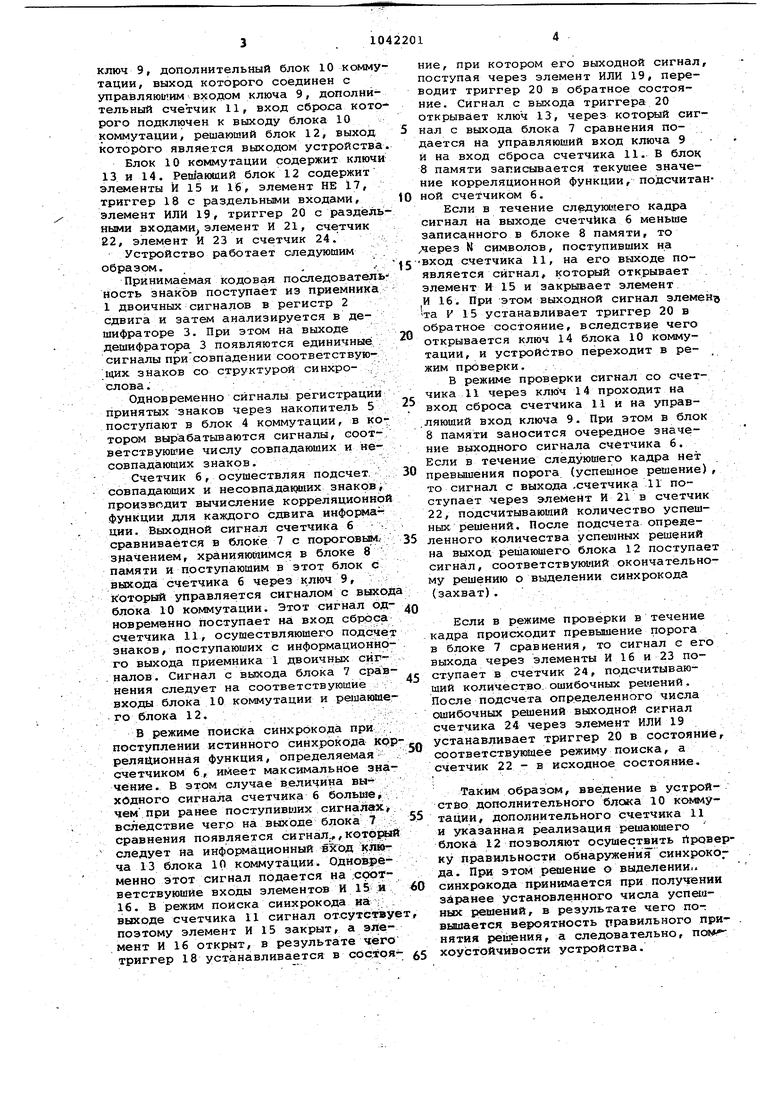

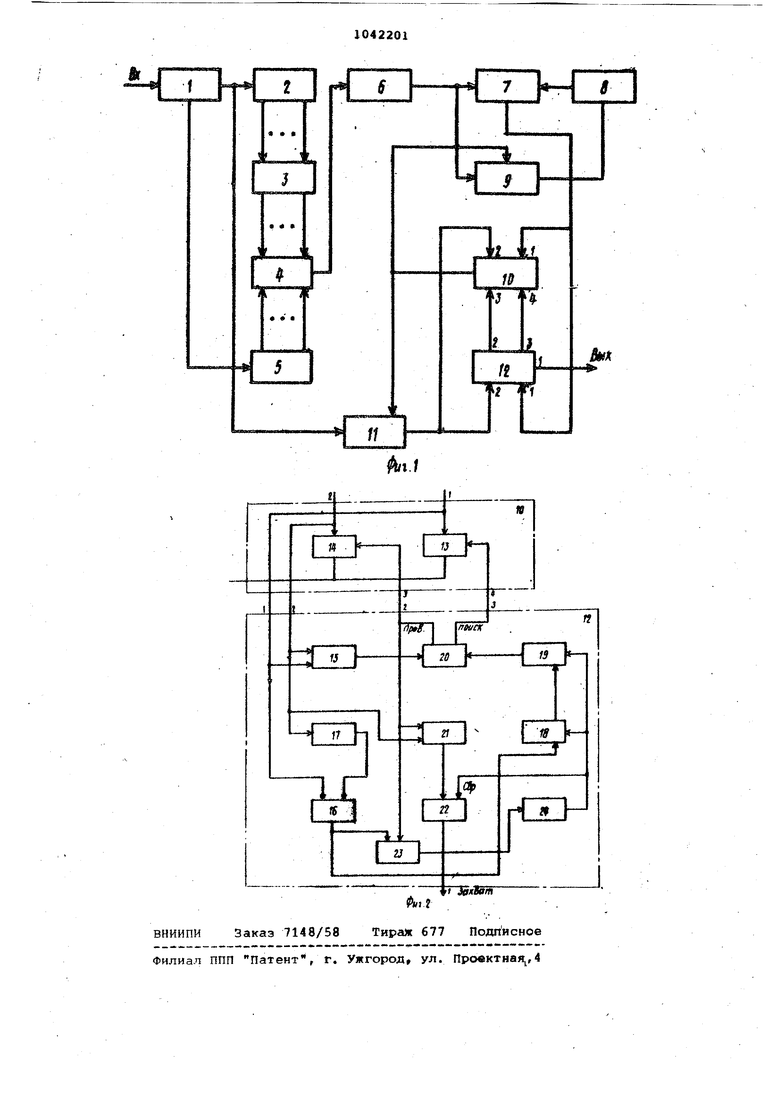

Иэрбретение относится к технике электросвязи и может использоваться при цикловой синхронизации в систе;мах передачи дискретной инфор 1ации, использующих маркерные синхрослова (синхрокод). Известно ухг-ройство приема сигна лов синхронного запуска, содержащее последовательно соединенные приемни с блоком обработки сигналов и накопитель, а также селектор синхросигн лов, -к одному из входов которого подключен счетчик, регистр сдвига, блок коммутации и блок управления, при этом выход блока обработки сигнала подключен непосредственно и через регистр сдвига к соответствую щим входам блока управления, выходы которого подключены к соответствующим входам счетчика, а выходы раз. рядов регистра сдвига подключены к управлякэдим входам блока коммутации включенного между выходами накопите и в-ходами селектора синхросигналов , Однако данное устройство не обла дает достаточной помехоустойчивость .так как имеет фиксированный порог принятия решении .о выделении синхро слова, вследствие чего при изменении соотношения сигнал/шум происходит . уменьшение вероятности правильного обнаружения синхрокода, а следовательно, снижение помехоустойчивости устройства. Наиболее близким к предлагаемому является устройство синхронизации по циклам, содержашее приемник двоичных сигналов, сигнальный выход которого через накопитель подключен к одному из входов блока коммутации а также дешифратор, регистр сдвига, формирователь отношений сигнал/шум и решающий блок, к входам которого подключены два канала обработки сигнала, каждый из которых состоит из последовательно соединенных ключа, блока памяти и блока сравнения, причем к входу одного канала обработки сигнала подключен выход счетчика, а к входу другого канала обработки сигнала - соответствующие выходы накопителя через формирователь отношений сигнал/шум, выход решающего блока подключен к управляющим входам ключей обоих каналов обработки сигнала, а информационный выход приемника сигналов через после довательно соединенные регистр сдвига и дешифратор подключен к другим входам блока коммутации, выход которого подключен к выходу счетчика 2 Это устройство также не обладает достаточной помехоустойчивостью, так как в нем не осуществляется пров.ерка правильности обнаружения максимума корреляционной функции, который должен соответствовать положению истин-, ного синхрослова. Цель изобретения - повьшение помехоустойчивости. Для достижения цели в устройство синхронизации по циклам, содержашее последовательно соединенные приемник двоичных сигналов, регистр, сдвига, дешифратор, блок коммутации, к другим входам которого подключен другой выход приемника двоичных сигналов 1через накопитель, и счетчик, выход которого подключен непосредственно и через последовательно соединенные ключи и блок памяти к входам блока сравнения, выход которого подключен к первому входу решающего блока, введены дополнительный блок коммутации и дополнительный счетчик, при STQM первый и второй входы решающего блока объединены с соответствующи1|1И входами дополнительного блока коммутации, к двум другим входам которого подключены соответственно выходы решающего блока, а выход дополнительного блока коммутации подключен к другому входу ключа и к первому входу дополнительного счетчика, к второму входу которого подключен соответствующий выход приемника двоичных сигналов, а выход дополнительного счетчика подключен к второму входу решающего блока. Решающий блок содержит последовательно соединенные элемент НЕ, вход которого объединен с первыми, входами первого и второго элементов И, третий элемент И, другой вход которого объединен с вторым входом первого элемента И, первый триггер, элемент ИЛИ и второй триггер, к другому входу которого подключен выход первого элемента И, первый выход второго триггера через второй второй элемент И подключен к первому входу первого счетчика, а через последовательно соединенные четвертый элемент И, к другому входу которого подключен выход третьего элемента И, и второй счетчик - к соответствующим входам первого счетчика, первого триггера и элемента ИЛИ, причем первый и в;горой входы первого эл,емента И являются входами, а первый и второй вьйсоды второго триггера и выход первого счетчика являютсн выходами решакявего блока. На фиг. 1 изображена структурная электрическая схема устройства синхронизации по циклам; ма фиг. 2 - структурные электрические схет.1Ы блока KONJмутации и решающего блока. Устройство синхронизации содержит приемник 1 двоичных сигналов, вход , которого является входом устройства, регистр 2 сдвига, дешифратор 3, блок 4 коммутации, накопитель 5, счетчик 6, блок 7 сравнения, блок 8 памяти. ключ 9, дополнительный блок 10 комму тации, выход которого соединен с управляюшим входом ключа 9, дополнительный счетчик 11, вход сброса кото рого подключен к выходу блока 10 коммутации, решающий блок 12, выход которого является выходом устройства Блок 10 коммутации содержит ключи 13 и 14. Рептаюший блок 12 содержит элементы И 15 и 16, элемент НЕ 17, триггер 18 с раздельными входами, элемент ИЛИ 19, триггер 20 с раздель ными в ходами, элемент И 21, счетчик 22, элемент И 23 и счетчик 24. Устройство работает следующим образом., .. Принимаемая кодовая последователь ность знаков поступает из приемника 1 двоичных сигналов в регистр 2 сдвига и затем анализируется в дешифраторе 3. При этом на выходе дешифратора 3 появляются единичные сигналы присовпадении соответствуюЧцих знаков со структурой синхрослова. : Одновременно сигналы регистрации принятых знаков через накопитель 5 поступают в блок 4 коммутации, в котором вырабатываются сигналы, соответствующие числу совпадающих и несовпадающих знаков. Счетчик б, осуществляя подсчет совпадающих и несовпадавших знаков, производит вычисление корреляционной функции для каждого сдвига информации. Выходной сигнал счетчика 6 сравнивается в блоке 7 с пороговьпл. значением, хранияюйимся в блоке 8 памяти и поступающим в это- блок с выхода счетчика б через ключ 9, который управляется сигналом с выход блока 10 коммутации. Этот сигнал одновремвнно поступает на вход сброса счетчика 11, осуществляющего подсчет знаков, поступающих с информационного выхода приемника 1 двоичных сиг. налов. Сигнал с выхода блока 7 срав нения следует на соответствующие входы блока 10 коммутации и решаюше го блока 12. В режиме поиска синхрокода при поступлений истинного синхрокора реляЦионная функция, определяемая счетчиком 6, имеет максимальное значение. В этом случае величина выходного сигнала счетчика 6 больше, чем при ранее поступивших сигналах, вследствие чего на вьвсоде блока 7 сравнения появляется сигнал.,,которз1й следует на информационный вход ключа 13 блока 10 коммутации. Одновременно этот сигнал подается на соответствующие входы элементов И 15 и 16. В режим поиска синхрокода на выходе счетчика 11 сигнал отсутствуе поэтому элемент И 15 закрыт, а эле мент И 16 открыт, в результате чего триггер 18 устанавливается в сосягряние, при котором его выходной сигнал, поступая через элемент ИЛИ 19, переводит триггер 20 в обратное состояние. Сигнал с выхода триггера 20 открывает ключ 13, через который сигнал с выхода блока 7 сравнения подается на управляющий вход ключа 9 и на вход сброса счетчика 11. В блок 8 памяти записывается текущее значение корреляционной функции, подсчитанной счетчиком 6. Если в течение следующего кадра сигнал на выходе счетчИка 6 меньше записанного в блоке 8 памяти, то через N символов, поступивших на вход счетчика 11, на его выходе появляется сигнал, который открывает элемент И 15 и закрывает элемент |И 16. При этом выходной сигнал элемен та И 15 устанавливает триггер 20 в обратное состояние, вследствие чего открывается ключ 14 блока 10 коммутации, и устройство переходит в режим проверки. . В режиме проверки сигнал со счетчика 11 через ключ 14 проходит на вход сброса счетчика 11 и на управляющий вход ключа 9. При этом в блок 8 памяти заносится очередное значение выходного сигнала счетчика 6. Если в течение следующего кадра нет превышения порога (успешное решение), то сигнал с выхода .счетчика 11 поступает через элемент И 21 в счетчик 22, подсчитывающий количество успешных решений. После под;счета определенного количества успешных решений на выход решающего блока 12 поступает сигнал, соответствукичий окончательному решению о выделении синхрокода (захват). Если в режиме проверки в течение кадра происходит превьшение порога в блоке 7 сравнения, то сигнал с его выхода через элементы И 16 и 23 поступает в счетчик 24, подсчитывающий количество, ошибочных решений. После подсчета определенного числа ошибочных решений выходной сигнал счетчика 24 через элемент ИЛИ 19 устанавливает триггер 20 в состояние, соответствующее режиму поиска, а счетчик 22 - в исходное состояние. Таким образом, введение в устройСтйо дополнительного блока 10 коммутации, доп олни тель ног о сче тчик а 11 и указанная реализация решающего блок а 12 по3 воляют осуше ствить rtров ерку правильности оВнаружения синхрокода. При этом решение о выделении,, синхрокода принимается при получении заранее установленного числа ycneiaных решений, в результате чего поввааается вероятность правильного принятия решения, а следовательно, пом хоустойчивости устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Телемеханическая система | 1987 |

|

SU1424044A1 |

| Устройство передачи и приема сигнала изображения | 1986 |

|

SU1438020A1 |

| Устройство цикловой синхронизации | 1988 |

|

SU1566500A1 |

| Система для передачи и приема информации | 1988 |

|

SU1583953A1 |

| Устройство цикловой синхронизации | 1989 |

|

SU1626431A1 |

| Система цикловой синхронизации для многоканальных систем связи | 1988 |

|

SU1598193A1 |

| Устройство для выделения маркера кадровой синхронизации | 1978 |

|

SU752313A1 |

| Устройство для приема самосинхронизирующейся дискретной информации | 1982 |

|

SU1080252A2 |

| Устройство для мажоритарного декодирования в целом | 1989 |

|

SU1688415A1 |

| Устройство для передачи и приема многочастотных многопозиционных сигналов | 1988 |

|

SU1578835A1 |

1. УСТРОЙСТВО СИНХРОНИЗАЦИИ ПО ЦИКЛАМ, содержащее последовательно соединенные приемник двоичных сигналов, регистр сдвига, дешифратор, блок коммутации, к другим входам которого подключен другой выход приемника двоичных сигналов через накопитель, и счетчик, выход которого подключен непосредственно и через последовательно соединенные ключ и памяти к входам блока сравйения, выход которого подключен к первому входу решающего блока, о Y л и ч а ю ш е е с я тем, что, с целью повышения помехоустойчивости, в него введены дополнительный блок коммутации и дополнительный счетчик, при этом первый и второй входы ремаюшего блока объединены с соответствуюними входами дополнительного блока коммутации, к двур другим входам которого подключены соответствуюшие ъыхазщ р ешаюшего блока, а выход дополнитёйЬ ного блока коммутации подключен к другому входу ключа и к первому входу дополнительного счетчика, к второму входу которого подключен соответствующий выход приемника двоичных сигналов, а выход дополнительного счетчиТ а подключен к второму входу решающего блока. 2. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что решаюиий ,блок содержит последовательно соединенные элемент НЕ, вход которого объединен с первыми входами первого и второго элементов И, третий элемент И, другой вход которого объединен с вторым входом первого элемента И, первый.триггер, элемент ИЛИ и второй триггер, к другому вхо(П ду которого подключен выход первого элемента И, первый выход второго триггера через второй элемент и подключён к первому входу первого счетчика, а через последовательно соединенные четвертый элемент И, к другому входу которого подключен выход третьего элемента И, и второй счето чик - к соответствующим входам первого счетчика, первого триггера и эле4 мента ИЛИt причем первый и второй to Nd входы первого элемента И являются входами, а первый и втррой выходы -JBToporo триггера и выход первого счето чика являются выходами рёшакятегб блока.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство приема сигналов синхронного запуска | 1973 |

|

SU543183A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство синхронизации по циклам | 1977 |

|

SU657643A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-09-15—Публикация

1982-03-03—Подача