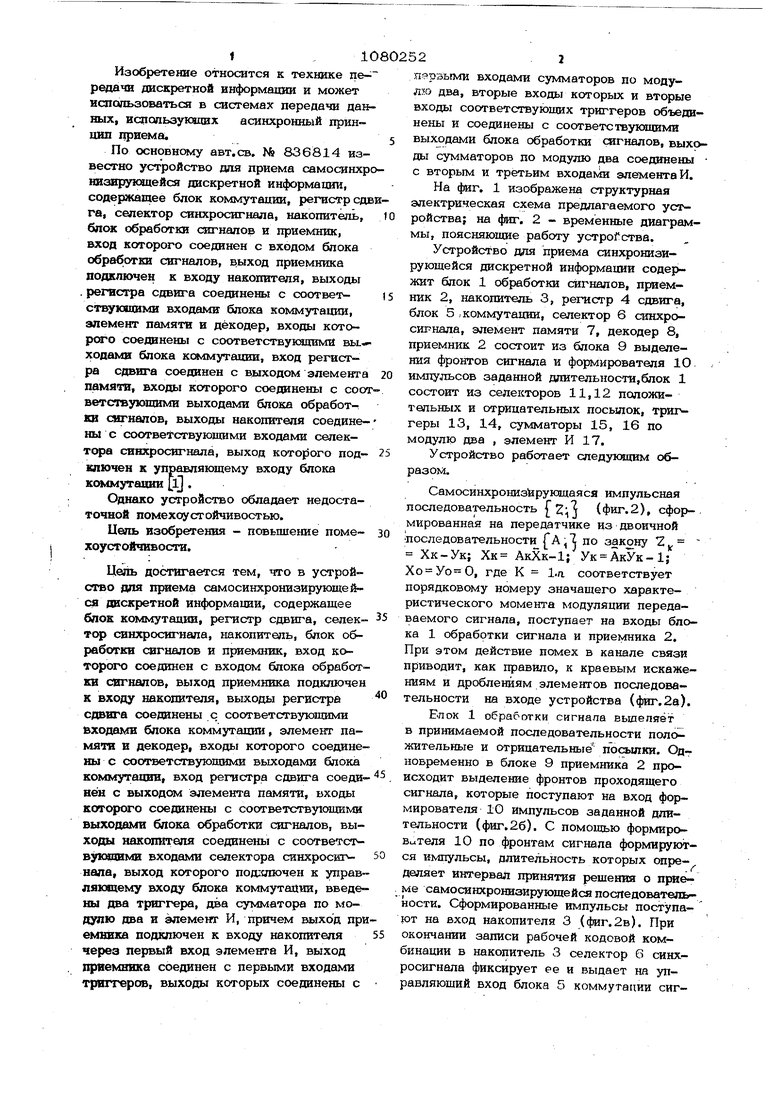

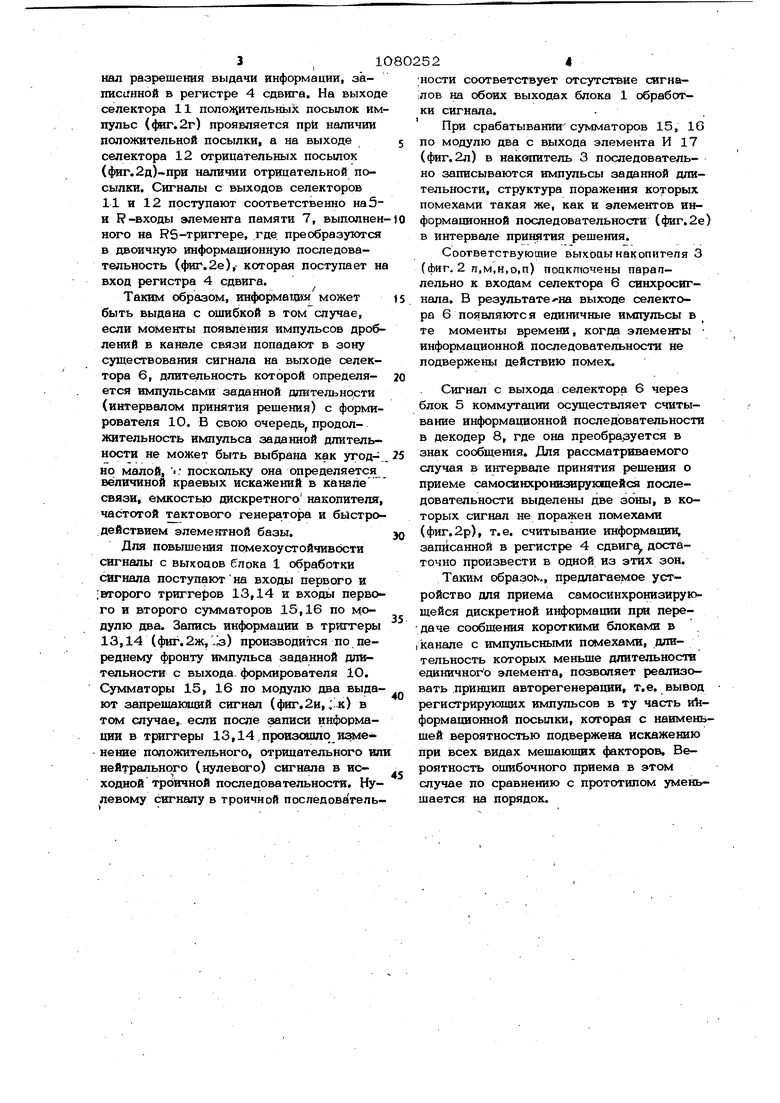

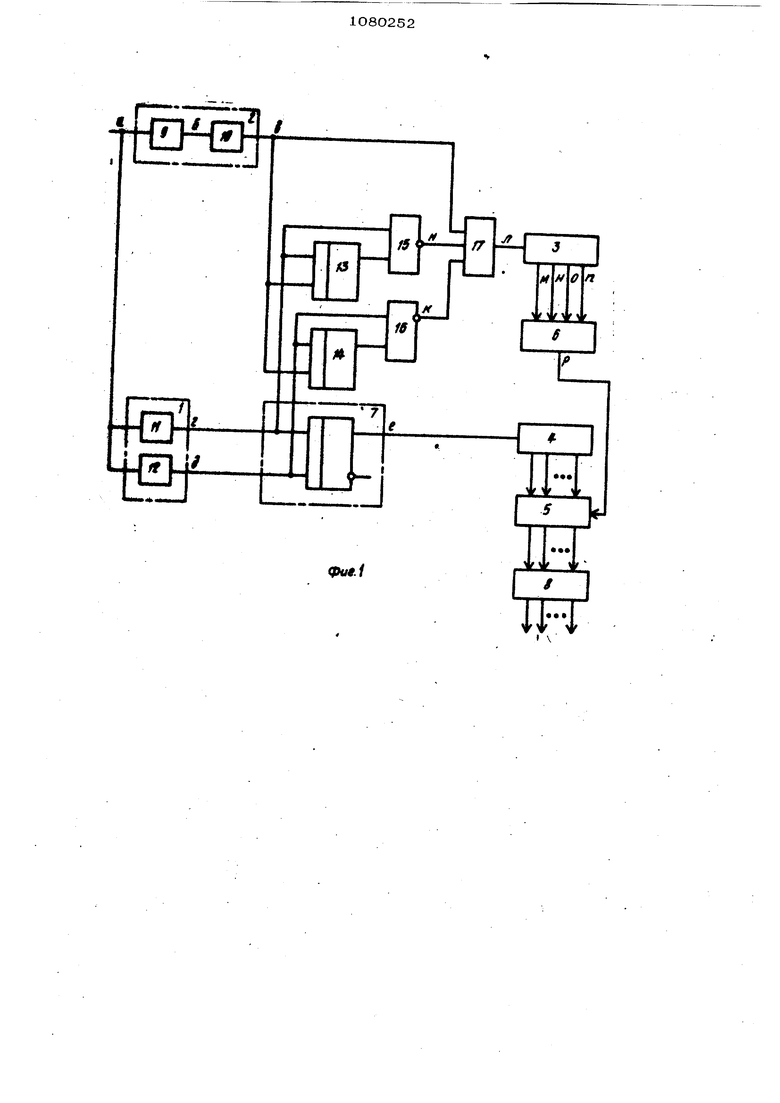

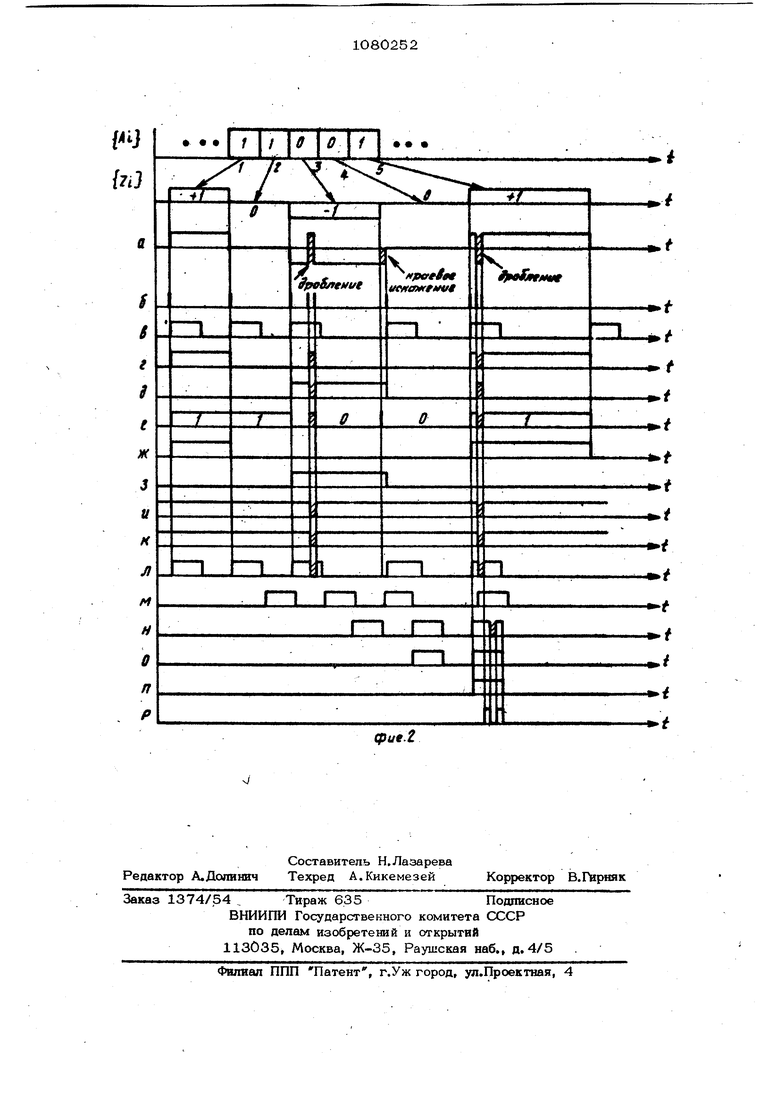

Изобретение относятся к технике передачи дискретной информашш и может использоваться в системах передачи дан ных, нспопьзующих асинхронный принцип приема. По основнхжлу авт.св. № 836814 известно устройство для приема самосинхр шзирукхцейся дискретной информации, содержащее блок коммутации, регистр сдв га, селектор синхросигнала, накопитель, блок обработки сигналов и приемник, вход которого соединен с входом блока обработки сигналов, выход приемника подключен к входу накопителя, выходы . регистра сдвига соединены с соответ ствуюцими входами блока коммутации, элемент памяти и декодер, входы которого соединены с соответствуквдимИ вьь ходами блока кс 4мутации, вход регистра сдвига соединен с выходом элемента памяти, входы которого соединены с соот ветствующими выходами блока обработ-г ки сигналов, выходы накопителя соединены с соответствующими входами селектс а синхросигнала, выход которого подключей к управляющему входу блока коммутации Щ Однако устройство обладает недостаточной помехоустойчивостью. Цепь изобретения - повышение помехоустойчивости. Цель достигается тем, что в устройство для приема самосинхронизирующейся дискретной информации, содержащее блок коммутации, регистр сдвига, селектор синхросигнала, накопитель, блок обработки сигналов и приемник, вход которого соединен с входом блока обработ ки сигналов, выход приемника подключен К ВХОДУ накопителя, выходы регистра сдвига соединены с соответствующими входами блока коммутации, элемент памяти и декодер, входы которого соедине ны с соответствующими выходами блока коммутации, вход регистра сдвига соеди нён с выходом элемента памяти, входы которого соединены с соответствующими выходами блока обработки сигналов, выходы иакопитепя соединены с соответствуюошмн входами селектора синхросигиала, выход которого под;шючен к управ ляющему входу блока коммутации, введе ны два триггера, два сумматора по модулю два и элемент И, причем выход пр емника подключен к входу накопителя через первый вход элемента И, выход приемника соединен с первыми входами триггеров, выходы которых соединены с перзь ми входами сумматоров по модулю два, вторые входы которых и вторые входы соответствующих триггеров объединены и соединены с соответствующими выходами блока обработки сигналов, выходы сумматоров по модулю два соединены с вторым и третьим входами элемента И. На фиг. 1 изображена структурная электрическая схема предлагаемого устройства; на фиг. 2 - временные диаграммы, поясняюЕПне работу устройства. Устройство для приема синхронизирующейся дискретной информации содержит блок 1 обработки сигналов, приёмник 2, накопитель 3, регистр 4 сдвига, блок 5 , коммутации, селектор 6 синхросигнала, элемент памяти 7, декодер 8, приемник 2 состоит из блока 9 выделения фронтов сигнала и формирователя 10 импульсов заданной дга1тельности,блок 1 состоит из селекторов 11,12 положительных и отрицательных посылок, триггеры 13, 14, сумматоры 15, 16 по модулю два , элемент И 17. Устройство работает следующим образом. Самосинхронизйрующаяся импульсная последовательность f Z {фиг.2), сфор-, мированная на передатчике из двоичной последовательности А, 1, по закону 2 Хк-Ук; Хк АкХк-1; Ук АкУк-1; Хо , где К 1.Л соответствует порядковому номеру значащего характеристического момента модуляции передаваемого сигнала, поступает на входы блока 1 обработки сигнала и приемника 2. При этом действие помех в канале связи приводит, как правило, к краевым искажениям и дроблениям элементов последовательности на входе устройства (фиг.2а). Блок 1 обработки сигнала вьщеляёт в принимаемой последовательности пол жительные и отрицательные посылки. Одновременно в блоке 9 приемника 2 происходит выделение фронтов проходящего сигнала, которые поступают на вход формирователя 10 Импульсов заданной длительности (фиг.26). С помощью формироВытеля 10 по фронтам сигнала формируются импульсы, длительность которых определяет интервал принятия решения о приеме самосинхронизирующейся последовательности. Сформированные импульсы поступают на вход накопителя 3 (фиг.2в). При окончании записи рабочей кодовой комбинации в накопитель 3 селектор 6 синхросигнала фиксирует ее и выдает на управляющий вход блока 5 коммутации сигнал разрешения выдачи информации, записанной в регистре 4 сдвига. На выход селектора 11 поло 4итепьнь1х посьшок им пульс (41ИГ.2г) проявляется при наличии положительной посылки, а на выходе селектора 12 отрицательных посылок (фиг.2д)-при наличии отрвдательной посылки. Сигналы с выходов селекторов 11 и 12 поступают соответственно на5и R-входы элемента памяти 7, выполнен ного на Н5-триггере, где преобразуются Б двоичную информационную последовательность (фиг.2е), которая поступает н вход регистра 4 сдвига. Таким образом, информачвм может быть выдана с ошибкой в том случае, если моменты появления импульсов дроблений в канале связи попадают в зону существования сигнала на выходе селектора 6, длительность которой определяется импульсами заданной длительности (интервалом принятия решения) с формирователя 10. В свою очередь, продолжительность импульса заданной длительности не может быть выбрана как угодно малой, «. поскольку она определяется величиной краевых искажений в К1знапе связи, емкостью дискретного накопителя, частотой тактового генератора и быстродействием элементной базы. Для повыше шя помехоустойчивсюти сигналы с выходов блока 1 обработки сигнала поступаютна входы первого и .второго триггеров 13,14 и входы первого и второго сумматоров 15,16 по модулю два. Запись информации в триггеры 13,14 (фиг.2ж,.is) производи1х;я по переднему фронту импульса заданной длительности с выхода, формирователя 10. Сумматоры 15, 16 по модулю два вы дают запрещающий сигнал (фиг.2и, -к) в том случае, если после записи информации в триггеры 13,14 .произошло изменение положительного, отрицательного ил нейтрального (нулевого) сигнала в исходной трб1агчной последовательности. Нулевому сигналу в троичной последователь;ности соответствует отсутствие сигналов на обоих выходах блока 1 обработки сигнала.. При срабатывании сумматоров 15, 10 по модулю два с выхода элемента И 17 (фиг.2л) в накопитель 3 последовательно записываются импульсы заданной длительности, структура поражения которых помехами такая же, как и элементов информационной последовательности (фиг.2е) в интервале принятия решения. Соответствующие выхоаы накопителя 3 (фиг. 2 л,м,н,о,п) поцключены параллельно к входам селектора 6 синхросигнала. В результатеНа выходе селектора 6 появляютс я единичные импульсы в те моменты времени, когда элементы информационной последовательности не подвержены действию помех. Сигнал с выхода; селектора 6 через блок 5 коммутации осуществляет считывание информационной последовательности в декодер 8, где она преобразуется в знак сообщения. Для рассматриваемого случая в интервале принятия решения о приеме самосянхронизирующейся последовательности выделены две зоны, в которых сигнал не поражен помехами (фиг.2р), т.е. считывание информации, записанной в регистре 4 сдвигеу достаточно произвести в одной из этих зон. Таким o6pa30NM предлагаемое устройство для приема самосинхронизирующейся дискретной информации при передаче сообщения короткими блоками в канале с импульсными помехами, длительность которых меньше длительности единичног о элемента, позволяет реализовать принцип авторегенерашга, т.е. вывод регистрирующих импульсов в ту часть vAs.формационной посьтки, которая с наименьшей вероятностью подвержена искажению при всех видах мешающих факторов. Вероятность ошибочного приема в этом случае по сравнению с прототипом уменьшается на порядок.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема самосинхронизирующейся дискретной информации | 1982 |

|

SU1030989A2 |

| Устройство для приема самосинхронизирую-щЕйСя диСКРЕТНОй иНфОРМАции | 1979 |

|

SU836814A1 |

| Устройство для приема самосинхронизирующейся дискретной информации | 1984 |

|

SU1228296A2 |

| Устройство для приема самосинхронизирующейся дискретной информации | 1980 |

|

SU924902A2 |

| Устройство выделения рекуррентного синхросигнала с исправлением ошибок | 1976 |

|

SU582578A1 |

| ДЕКОДЕР ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА КОДА RZ | 2005 |

|

RU2291560C1 |

| Устройство для передачи и приема цифровых сигналов | 1988 |

|

SU1566499A1 |

| Адаптивное устройство для обработки избыточной информации | 1982 |

|

SU1062752A1 |

| Некогерентный приемник | 1988 |

|

SU1525933A1 |

| ПРИЕМНО-ПЕРЕДАЮЩЕЕ УСТРОЙСТВО ДИСКРЕТНЫХ СИГНАЛОВ | 1990 |

|

RU2123761C1 |

УСТРОЙСТВО ДЛЯ ПРИЕМА САМОа1НХРОНИЗИРУЮШЕЙСЯ ДИСКРЕТНОЙ ИНФОРМАЦИИ по авт.св. № 836814, отличающееся тем, что, с целью повшаения помехоустойчивости, введены два триггера, два сумматора Ш) модулю два и алемент И,_причем выход приемника подключен к вхсяу накопителя через первый вход элемента И, выход приемника соединен с первыми входами триггеров, выходы которых средине-* ны с первыми входами сумматоров по модулю два, вто1ше входы ксаарьа. и вторые входы соответствующих триггеров объединены и соединены с соответсх^ вующими выходами блока обработки сигналов, выходы сумматоров по модулю два . соединены с втсфым и третьим входами элемента И,(О

/7

f5

J и L L5

16

6

t

Ф(/«/

G

{4iJ {7iJ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-03-15—Публикация

1982-12-20—Подача