ел

05 О

сл

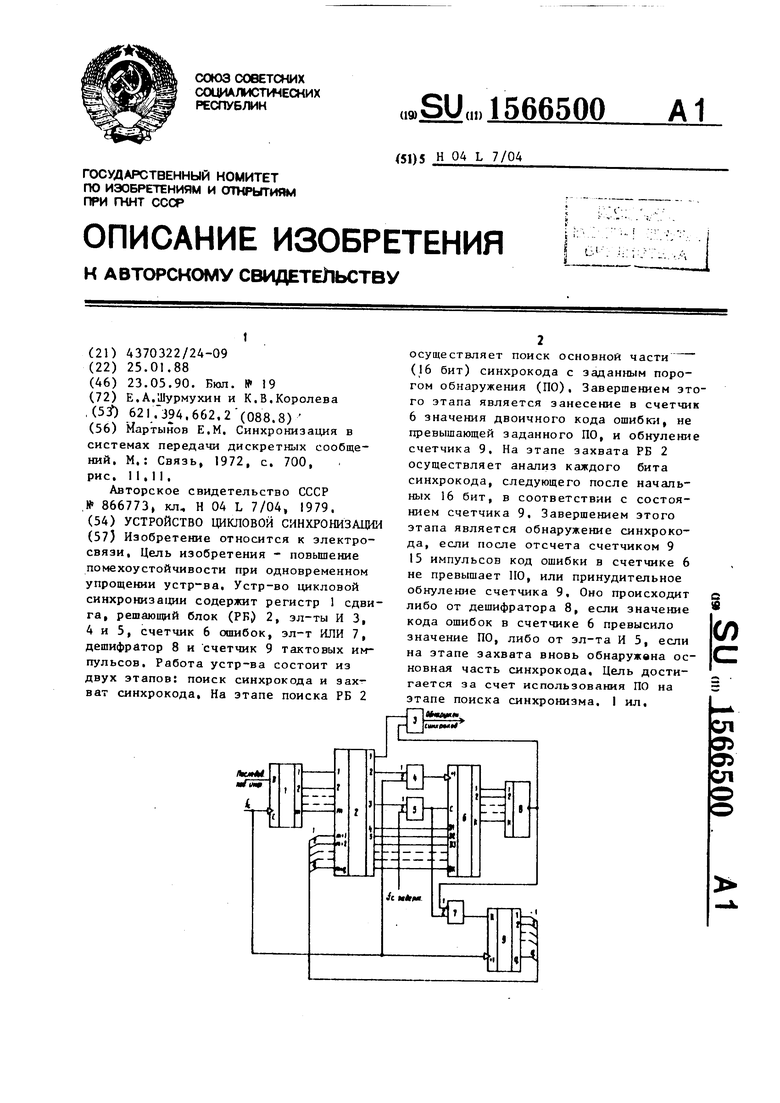

Изобретение относится к электросвязи и может быть использовано для помехоустойчивого выделения сигналов цикловой синхронизации в системах передачи дискретной информации.

Цель изобретения - повышение помехоустойчивости при одновременном упрощении устройства.

Устройство содержит регистр 1 сдвига, решающий блок 2, элементы И 3-5, счетчик 6 ошибок, элемент ИЛИ 7, дешифратор 8 и счетчик 9 тактовых импульсов.

Устройство работает следующим образом.

Двоичные информационные посылки, получаемые из канала связи, поступают на вход регистра 1 сдвига. Параллельные выходы всех разрядов регистра 1 соединены с входами решающего блока 2, Циклический синхрокод, который должно обнаруживать устройство, содержит п бит, из которых m начальных бит составляют его основную часть. Решающий блок 2 производит анализ каждой m-разрядной комбинации, возникающей на выходах регистра 1,

Решающий блок 2 представляет собой постоянное запоминающее устройство, которое выполняет функцию сравнения кода, поступающего на его адресные входы с эталонным кодом синхропосле- довательности за счет соответствующего программирования. При этом задается порог обнаружения синхрокода, т.е. допустимое число бит принимаемого синхрокода, которое может не совпадать с эталоном.

0

5

0

5

гает на один шаг анализируемую последовательность и устанавливает счетчик 9 в состояние I. Решающий блок 2 анализирует поступивший в регистр 1 (т+1)-й разряд синхрокода и состояние выходов счетчика 9. При наличии ошибки в (тг,+ 1)-м разряде синхрокода на втором выходе решающего блока 2 появляется сигнал очередной ошибки кода, который тактируется на элементе И 4 импульсом сдвига и поступает на счетный вход счетчика 6 ошибок. Когда код ошибки в счетчике 6 превышает допустимое значение, дешифратор 8 вырабатывает сигнал фазировки счетчика 9, который через элемент ИЛИ 7 поступает на R-вход счетчика 9 и устанавливает его в нулевое состояние. В этом случае повторяется описанный цикл поиска синхрокода, Если в течение n-m тактов сдвига после первой фазировки счетчика 9 значение ошибки синхрокода, формируемое счетчиком 6, не превышает допустимого значения, то на первом выходе решающего блока 2 формируется сигнал обнаружения синхрокода, который поступает на элемент И 3, На второй вход элемента И 3 с дешифратора 8 поступает сигнал отсутствия ошибки синхрокода. На выходе элемента И 3 формируется сигнал конца синхрокода.

Для примера рассмотрим циклический синхрокод 111110001101110 1010000100101100, в котором каждый последующий бит, начиная с 6, обра-.

зован по закону а

ап ©а,-.,

где

знак 6) означает сложение по mod 2,

а первые пять бит задаются при-кодиро

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство передачи и приема сигнала изображения | 1986 |

|

SU1438020A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ ДЛЯ СИГНАЛОВ С СОСРЕДОТОЧЕННОЙ ИЛИ РАСПРЕДЕЛЕННОЙ ПО ЦИКЛУ СИНХРОГРУППОЙ | 2021 |

|

RU2780048C1 |

| УСТРОЙСТВО ПРИЕМА ИНФОРМАЦИИ ИЗ КАНАЛА | 1998 |

|

RU2137320C1 |

| АДАПТИВНЫЙ СПОСОБ ОБНАРУЖЕНИЯ И РАСПОЗНАВАНИЯ СИНХРОСИГНАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2002 |

|

RU2238612C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| Устройство для обнаружения и регистрации ошибок дискретного канала передачи и накопления информации | 1988 |

|

SU1567078A1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

Изобретение относится к электросвязи. Цель изобретения - повышение помехоустойчивости при одновременном упрощении устройства. Устройство цикловой синхронизации содержит регистр 1 сдвига, решающий блок /РБ/ 2, эл-ты И 3,4 и 5, счетчик 6 ошибок, эл-т ИЛИ 7, дешифратор 8 и счетчик 9 тактовых импульсов. Работа устройства состоит из двух этапов: поиск синхрокода и захват синхрокода. На этапе поиска РБ 2 осуществляет поиск основной части /16 бит/ синхрокода с заданным порогом обнаружения /ПО/. Завершением этого этапа является занесение в счетчик 6 значения двоичного кода ошибки, не превышающей заданного ПО, и обнуление счетчика 9. На этапе захвата РБ 2 осуществляет анализ каждого бита синхрокода, следующего после начальных 16 бит, в соответствии с состоянием счетчика 9. Завершением этого этапа является обнаружение синхрокода, если после отсчета счетчиком 9 15 импульсов код ошибки в счетчике 6 не превышает ПО, или принудительное обнуление счетчика 9. Оно происходит либо от дешифратора 8, если значение кода ошибок в счетчике 6 превысило значение ПО, либо от эл-та И 5, если на этапе захвата вновь обнаружена основная часть синхрокода. Цель достигается за счет использования ПО на этапе поиска синхронизма. 1 ил.

Если ошибка в анализируемой синхро

группе не превышает порога обнаружения, на третьем выходе решающего блока 2 появляется сигнал параллельного ввода, который через элемент И5 производит запись в счетчик 6 К-разряд- ного кода ошибки, который формируется на выходах с 4-го по ()-й решающего блока 2. Код ошибки представляет собой двойное значение числа бит анализируемой синхрогруппы, несовпадающее с эталоном. Элемент И 5 тактируется импульсной последовательностью задержанной по отношению к тактам сдвига регистра 1,

Одновременно с записью кода ошибки в счетчик 6 через элемент ИЛИ 7 происходит фазирование счетчика 9 путем установки его в нулевое состояние. Следующий тактовый импульс сдви

5

0

5

Длина синхрокода п составляет 31 бит. Минимальная основная часть этого синхрокода имеет длину 14 бит. При этом каждое последующее кодовое слово, образованное при сдвиге на один такт, отличается от предыдущего на величину ,

первое кодовое слово,

второе кодовое слово (), 1 1 100011011101 - третье кодовое

слово () и т.д.

В этом случае оставшаяся часть синхрокода составляет 17 бит,

Выбирают длину основной части синхрокода , В этом случае оставшаяся часть синхрокода составляет n-m 15 бит. Для пересчета 15 символов

1111 10001101II 1 1 110001101110

необходим четырехразрядный счетчик. Анализ рассматриваемого синхрокода может осуществляться на двух ПЗУ типа 556 РТ6.

Алгоритм работы устройства состоит из двух фаз: фазы поиска синхрокода; фазы захвата синхрокода.

На этапе поиска решающий блок 2 осуществляет поиск основной части синхрокода (16 бит) с заданным порогом обнаружения, Завершением фазы поиска является занесение в счетчик 6 значения двоичного кода ошибки, не превышающей заданного порога, и обнуление счетчика 9 тактовых импульсов.

На этапе захвата решающий блок 2 осуществляет анализ каждого бита синхрокода, следующего после начальных 16 в соответствии с состоянием счетчика 9 тактовых импульсов. Завершением фазы эахвата является обнаружение синхрокодл, если после отсчета счетчиком 9 пятнадцати импульсов код ошибки в счетчике 6 не превышает порога обнаружения, или принудительное обнуление счетчика тактовых импульсов 9, либо от дешифратора 8, если значение кода ошибок в счетчике 6 превысило значение порога обнаружения, либо от элемента И 5, если же на этапе захвата вновь обнаружена основная часть синхрокода. Последнее означает, что ранее обнаружен-,, пне счетчика ошиОок,входы которого сое- ная основная часть синхрокода была об- динены с выходами Код ошибки решаюнаружена ложно. При правильном обнаружении начальной части синхрокода занесение кода в счетчик ошибок не производится.JQ

Таким образом, предложенное устройство обеспечивает повышение помехоустойчивости за счет использования порога обнаружения на этапе поиска синхронизма.

Формула изобретения

Устройство цикловой синхронизации, содержащее счетчик ошибок и три элемента И, причем выход первого элеменQ та И является выходом устройства, выход второго элемента И соединен с входом элемента ИЛИ, выход которого подключен к установочному входу счетчика тактовых импульсов, а первый вход

5 первого элемента И соединен с выходом дешифратора, отличающееся т§м, что, с целью повышения помехоустойчивости при одновременном упрощении устройства, в него введены ре0 гистр сдвига и решающий блок, первая группа входов которого соединена с выходами регистра сдвига, вторая группа входов подключена к выходам счетчика тактовых импульсов, первый

5 выход решающего блока соединен с вторым входом первого элемента И, второй и третий выходы подключены к первым входам соответственно третьего и второго элементов И, вторые входы

0 которых являются соответственно первым и вторым тактовыми входами устройства третье го и второго элементов И, а выходы подключены соответственно к счетному входу и Б ;оду Исходное состоящего блока, а выходы счетчика ошибок подключены к входам дешифратора, выход которого соединен с инверсным входом элемента ИЛИ, счетные входы регистра сдвнгл и счетчика тактовых импульсов соединеШ с вторым входом третьего элемента И11И,

| Мартынов Е.М | |||

| Синхронизация в системах передачи дискретных сообщений, М.: Связь, 1972, с | |||

| Машина для отмеривания теста | 1925 |

|

SU700A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство фазового пуска | 1979 |

|

SU866773A1 |

Авторы

Даты

1990-05-23—Публикация

1988-01-25—Подача