Изобретение относится к вычислительной технике и может быть использовано при проектировании аппаратных средств автоматического контроля цифровых вычислительных устройств

Известен сумматор по модулю три, выполненный на ферродиодных логических элементах ГЛ„

Сумматор имеет большие затраты оборудования и невысокую надежность,/

Известен сумматор по модулю три, выполненный на троичных логических. элементах zj.

Сумматор характеризуется большими затратами оборудования и низким быстродействием

Наиболее близким к предлагаемому является сумматор по модулю три, содержащий троичные логические элементы, причем шина первого слагаемого соединена с первым входом первого троичного логического элемента, к второму входу которого подключена шина второго слагаемого, выход первого троичного логического элемента соединен с первыми входами второго и третьего троичных логических элементов, выходы которых подключены соответственно к первому и второму входам четвертого троичного логического эле мента, выход которого подключен к вы ходной шине сумматора, шина второго слагаемого соединена с третьим входо первого троичного логического элемен та и вторым входом третьего троичного логического элемента, шина первого слагаемого подключена к четвертому входу первого троичного логического элемента, к третьему входу третьего троичного логического элемента и вто рому входу второго троичного логичес кого элемента, третий вход которого подключен к шине второго слагаемого и четвертый вход - к выходу пер, вого троичного логического элемента ji четвертому входу третьего троичного логического элемента, выход которого соединен с третьим входом четвертого троичного логического элемента, четвертый вход которого подключен к выходу второго троичного логического элемента Гз1 Известный сумматор по модулю три имеет низкое быстродействие, так как операция суммирования происходиг за три фазы тактового питания Цель изобретения - повышение быст родействия сумматора путем сокращения числа тактов формирования остатка по модулю.три.

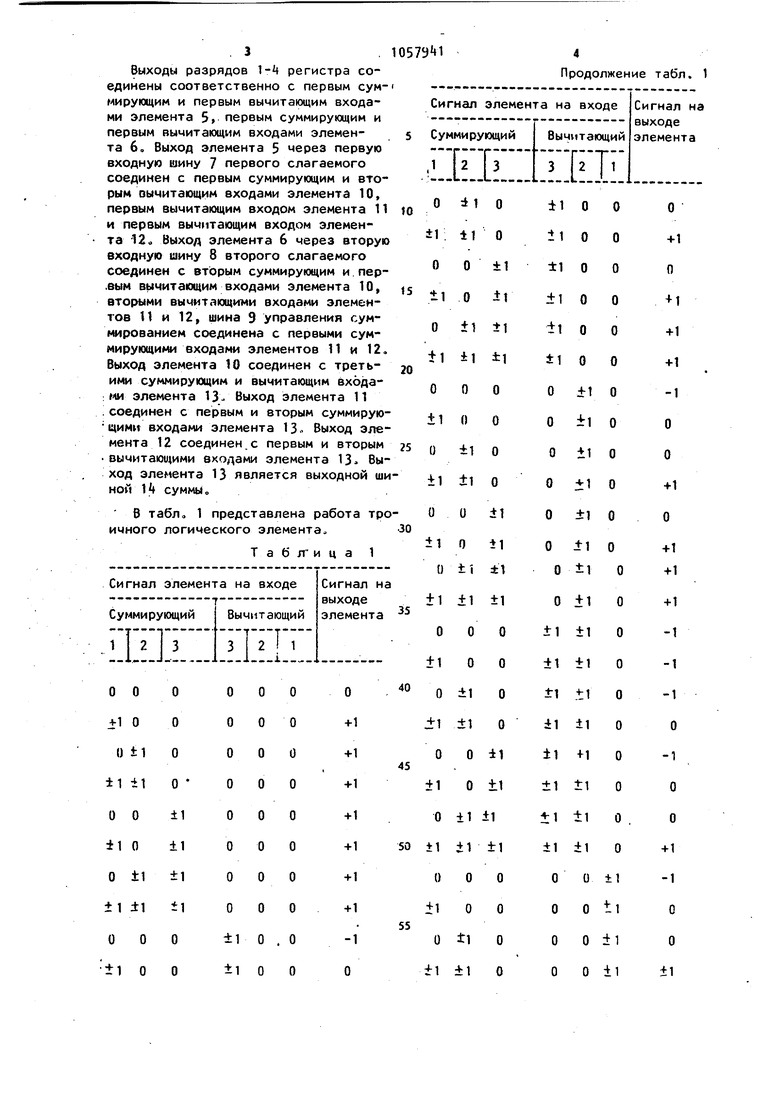

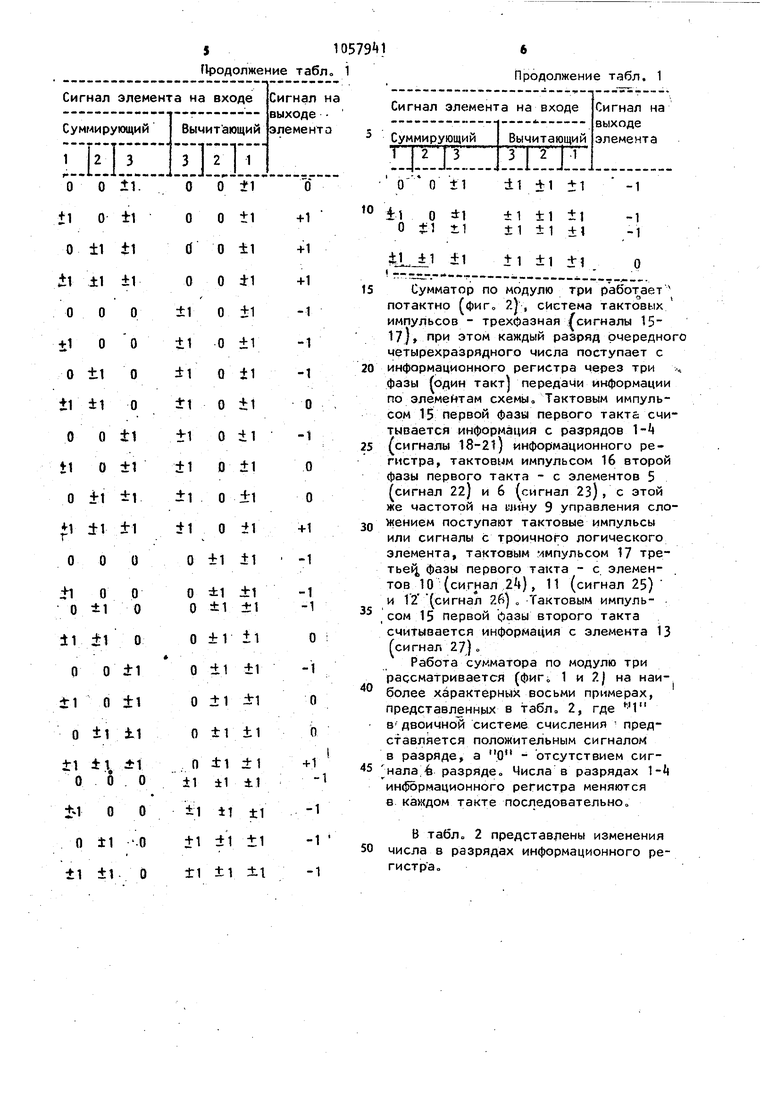

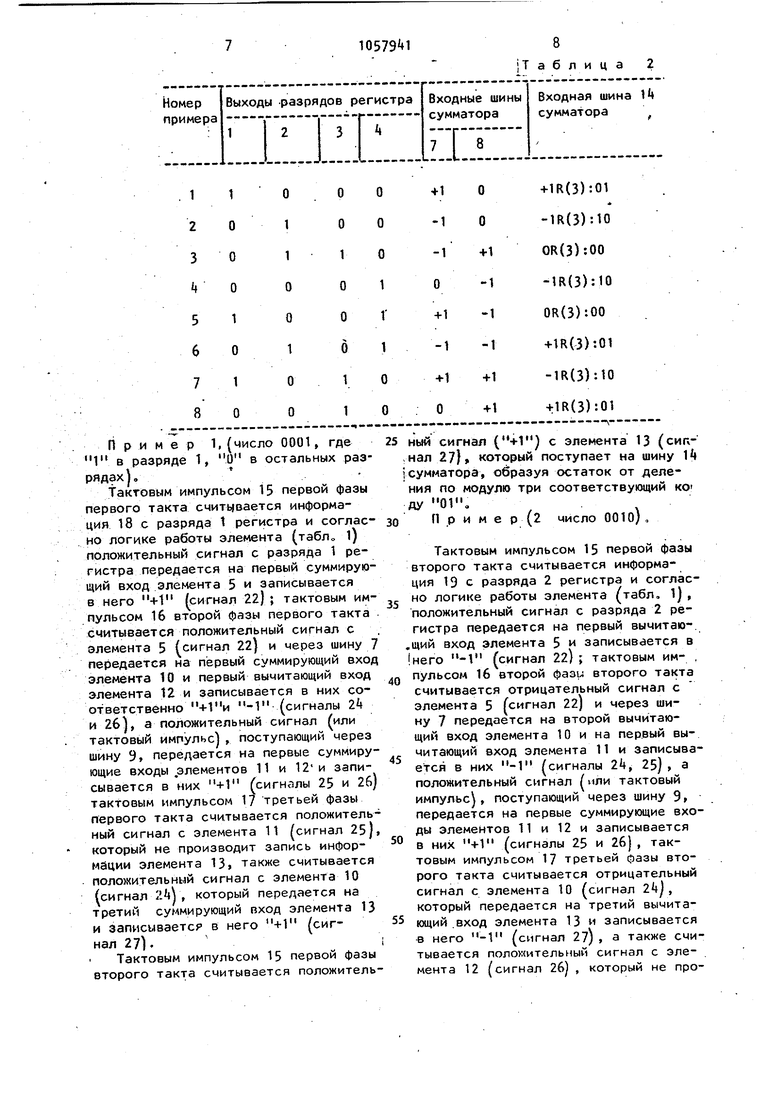

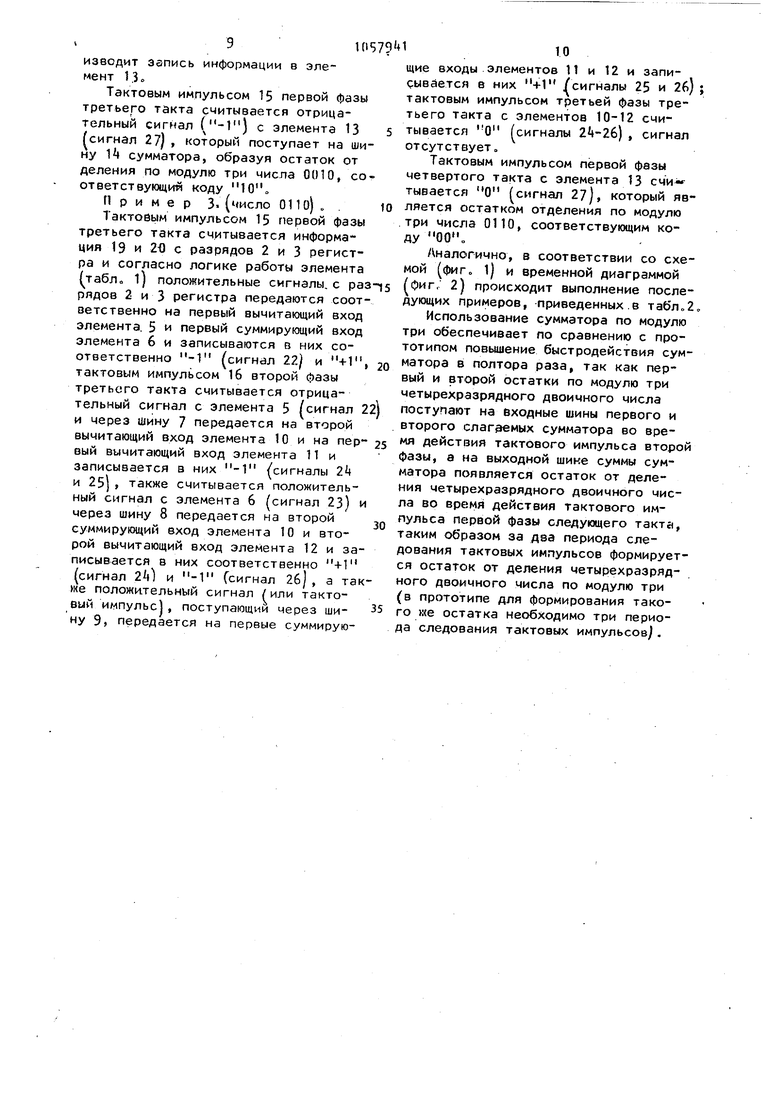

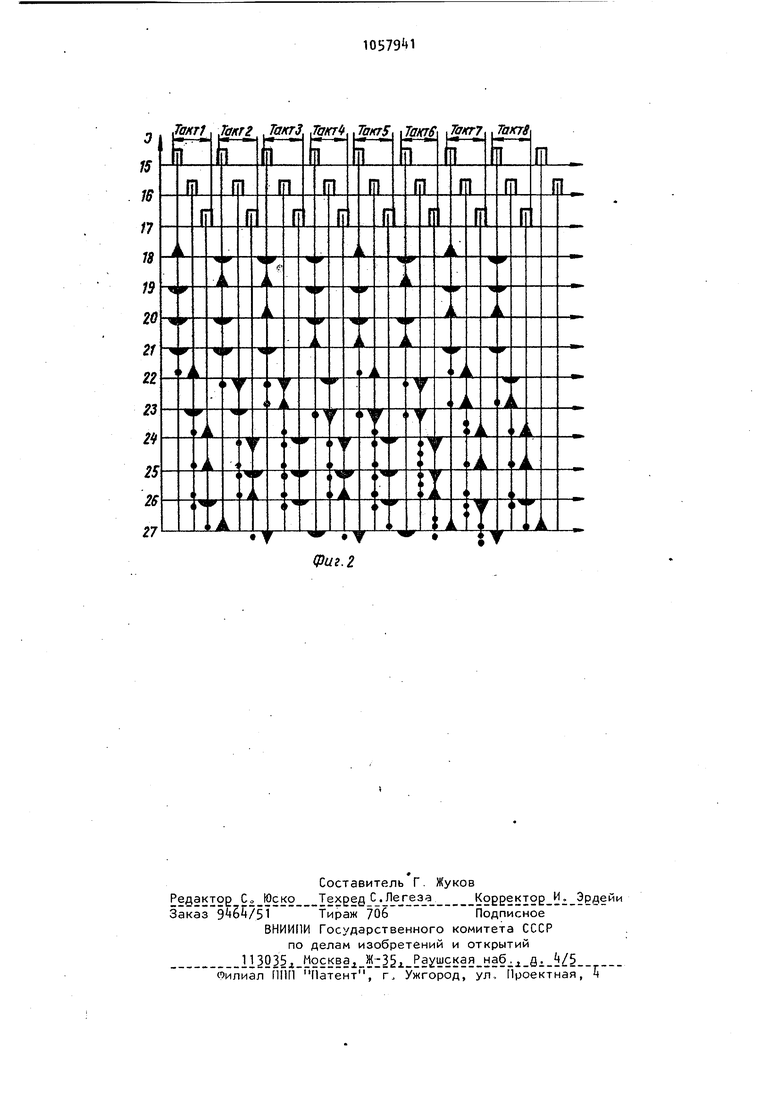

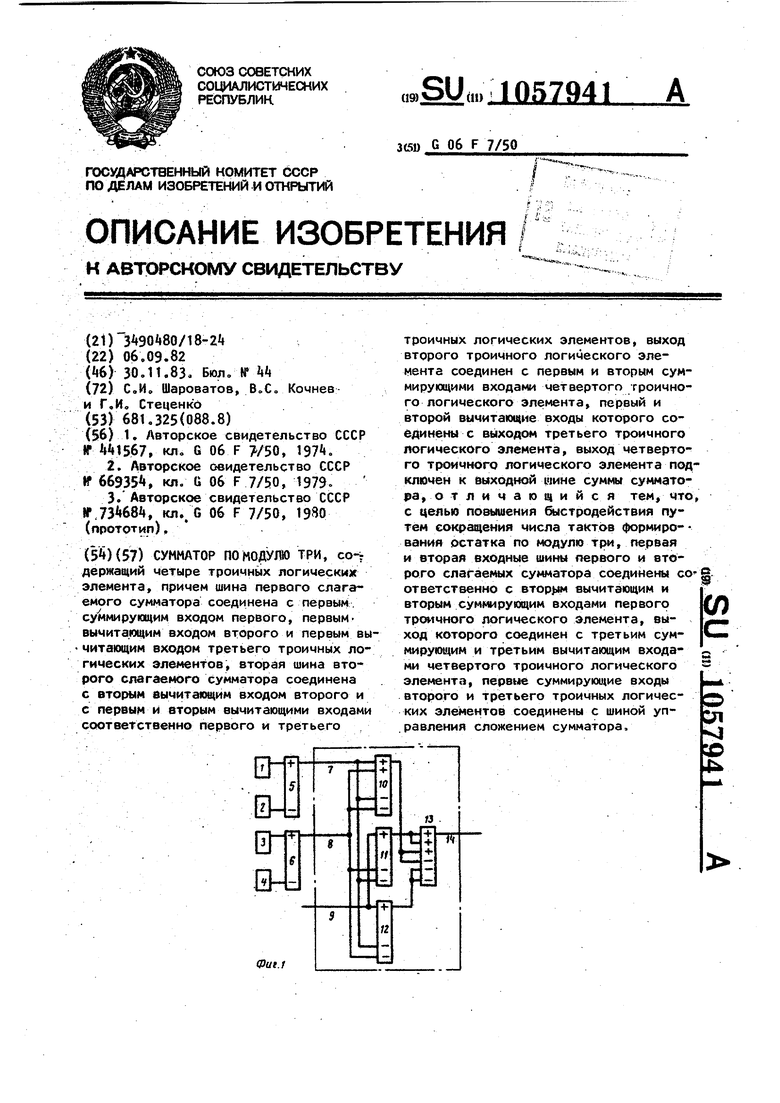

Поставленная цель достигается тем, что в сумматоре по. модулю три, содержащем четыре троичных логических элемента, причем шина первого слагаемого сумматора соединена с первым суммирующим входом первого, первым вычитающим входом второго и первым вычитающим входом третьего троичных логических элементов, вторая шина второго слагаемого сумматора соединена с вторым вычитающим входом второго и с первым и вторым вычитающими входами соответственно первого и третьего, троичных логических элементов, выход второго троичного логического Элемента соединен с первым и вторым суммирующими входами четвертого троичного логического элемента, первый и второй вычитающие входы которого соединены с вь|ходом третьего троичного логического элемента, выход четвертого троичного логического элемента подключен к выходной шине суммы сумматора, первая и вторая входные шины первого и второго слагаемых сумматора соединены соответственно с вторым вычитающим и вторым суммирующим входами первого тро 1чного логического элемента, выход которого соединен с третьим суммирующим и третьим вычитающим входами четвертого троичного логическогд элемента, первые суммирующие входы второго и третьего троичных логических элементов соединены с шиной управления сложением сумматора. На фигс 1 изображена функциональная схема сумматора по модулю три; на - временная диаграмма его работы. Четырехразрядное двоичное число находится в разрядах 1- информационного регистра (фиг, 1 На троичных логических элементах 5 и 6 определяются первый и второй остатки от деления двоичных чисел, расположенных соответственно в разрядах 1, 2 и 3, t регистра, Элементы 5 и 6 соединены с сумматором по модулю три, состоящем из первой 7 и второй 8 входных шин первого и второго слагаемых сумматора шины 9 управления сложением, троичных логических элементов 10-13 и выходной шины 1k суммы, на которую поступает остаток от деления по модулю три четырехразрядного двоичного .числа

510579 1

Продолжение табЛо 1

Продолжение табл. 1

ЮЗУЭ

8 {Таблица

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор по модулю три | 1977 |

|

SU734684A1 |

| Сумматор по модулю три | 1976 |

|

SU669354A1 |

| Сумматор-вычитатель | 1984 |

|

SU1171782A1 |

| Троичный сумматор | 1983 |

|

SU1137461A1 |

| Одноразрядный двоичный вычитатель | 1982 |

|

SU1043639A1 |

| Одноразрядный двоичный вычитатель | 1983 |

|

SU1124289A1 |

| Реверсивный счетчик импульсов | 1986 |

|

SU1405110A1 |

| Двоичный сумматор | 1981 |

|

SU1001088A1 |

| Двоичный сумматор | 1980 |

|

SU918945A1 |

| Последовательный двоичный вычитатель | 1984 |

|

SU1171781A1 |

СУММАТОР ПО МО ДУЛЮ ТРИ, CO-J держащий четыре троичных логических элемента, причем шина первого слагаемого сумматора соединена с первым. суммирующим входом первого, первымвычитающим входом второго и первым вычитающим входом третьего троичных логических элементов, вторая шина второго слагаемого сумматора соединена с вторым вычитающим входом второго и с первым и вторым вычитающими входами соответственно первого и третьего троичных логических элементов, выход второго троичного логического элемента соединен с первым и вторым суммирующими входами четвертого троичного логического элемента, первый и второй вычитающие входы которого соединены с выходом третьего троичного логического элемента, выход четвертого троичного логического элемента подключен к выходной лчине суммы сумматора, от личающи йся тем, что, с целью повышения быстродействия путем сокращения числа тактов формиро- вания остатка по модулю три, первая и вторая входные шины гюрвого и второго слагаемых сумматора соединены сО S ответственно с втор вычитающим и (Л вторым суммирующим входами первого троичного логического элемента, выход которого соединен с третьим суммирующим и третьим вычитающим входами четвертого троичного логического элемента, первые суммирующие входы второго и третьего троичных логических элементов соединены с шиной упел м равления сложением сумматора. Ф 4

Пример 1, (число 0001, где 1 в разряде 1, О в остальных разрядах).

Тактовым импульсом 15 первой фазы первого такта считывается информация 18 с разряда 1 регистра и согласно логике работы элемента (табл 1) положительный сигнал с разряда 1 регистра передается на первый суммирующий вход элемента 5 и записывается в него +1 /сигнал 22); тактовым импульсом 16 второй фазы первого такта считывается положительный сигнал с Элемента 5 (сигнал 22) и через шину 7 передается на первый суммирующий вход элемента 10 и первый вычитающий вход элемента 12 и записывается в них соответственно +1 и -1 (сигналы 2k и 26, а положительный сигнал (или тактовый импульс, поступающий через шину 9, передается на первые суммирующие входы .элементов 11 и 12и записывается в них +1 (сигналы 25 и 2б) тактовым импульсом 1/ третьей фазы первого такта считывается положительный сигнал с элемента 11 (сигнал 25), который не производит запись информации элемента 13 также считывается положительный сигнал с элемента 10 (сигнал 2, который передается на третий суммирующий вход элемента 13 и записывается в него +1 (сигнал 27).

Тактовым импульсом 15 первой фазы второго такта считывается положительный сигнал () с элемента 13 (,нал 27), который поступает на шину Т iсумматора, образуя остаток от деления по модулю три соответствующий коду 01, П р и м е р (2 число ООЮ).

Тактовым импульсом 15 первой фазы второго такта считывается информация 19 с разряда 2 регистра и согласно логике работы элемента (табл, 1), положительный сигнал с разряда 2 регистра передается на первый вычитаю-. .щий вход элемента 5 и записывается в него -1 (сигнал тактовым им- , пульсом 16 второй фазы второго такта считывается отрицательный сигнал с элемента 5 сигнал 22) и через шину 7 передается на второй вычитающий вход элемента 10 и на первый вычитающий вход элемента 11 и записывается в них -1 (сигналы 2k, 25) , а положительный сигнал (или тактовый импульс, поступающий через шину 9, передается на первые суммирующие входы элементов 11 и 12 и записывается в них +1 (сигналы 25 и 26}, тактовым импульсом 17 третьей фазы второго такта считывается отрицательный сигнал с элемента 10 (сигнал 2+, который передается на третий вычитающий .вход элемента 13 и записывается в него -1 (сигнал 27), а также считывается положительный сигнал с элемента 12 (сигнал 26) , который не производит запись информации в элемент 1.3 о Тактовым импульсом 15 первой фазы третьего такта считывается отрицательный сигнал (-1) с элемента 13 /сигнал 27), который поступает на шину 1 сумматора, образуя остаток от деления по модулю три числа 0010, со ответствующит) коду Пример 3. (число оно) „ . Тактовым импульсом 15 первой фазы третьего такта считывается информа ция 19 и 20 с разрядов 2 и 3 регистра и согласно логике работы элемента /табл l) положительные сигналы, с раз рпдов 2 и 3 регистра передаются соответственно на первый вычитающий вход элемента. 5 и первый суммирующий вход элемента 6 и записываются в них соответственно -1 (сигнал 22| и +1 тактовым импульсом 16 второй фазы третьего такта считывается отрицательный сигнал с элемента 5 /сигнал 2 и через шину 7 передается на второй вычитающий вход элемента 10 и на первый вычитающий вход элемента 11 и записывается в них -1 сигналы 2 и 25); также считывается положительный сигнал с элемента 6 /сигнал 23) и через шину 8 передается на второй суммирующий вход элемента 10 и второй вычитающий вход элемента 12 и записывается в них соответственно +1 (сигнал 2Ц и -1 Ссигнал 2б , а так же положительный сигнал /или тактовый импульс, поступающий через шину 9, передается на первые суммируюИ15ТО щие входы элементов 11 и 12 и запидывается в них +1 /сигналы 25 и 2б); тактовым импульсом третьей фазы третьего такта с элементов 10-12 считывается О /сигналы ) , сигнал отсутствует. Тактовым импульсом первой фазы четвертого такта с элемента 13 считывается О сигнал 27), который является остатком отделения по модулю три числа 0110, соответствующим коду 00. Аналогично, в соответствии со схемой (фиг. 1) и временной диаграммой (Оиг. 2) происходит выполнение последующих примеров, приведенных.в та6л„2 Использование сумматора по модулю три обеспечивает по сравнению с прототипом повышение быстродействия сумматора в полтора раза, так как первый и второй остатки по модулю три четырехразрядного двоичного числа поступают на входные шины первого и второго слагаемых сумматора во вре действия тактового импульса второй фазы, а на выходной шине суммы сумматора появляется остаток от деления четырехразрядного двоичного числа во действия тактового импульса пе;рвой фазы следующего тактй, таким образом за два периода следования тактовых импульсов формируется остаток от деления четырехразрядного двоичного числа по модулю три (в прототипе для формирования такого «е остатка необходимо три периода следования тактовых импульсов/.

TuKTl

фиг. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Модель дуги для оптимизации сетевого графика по времени-стоимости | 1971 |

|

SU441567A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-11-30—Публикация

1982-09-06—Подача