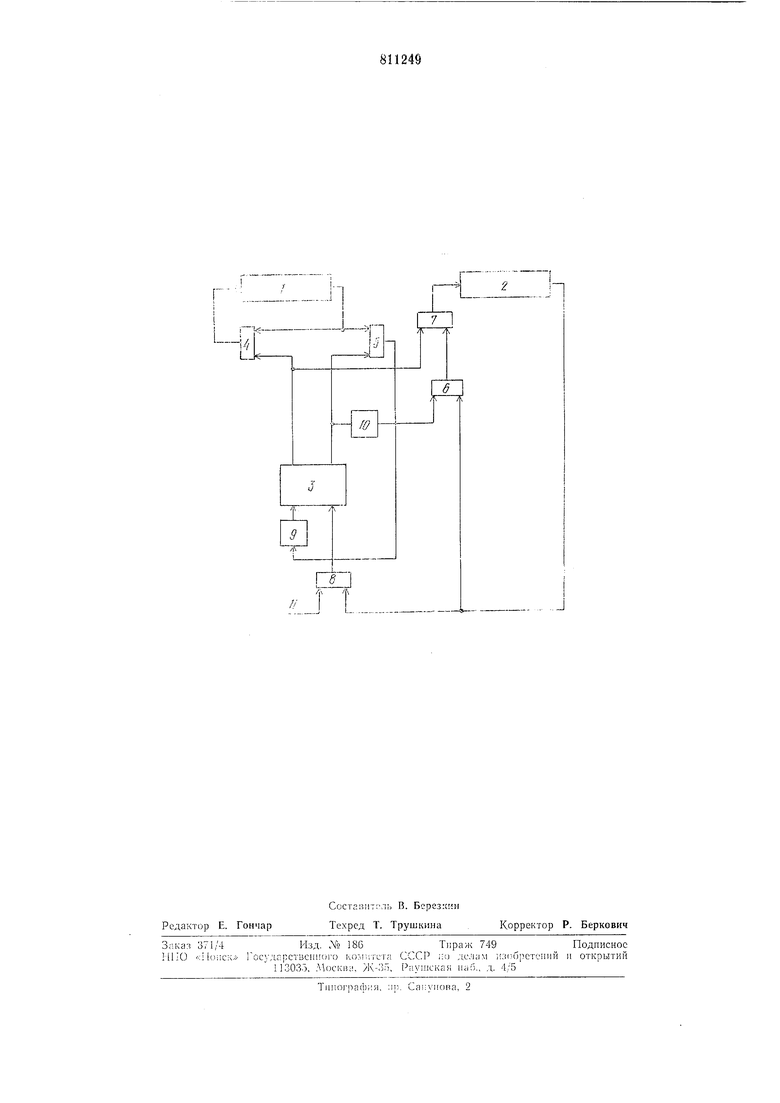

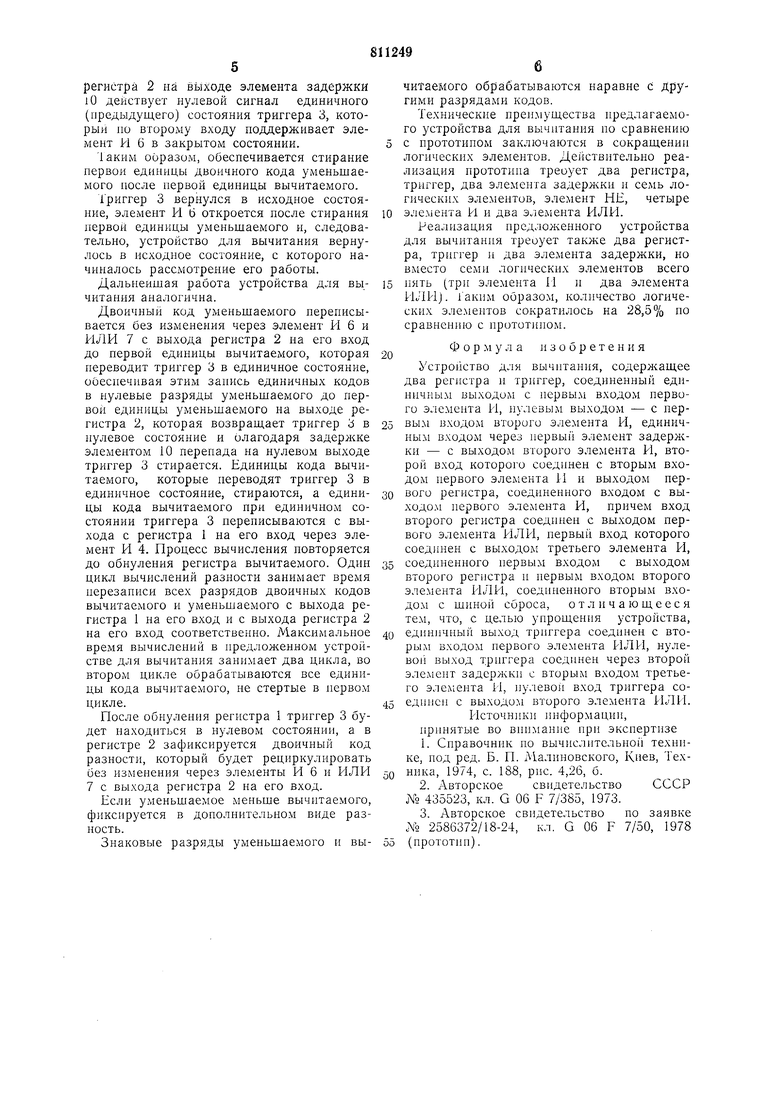

чем вход второго регистра соединен с выходом исррого элемента ИЛИ, первьи вход которого еоедипеи е выходом Tpeibcio элемента И, соедниелното первым ьлидо.м с выходом второго региетра и иервы.м входом JSTOporo элемента , еоедаиеииого вторым входом е шиной еороса, еднничиын выход трнггера еоединен е вторым входом первого эле.меггга ИЛИ, нулевой выход трнтгера еоедиаеи через второн э.гс-мент задержки е вторым входо.м третьего элемента и, нулевон вход триггера еоедннен е выходом BTOpOio э 1емеа;а . Иа чертеже нзооражена етруктурная ехема устронетва для вычигания. егронетво для вычитання еодержнт два региетра 1 н 2., триггер б, три двухвходовых элемента и , два двуАВходовв1Х элеме1гга / н а, два элемента задержкн у н Ю, шнну еороса li. оход регистра i 11одключен к выходу элемента и 4. Ьход регистра J. нодключен к выходу элемента ilJlri /, нервыи вход коTopoio 11одключе11 к выходу э;1еме1гга И (J. 1рнггер 6 нодключен еднннчнв1м выходом к нервому входу элел1е1гга И 4: и втоpOAiy входу элемента ИлИ 7, нулеввьм выходом к нервому входу элеме1гга И 5 н входу элемента задержки lO, еднннчнв1м входол - к выходу ЭоЧемента за;-,ержки У, иулевв1М входом - к выходу ЭоШмента ИЛИ и. Ьв1ход региетра 1 иодключен к вторым входам элементов И 4 и о. Выход регистра 2 иодключен к нервым входам элементов i-i U и ИЛИ 8. Быход элехмента У. 5 нодключен к входу элемента задержки i). Ьторон вход элемента Ti 6 иодключен к выходу элемента задержкн 1U. Ъторои вход элемента ИЛИ 8 иодключен к шиие еороса И. ; ;троастви для вычитания работает с«тедуютн,им ооразом. Б иеходиом состоянии триггер о уетанавливаетсь в пулевое еостоя1Н1е сигналом, ностуиающнм но гнине Сороса 11. ii регнетр 1 но сиихронизируюнднл им11ульеам тактово ; частоты носледовате твно, на411ная е младших разрядов, заинсыцастся двоичнвы код вьгтнтаемого; в регнетр 2 - двоичный код уменошаемого но сннхронизируюшим имнулвеам, задержанны.1 на нолнернода относительно синхронизируюш,их имиульсов региетра 1. Иа шину сброса И иоетуиает серия времеииых сигналов, совнадаюгцая но време1И1 е моментом считывания с выхода регистра 2 иоследнего /г-го разряда. Так как в исходном состоянни триггер 3 находится в нулевом состоянии, то элементы И 5 н И 6 открыты его нулевым выходом н э;1емент И 4 закрв т его единнчнв1М ввичодом и на втором входе элемента ИЛР1 7 действует нулевой снгнал. Элемент задержки 10 задерла-шает перенады на нулевою вв)хо,д,с1 Tpiiricpa о на вгорол вход элемсита 14 о. L выхо/ui perj;cipa 2 считывается ноеледоисПслвио, иачлиая с младшего разряда, двиичив н код улдснвшаемого, которьь через элемент и 13, открьиыи нулевыл выходом тр1ЛТера 6, и э.телхеит i-iolii / носту ает иа вход pej4TCTpa 2. 1 аким ооразол, младшие разрядв уменьшае.мого исреинеываются оез изменения с ввьхода регистра 2 на его вход до тех Jiop, нока грнггер о не иереидет в единичное состояние. jparrep J уетановнтея в единичное соCTOHiHie нервои младшей единицей двоичного кода звгтнтаелюго, которая с выхода регистра 1 через элемент и о, открытый нулейв;м выходом трнггера 3, иоетуиает на единичнын вход трнггера 3 через элемент задержки У, KOTopuiJi задерживает авичоднои имиульс регистра 1 иа время его действия. ij результате триггер 3 иере1 дет в едиинчиое состояние только иослс окончания деиетвия имиульса единицы, вычитаемого на выходе региетра 1. Этим оиесиечиваетея етнраиие 11ервои единицы кода вычитаемого е 1юмош,ью элемента И 4, закрытого единичнвим выходом тритгера 3. После перехода трнггера 3 в единичное еостоянис э.1емсн1 li о закрывается его нулевым выходола, а элемент И 4 открывается его еднничным выходом. Ьдиничнвни С1нл1ал с еднннчного ввьхода трнггера 3 ностунаст через элеме гг 7 на вход регистра 2, оосснечивая заниеь еднничньи: кодов в разряды уменьшаемого, которые следуют ноеле нерво единицы BBIчитаемого и в которых заиисан нулевой код. В это время разряды вычитаелюго неренисываются оез нзменення через .мент И 4, открытый eдиJHiчным выходом триггера 3, е ввьчода регистра 1 на его вход. Так будет иродолжаться до тех иор, пока иа ввичоде регистра 2 не иоявится имиулье единицы уменьшаел1ого, который через элемент Ис,1И и ностунает на нулевой вход триггера 3 н установит его в нулевое еоетоянне. Переход триггера 3 в нулевое еоетояние нриведет к запиранию элемента И 4 н отниранлю эле.мента И 5, а также сиимает единичный еигнал на втором входе элемента ИЛИ 7. Имиульс единицы уменьшаемого е БВ1хода региетра 2 через элемент И 6 не иройдет, так как элемент задержки 10 обеспечивает задержку иеренада на нулевом выходе триггера 3 на время действия имиульса иа выходе региетра 2. Иоэтому носле нерехода триггера 3 в пулевое состояпие в течение времени действия имнульса еднппцы уменьшаемого на выходе

регистра 2 на выходе элемента задержки 10 действует нулевой снгнал единичного (предыдущего) состояния триггера 3, который но второму входу иоддерживает элемент И 6 в закрытом состоянии.

1аким ооразом, обеснечивается стирание первой единицы двоичного кода уменьшаемого после первой единицы вычитаемого.

1риггер 3 вернулся в исходное состояние, элемент И б откроется после стирания первой единицы уменьшаемого и, следовательно, устройство для вычитания вернулось в исходное состояние, с которого начиналось рассмотрение его работы.

Дальнейшая работа устройства для вычитания аналогична.

Двоичный код уменьшаемого переписывается без изменения через элемент И 6 и ИЛИ 7 с выхода регистра 2 на его вход до первой единицы вычитаемого, которая переводит триггер 3 в единичное состояние, обеспечивая этим запись единичных кодов в нулевые разряды уменьшаемого до первой единицы уменьшаемого на выходе регистра 2, которая возвраш,ает триггер 3 в иулевое состояние и благодаря задержке элементом 10 переиада на нулевом выходе триггер 3 стирается. Единицы кода вычитаемого, которые переводят триггер 3 в единичное состояние, стираются, а единицы кода вычитаемого при единичном состоянии триггера 3 нереписываются с выхода с регистра 1 на его вход через элемент И 4. Процесс вычисления новторяется до обнуления регистра вычитаемого. Один цикл вычислений разности занимает время иерезаписи всех разрядов двоичных кодов вычитаемого и уменьшаемого с выхода регистра 1 на его вход и с выхода регистра 2 на его вход соответственно. Максимальное время вычислений в предложенном устройстве для вычитания занимает два цикла, во втором цикле обрабатываются все единицы кода вычитаемого, не стертые в первом цикле.

После обнуления регистра 1 триггер 3 будет находиться в нулевом состоянии, а в регистре 2 зафиксируется двоичный код разности, который будет рециркулировать без изменения через элементы И 6 и ИЛИ 7 с выхода регистра 2 иа его вход.

Если уменьшаемое меньше вычитаемого, фиксируется в доиолнительном виде разность.

Знаковые разряды уменьшаемого и вычитаемого обрабатываются наравне с другими разрядами кодов.

Технические преимущества предлагаемого устройства для вычитания по сравнеиию

с прототипом заключаются в сокращении логических элементов. Действительно реализация нрототииа треоует два регистра, триггер, два элемента задержки и семь логических элементов, элемент ИЕ, четыре

элемента И и два элемеита ИЛИ.

Реализация предложенного устройства для вычптаппя треоует также два регистра, триггер и два эле.мента задерл ;ки, но вместо семи логических элементов всего

пять (три элемеита II и два элемента ИЛИ). 1аким образом, количество логических эле.меитов сократилось на 28,5% по сравнению с прототипом.

Ф о р .м у л а изобретения

Устройство для вычитаиия, содержащее два регистра и триггер, соединенный единичным выходом с первы.м входом первого элемента И, нулевым выходом - с иервы.м входом второго элемента И, единичным входом через первый элемент задерл-:ки - с выходом второго элемеита И, второй вход которого соединен с вторым входом иервого элемента И и выходом нервого регистра, соединенного входом с выходо.м иервого элемента И, причем вход второго регистра соединен с выходом первого элемента ИЛИ, иервый вход которого соединен с выходом третьего элемента И,

соединенного иервы.м входом с выходом второго регистра и иервым входом второго элемеита ИЛИ, соедпненного вторым входом с шииой сброса, отличающееся тем, что, с целью уирощения устройства,

едииичный выход триггера соединен с вторым входом иервого элемента ИЛИ, нулеBoii выход триггера соединен через второй элемент задержки с вторым входом третьего элемеита И, нулевой вход триггера соедппси с выходом второго элемеита ИЛИ.

Источники информации, нрпнятые во внимание прп экспертпзе

1.Справочнпк по вычислительиой техиике, под ред. Б. И. Малиновского, Киев, Техника, 1974, с. 188, рис. 4,26, б.

2.Авторское свидетельство СССР № 435523, кл. G 06 Е 7/385, 1973.

3.Авторское свидетельство по заявке № 2586372/18-24, кл. G 06 Е 7/50, 1978

(ирототип).

. jn

tl

c

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения и вычитания чисел в фазо-импульсной форме | 1976 |

|

SU595732A1 |

| ДВОИЧНО-ДЕСЯТИЧНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР | 1971 |

|

SU293241A1 |

| Аналого-цифровой преобразователь | 1976 |

|

SU563713A1 |

| МНОГОКАНАЛЬНЫЙ КОРРЕЛЯТОР | 1973 |

|

SU387370A1 |

| УСТРОЙСТВО Д.ПЯ ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 1971 |

|

SU300449A1 |

| РЕВЕРСИВНЫЙ ДВОИЧНЫЙ СЧЕТЧИК | 1969 |

|

SU236872A1 |

| Двоично-десятичный реверсивный счетчик | 1976 |

|

SU600736A1 |

| Буферное запоминающее устройство с самоконтролем | 1976 |

|

SU595796A1 |

| Функциональный преобразователь число-импульсного кода в двоичный код | 1972 |

|

SU474001A1 |

| Устройство для цифровой многочестотной манипуляции | 1973 |

|

SU574863A1 |

Авторы

Даты

1981-03-07—Публикация

1978-12-04—Подача