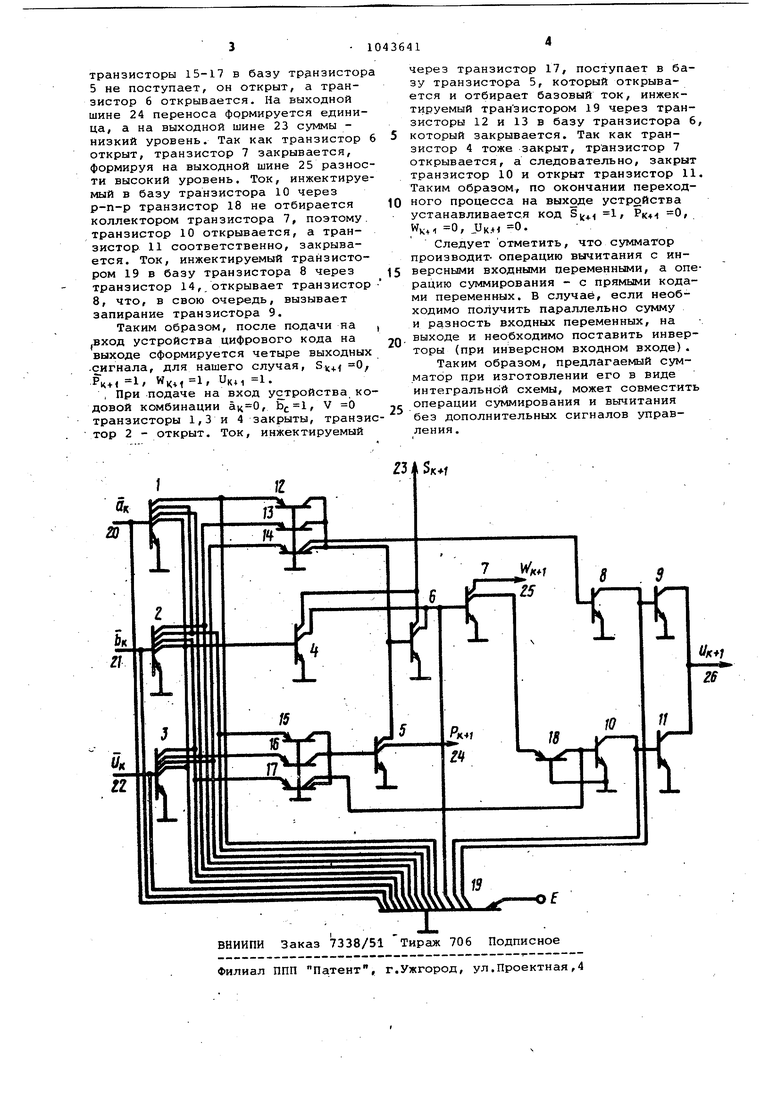

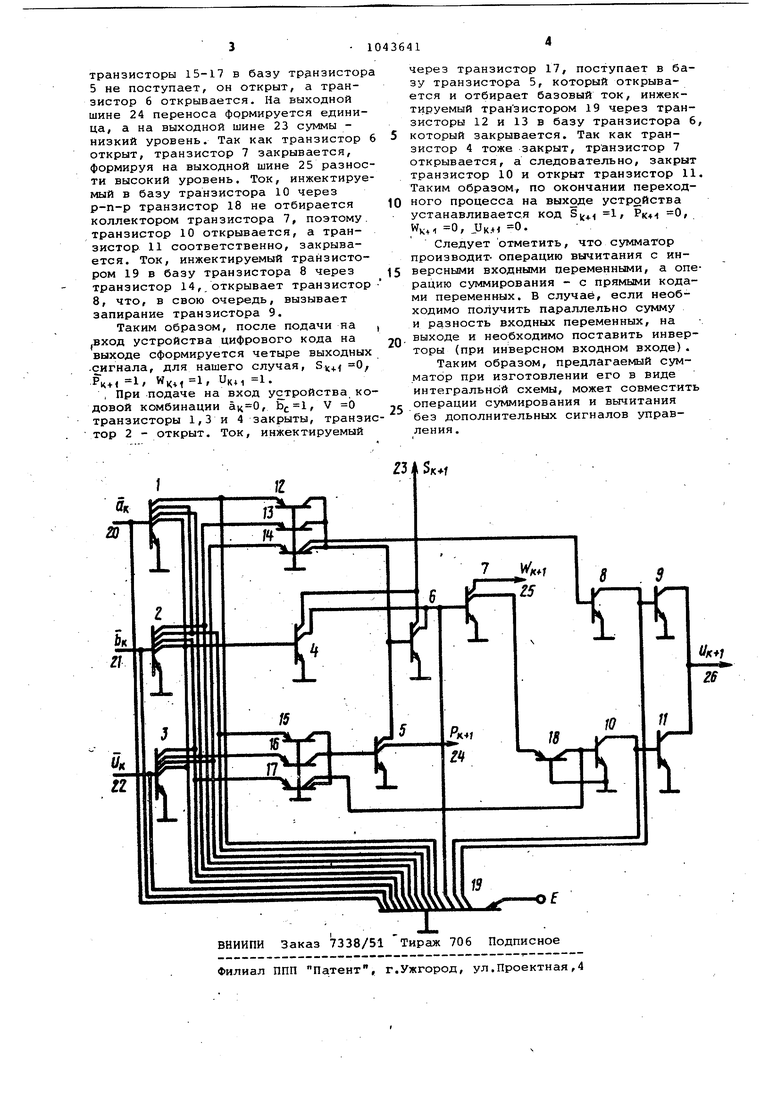

Изобретение относится к вычисли тельной технике и может быть испол зовано при построении интегральных схем обработки информации. По основному авт. св. 907543 известен одноразрядный сумматор, содержащий п-р-п и р-п-р транзисто ры, многоколлекторные п-р-п транзисторы и многоколлекторный р-п-р транзистор, эмиттер которого соеди нен с шиной питания сумматора, а коллекторы, соответственно, с эмит терами всех р-п-р транзисторов и базами первого, второго и третьего многоколлекторных п-р-п транзисторов, коллекторы, первого и второго р-п-р транзисторов соединены с базой первого п-р-п транзистора, а к лекторы третьего и четвертого р-п-р транзисторов соединены с базой чет вертого многоколлекторного п-р-п транзисторов, базы всех р-п-р транзисторов, эмиттер первого п-р-п тра зисторов, база многоколлекторнйго р-п-р транзистора и эмиттеры всех многоколлекторных п-р-п транзистор соединены с шиной нулевого потенци сумматора, последний содержит также второй п-р-п транзистор, база которого соединена с одним из коллекторов многоколлекторного р-п-р транзистора и первым коллектором первог второго и третьего многоколЛекторных р-п-р транзисторов, вторые коллекторы этих транзисторов соединены соответственно с эмиттерами первого второго и пятого р-п-р тран-зисторов коллектор пятого р-п-р транзистора соединен с коллек.тором второго р-птранзистора, коллектор четвертого р-п-р транзистора соединен с коллек тором шестого р-п-р транзистора, эмиттер которого соединен с третьими коллекторами первого и второго многоколлекторных п-р-п транзисторов, эмиттер четвертого р-п-р транзистора соединен с третьим коллекто ром третьего и четвертым коллекторо второго многоколлекторного п-р-п транзисторов, четвертые коллекторы первого и третьего многоколлекторных п-р-п транзисторов соединены с эмиттером третьего р-п-р транзистора, коллекторы первого и второго п-р-п транзисторов соединены с выходом суммы м сумматора, первый кол лектор четвертого многоколлекторног п-р-п транзистора соединен с базой nepiBoro п-р-п транзистора, второй коллектор четвертого многоколлектор ного п-р-п транзистора соединен с выходом переноса сумматора, а входами сумматора являются базы первого, второго и третьего многоколлекторных п-р-п транзисторов l . Недостатком известного устройства является ограниче ние функциональных возможностей, что выражается в невозможности осуществления операции вычитания. Цель изобретения - расширение функциональных возможностей одноразрядного сумматора за счет осуществления операции вычитания. Указанная цель достигается тем, что одноразрядный сумматор содержит третий, четвертый, пятый и шестой п-р-п транзисторы, а также седьмой р-п-р транзистор и пятый многоколлекторный п-р-п транзистор, причем перJый коллектор пятого многоколлрктор-. ного п-р-п транзистора соединен с шиной разности одноразрядного сумматора, второй коллектор соединен с ,эмиттером седьмого р-п-р транзистора, а база пятого многоколлекторного п-р-п транзистора соединена с вторыми коллекторами первого и второго п-р-п транзисторов и соответствующим коллектором многоколлекторного р-п-р транзистора, база третьего п-р-п транзистора соединена с вторым коллектором пятого р-п-р транзистора, а коллектор соединен с базой четвертого п-р-п транзистора и соответствующим коллектором многоколлекторного р-п-р транзистора, коллектор четвертого п-р-п транзистора соединен с коллектором пятого п-р-п транзистора и подключен к шине заема одноразрядного сумматора, база пятого п-р-п транзистора соединена с соответствующимколлектором многоколлекторного р-п-р транзистора и коллектором шестого п-р-п транзистора, база которого соединена с вторым коллектором шестого и коллектором седьмого р-п-р транзисторов, база седьмого р-п-р транзисторов, эмиттеры всех п-р-п транзисторов и эмиттер пятого многоколлекторного п-р-п транзистора подключены к шине нулевого потенциала. На чертеже Представлена принципиальная электрическая схема одноразрядного сумматора. Одноразрядный сумматор содержит п-р-п транзисторы 1-11, р-п-р транзисторы 12-18 и многоколлекторный инжектирующий транзистор 19. Входами сумматора являются шины 20-22, выходом суммы - шина 23, переноса - шина 24, разности - шина 25 и заема шина 26. Сумматор работает следующим образом. Предположим, что на входе устройства имеем кодовую комбинацию , , Un l. Транзисторы 1 и 3 открыты, а транзистор 2 закрыт, следовательно, ток, инжектируемый в эмиттеры транзисторов 12 и 13, отбирается соответственно коллекторами транзисторов 1 и 3, а через транзистор 14 ток поступает в базу транзистора 6. Учитывая, что ток через

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный сумматор-вычитатель | 1986 |

|

SU1335982A1 |

| Четырехуровневый одноразрядный сумматор | 1982 |

|

SU1095174A1 |

| Двоичный сумматор на инжекционных элементах | 1982 |

|

SU1109740A1 |

| Одноразрядный комбинационный сумматор | 1981 |

|

SU981995A1 |

| Инжекционный сумматор | 1988 |

|

SU1539992A1 |

| Каскад двоичного деления частоты | 1979 |

|

SU815870A1 |

| Одноразрядный сумматор | 1980 |

|

SU907543A1 |

| Одноразрядный сумматор-вычитатель | 1987 |

|

SU1424013A1 |

| Узел защиты интегрального стабилизатора напряжения | 1985 |

|

SU1317418A1 |

| Инжекционный сумматор-вычитатель | 1987 |

|

SU1471305A1 |

ОДНОРАЗРЙДНЫЙ СУММАТОР по авт. св. 907543, о т л и ч а ющ и и с я тем, что, с целью расширения функциональных возможностей за счет осуществления операции вычитания, он содержит третий, четвертый, пятый и шестой п-р-п транзисторы, а также седьмой р-п-р транзистор и пятый многоколлекторный п-р-п транзистор, причем первый коллектор пятого многоколлекторного п-р-п транзистора соединен с шиной разности одно- разрядного сумматора, второй коллектор соединен с эмиттером седьмого р-п-р транзистора, а база пятого .многоколлекторного п-р-п транзисто- ра соединена с вторыми коллекторами первого и второго п-р-п транзисторов и соответствующим коллектором многоколлекторного р-п-р транзистора, база третьего транзистора соединена с рторым коллектором пятого р-п-р ,транзистора, а коллектор соединён с базой четвертого п-р-п транзистора и соответствующим коллектором многоколлекторного транзистора, коллектор четвертого п-р-п транзистора соединен с коллектором пятого п-р-п транзистора и под:(лючен к шине заема одноразрядного сумматора, база пятого п-р-п транзистора соединена с ррответству-i ющим коллектором многоколлекторного | р-п-р транзистора и коллектором шестого п-р-п транзистора, база которого соединена с вторым коллектором Шестого и коллектором седьмого р-п-р транзисторов, база седьмого р-п-р транзистора, .эмиттеры всех транзисторов и эмиттер пятого многоО 4ia коллекторного п-р-п транзистора подключены к шине нулевого потенциала.. . : Э: «

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Одноразрядный сумматор | 1980 |

|

SU907543A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-09-23—Публикация

1982-03-29—Подача