4

00

ел

Изофетение относится к вачиспитепьной текнике, в частности к оперативным запоминающим устройствам (ОЗУ) вычислительных машин.

Известны ОЗУ на ферритовых сердеч- 5 никах с ППГ с организацией 2Д2 W. с двумя сердечниками на бит, в которых используется режим переключения сердечников по частным циклам петли гистере. |зиса М-.to

Такие ОЗУ имеют высокое быстродействие и малую потребляемую мощность, однако они не находят широкого применения, так как в них предъявляются жесткие, затруаняющие их реализацию требования не }5 только к амплитуде, но и к длительности адресного тока записи, определяющего положение рабочей точки сердечника с ППГ. на кривой перемагничивания.

Наиболее близким к изобретению яв 20 ляется устройство, которое содержит магнитный накопитель, блок, усилителей .. считывания, блок формирователей раэрядиых токов, дешифратор адреса, в оконечной ступени которог о для получения25 дв„-хполяркого тока в адресной шИне исл пользуются диодно-матричный переключатель, формирователь тока считывания, . формирователь тока заапдаси, разделительные элементы и нормирующие элементы по ; Q количеству адресных шин, причем кагкдый из нормирующих элементов вьшолнен в виде сердечника с ППГ с нормирующей обмоткой и обмоткой сброса IX. Известное устройство благодаря стабилизации рабочей точки сердечников магБИТНОГО накгатителя нормированным йрирашением магнитного потока с нормирующего элемента сохраняет работоспособность в широком диапазоне дестабилизиру- „ ющих факторов.

Однако использование нормирующего элемента, состоящего из сердечника с .ППГ с двумя обмоткат га, и разделительно-го элемента, выполненного в виде диода, на каждую адресную шину привходит к разрастанию габаритов и стоимости устройства, а также снижает технологичность и надежность ОЗУ.

Цель изофетения - упрощение устройства.

Указанная цель достигается тем, что ,в ОЗУ, .содержащее- магнитный накопитель, разрядные щины которого подключены к блоку формиро вателей разрядных токов и 55 усилителей считывания, адресные шины магнитного накшителя подключены к выходам диодно «- матричного переключателя, первый вход которого соединен с выходом формирователя тока записи, фо{ 1мирователь тока считывания, нормирующи элемент, вьшолненный в виде сердечника |с ППГ с нормирующей обмоткой и обмот-; кой сброса, v разделительные элементы, введен ключ, вход которого подключен к выходу формирователя тока записи, выходы разделительных элементов подключены к соответствующим выходда диодно-матричного переключателя, входы разделительных элементов объединены и подключены к одному выводу нормирующей обмотки. Другой вьшод которой соединен с кодом ключа, один вывод обмотки соединен, с выходом формирователя тока считывания, другой вывод - с вторым входом диодно-матричного переключателя .

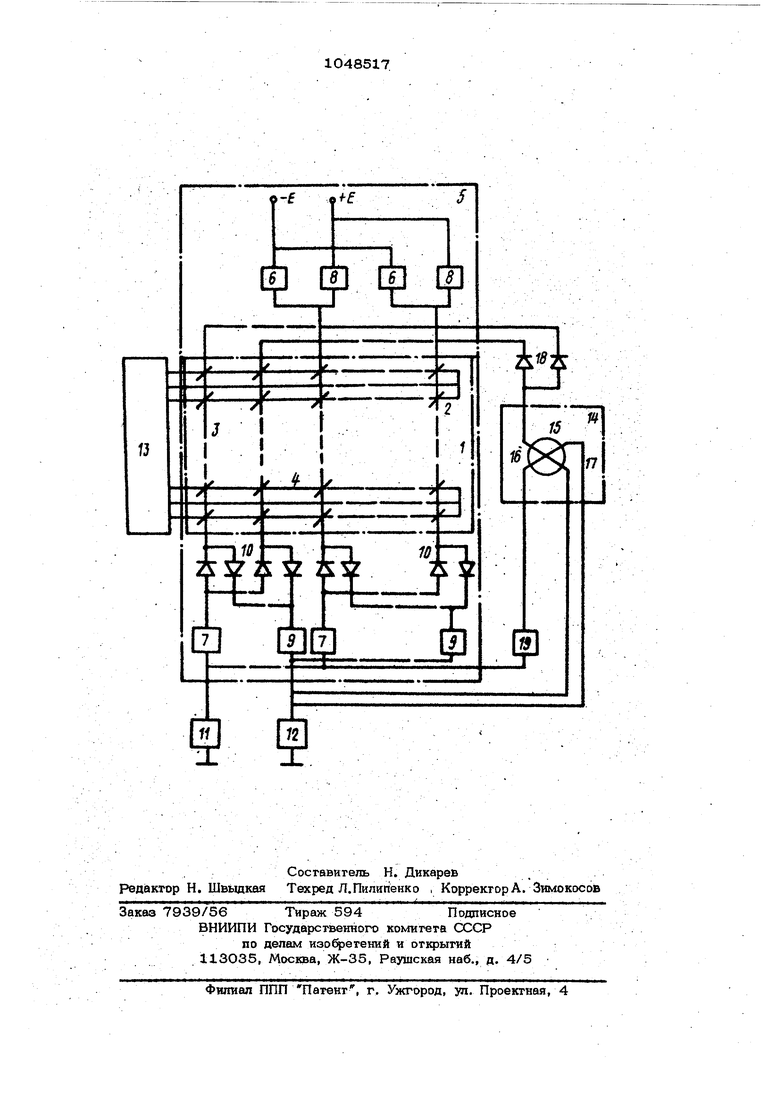

На чертеже представлена функциональная схема ОЗУ.

ОЗУ содержит магнитный накопитель 1, в котором информационные сердечники 2 прошиты адресными шинами 3 и раз рядными шинами 4, диодно-матричныЙ переключатель 5 с ключами записи 6 и 7, ключами считьюания 8 и 9 и диодами 10, формирователь тока записи 11, формирователь тока считывания 12, блок формирователей разрядных токов и усилителей считывания 13, нормирующий элемент 14, вьтолненный в виде сердечника с ППГ 15 с норт 4 ирующей обмоткой 16 и обмоткой сброса 17, разделительные элементы 18 и ключ 19.

Устройство работает следукяцим образом. .

При записи информации в - магнитный накопитель 1 открывается ключ 19 и пара ключей записи 6 и 7 в даодно-матричном переключателе 5. Адресный ток записи от формирователя тока записи 11 распределяется между выбранной.адресной шиной -3 и нормирующей обмоткой 16. При этом переключаются сердечник 15 нормирукяцего элементй 14 и находящиеся на выбранной адресной щине 2 m . информационных сердечников, где m - количество разрядов ОЗУ. Приращение магнитного потока в сердечнике 15 нормирующего элемента йФк и суммарное приращение потока в информационных сердечниках 2 магнитного накЬпителя 2 m & ( связаны меокду собой следующим соотношением:

(,,il.cpj, 2тАФцЦих+и;д д „4Ф где Wn - число витков нормирукшхей обмотки 16; . ( - напряжение на ключе 19 и диоде 18 в нормирукхцей . цепи; ( спряжение на ключе 7 и nunno 1 П в пиппно-матпиг диоде IP в диодно-матричном переключателе: - длительность импульса гбк записи ф| фд - потери на проводнике соответственно нормирую шей о&лотки 16 и адресной шины 3. Одновременно с афесным током запис в каждую из разрядных шин 4 подается разряднь1й ток записи, который не меняя суммарного приращения потока у пары информашюнных сердечников 2, находя- . шихся на пересечении ра ядной шины с выбранной адресной шиной, приводит к увёпи leнию прирашения потока в одном тлу/ ормвяя :онном сердечнике 2 и уменьшению прирашв ния потока в другом сердечнике данной пары. Тем самым разрядный ток записи определяет величину и полярность разност ного потока от пары информационных серг дечников 2 который в свою очередь определяет полезный сигнал при считьтаНИИ информации с данной разр;ядной шины. Число витков VVx, в нормиру Ёошей обмотке 16 выбирается таким образом, чтобы тгри полном переключении сердечннка 15 нормирующего элемента 14 суммарное приращение потока в информацио ных сердечниках 2 на адресной шине 3 составило половину от маисималЕгно возможного приращения потока в втих сердечниках. При этом несмотря на то, что лФ, лишь приблизительно равно 2 м -i Фц , при записи име-ет место нормирование приращения пото1ка информашюнных се|}дечвикрв 2 потоком полного переключения нормирующего сердечника 15i и положение рабочей гочкн информешионных сердечников 2 не выходит|за границы линейной зоны в характеристике запйси, т. е. в зависимости величины разностного потока от раз«г-- рядного тока записи. П(да считывании информации в адресную шину 3 подается адресный ток считывания, амплитуда которого выбирается достаточной для переключений информационных сердечников 2 в исходное состояние С-Вп ). В цепь адресного тока считывания включена обмотка сброса 17 нормирующего элемента 14, за счет чего сердечник 15 при считывании также пврег ключается в исходное состояние. При сохранении преимуществ ваюесгного устройства, обусжжпенных нормированием приращения потока информациоя;о 1х сердечникбв, предложенное ОЗУ содержит значительно меньшее число нормирующих и разделительных элементов, |что позволяет ростигь конструшию устройства. .

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1977 |

|

SU708415A1 |

| Цифровое устройство числового программного управления | 1971 |

|

SU441858A1 |

| Магнитное оперативное запоминаю-щЕЕ уСТРОйСТВО | 1979 |

|

SU841039A1 |

| ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1973 |

|

SU393741A1 |

| Запоминающее устройство | 1974 |

|

SU491153A1 |

| РЕВЕРСИВНЫЙ ДЕШИФРАТОР | 1969 |

|

SU247351A1 |

| МАТРИЧНОЕ ФЕРРИТ-ДИОДНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU395899A1 |

| Управляющий автомат цифрового устройства числового управления | 1972 |

|

SU507153A1 |

| Устройство для контроля двухпроводных запоминающих матриц | 1978 |

|

SU752503A1 |

| Реверсивный дешифратор | 1976 |

|

SU604151A1 |

ОПЕРАТИВНОЕ ЗАПОМИНАЮ ШЕЕ УСТРОЙСТВО, содержащее магнитный накопитель , разрядные шины которого поаключены к блоку формирователей разрядных токов и усилителей считывания, адресные шины магнитного накопителя подключены к выходам диодно-матричного переключателя, переый вход которого соединен с выходом формирователя .тока записи, формирователь тока считывания, нормируххдий элемент, вьшолненный в виде сердечннка с ППГ с нсфмирукяией овмоткой ноЛ откоЙ сброса, разделительные элементы, о т я и ча ющееся тем, что, с пелью упро- щения устройства, введен ключ, вход которого подключен к выходу форми.. рователя тока записи, выходы рвздепительньк элементов подключены к соответствующим выходам днодно-матрнчного перекпю-. чателя, входы разделительных элементов объединены и лодключешл к одному выводу нормирукядей обмоткя, вывод которой соединен с выходом влюча, одкн , (Л вывод обмотки сброса соединен с выходом j формирователя тока счнтывання, другой j вывод - с вторым всодом диодно-матрачного переключателя k

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающие угтройства ЭЦВМ | |||

| Сборник статей | |||

| Пер | |||

| с ант | |||

| под ред А | |||

| А | |||

| Крупского-, М., Мир, 1968, с | |||

| Приспособление для записи звуковых явлений на светочувствительной поверхности | 1919 |

|

SU101A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Оперативное запоминающее устройство | 1977 |

|

SU708415A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| , | |||

Авторы

Даты

1983-10-15—Публикация

1981-11-24—Подача