10515 соеаинен с вторым вхоцси « четвертого элемента И, с первым входом схемы сравнения, второй вход которой соединен с вторым входом пятого элемента И и выходом регистра накопления, выход схемы сравнения является выходов ре34зультатв контроля устройства, вьжоа второго генератора одиночного импульса соединен с третьим входом четвертого элемента ИЛИ, тактовый вход триггера соединен с тактовым входом усгройсгва.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1989 |

|

SU1631556A1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1989 |

|

SU1631555A1 |

| Устройство для реализации быстрого преобразования Фурье | 1988 |

|

SU1672468A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| Вычислительное устройство | 1987 |

|

SU1522195A1 |

| Интегроарифметическое устройство | 1987 |

|

SU1515162A2 |

| Вычислительное устройство | 1981 |

|

SU1057940A1 |

| Устройство для реализации быстрого преобразования Фурье | 1984 |

|

SU1233166A1 |

| Устройство для вычисления полинома второй степени | 1983 |

|

SU1109743A1 |

| Устройство для сложения и вычитания чисел по модулю | 1990 |

|

SU1755275A1 |

УСТРЧЭЙСТВО ДЛЯ ВЫЧИС- ЛЕНИЙ В КОНЕЧНЫХ ПОЛЯХ, соцержашее первый, второй и третий элементы И, элемент ИЛИ, регистр наксншения, умножитель, сумматор, регистр one ранца, причем выхоа сумматора соецинен с первым вхоцом первого элемента И, вьпсоа соединен с первым вхоаом элемента ИЛИ, выхоц которого соединен с входом регистра накопления, выход которого соединен с первым входом умножителя, о т л в -, чающееся тем, что, с пелью расширения функциональных возможностей за счет обеспечения выполнения операции умножения со сложением, помимо операций умножения и словкения, и увеличения достоверности вычислений, в него введены триггер, первый и второй генераторы одиночного импуль са, первый и второй элементы НЕ, схема сравнения, четвертый н пятый элементы И, второй, третий, четвертый и пятый элементы ИЛИ, второй регистр операнда, суммирующий блок, причем выход первого элемеита НЕ соецвнен с вторым входом первого элемента И, а вход соединен с выходом второго элемента И, с первым входом второго элемента ИЛИ и с входом первого генератора одиночного импульса, выход которого соединен с вторым входом первого элемента ИЛИ, первый вход второго элемента И соединен с вхоаом обращения устройства и с установочным входом триггера, инверсный выход которот о соединен с вторым входом элемента И, второй вход второго элемента ИЛИ соединен с входом контроля устройства, а выход соединен с первым входом третьего элемента ИЛИ, с первым входом пятого элемента И, выход которого соединен с первым входом (Л четвертого элемента ИЛИ, второй вход . которого соединен с выходом четвертого элемента И, первый вход которого соединен с выходом второго элемента НЕ, вход которого соединен с выходом третьего элемента ИЛИ, второй вход которого соединен с входом второго генератора ел одиночного импульса, первым входом пятого элемента ИЛИ, входом сложе;л ния устройства, выход второго регистра :о 1 операнда соединен с первым входом тре- i тьего элемента И, второй вход которого | соединен с выходом пятого элемента ИЛИ, второй вход которого соединен с входом умножения со сложением устройства, выход третьего элемеита И соединен г; первым входом сумматора, второй вход которого соединен с выходом умножителя, второй вход которого соединен с выходом четвертого элемеита ИЛИ, входом суммирующего блока, выход кЬторюго соединен с входом первого регистра операнда, выход которого

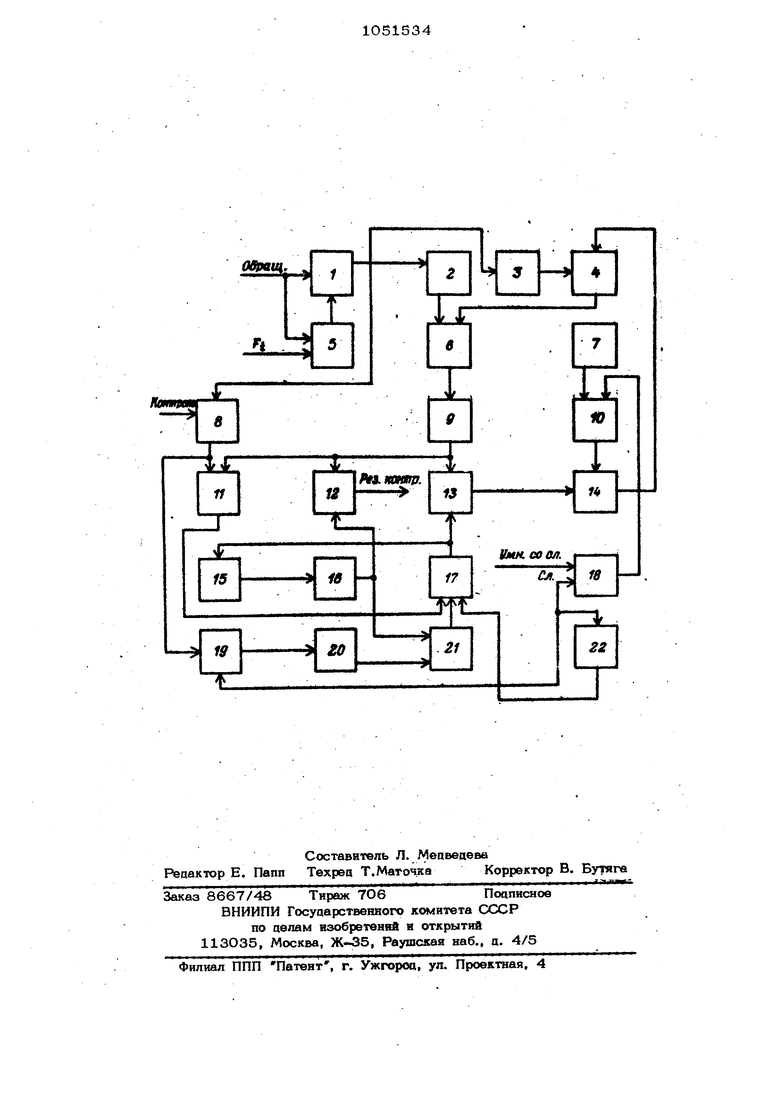

Изобретение относится к вычислител ной технике и мсякет быть применено п построении спейиализированных вычисли тельных устройств для кодирования и декодирования корректирующих сшибки кодов. Известно устройство для умножения элементов конечного поля, содержащее , цэа регистра сомножителей, элементы И и выходной регистр с обратными связами . Недостатками данного устройства являются низкое быстродействие определения произведения и невозможность вьшолнения других вычислительных one раций. Наиболее близким по техническому решению к предлагаемому является уст ройство для вычислений IB конечных пол содержащее первый, второй и третий элементы И, элемент ИЛИ, регистр накопления, умножитель, сумматор, регистр операнда, причем выход суммато соединен с первым входом первого элемента И, выход которого соединен с ккодом регистра накопления, выход кот рого соединен с первым входом умножителя 2 , Это устройство характеризуется невысокой надежностью работы из-за бол шой сложности реализации, опрецеляе- ыо1, в основном, сложностью блока обращения, и отсутствия контроля его исправности. Кроме того, устройство выполняет вычислительные операции только с одним или двумя операциями, Б то время как при декодировании кодой очень часто необходимо выполнять операции с тремя операндами. Цель изобретения - расширение функ циональных возможностей за счет обесп чения выполнения операции умножения со сложением, помимо операций умно жения и сложения, и увеличение достоверности вычислений. Для достижения поставленной цели в згстройсгво для вычислений в конечных полях, содержащее первый, второй и третий элементы И, элемент ИЛИ, регистр накопления, умножитель, су1 лматор, регистр операнда, причем выход сумматора соединен с первым входом перв.ого элемента И, выход которого соеди- нен с первым входом элемента ИЛИ, выход которого соединен с входом регистра накопления, выход которого соединен с первым входом умножителя, введены триггер, первый и второй генераторы одиночного импульсу, первый и второй элементы НЕ, схема сравнения, четвертый и пятый элементы И, второй, третий, четвертый и пятый элементы ИЛИ, второй регистр операнда, суммирующий блок, причем выход первого элемента НЕ соединен с вторым входомпервого эле- мента И, а вход соедтшен с выходом второго элемента И, с первым входом второго элемента ИЛИ и с входом первого генератора одиночного импульса, выход которого соединен с вторым входом первого элемента ИЛИ, первый вход вто рого элемента И соединен с входом обращения устройства и с установочным входом триггера, инверсный выход которого соединен с вторьгм входом элемента И, второй вход второго элемента ИЛИ соединен с входом контропя устройства, а выход соединен с первым входом третьего элемента ИЛИ, с первым входом пятого элемента И, выход которого соединен с первым входом чет вертого элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента И, первый вход которого соединен с выходом второго элемента НЕ, вход которого соединен с выходом тре- тьего элемента ИЛИ, второй вход кото- рого соединен с вхоцом второго генератора одиночного импульса, первым вход пятого элемента ИЛИ, вхоцом сложения устройства, выход второго регистра опе ранда соединен с первым входом третье го -элемента И, второй вход которого соединен с. выходом пятого элемента ИЛ второй вход которого coeflfflf H с входом умножения со сложением устройства, вы ход третьего элемента И соединен с первым входом сумматора, второй вход которого соединен с выходом умножител второй вход которого соединен с выходом четвертого элемента ИЛИ, входом суммирующего блока, выход которого соединен с вхоцс первого регистра операнда, выход которого соединен с вторым входом четвертого элемента И, с первым входом скемы сравнения, второй вход- которой соединен с вторым входом пятого элемента И и выхб- дом регистра накопления, выход схемы сравнения является выходом результата контроля устройства, выход второго генератора одиночного импульса соединен с Третьим входом четвертого элемента ИЛИ, тактовый вх;од триггера соединен с тактовым входом устройства На чертеже представлена функциональная схема устройства. Устройство для вычислений в конечных полях содержит элемент И 1, гене|затор 2 одиночного импульса, элемент НЕ 3, элемент И 4, триггер 5, элемент ИЛИ 6, регистр 7 операнда, элемент ИЛИ 8, регистр 9 накопления, элементы И 10 и 11, cxeMj 12 сравнения, .умножитель 13, сумматор 14, суммируюший блок 15, регистр 16 операнда, элементы ИЛИ 17 - 19, элемент НЕ 20, элементы И 21, генератор 22 одиночного импульса. Устройство работает следующим образом. В случае, когда все управляющие сигналы равны нулю, устройство выполняет операцию умножения. В исходном состоянии триггер 5 обнулен. Первый сомножитель из регистра 9 подается на первьА вход умножителя 13. Второй сомножитель из регистра 16 операнда через элементыИ2 и ИЛИ 17 подключается к второму входу умножителя 13, так как на второй вход элемента И 21 поступает единица а на второй и третий входы элемента ИЛИ 17 - нули. Полученное с выхоаа умножителя 13 произведение складьша- ется в сумматоре 14с нулем, поскольку на второй вход элемента И Ю подается нуль с выхода элемента ИЛИ 18. Таким образом, результат умножения с выхода сумматора 14 через элементы И 4 и ИЛИ 6 записывается в регистр 9, так как на другие входы элементов И 4 и ИЛИ 6 подключены соответственно единица и нуль. Данная операция при нспользсжании однотактного умножителя элементов ксжечных полей выполняется за.один такт. Операция сложения выполняется в том случае, если сигнал управления режимом сложения равен единице, а все остальные управляющие режимом сигналы равны нулю. При этом на второй вхоа умножителя 13 подключается через второй вход Ъ выход элемента ИЛИ 17 еайничная комбинация с выхода генератора 22 одиночного импульса, так как на его управляющий вход подана единица. Поэтому на первый вход сумматора 14 поступает число из регистра 9, а на второй через элемент И Ю число из регистра 7 операнда, поскольку на второй вход элемента И Ю подключена единица. С выхода сумматора 14 результат сложения записывается в регистр 9 так, как при умножении. Операция сложения выполняется за один такт. Для выполнения операции умнс кения со сложением необходимо подать единичный сигнал управления соответствующим режимом. Данный сигнал, прокоая через элемент ИЛИ 18, разрешает прохождение слагаемого на второй вход сумматора 14. Подключение сомножителей к входам умножителя 13 в запись результата операции происходит так же, как при умножении. Выполнение операции длится один такт. Операция обращения в конечном поле в предлагаемом устройстве выполняет ; о -«2 , где ji - обращався в виде а -5- 8 о мое число, о - результат, М - разрядность элементов конечного поля. При нулевом сигнале управления режимом обращений триггер 5 сброшен. С появлением в начале такта сигнала обращения производится запуск триггера в конце такта тактовой частоты F, nocTynaioшей на вход запуска триггера 5. Сигнал обращения должен быть длительностью в VI тактов. При этом на инверсном выхо qe триггера 5 на первом такте обрашения еаиница, на послецующих тактах нуль.

Н

Обращаемое число в исходном состоянии хранится в регистре 9. На первом такте обращения с выхода элеме1Ь та И 1 выхоцит еаиничный сигнал, который, проходя через элемент ИЛИ 8, разрешает прохождение обращаемого ;числа через элементы И 11 и ИЛИ 17 на вход суммируюшего блока 15, реализующего 4ункцию возведения в квадрат. Этот же сигнал с выхода элемента ИЛИ 8 через элементы ИЛИ 19 и НЕ 2О запрещает прохождение сигнала с выхода регистра 16 операнда на вход элемента ИЛИ 17. В то же время еди нйчная комбинация с выхода генераторе 2 одиночного импульса через элемент ИЛИ б подключается на вход регистра 9, Единичный сигнал с выхода элемента И 1, проходя через элемент НЕ 3, запрещает прохождение сиЬ нвбпа с выхода сумматора 14 на первый вход элемента ИЛИ 6. В конце первого такта в регистр 9 записывается единичная комбинация, а в регистр 16 операн-. да - квадрат обращаемого числа.

Начиная с второго в последующих текстах обращения устройство работает следующим образом.

Число, хранимое в регистре 16 операнда, проходя через элементы И 21 и ИЛИ 17, возводится в квадрат в суммируюшем блоке 15. Это же число подключается с выхода элемента ИЛИ 17 н вторсй вход умножителя 13. На первый вход, умножителя 13 .поступает число с регистра 9. В конце каждого такта в регистр 16 операнда записывается результат с выкодасуммирующего блока 15, а в регистр 9 - результат умножения. Таким образе, в регистре 9 образуется следую шая последовательность чисел: , , В, ..., . На П -ом такте обращения в регистр 9 записывается tpe буемый результат.

Режим контроля начинается при включении единичного сигнала управления ре

.жимом контроля. В этом режиме проверя

ются основные узлы устройства. Число из регистра 9 попадает на первый вход умножителя 13, Сигнал управления режимом контроля, проходя через элемент ИЛИ 8, разрешает прохождение сигнала с регистра 9 через элементы И 11 и ИЛИ 17 на в1Х)рой вход умножителя 13. Результат умножения складывается на сумматоре 14 с нулем и через элементы И 4 и ИЛИ 6 подключается к входу регистра 9, Сигнал с регистра 9 через элементы И 11, ИЛИ 17 и суймируюший блок 15, реализующий схему возведения в квадрат, подключается к входуя гистра 16 операнда. В конце такта результат возведения - ; в квадрат записывается в регистр 16 операнда, а результат умножения числа само на себя - в регистр 9. Данные рэзулы таты должны быть равны. Они сравниваются на схеме 12 сравнения, сигнал с выхода которой показывает результат контроля.

Режим контроля может длиться любое количество . При этом в каждом такте работы будут сравниваться результаты операции возведения в квад рат и операции умножения.

Такое построение устройства позволяет выполнять дополнительнью функции умножения со сложением и контроль При анапйзе выполнения спецвычислнтелем .операций кодирования-декоаирования, получаем, что основной объем вычислительных операций составляют операции умножения со сложением, поэ тому выполнение операции умножения со сложением в один такт упрощает про цесс и почти в 2 раза сокращает врем выполнения процедур. Введение дополнительной функции контроля позволяет убедиться в работоспособности устройства.

Т61КИМ образом, введение peжиlvfa контроля и упрощение реализации предлагаемого устройства позволяет повысить надежность его работы по сравнению с прототипом.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Галлагер Р | |||

| Теорвся информации и надежная связь | |||

| М., Советское рацно, 1974, с | |||

| Телефонно-трансляционное устройство | 1921 |

|

SU252A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| and Schneider David I | |||

| Compotation wiht Finite Fields.- Informat ion and Control, V, 6, № 2, June 1963, fiq.l, p | |||

| Машина для разделения сыпучих материалов и размещения их в приемники | 0 |

|

SU82A1 |

Авторы

Даты

1983-10-30—Публикация

1982-07-05—Подача