элемента задержки, входы синхронизации (k-l)-ft группы триггеров соедине 1П57940 ны ки с входом (k-2)-ro элемента задержи выходом элемент.а И,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1985 |

|

SU1305667A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для умножения | 1984 |

|

SU1233136A1 |

| Устройство параллельной обработки видеоинформации | 1989 |

|

SU1651299A1 |

| Параллельный сумматор | 1981 |

|

SU1018114A1 |

| Устройство для умножения | 1985 |

|

SU1254473A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2022339C1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Устройство для поиска координат точки экстремума функции двух переменных | 1981 |

|

SU966703A1 |

1. ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее два блока памяти, k умножителей, сумматор и микропрограммный блок управления, причем первый вход устройства соединен с информахшонным входом первоТо блока памяти, выходы которого соединены с первыми входами соответствующих умножителей, выходы сумматора.соединены соответственно с инЛормациоН ными входами второго блока памяти, выходы которого являются выходами устройства и соединены с первой группой информационных входов сумматора, выходы микропрограммного блока управления, с первого по третий, соединены соответственно с управляющими входами первого и второго блоков памяти и сумматора, отличающееся тем, что, с целью сокращения аппаратурных затрат, оно содержит регистр, блок задержки. причем второй вход устройства соединен с информационным входом регистра, выход которого соединен с вторым входом первого умножителя и информационным входом блока задержки, выходы которого с первого по (k-0-й соединены соответственно с вторыми входами умножителей, со второга по k-и, выходы умножителей соединены с второй группой инбормационных входов сумматора, упраллякг111Ие вхо.пм регистра и блока задержки соединены соответственно с четвертым и пятым выходами микропрограммного блока управления. 2. Устройство по п. 1, о т л и3 чающееся тем, что блок за- (Л держки содержит (k-l) групп триггеров по п триггеров в каждой (п-число разрядов, на которое производится умножение), k-2 элемента задержки, элемент И, генератор импульсов, триггер,управления, причем управляющий вход блока задержки соединен ел с установленным входом триггера уп- равления, выход которого соединен с X) первым входом элемента И, второй 1зход которого соединен с выходом генератора импульсов, входы триггеров первой группы соединены с информационным входом блока задержки, выходы триггеров каждой из групп соединены с соответствуюп(им выходом блока задержки и входами триггеров последующей группы, входы синхронизации триггеров групп с первой по (и-2)-ю соединены соответственно с выходами соответствуюршх элементов задержки, выходы каждого из которых соединены с выходом последующего

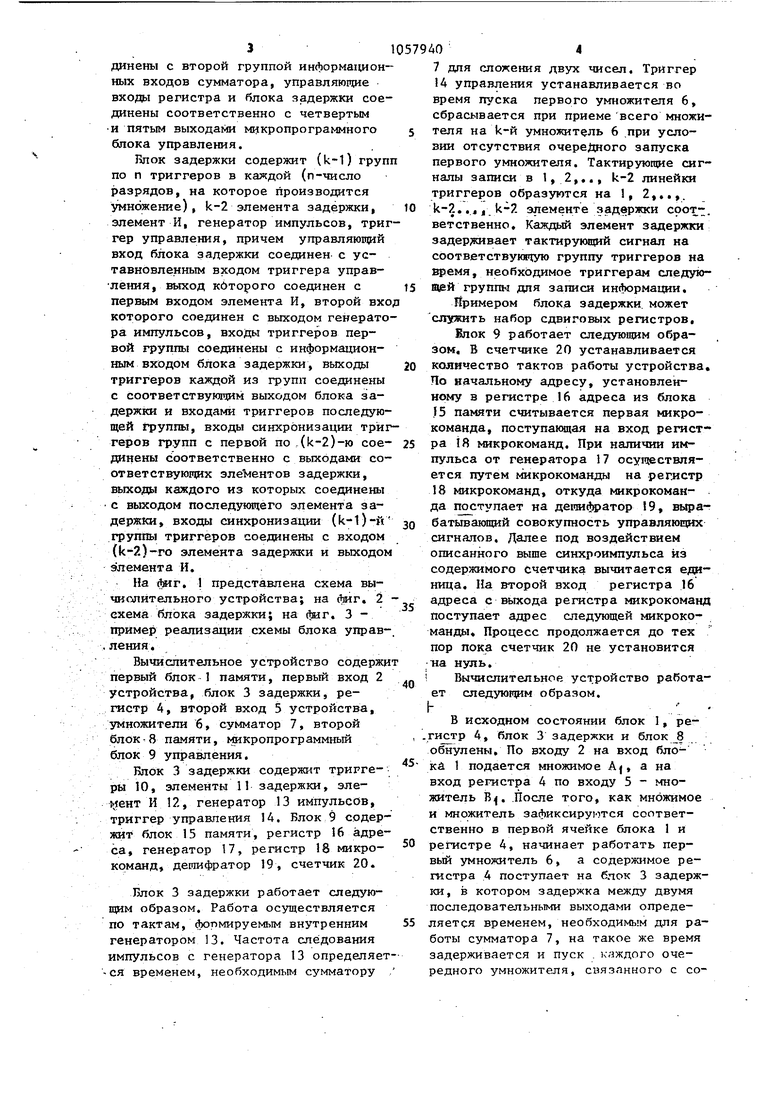

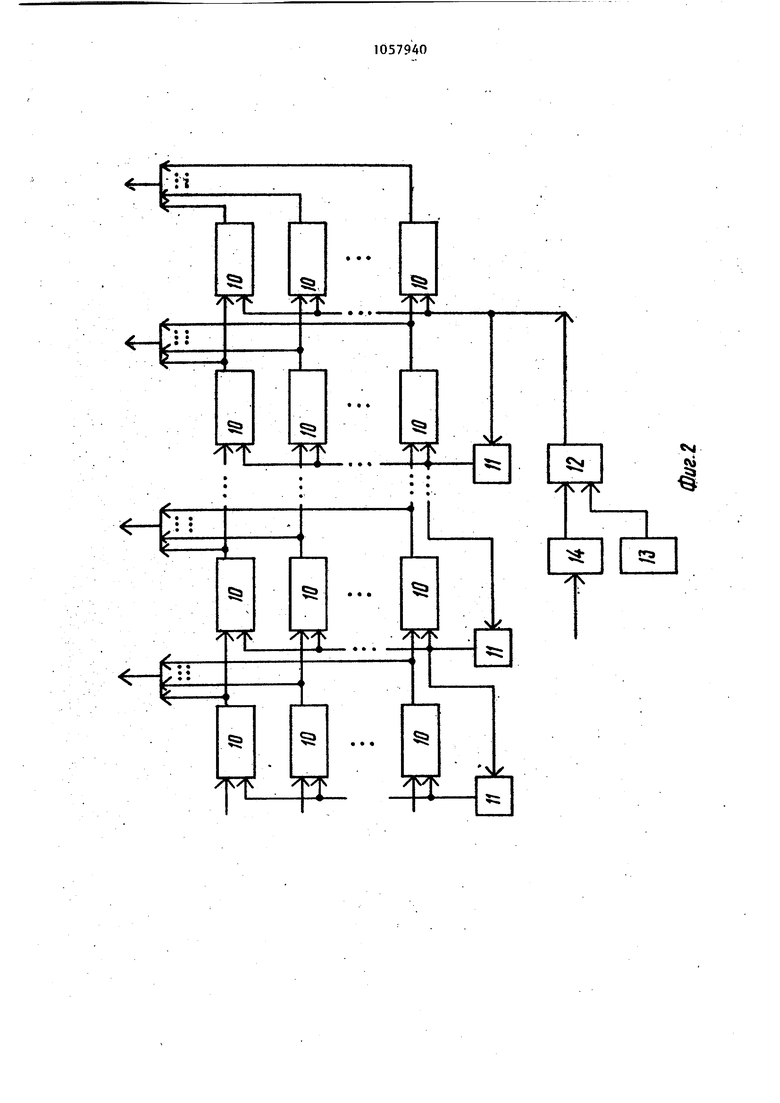

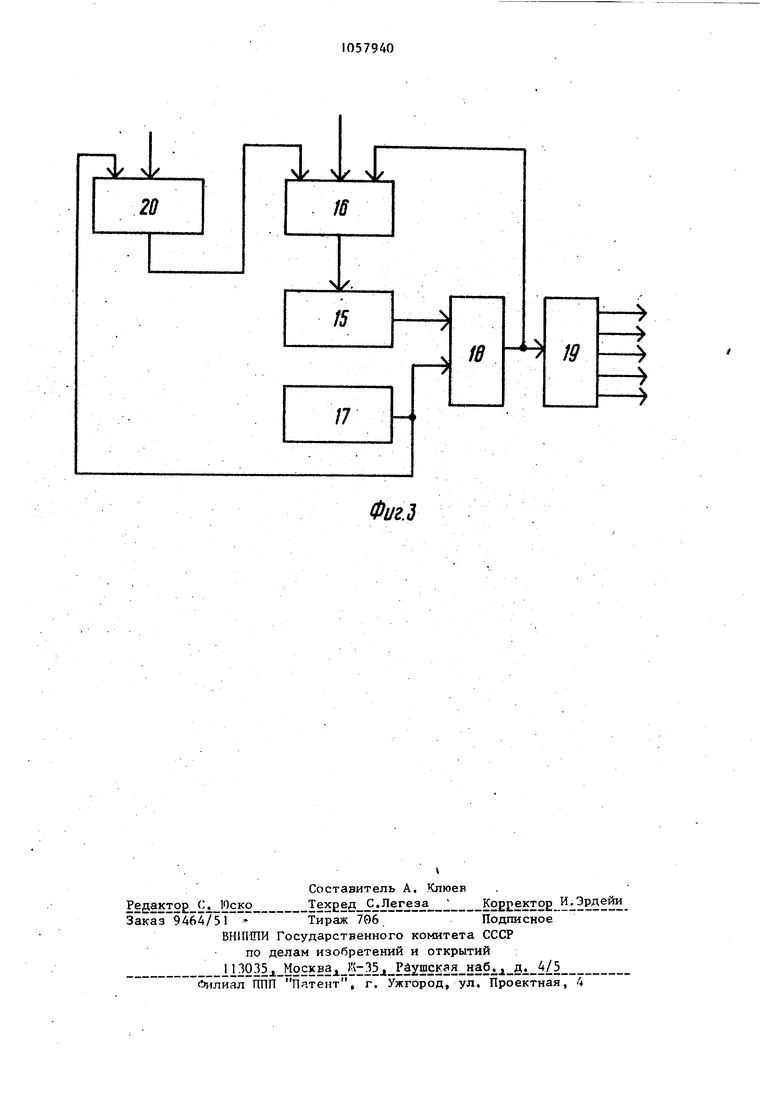

: Изобретение относится к вычислительной технике и может быть исполь зовано при построении специализированных вычислительных систем. Известно вычислительное устройст во , выполняющее параллельно операции умножения при вычислении сумм произведений, содержащее,й-апоминающие блоки множимых и множителей, sa поминакиций блок результатов и сумматоры ГП . Недостатком устройства является низкая производительность при выпол нении действий над матрицами. Наиболее близким по технической сущности к предлагаемому является вычислительное устройство, содержащее четыре блока памяти, k умножителей, сумматор и блок управления, причем входы первого и второго блоков памяти являются соответственно первым и вторым входами устройстsaj выходы первого и второго блоков памяти соединены соответственно с. первыми и вторыми входами соответст вующих умножителей, выходы которых соединены с соответствующими входам третьего блока памяти, вьрсоды Korop го соединены с первой группой входо сумматора, выходы которого соеди11ены -соответственно с входами четвертого блока памяти, выходы которого являются выходами устройства и соединены с второй группой входов сумматора, выходы с первого по пятый блока управления соединены соответственно с управляющими входами первого второго, третьего и четвёртого блоков памяти, управляющим входом сумматора , Недостаток известного устройства - значительные аппаратурные затраты при вычислении суммы векторов, каждый из которых представляет собой произведение симметричной {патрицы на соответствующий вектор-столбец, ,определяемой следующим выражением: ,B iA2B5 - KB 4 A,,BK+,t...t А„ВК Cf АдBQ ...«АкВн Ы&К-( ,вк+ A2e« ®5l + - 4 2k+- Kбпц.к-1 где AJ,,..,AHJ- элементы векторовстолбцов;1, В 1дцц.4 элементы сим{4етричных матриц; С 1 -jCn элементы вектора результата. Цель изобретения - сокращение аппаратурных затрат при вычислении суммы векторов, каждый из которых представляет произведение симметричной матри1ц 1 на соответствукяций вектор столбец. Поставленная цель достигается тем, что вычислительное устройство, содержащее два блока памяти, k умножителей, сумматор и микропрограммньй блок управления, причем первый вход устройства соединен с информационным входом первого блока памяти,выходы которого соединены с первыми входаш соответствующих утегожителей, выходы сумматора соединены соответственно с информационными входами второго блока памяти, выходы которого являются выходами устройства и соединены с первой группой информационных входов ;сумматора, выходы микропрюгршумного блока управления, с первого по третий, соединены соответственно с управляющими входами первого и второго блоков памяти и сумматора, содержит регистр, блок задержки, причем второй вход устройства соединен с информационным входом регистра, выход которого соединен с вторым входом первого умножителя и информагщониым входом блока задержки, выхода которого с первого по (k-1)-й соединены соответственно с вторыми входами умножителей, со второго по k-й, выходы умножителей соединены с второй группой информационных входов сумматора, управляющие входы регистра и блока задержки соединены соответственно с четвертым и пятым выходами М11кропрограммного блока управления. Блок задержки содержит (k-l) груп по п триггеров в каждой (п-число разрядов, на которое производится умножение), k-2 элемента задержки, элемент И, генератор импульсов, три гер управления, причем управляющий вход блока задержки соединен- с уставновленным входом триггера управления, выход кбторого соединен с первым входом элемента И, второй вхо которого соединен с выходом генерато ра импульсов, входы триггеров первой группы соединены с информационным входом блока задержки, выходы триггеров каждой из групп соединены с соответствующим выходом блока задержки и входами триггеров последующей группы, входы синхронизации три геров групп с первой по Xk-2)-ю соединены соответственно с выходами соответствующих эле ентов задержки, выходы каждого из которых соединены с выходом последующего элемента задержки, входы синхронизации (k-l)-A группы триггеров соединены с входом )-ro элемента задержки и выходом элемента И. На ййг. 1 представлена схема вычислительного устройства; на Лиг. 2 схема блока задержки; на Лиг. 3 пример реализации схемы блока управ,ления. Вычислительное устройство содержи первый блок 1 памяти, первый вход 2 устройства, блок 3 задержки, регистр 4, второй вход 5 устройства, умножители 6, сумматор 7, второй блок8 памяти, ткропрограммный блок 9 управления. Блок 3 задержки содержит триггеры 10, элементы 11 задержки, элемент И 12, генератор 13 импульсов, триггер управления 14. Блок 9 содержит блок 15 памяти, регистр 16 адреса, генератор 17, регистр 18 микрокоманд, дегаифратор 19, счетчик 20. Блок 3 задержки работает следующим образом. Работа осуществляется по тактам, формируемым внутренним генератором 13, Частота следования импульсов с генератора 13 определяет ся временем, необходимым сумматору 7 для сложения двух чисел. Триггер 14управления устанавливается во время пуска первого умножителя 6, сбрасывается при приеме всего множителя на k-й умножитель 6 .при условии отсутствия очередного запуска первого умножителя. Тактирующие сигналы записи в 1,2,,., k-2 линейки триггеров образуются на 1, 2,..,. k-2..4 J k-2 элементе задержки . ветственно. Каждый элемент задержки задерживает тактирующий сигнал на соответствующую группу триггеров на время, необходимое триггерам следующей rpynra i для записи информации. Примером блока задержки может служить набор сдвиговых регистров, Кпок 9 работает следующим образом. В счетчике 20 устанавливается количество тактов работы устройства. По начальному адресу, установленному в регистре 16 адреса из блока 15памяти считывается первая микрокоманда, поступакидая на вход регистра 18 микрокоманд. При наличии импульса от генератора 17 осуществляется путем микрокоманды на регистр 18 микрокоманд, откуда микрокоманда поступает на дегтайфатор 19, вырабатывающий совокупность управляющих сигналов. Далее под воздействием описанного выше синхроимпульса из содержимого счетчика вычитается единица. На второй вход регистра 16 адреса с выхода регистра микрокоманд поступает адрес следующей микрокоманды. Процесс продолжается до тех пор пока счетчик 20 не установится на нуль. Вычислительное устройство работает следуюрщм образом, н.: в исходном состоянии блок I, реги тр 4, блок 3 задержки и блок 8 обнулены. По входу 2 на вход блока 1 подается множимое AJ, а на вход регистра 4 по входу 5 - множитель В;(. После того, как множимое и множитель зафиксируются соответственно в первой ячейке блока 1 и регистре 4, начинает работать первый умножитель 6, а содержимое регистра 4 поступает на блок 3 задержки, в котором задержка между двумя последовательными выходами определяется временем, необходимым для работы сумматора 7, на такое же время задерживается и пуск . каждого очередного умножителя, снязанного с соответствующим выходом блока 3 задержки, а следовательно, задерживается н момент получения результатов умножения с очередного умножителя. В результате первого умножения на выходе 5 первого умножителя 6 получается произведение вида A;fB, которое поступает на вход сумматора 7, где оно в первом такте слагается с содержащимся в первой ячейке блока 8 нулем О Результат сложения фиксируется в той же ячейке блока 8. Через время, равное такту сложения, на выходе второго умножителя 6 получается произведение вида O-BJ, которое суммирует- 5 ся на сумматоре 7 с содержащимся во второй ячейке блока 8 нулем и фиксируется в той же ячейке блока 8. Аналогичная процедура повторяется и для каждого последующего умножителя. 20 Т.е. произведения с выходов умножителей поступают на вход сумматора 7 с интервалом, равным циклу одного сложения сумматора 7 и задаваемому блоком 3 задержки,25

Во время работы первого умножите ля 6 содержимое блока 1 сдвигает- , ся на одну ячейку, т.е. множимое Af перемещается во вторую ячейку блока 30 1, а по входам 2 и 5 считывается следующая пара операндов (А j и Bg) которая к моменту окончания работы

первого умножителя 6 фиксируется соответственно в первой ячейке блока 1 и в регистре 4. Первый умножитель 6 начинает новый цикл умножения, результатом которого является произведение А2гВ2. Следует отметить, что к моменту подачи этого произведения на вход сумматора 7, на выходе его должна уже быть сумма , которая фиксируется в k-й ячейке блока 8. На сумматоре 7 произведение АоВ суммируется с суммой , хранящейся в первой ячейке блока 8, и фиксируются в той же ячейке этого блока. В это времяс выхода второго умножителя 6 на вход сумма.тора 7 поступает произведение , которое суммируется с хранящейся во второй ячейке блока 8 суммой 0+0-Б, и результат запоминается во второй ячейке блока 8 К моменту записи результата суммирования во вторую ячейку на вход сумматора 7 поступает произведение с третьего умножителя. Далее описанньш процесс повторяется до тех пор, пока не будет исчерпан весь массив множителей.

Технико-экономический эффект изобретения по сравнению с прототипом состоит н замене двух бгюков памяти на требующие существенно меньших аппаратурных затрат регистр и блок задержки.

i

гг

/ / /

/5

20

/5

-)

Ц

/9

4 fff

Фиг.д

| I | |||

| Заявка ФРГ № 2855722, кл,Q 06 Р 7/52, опублик | |||

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для устранения мешающего действия зажигательной электрической системы двигателей внутреннего сгорания на радиоприем | 1922 |

|

SU52A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

Авторы

Даты

1983-11-30—Публикация

1981-12-14—Подача