; ,2тЗОЗПг353ЧУ5ХЛУ539

J3 гп и Н t t J М ( и 7 2it

л фие.

15

J М

л фие.

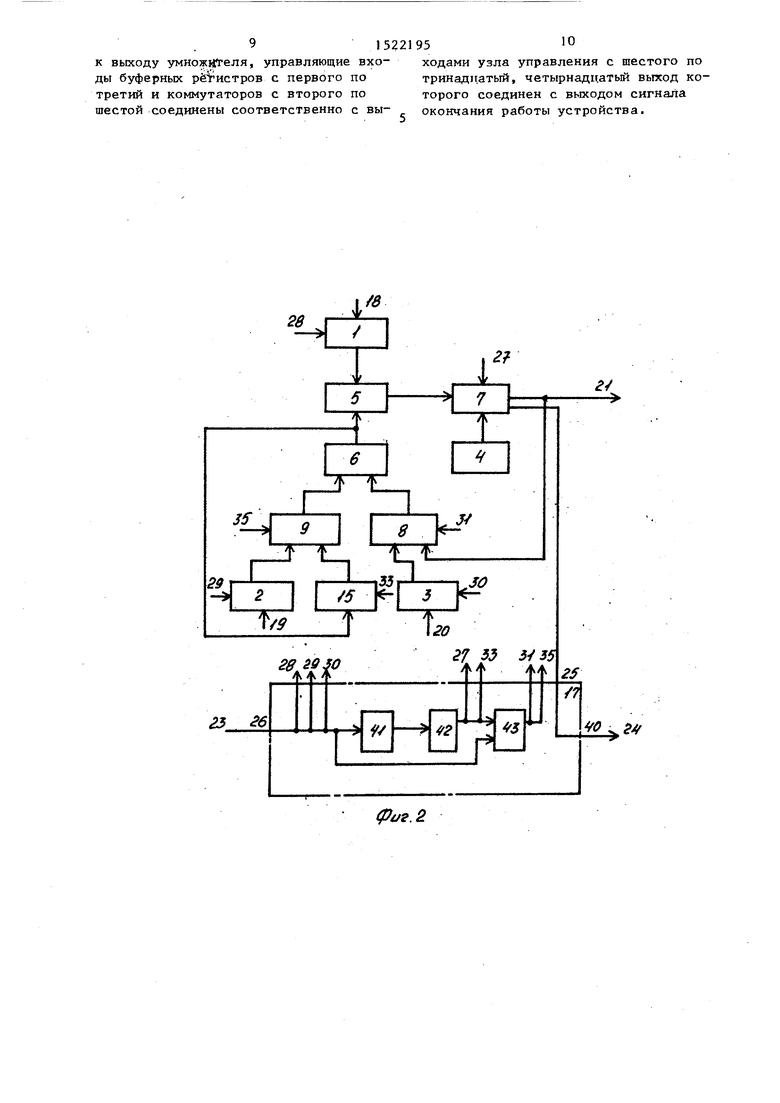

Изобретение относится к вычислительной технике и может быть использовано в качестве операционного бпо- ка в специализированных вычислителях различного назначения.

Цель изобретения - расширение Функциональных возможностей за счет возможности выполнения произвольной операции, являющейся суперпозицией операций умножения ,.деления и извлечения квадратного корня, над тремя переменными.

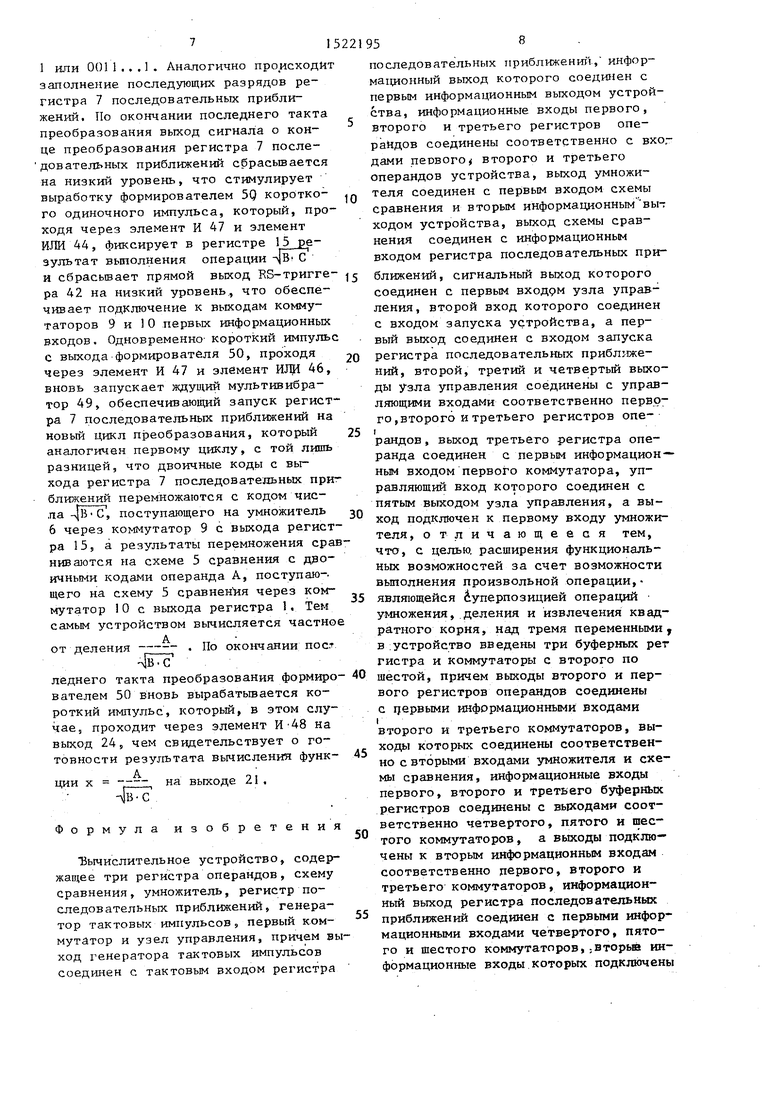

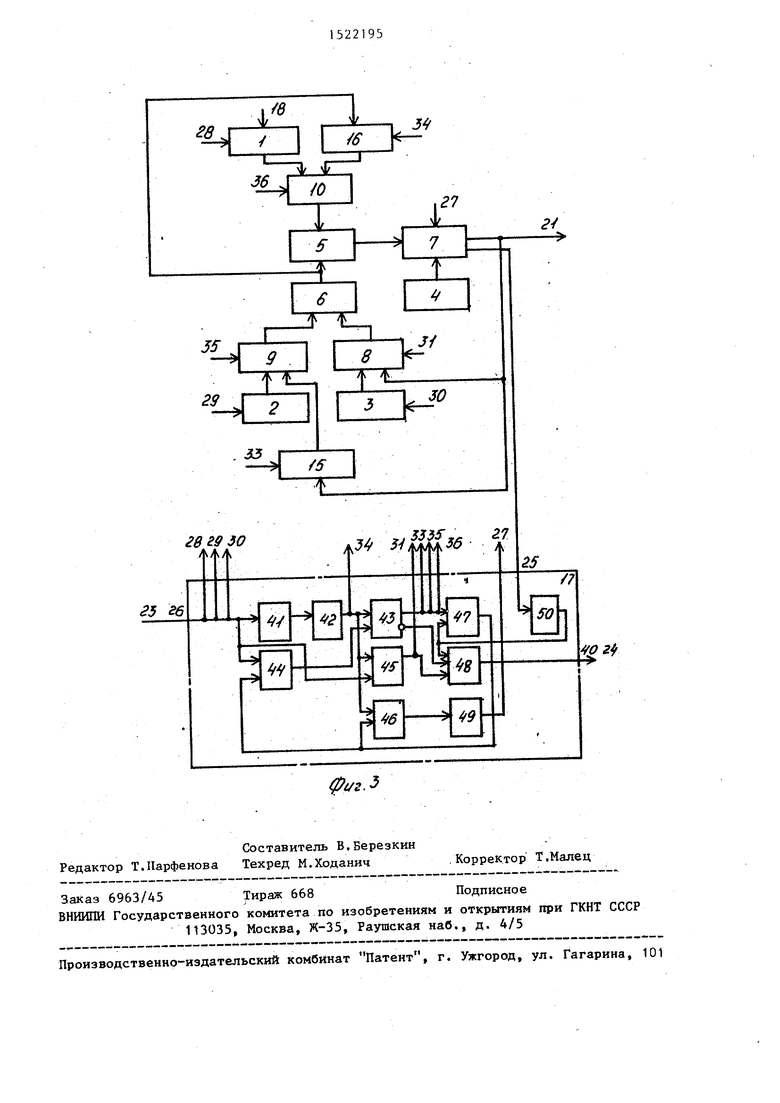

На фиг.1 показана функциональная схема предлагаемого вычислительного устройства: на фиг.2 - схемй устрой- ств а, осуществляющего операцию

А

ёТГ

на фиг.3 - схема устройства,

X

осуществляющего операцию

А

Устройство содержит регистры 1-3 операндов, генератор 4 тактовых импульсов, схему 3 сравнения, умножитель 6, регистр 7 последовательных приближений, коммутаторы 8-1.3, буферные регистры 14-16, узел 17 управления, :вх6ды; 18 - 20 операндов А,В, С, информационные выходы 21 и 22, вход 23 запуска, выход 24 сигнала окончания работы. Узел 17 имеет входы 25 и 26 и выходы 27-40.

По входам 18 - 20 в устройство вводятся три операнда А,В,С. Устройство способно с помощью соответствующих коммутаций осуществлять операции умножения, деления и извлечения квадт ратного корня и осуществлять их промежуточное запоминание в регистрах 14- 16. Ддя осуществления умножения операнды с помощью соответствующих управляющих сигналов кoммyтиpyюfcя на умножителя 6, а результат снимается с выхода 22. Для осуществления . деления делимое коммутируется на один вход схемы 5 сравнения, на другой вход которой поступает с выхода умножителя 6 произведение скоммутиро- ванных на его входы делителя и кода с выхода регистра 7, результат формируется на выходе 21. Дпя осуществления извлечения квадратного корня подкоренное значение коммутируется на , один вход схемы 5 сравнения, на другой вход которой поступает с выхода умножителя 6 квадрат значения кода регистра 7, скоммутированного на оба

его входа. Узел 17 может быть выполнен как микропрограммно, так и аппа- ратно. При реализации конкретных функций часть оборудования может быть исключена, как избыточная. Более подробно работа устройства показана на примере реализа11;ии .двух конкретных АА

- -- и -v ВлС

функций X

;- их -

5

0

5

0

5

0

45

50

5

УстройствоJреализующее функцию изображено на фиг.2. Как

А

iTc

видно из сравнения с общей схемой (фиг.1),из него исключены избыточные. в данном случае коммутаторы 10-13, регистры 14 и 16 и соответствующие i им управляющие сигналы. Узел 17 содержит ждущий мультивибратор 41, формиг рователь 42 импульса и триггер 43.

Устройство работает следующим образом.

Передний фронт импульса запуска с входа 23 приводит устройство в исходное состояние, устанавливая на вы-- ходе RS-триггера 43 высокий уровень сигнала. При этом обеспечивается подк почение к выходам коммутаторов 8 и 9 их первых информационных входов. Одновременно передний фронт импульса запуска фиксирует в регистрах 1-3 значения двоичных кодов соответствен- но операндов А, В и С.

Задним фронтом импульса запуска запускается ждущий мультивибратор 41 j формирующий импульс, длительность которого должна быть не меньше времени до появления результата операции на выходе умножителя 6. По заднему фронту импульса с выхода ждущего мультивибратора 41 формирователем 42 .вырабатьшается короткий одиночный импульс, длительность которого должна быть не меньше периода тактовых импульсов генератора 4. Этот импульс своим передним фронтом фиксирует результат операции в ре-: гистре 15 и сбрасьгоает выход триггера 43 на низкий уровень сигнала, чем обеспечивается подключение к выход коммутаторов 8 и 9 их вторых информационных входов. Кроме того, появление указанного импульса на входе запуска регистра 7 последовательных приближений обеспечивает его запуск на цикл работы. Причем, в момент запуска выход сигнала о конце преобразования регистра 7 последова

5J

тельных приближ1ений уотанавливается на высокий уровень. Затем за число тактов, на единицу большее числа разрядов регистра 7 последовательньк приближений, осуществляется выполАнение операции -;г

D L.

На первом такте производится умножение двоичного числа 01I...1, посту пающего на вход умножителя 6 с выхода регистра 7 последовательных приближений, на число В«Су код которого поступает на вход умножителя 6 с выхода регистра 15. Результат указанной операции сравнивается на схеме 5 сравнения с двоичным кодом числа А, поступающего на схему 5 сравнения с выхода регистра 3.

Результат сравнения поступает на информационный вход регистра 7 после довательных приближений и в начале второго такта записьшается в его старший разряд, при этом следуняций .разряд устанавливается в нуль, т.е на выходе регистра 7 последовательных приближений устанавливается двоичный код в зависимости от результата сравнения 1011 ... 1 или 001 1 ... 1 . Аналогично происходит заполнение последующих разрядов регистра 7 последовательных приближений.

По окончании последнего такта преобразования выход сигнала о конце преобразования регистра 7 последова- тельных приближений сбрасывается на низкий уровень, что сввдетельствует о готовности результата вычисления

функции X V

на выходе 21.

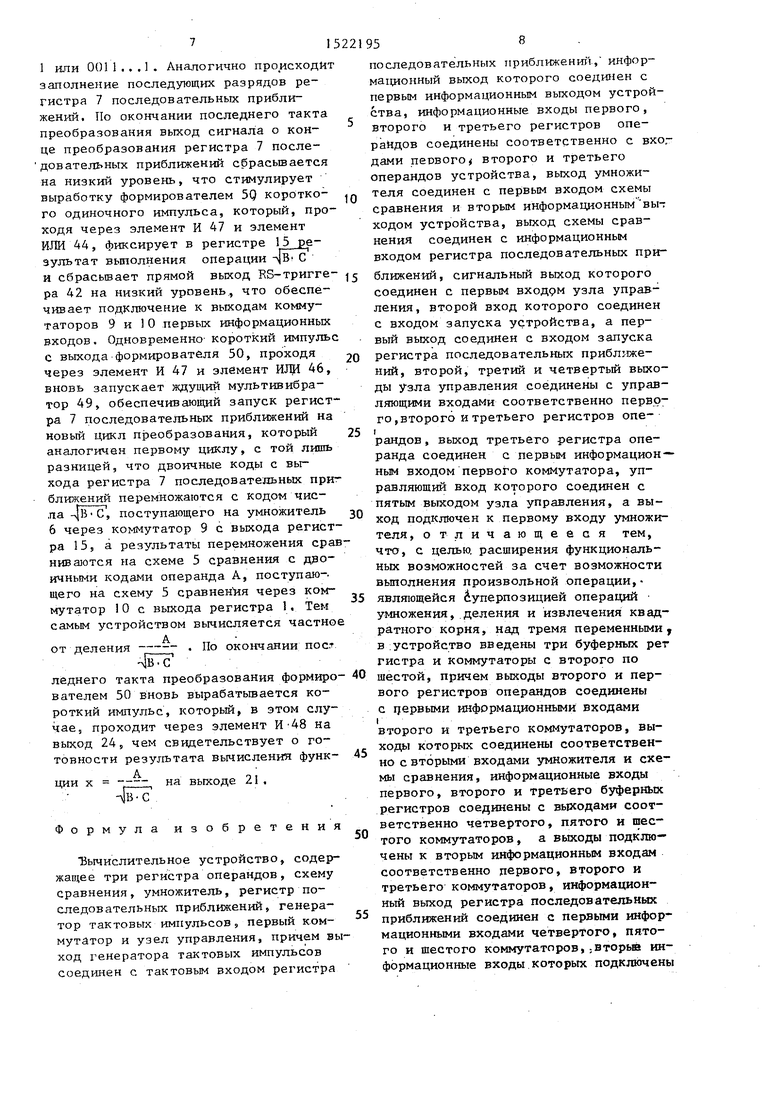

Устройство, реализующеефункцию

А X -ггп, показано на фиг.З. Как

л|В С

видно из сравнения с общей схемой (фиг.1), из него исключены избыточные в данном случае коммутаторы 11 - 13, регистр 14 и соответствующие им управляющие сигналы. Увел 17 содержит ждущий мультивибратор 41, формирователь 42 импульса, триггер 43, элемент ИЛИ 44, триггер 45, элемент ШШ 46, элементы И 47 и 48, ждущий мультивибратор 48, формирователь 50 импульсов

Устройство работает следующим образом.

Передний фронт сигнала запуска по входу 23 приводит устройство в ис

15

21

5

20

0

5

0

5

956

ходное состояние, сбрасьгоая прямой выход RS-триггеров 43 и 45 на низкий уровень сигнала. При этом коммутаторами 8-10 обеспечивается подключение к их выходам первых информационных входов. Задний фронт сигнала запуска, поступая на управляющие входы регистров 1-3, фиксирует в них соответственно значения двоичных кодов

операндов А,С и В. Этим же задним фронтом сигнала запуска запускается ждущий, мультивибратор 41, длительность формируемого импульса которого должна быть не меньше времени до появления результата операций на выходе умножителя 6. По заднему фронту импульса с выхода ждущего мультивибратора 41 формирователем 42 выра- батьюается короткий одиночный импульс, фиксирующий результат операции В-С в регистре 16. При этом на прямом выхог; де RS-триггеров 43 и 45 устанавливается высокий уровень сигнала, который обеспечивает подключение к выходам коммутаторов 8-10 вторых информационных входов, а также запускается ждущий мультивибратор 49, которым формируется импульс, длительность которого должна быть не меньше периода тактовых импульсов генератора 4, Последнее обеспечивает запуск регистра 7 последовательных приближений на цикл работы. Причем, в момент за- пуск выход сигнала о конце преобразо- . вания регистра 7 последовательньгх приближений устанавливается на высокий уровень. Затем за число тактов,

на единицу большее числа разрядов регистра 7 последовательных приближений, осудаствляется выполнение операции С. На первом такте осуществляется возведение в квадрат двоичного числа СП ... 1 , поступающего с выхода регистра 7 последовательных приближений через коммутаторы 8 и 9 на входы умножителя 6, и сравнение результата указанной операции на схеме 5 сравнения с двоичным кодом числа В С, поступающего на схему 5 сравнения через коммутатор 10 с регистра 16.

Результат сравнения поступает на информационный вход регистра. 7 последог вательных приближений и в начале второго такта записьюается в его старший разряд, при /этом следующий разряд устанавливается : в нуль, . устанавливается двоичный код в зависи- -мости от результата сравнения 1011...

1

1 или 0011 ... 1. Анапогично происходит заполнение последующих разрядов регистра 7 последовательных приближений. По окончании последнего такта преобразования выход сигнал;а о конце преобразования регистра 7 последовательных приближений сбрасьшается на низкий уровень, что стимулирует выработку формирователем 5Q коротко- го одиночного импульса, который, проходя через элемент И 47 и элемент ИЛИ 44, фиксирует в регистре 15 ре- зультат выполнения операции В С и сбрасывает прямой выход RS-тригге- ра 42 на низкий уровень., что обеспечивает подключение к выходам коммутаторов 9 и 10 первых информационных входов. Одновременно- короткий импульс с выхода формирователя 50, проходя через элемент И 47 и элемент ИШ 46, вновь запускает ждущий мультивибратор 49, обеспечивающий запуск регистра 7 последовательных приближений на новый цикл преобразования, который аналогичен первому циклу, с той лишь разницей, что двоичные коды с выхода регистра 7 последовательных при ближений перемножаются с кодом числа -цВ с , поступающего на умножитель 6 через коммутатор 9 с выхода регистра 15, а результаты перемножения сравниваются на схеме 5 сравнения с двоичными кодами операнда А, поступаю-, щего на схему 5 сравнен я через коммутатор 10 с выхода регистра 1. Тем самым устройством вычисляется частное А

от деления

По окончании пост

леднего такта преобразования формиро- вателем 50 вновь вырабатьгоается короткий импульс, который, в этом случае, проходит через элемент И 48 на выход 24, чем свидетельствует о готовности результата вычисления функ-

А.„,

ции X -- на выходе 21 .

,.

Формула изобретения

Вычислительное устройство, содержащее три регистра операндов, схему сравнения, умножитель, регистр последовательных приближений, генератор тактовых импульсов, первый коммутатор и узел управления, причем выход генератора тактовых импульсов соединен с тактовым входом регистра

8

Q

0

5

0

5

0 45

.

0

5

последовательных приближений, инфор- матщонный выход которого соединен с первым информационным выходом устройства, информационные входы первого, второго и третьего регистров операндов соединены соответственно с вхо,- дами первого второго и третьего операндов устройства, выход умножителя соединен с первым входом схемы сравнения и вторым информационным выт ходом устройства, выход схемы сравнения соединен с информационным входом регистра последовательных приближений, сигнальный выход которого соединен с первым входрм узла управления, второй вход которого соединен с входом запуска устройства, а первый выход соединен с входом запуска регистра последовательных приближений, второй, третий и четвертый выходы узла управления соединены с управляющими входами соответственно первого,второго и третьего регистров операндов , вьгход третьего регистра операнда соединен с первым информационным входом первого коммутатора, управляющий вход которого соединен с пятьм выходом узла управления, а выход подключен к первому входу умножителя, отличающееся тем, что, с целью, расширения функциональных возможностей за счет возможности выполнения произвольной операции, являющейся Суперпозицией операций умножения,.деления и извлечения квадратного корня, над тремя переменными, в ;устройство введены три буферных рет гистра и коммутаторы с второго по шестой, причем выходы второго и первого регистров операндов соединены с цервыми информационными входами

второго и третьего коммутаторов, выходы которых соединены соответственно с вторыми входами умножителя и схемы сравнения, информационные входы первого, второго и третьего буферных регистров соединены с вьрсодами соответственно четвертого, пятого и шестого коммутаторов, а выходы подключены к вторым информационным входам соответственно первого, второго и третьего коммутаторов, информационный выход регистра последовательных приближений соединен с первыми информационными входами четвертого, пятого и шестого коммутаторов,:Вторьш информационные входы которых подключены

9152219510

к выходу умножителя, управляющие вхо- ходами узла управления с шестого по ды буферных регистров с первого потринадп.атый, четырнадцатый выход котретий и коммутаторов с второго поторого соединен с выходом сигнала

шестой соединены соответственно с вы- окончания работы устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации быстрого преобразования Хартли | 1987 |

|

SU1444815A1 |

| Устройство для формирования и обработки гистограмм | 1989 |

|

SU1755296A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Устройство для извлечения квадратного корня | 1987 |

|

SU1425662A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1988 |

|

SU1640709A1 |

| Преобразователь кода | 1989 |

|

SU1619401A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для автоматического измерения параметров радиоприемников | 1990 |

|

SU1732302A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Вычислительное устройство | 1986 |

|

SU1322271A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве операционного блока в специализированных вычислителях различного назначения. Цель изобретения - расширение функциональных возможностей за счет возможности выполнения произвольной операции, являющейся суперпозицией операции умножения, давления и извлечения квадратного корня, над тремя переменными. Устройство содержит регистры 1-3 операндов, генератор 4 тактовых импульсов, схему 5 сравнения, умножитель 6, регистр 7 последовательных приближений, коммутаторы 8-13, буферные регистры 14-16, узел управления, входы 18-20 операндов, информационные выходы 21, 22, вход 23 запуска, выход 24 сигнала окончания работы. Узел 17 имеет входы 25, 26 и выходы 27-40. 3 ил.

(ра2.2

J

/

| Вычислительное устройство | 1979 |

|

SU794635A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения-деления | 1985 |

|

SU1249509A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1989-11-15—Публикация

1987-01-19—Подача