вертого элементов И, выход элемента ИЛИ соединен с входом второго о ранда сумматора, второй и третий входы пятого элемента И соединены соответственно с выходом элемента и выходом второго регистра сдвига. 2. Устройство по п. 1, отли чающееся тем, что тактователь импульсов содержит два элемен та И-НЕ. элемент ИЛИ, два элемеита НЕ, причем информационный вход тактователя импульсов соединен с п вым входом элемента ИЛИ и первым 43 входом первого элемента И-НЕ, выход которого соединен через первьй элемент НЕ с вторым викодом тактователя импульсов, первый выход которого соединен с выходом второго элемента И-НЕ и вторым входом первого элемента И-НЕ, выход которого соединен с первым входом второго элемента И-НЕ, второй вход которого соединен с выходом элемента ИЛИ, второй вход которого СОРчинен с выходом втопого элемента irE, вход которого соединен с управляющим входом тактователя импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Квадратор | 1983 |

|

SU1180885A1 |

| Квадратор | 1985 |

|

SU1258826A2 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Устройство для вычисления суммы квадратов трех величин | 1988 |

|

SU1580356A1 |

| Квадратор | 1986 |

|

SU1322273A1 |

| Устройство для контроля экспоненциальных процессов | 1987 |

|

SU1500997A1 |

| Интегро-дифференциальный вычислитель | 1983 |

|

SU1108445A2 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1168930A1 |

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА ПЕРЕДАЧИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 1986 |

|

SU1840556A2 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1228290A1 |

1. УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ПОЛИНОМА ВТОРОЙ СТЕПЕНИ, содержащее первый и второй регистры сдвига, сумматор, два элемента И, элемент ИЛИ, элемент задержки, триггер, блок синхронизации, причем инверсный выход триггера соединен с первым входом первого элемента И, вторбй вход которого соединен с выходом элемента ИЛИ, первый вход которого соединен через элемент задержки, с прямым выходом триггера, выход второго регистра сдвига соединен с вторым входом элемента ИЛИ и входом сброса триггера, выход первого элемента И соединен с входом сдвига второго регистра сдвига, выход первого регистра сдвига соединен с входом первого операнда сумматора, выход которого соединен с входом сдвига первого регистра сдвига, первый вход блока синхронизации соединен с входами синхронизации первого и второго регистров сдвига, входы сброса которых соединены с вторым выходом блока синхронизации, третий вход которого соединен с первым входсж второго элемента И, отличающееся тем, что, с целью сокращения объема оборудования, в него введены два формирователя импульсов, два тактователя импульсов, второй и третий элементы ИЛИ, третий, четвертый и пятый элементы И, элемент НЕ, элемент задержки, причем четвертый выход блока синхронизации соединен с управляющими входами первого и второго формирователей импульсов, информационные входы которых соединены соответственно с первым и вторым информационными входами устройства, выход первого формирователя импульсов соединен с первыми входами второго элемента ИЛИ и третьего элемента И, вторые входы которых соединены с вы(Л ходом второго формирователя импуль- сов, выходы второго элемента ИЛИ и третьего элемента И соединены соответственно, с управляющими входами первого и второго тактователей импульсов, информационные входы первого и второго тактователей импульсов соединены с пятым выходом блока синсо и хронизации, выход второго регистра сдвига соединен через второй элемент задержки с первым входом четвертого О9 элемента И, второй вход четвертого элемента И соединен с вторым входом второго элемента И, с входом элемента НЕ и первым выходом второго тактователя импульсов, второй выход которого соединен с информационным входом триггера, выход первого тактователя импульсов соединен с первым входом пятого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, второй и третий входы которого соединены соответственно с выходами второго и чет

1

Изобретение относится к автоматике и вычислительной технике и предназначено для возведения в квадрат либо для умножения двух величин, представленных в цифровой или аналоговой форме представления информации

Известен квадратор, содержащий два регистра сдвига, сумматор, два элемента задержки, триггер, два элемента ИЛИ и элемент И l ).

Недостаток такого устройства ограниченность функциональных возможностей, так как оно не позволяет вьтолнить умножение двух величин, представленных в цифровой или аналоговой форме представления информации

Наиболее близким к предлагаемому по технической сущности является устройство для вычисления полинома второй степени, содержащее первый и второй регистры сдвига, сумматор, два элемента И, элемент ИЛИ, элемент задержки, триггер, блок синхронизации, причем инверсный выход триггера соединен с первым.входом первого эле мента И, второй вход которого соединен с выходом элемента ИЛИ, первый вход которого соединен через элемент задержки с прямым выходом триггера, выход второго регистра сдвига соединен с вторым входом, элемента ИЛИ и входом сброса треггера, выход первого элемента И соединен с входом сдвига второго регистра сдвига, выход первого регистра сдвига соединен с входом первого операнда сумматора, выход которого соединен с входом сдвига первого регистра сдвига, первый выход блока синхронизации соединен с входами синхронизации первого и второго регистров сдвига, входы сброса которых соединены с вторым выходом блока синхронизации, третий выход которого соединен с первым входом второго элемента И 2.

Недостатком известного устройства является большой объем оборудования.

Цель изобретения - сокращение объема оборудования.

Поставленная цель достигается тем, что в устройство, содержащее первый и второй регистры сдвига, сумматор, два элемента И, элемент ИЛИ, элемент задержки, триггер, блок синхронизации, причем инверсный выход триггера соединен с первым входом первого элемента И, второй вход которого соединен с выходом элемента ИЛИ, первый вход которого соединен через элемент задержки с прямым выходом триггера, выход второго регистра сдвига соединен с вторым входом элемента ИЛИ и входом сброса триггера, выход первого элемента И соединен с входом сдвига второго регистра сдвига, выход первого регистра сдвига соединен с входом первого операнда сумматора , выход которого соединен с входом сдвига первого 1егистра сдвига, первый выход блока синхронизации соединен с входами синхронизации первого и второго регистров сдвига, входы сброса которых соединены с вторым

выходом блока синхронизации, третий выход которого соединен с первым входом второго элемента И, введены два формирователя импульсов, два тактователя импульсов, второй и третий 5 элементы ИЛИ, третий, четвертый и пятый элементы И, элемент НЕ, элемент задержки, причем четвертый выход блока синхронизации соединен с управляющими входами первого и второго форми- О рователей импульсов, информационные входы которых соединены соответственно с первым и вторым информационными входами устройства, выход первого формирователя импульсов соединен с пер- 5 выми входами второго элемента ИЛИ и третьего элемента И, вторые входы которых соединены с выходом второго формирователя импульсов, выходы вторЬго элемента ИЛИ и третьего элемен- 20 та И соединены соответственно с управляющими-входами первого и второго тактователей импульсов, информационные входы первого и второго тактователей импульсов соединены с пятым выхо- 25 ды 30-34,

дом блока синхронизации, выход второго регистра сдвига соединен через второй элемент задержки с первым входом четвертого элемента И, второй вход четвертого элемента И соединен с вторым входом второго элемента И, с входом элемента НЕ и первым выходом второго тактователя импульсов, второй вькод которого соединен с информационным входом триггера, выход первого тактователяимпульсов соединен с первым входом пятого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, второй и третий входы которого соединены соответственно с выходами второго и четвертого элементов И, выход элемента ИЛИ. соединен с входом второго операнда сумматора, второй и третий входы пятого элемента И соединены соответственно с выходом элемента НЕ и выходом второго регистра сдвига.

Кроме того, тактователь импульсов содержит два элемента И-НЕ, элемент ИЛИу два элемента НЕ, причем информационный вход тактователя импульсов соединен с первым, входом элемента ШШ и первым входом первого элемента И-НЕ, выход которого соединен через первый элемент НЕ с вторым выходом тактователя импульсов, первый выход которого соединен с выходом второго, элемента И-НЕ и вторым входом первогЬ элемента И-НЕ, выход которого соединен с ч

первым входом второго элемента И-НЕ, второй вход которого соединен с выходом элемента ИЛИ, второй вход которого соединен с выходом второго элемента НЕ, вход которого соединен с управляющим входом тактователя импульсов,

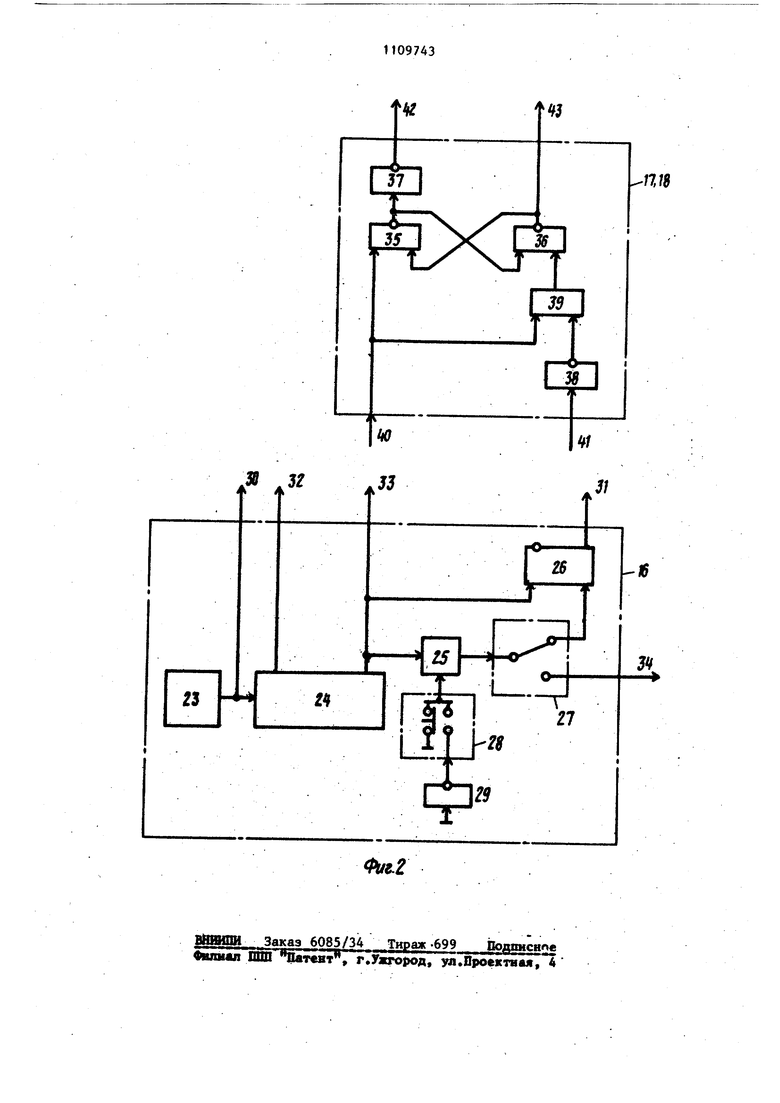

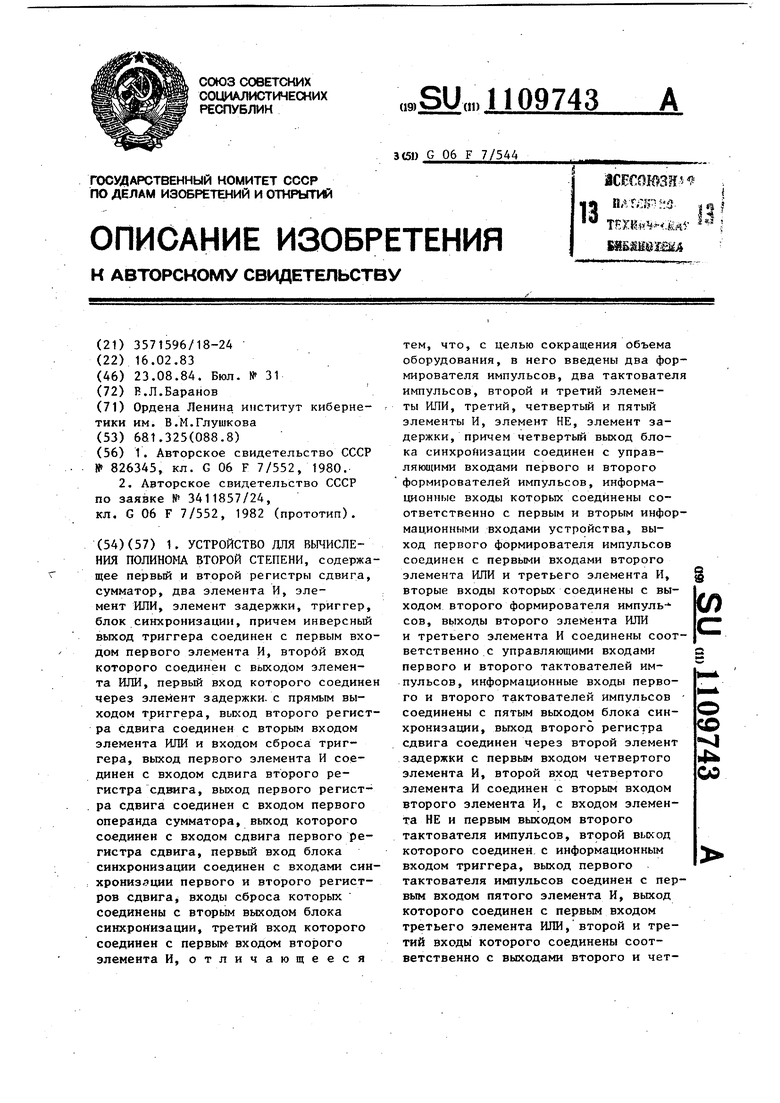

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - структурная схема блока синхронизации и тактователя импульсов.

Устройство содержит регистры 1 и 2 сдвига, сумматор 3, триггер 4, элементы ИЛИ 5-7, элементы И 8-12, элементы 13 и 14 задержки на такт, элемент НЕ 15, блок 16 синхронизации, тактователи 17 и 18 импульсов, формирователи 19 и 20 импульсов, информационные входы 21 и 22 устройства.

Блок синхронизации содержит генератор 23 тактовых импульсов, распределитель 24 импульсов, генератор 25 одиночных импульсов, триггер 26,

коммутаторы 27 и 28, элемент НЕ 29, выхоТактователи 17 и 18 импульсов содержат элементы И-НЕ 35 и 36, элементы НЕ 37 и 38, элемент ИЛИ 39, информационный вход 40, управляющий вход 41 и выходы 42 и 43.

Устройство работаетследующим образом,

В исходном состоянии коммутатором 27 блока 16 синхронизации подключают выход генератора 25 одиночных импульсов к информационному входу триггера 26, Генератор 23 тактовых импульсов блока 16 синхронизации формирует последовательность тактовых импульсов, из которых п-разрядный распределитель 24 импульсов формирует п последовательностей импульсов, длительностью 1/f, периодом и сдвинутых один относительно другого на время , где f - частота- тактовых импульсов генератора 23 тактовых импульсов, п - количество разрядов регистров 1 и 2 сдвига. Кот-п утатором 28 подают сигнал логической единицы с выхода элемента НЕ 29 на вход запуска, генератора 25 одиночных импульсов, на выходе которого выделяется одиночный импульс из последовательности п-го разряда распределителя 24 импульсов. Выходной импульс генератора 25 одиночных импульсов через коммутатор 27 поступает на информащ1онный вход триггера 26 устанавливая его в единичное состояние. Сигнал логической единицы прямого выхода три гера 26 поступает на входы управлен регистров 1 и 2 сдвига, которые под действием тактовых импульсов, посту щих с первого выхода блока 16 синхр низации, устанавливаются в нулевое состояние, поскольку на их входе.вв да данных действует сигнал логического нуля. Триггер 4 устанавливается в нулевое состояние нулевым сигналом сдвигаемым с выхода регистра 2 сдвига. Таким образом, р исходной состоя нии регистры 1 и 2 сдвига, а также триггер 4 находятся в нулевом состоянии. Режим вычислений устанавливается коммутатором 27 путем подключения выхода генератора 25 одиночных импульсов к входам запуска формирователей 19 и 20 импульсов. Вычисления к квадраторе-умножителе начинаются после запуска с помощью коммутатора 28 генератора 25 одиночных импульсов, выходной импульс которого запускает формирователи 19 и 20 импульсов. На выходах формирователей 19 и 20 импульсов формируются импульсы, длительность которых пропорциональна сигналам (аналоговым или цифровым), действующим на информационных входах 21 и 22 устройства. Если длительность выходных импуль сов формирователей 19 и 20 импульсов различна, то наибольший по длительности импульс выделяется на выходе . элемента ИЛИ 7, а импульс меньшей длительности - на выходе элемента И 12, под действием которого тактователь 17 импульсов формирует из последовательности импульсов п-го разряда распределителя 24 импульсов пачку импульсов, количество которых пропорционально наименьшей величине действующей на одном из информационных входов 21 и 22 устройства, а также импульс, стробирующий эту пачку импульсов. Стробирующий импульс тактователя 17 импульсов открывает элементы И 9 и 10, а также через элемент НЕ 15 блокирует элемент И 1 Пачка импульсов с импульсного выхода тактователя 17 импульсов поступает на информационный вход триггера 4. Первьй импульс пачки устанавливает в единичное состояние триггер 4 в п-м такте (соответствуницем сдвигу п-х разрядов кодов с выходов регистров 1 и 2 сдвига). Установка триггера 4 в единичное, состояние приводит к формированию на его инверсном выходе нулевого сигнала, блокирующего элемент И 8, а на прямом выходе - единичного сигнала, который спустя время задержки элементом 13 задержки на такт начинает действовать через элемент ИЛИ 5 на первом входе элемента И 8. Под действием .тактовьк импульсов первого выхода .блока 16 синхронизации с выхода регистра 2 сдвига в первом такте сдвигается младший разряд начального нулевого кода, сигнал которого поступает на инверсный вход.сброса триггера 4 и устанавливает его в нулевое положение. В нулевом состоянии на инверсном выходе триггера 4 формируется единичный сигнал, который снимает блокировку элемента ИЗ. Благодаря задержке элементом 13 задержки на такт сигнала прямого выхода триггера 4 на входе элемента И 8 формируется импульсный сигнал, который в первом такТе записывается в качестве младшего разряда кода в регистр 2 сдвига под действием тактовых импульсов первого выхода блока 16 синхронизации. В течение первого такта выходной сигнал первого разряда распределителя 24 импульсов, действующий на третьем выходе блока 16 синхронизации, поступает через элемент И 10, открытый сигналом стробирующего выхода тактователя 17 импульсов, и через элемент ИЛИ 6, сумматор 3 на информационный вход регистра 1 сдвига. Под действием тактовых импульсов первого выхода блока 16 синхронизации в первом такте в регистр 1 сдвига записывается единичный сигнал в качестве младшего разряда кода. В течение последующих тактов с второго до п-го нулевые разряды кодов с второго по п-й под действием тактовых импульсов первого выхода блока 16 синхронизации переписываются с выходов регистров 1 и 2 сдвига на их информационные входы, а единица младшего разряда кода продвигается в последний разряд регистров 1 и 2 сдвига. Таким образом,после шага вычислений в течение п тактов в регистра 1 и 2 сдвига формируются cooTBetcTBeHHo двоичные коды квадратной функции х 1 и аргумента Х;, 1. На втором и последующих шагах вычислений доокончания действия наименьшего импульсного сигнала на выходах формирователей 19 и 20 импульсов устройство формирует в регистрах 1 и 2 сдвига с ответственно двоичные коды квадратич ной функции и аргумента согласно соотношениюxf XiV2xi.,+ 1, где Xj и значения аргумента квадратичной функции на i и i-1 шагах вычислений соответственно. Например, установка триггера 4 в единичное состояние i-м импульсом пачки, действующей на импульсном выходе тактователя 17 импульсов,обеспе чивает формирование в регистрах 1 и сдвига двоичных кодов величин х 2 и X. соответственно согласно соотношению (1) следующим образом. Под действием тактовых импульсов первого выхода блока 16 синхронизации на первый вход сумматора 3 сдвигается двоичный код величины X квадратичной функции на предьщущем шаге вычислений, а с выхода регистра 2 сдвига через элемент 14 задержки на такт, элементы И 9 или 6 на второй вход сумматора 3 сдвигается двоичный код аргумента х.. Элемент 14 задержки обеспечивает сдвиг на один разряд двоичного кода х аргумента на предьщущем шаге вьшисле ний по отношению к двоичному коду функции х, сдвигаемому с выхода ре гистра 1 сдвига. Сумматор 3 формируе согласно соотношению (1) двоичный, код квадратичной функции х ; на i-м шаге вычислений, который последовательно, начиная с младшего разряда, сдвигается с выхода сумматора 3 в ре гистр 1 сдвига. Единица младшего раз ряда поступает с третьего выхода бло ка 16 синхронизации через элементы И 10, ИЛИ 6 на второй вход суммат ра 3. В это время в регистре 2 сдвига двоичный код величины х. увеличивается на единицу. Действительно, уста новка триггера 4 в едини«1ное состояние обеспечивает разрыв цепи циркуля ции кодов с выхода регистра 2 сдвига на его вход, так как элемент И 8 закрыт нулевым сигналом инверсного выхода триггера 4. Следовательно, до возврата триггера 4 в нулевое состоя ние в младшие разряды кода регистра 2 сдвига записываются нулевые сигналы. Триггер 4 возвращает в нулевое состо ние первый, начиная с младшего разря да, нулевой сигнал кода, который сдвигается с выхода регистра 2 сдвига. Переход триггера 4 из единичного состояния в нулевое приводит к формированию на выходе элемента И 8 импульсного сигнала благодаря задержке элементом 13 задержки единичного сигнала прямого выхода триггера 4 его предьщущего состояния. Следовательно, вместо сдвигаемого с выхода регистра 2 сдвига нулевого сигнала на информационный вход регистра 2 сдвига поступает единичный сигнал с выхода элемента И 8. Остальные разряды двоичного кода, сдвигаемого с выхода регистра 2 сдвига, переписываются в регистр 2 сдвига без изменения через элементы ИЛИ 5 и И 8, так как триггер 4 находится в нулевом состоянии. Таким образом, двоичный код в регистре 2 сдвига на каждом шаге вычислений увеличивается на единицу и соответствует количеству импульсов , действующих на импульсном выходе тактователя 17 импульсов. После окончания действия наименьшего импульса на выходе формирователя 19 или 20 импульсов элемент И 12 закрывается и. на выходах тактователя 17 импульсов устанавливаются нулевые сигналы. Нулевой сигнал стробирующего выхода тактователя 17 импульсов блокирует элементы И 9 и 10, а также через элемент НЕ 15 снимает блокировку элемента И 11, на третьем входе которого продолжает действовать импульс стробирующего выхода тактователя 18 до окончания действия наибольшего импульса на выходе формирователя 19 или 20 импульсов. На интервале времени от момента окончания наименьшего до момента окончания наибольшего импульса на выходах формирователей 19 и 20 импульсов устройство реализует операцию умножения двух величин согласно следующему соотношению x-a X , (2) где X - наименьший сомножитель; у - наибольший сомножитель. К моменту окончания наименьшего импульса (соответствующего наименьшему сомножителю), в регистре 1 сдвига

формируется согласно соотношению ,(1) двоичный код X квадрата наименьшего co raoжитeля, а в регистре 2 сдвига двоичный код X наименьшего сомножителя, который под действием тактовых импульсов первого выхода блока 16 синхронизации сдвигается через элементы И 11 и ИЛИ 6 на второй вход сумматора 3, где суммируется с двоичным кодом величины х, сдвигаемой с выхода регистра 1 сдвига. Двоичный код суммы, начиная с младшего разряда, под действием тактовых импульсов первого выхода блока 16 синхронизации записывается в- регистра 1 сдвига за время п тактов.

Формирование согласно соотношению (2) продолжается аналогичным образом на последующих шагах вычислений до тех пор, пока действует импульс наибольшего сомножителя на выходе формирователя 19 или 20 импульсов.

После окончания импульса наибольшего сомножителя на стробируницем выходе тактователя 18 импульсов устанавливается нулевой сигнал, блокирующий элемент И 11. Так как элементы И 9 и 10 также блокируются нулевым сигналом стробирующего выхода тактователя 17 импульсов, то на втором входе сумматора 3 действуют нулевые сигналы, а в регистре 1 сдвига динамическим способом, путем циркуляции кода через сумматор 3 фиксируется двоичный код произведения двух входных величин.

В регистре 2 сдвига запоминается динамическим способом (путем циркуляции кода через элементы ИЛИ 5 и И 8), двоичный код наименьшего сомножителя входной величины.

Тактователь 17 или 18 импульсов работает следующим образом.

На информационный вход 40 поступает последовательность импульсов, а на управляю ций вход 41 - сигнал управления.

В случае отсутствия сигнала управления на управляющем входе 41 на выходе элемента НЕ 38 устанавливается сигнал логической единицы, поступающий через элемент ИЛИ 39 на один из элемента И-НЕ 36. Во BpeMfi пдузы между импульсами на входе 33 на выходе элемента Й-НЕ 35 формируется сигнал логической единицы, который совместно с единичным сигналом вькода элемента ИЛИ 39 устанавливает на выходе элемента И-НЕ 36 сигнал логического нуля, блокирующий элемент И-НЕ 35 во время действия импульса на входе 33. Сигнал логической единиш 1 выхода элемента И-НЕ 35 поддерживает сигнал логического нуля на выходе элемента НЕ 37«

В случае действия единичного сигнала на управляющем входе 41 на выходе элемента НЕ 38 устанавливается сигнал логического нуля. Во время паузы между импульсами на входе 33 на выходе элемента ИЛИ 39 устанавливается сигнал логического нуля, формирующий на выходе элемента И-НЕ 36 единичный сигнал строба, который пропускает последовательность импульсов входа 33 через Элементы И-НЕ 35 и НЕ 37 на выход 42 тактователя 17 импульсов. В этом режиме во время действия импульса на входе 33 нулевой сигнал на выходе элемента И-НЕ 35 блокирует элемент И-НЕ 36, на выходе которого поддерживается сигнал логической единицы строба.

Предлагаемое устройство может использоваться в режиме формирования квадратичной функции, если на входы 2 Г и 22 устройства поступает один и тот же сигнал (аналоговый или цифровой). Если сигналы на входах 21 и 22 устройства различны, то оно формирует двоичный код произведения входных величин.

Использование предлагаемого устройства позволяет сократить объем оборудования по сравнению с известным устройством.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Квадратор | 1979 |

|

SU826345A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3411857/24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-23—Публикация

1983-02-16—Подача