рования слагаемых являются выходами блока формирования слагаемых, при этом блок анализа содержит триггер, суммато по модулю два, элемент И, элемент ИЛИ первые входы элемента И и сумматора по модулю два блока анализа соенинены с первым входом блока анализа, первый вход триггера блока анализа является вторым входом блока анализа, выкод триггера блока аналиаа соединен с вторыми входами элемента И и сумматора по модулю два и первым входом элемента ИЛИ блока анализа, второй вход которого является третьим входом блока анализа, а выход - первым выходом блока анализа, выходы сумматора по модулю два я элемента И блока анализа являются соответственно вторым и тре535тьйм выхоцами блока анализа, второй вход триггера блока анализа соецинен с четвертым вхоцом блока анализа. 2. Устройство по п. 1, о т л и ч а - ю ш е е с я тем, что блок формирования cm налаудвоения содержит два узла приоритета, группу элементов И и элемент ИЛИ, причем первая группа входов блока соединена с входами первого узла приоритета, вторая группа входов блока соединена с входами второго узла приоритета, оцноименные выходы первого и второго узлов приоритета соединены с входами соответствующих элементов И группы, выходы которых соединены с входами элемента ИЛИ, выход которого является выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня | 1981 |

|

SU1015378A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2010 |

|

RU2446461C2 |

| Устройство для извлечения квадратного корня | 1989 |

|

SU1658150A2 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1332313A1 |

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

| Устройство для извлечения квадратного корня | 1988 |

|

SU1569827A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1988 |

|

SU1624699A1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU955039A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2446454C1 |

1. УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ, содержащее блок формирования слагаемых, первый сумматор, сумматорвычитатель, причем блок формирования слагаемых содержит группы элементов И, выходы блока формирования слагаемых подключены к входам первого сумматора, выходы разрядов которого соединены с первой ГРУппдй информационных входов сумма тора-вычита теля, отличающееся тем, что, с целью расширения функциональных возможностей путем вычисления частного от деления суммы партых произведений на произвольное число, с«о содержит второй сумматор, два регистра сдвига, блок формирования . сигнала удвоения, блок анализа и элемент ИЛИ, причем первые входы элементов И блока формирования слагаемых подключены к входам соответствующих разрядных значений операндов пер вой группы устройства, выходы первого регистра сдвига соединен с входами rtt вого сумматора, выхоцы разрядов которого соединены с первсй группой входов блока сформирования сигнала удвоения, выходы переноса пегжого сумматора соединены с входами элемента ИЛИ, выходы разрядов второго сумматора соединены с группой выходов устройства и с информационными входами рвзряцов второго регистра сдвига, группа входов делителя устройства соединена с второй группой входов блока формирования сигнала удвоения и с второй группой информационных входов сумматора-вычислителя, выходы разрядов которого соединены с инфррмационными входами разрядов первого регистра сдвИ га, управляющий вход которого соединен с первым управляющим входом устройства, второй управляющий вход устройства соединен с управляющим входом второго регистра сдвига, выход блока формирования сигнала удвоения соединен с первым управляющим входом сумматора-вычитателя и с первым входом блока анализа, выход элемента ИЛИ соединен с входом младщего разряда второго сумматора и вторым входом блока анализа, У1 У1 выход переноса сумматора-вычитателя соединен с третьим входом блока анализа, четвертый вход. которого подключен к первому управляющему входу устрой: :л ства, первый выход блока анализа сое- динен с вторым управляющим входом сумматора-вычитателя, второй выход блока анализа соединен с информаиион; ным входом младщего разряда второго регистра сдвига, третий выход блока анализа соединен с входом младшего разряда второго сумматора, вторые входы элементов И групп блока формирования слагаемых соединены с входами значений операндов второй группы устройства, выходы элементов И групп блока форми

Изобретение относится к вычислительной технике и может быть применено в спецпроцессорах или в комплексе с цифрОвой вычислительной машиной для оперативного вычисления частного от делеНИИ суммы парных произведений на произвольное число, например, в системах автоматического управления быстропро;техакяпими процессами, динамическими объектами, математические модели котбрых прецставляются в виде совокупности сумм парных произведений.

Известно устройство для деления

двоичных чисел, содержащее Ц параллельных ( П +2)-разрядных сумматора, (И -1 управляемый и один неуправляемый (fi+i )-разрядные преобразователи прямого кона в дополнительный, причем выход каждого 4 -го разряда j -го сумматора (1, ...,м), (, ...,) соединен с первым входом ()-го разряда (| +1)О сумматора, а второй вход о -го сумматора (О 1, .... 1 ) соединен с соответствующим информационным входом (f+i)-ro разряда Q -го управляемог преобразователя пралого кода в допол ннтельный {д1

Недостатком этого устройства являются функциональные возможности, так как в нем не вычисляется частное от суммы парных произведений ка произвопьное число.

Наиболее близким к предлагаемому является устройство для деления, содержашее сумматор, блок формирования слагаемы : (содержащий группы элементов и), сумматор-вычитатель (блок вычитателей) и узел определения знаК:а 4acTHorOj причем входы первой группы устройства, подключены х входам блока формирования слагаемых, выхоцы которого подключены к входам сумматора, выходы которого и входы второй группы устройства подключены к входам сумматора-вычитателя, выходы разрядов которого являются выходами устройства и подключены к входам блока формирования слагаемых, входы узла опрецеления знака частного соединены сО знаковыми входами операндов 2 ,

Недостатком этого устройства являются ограниченные функциональные возможности, определяемые тем, что в |нем не вычисляется частное от деления суммы париых произведений на произвольное число.

Цель изобретения - расширение функциональных возможностей путем вычисления частного от деления суммы парных произвеценкй на произвольное число,

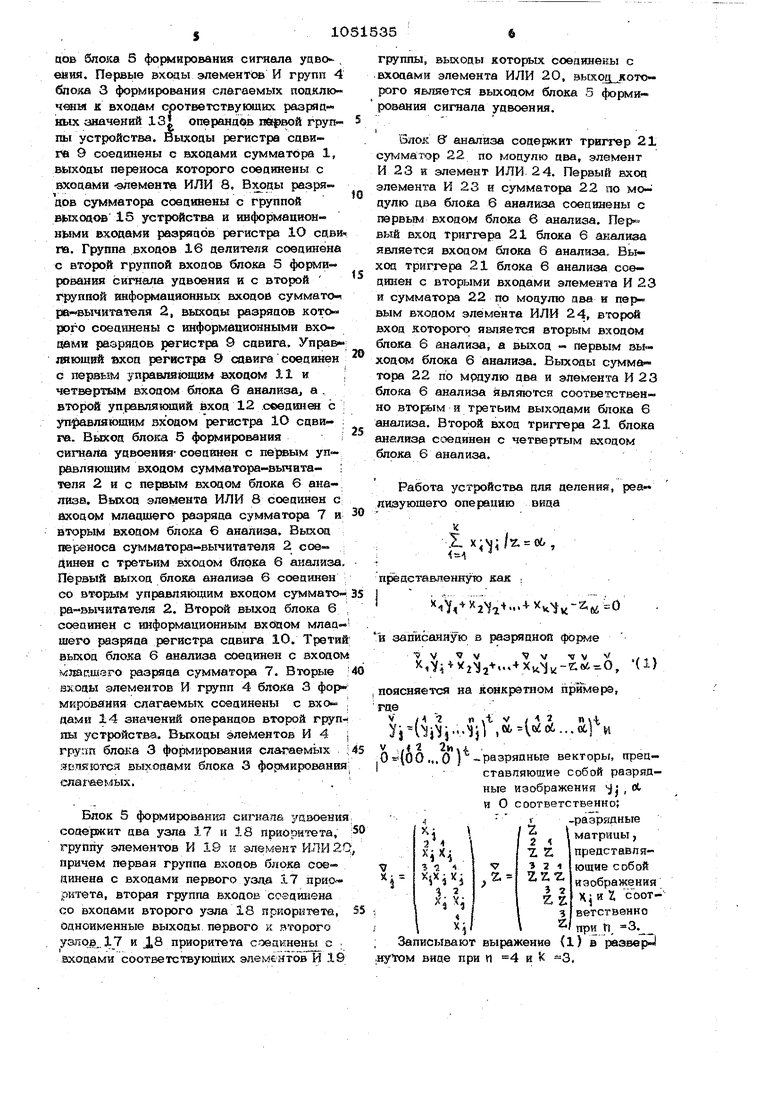

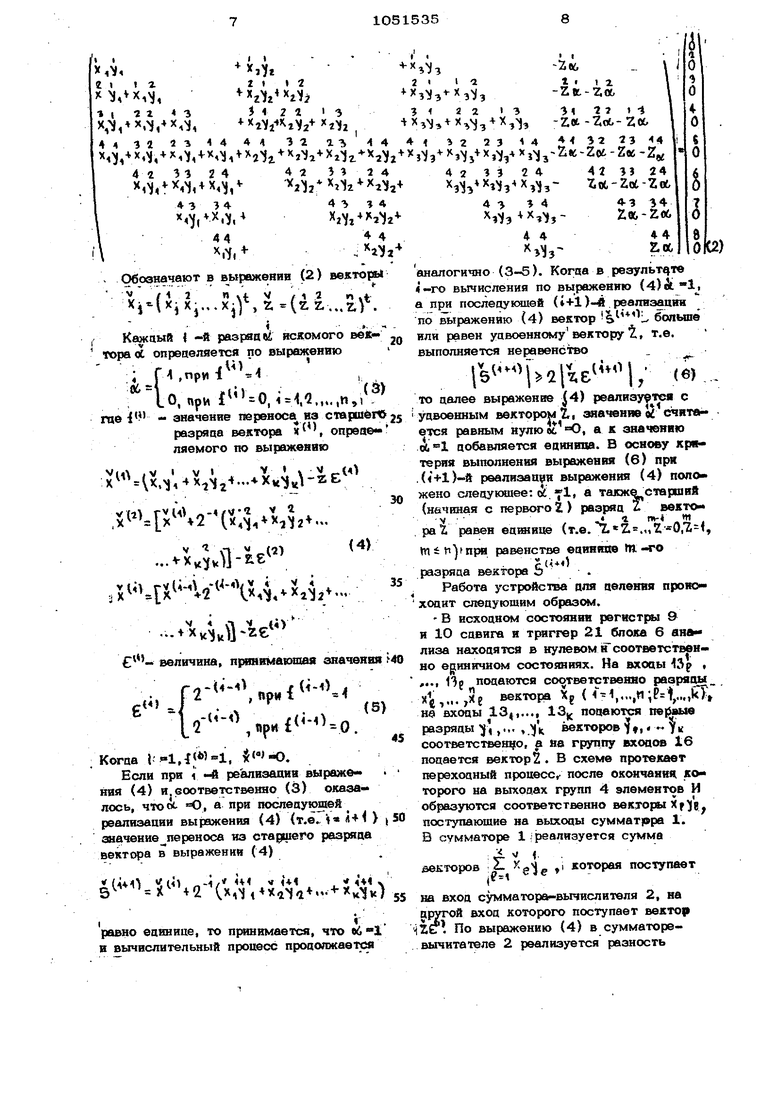

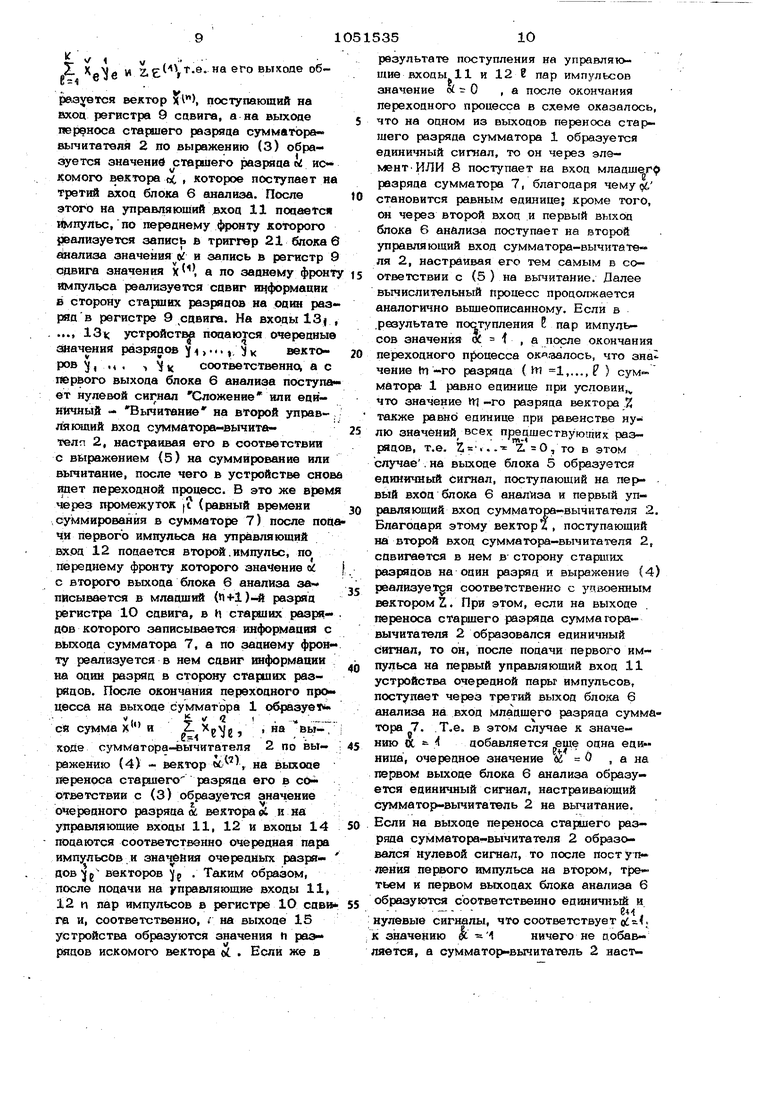

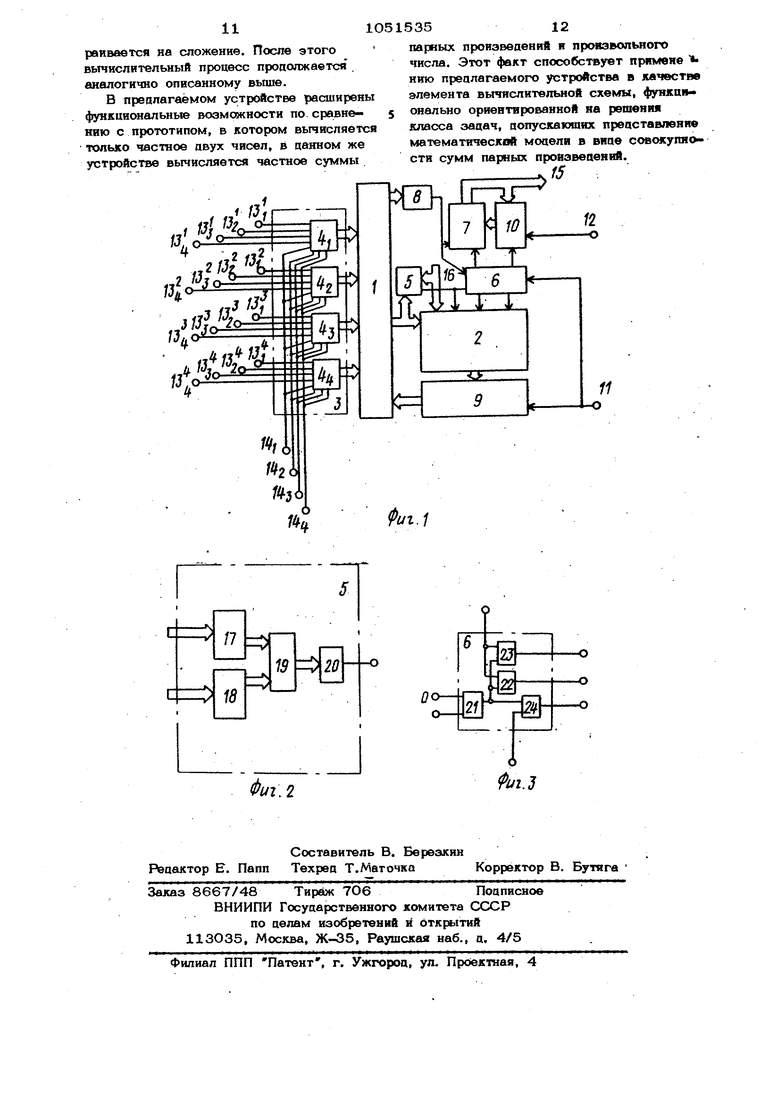

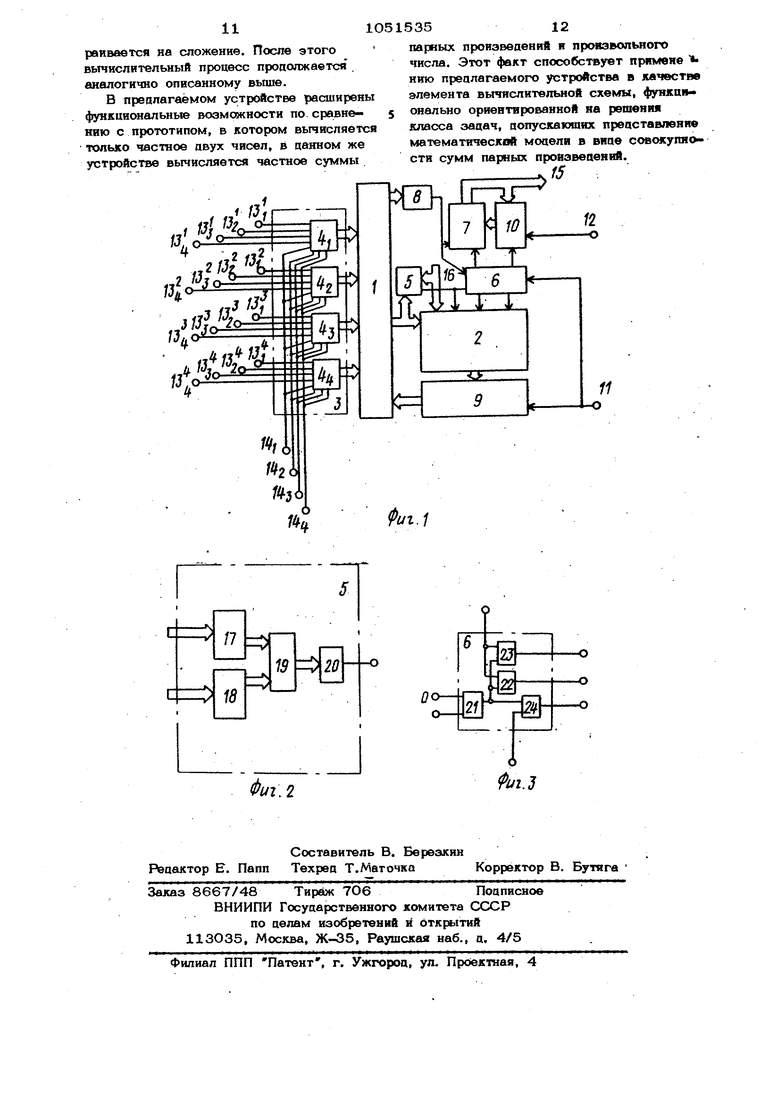

Укаг1анная цель достигается тем, что в устройство для деления, содержащее блок формирования слагаемых, первый сумматор, сумматор-вычислитель, поичем блок формирования слагаемых coaej жит группы элементов И, выхоаы блока формирования слагаемых поцключены к входам первого сумматора, выхоаы аов которого соединены с первой группой информационных вхоцов сумматора-вычи- тателя, дополнительно введены второй сумматор, два регистра сдвига, блок формирования сигнала удвоения, узел анализа и элемент ИЛИ, причем первые входы элементов И групп блока формирования слагаемых подключены к входам соответствующих разрядных значений операндов первой группы устройства,, выходы первого регистра сдвига соединены с входами первого сумматора, выходы разрядов которого соединены с первой -группой входов блока формирования сигна лов удвоения, выходы переноса первого сумматора соединены с входами элемен та ИЛИ, выходы разрядов второго сумматора соединены, с группой выходов устройства и с .информационными входами разрядов второго регистра сдвига, группа входов целителя устройства соединена с эторой группой входов блока формирования сигнала удвоения и с второй группой информационных входов сумматора-вычислителя, выходы разрядов которого соедине ны с информационными входами разрядов первого регистра сдвига, управляющий вход которого соединен с первым упра&ляющим входом устройства, второй управляющий вход устройства соединен с управ ляющим входом второго регистра сдвига, .выход блока формирования сигнала удвоения соединены с первым управляющим входом сумматора-вычитателя и с первым входсад блока анализа, выход элемента ИЛИ соединен с входом младшего разряда второго сумматора и вторым входом блока анализа, выход переноса сумматоре вычитателя соединен с третьим входом блока анализа, четвертый вход которого подключен к первому управляющему входу устройства, первый выход блока анализа соединен с вторым управляющим в.хоаом сумматора-вычитателя, второй выход блока анализа соединен с информационным входом младшего разряда второго регистра сдвига, третий выход блока анализа соединен с входом младшего разряда второго сумматора, вторые входы /элементов И групп блока формирования слагаемых соединены с входами заачеНИИ операндов второй группы устройства, выходы элементов И групп блока фор мирования слагаемых являются выходами блока формирования слагаемых, rtpit этом блок анализа содержит триггер, сумма- j тор по модулю два, элемент И, элемент ИЛИ, первые входы элемента И и сумматора по модулю два блока анализа соединены с первым входом блока анализа, первый вход триггера блока анализа является вторым входом блока анализа, выход триггера блока анализа соединен с вторыми входами элемента И и умматора по модулю два и первым входом элемента ИЛИ блока анализа, второй вход которого является третьим входом блока анализа, а выход - первым выходом блока анализа, выходы сумматора по модулю два и элемента И блока анализа являются соответственно вторым и третьим Bbtxодами блока анализа, второй вход триггера блока анализа соединен с четвертым .входом блока анализа. Крюме того, блок формирования сигнала удвоения содержит ава узла приоритета, группу элементов И и элемент ИЛИ, причем первая группа входов блока соединена с входами первого узла приоритета, вторая группа входов блока соединена с входами второго узла приоритета, одноименные выходы первого и второго узлов приоритета соединены с входами соответствующих элементов И группы, выходы которых соединены с входами элемента ИЛИ, выход которого является выходом блока. На фиг. 1 приведена схема устройства для деления для случая, когда К 4 и И 4 (k - количество сумм парных произведений; Y - разрядность представления инфорвиации); на фиг. 2 - схема блока формирования сигнала удвоения; на фиг.З - схема блока анализа. Устройство для деления содержит сумматор 1, сумматор-вычитатепь 2, блок 3 формирования слагаемых, состоящий из групп 4 элементов И, блок 5 формирования сигнала удвоения, блок 6 анализа, сумматор 7, элемент ИЛИ 8, регистры 9 и 1О сдвига, первый управляющий , втррой упр1эвляк -; ший вход 12, входы 13 разрядных значеннй опербшдов первой группы ( i 1, .... Й; 2 1. ..., ), входы Мр значений операндов ьгорой группы, группу выходов 15 и группу входов 16 делителя. ; Выходы блока 3 формирования подключены к входам сумматора 1, выходы разрядов которого соединены с первой группой информационных входов суммато-J ра-вычитателя 2 и первой группой вхоQOB блодса 5 формирования сигнала уаво eisHH. Первые входы элементов И групп 4 блока 3 формирования слагаемых поцклюЧ&1Ы & вхоаам срответствукяцих разряаНЬ1Х аяачений isi операндвв пефвой группы устройства. Выходы регистра сдвиг& 9 соединены с входами сумматора 1, выходы переноса которого соединены с входами -элемента ИЛИ 8. Входы разрядов сумматора соединены с группой в|ыходов 15 устройства и информационными входами разрядов регистра 1О сави па. Группа входов 16 делителя соединена с второй группой входов блока 5 формирования сигнала удвоения и с второй группой информационных входов суммато-i р1а вычиштеля 2, выходы разрядов кото рого соединены с информационными входами разрядов {югистра 9 сдвига. Управ 1ШЮШИЙ вход регистра 9 сдвига соединен с первым управпяюншм входом 11 и : четвер-илм входом блока 6 анализа а . второй упрввлякндий вход 12 сеедии@{ с : уп ляюшим входом регистра 1О сдай- : гв. Выход блока 5 формированияi сигнала удвоения- соединен с первым уп реиаяяющим входом сумматора-вычита- ; теля 2 и с первым входом блока 6 анализа. Выход элемента ИЛИ 8 соединен с дхоаом младшего разряда сумматора 7 и вторым входом блока 6 анализа. Выход переноса сумматора-вычитателя 2 соединен с третьим входом блока 6 анализа. Первый выход блока анализа 6 соединен ео вторь м управяякядим входом сумматора-вычитателя 2. Второй выход блока 6 срецинен с информационным вхсйом млад- шего разряда регистра сдвига 10. Третий выход блока 6 анализа соединен с входом мзшпшего разряда сумматора 7. Вторые входы элементов И 4 блока 3 фор мкрования слагаемых соединены с вхо«« дами 14 значений операндов второй групяы устройства. Выходы элементов И 4 групп блока 3 формирования слагаемых . являются выходами блока 3 формирования слаг йемых. . Блок 5 формирования сигнала уйвоения содеркит два узла 17 и 18 приоритета, группу элементов И 19 и элемент ИЛИ 2Q причем первая группа входов блока соединена с входами первого узда 17 приоритета, вторая группа входов соединена со входами второго узла 18 приор5зтета, Одноименные выходы первого к второго уэлрв,. и J,8 приоритета сшакнены с ; .входами соответствующих элементов И 19 группы, выходы которых соединены с входами элемента ИЛИ 20, выход которого является выходом блока 5 формирования сигнала удвоения. I Блок 8 анализа содержит триггер 21 cytvJMarxsp 22 по модулю два, элемент И 23 и элемент ИЛИ 24. Первый вход элемента И 23 н сумматора 22 по модулю alia блока 6 анализа соецинены с входом блока 6 анализа. Пер« вый вход триггера 21 блока 6 анализа является входом блока 6 анализа,, Выход триггера 21 блока 6 анализа соединен с вторыми входами элемента И 23 и сумматора 22 по модулю два и первым входом элемента ИЛИ 24, второй вход KOToponj является вторым входом блока 6 анализа, а выход - первым выходе блока 6 анализа. Выходы сумма тора 22 по мрдулю два и элемента И 23 блока 6 анализа являются соответственно вторым и третьим выходами блока 6 анализа. Второй вход триггера 21 блока анализа соединен с четвертым входом блока 6 анализа. Работа устройства для деления, pea дизуюшего операцию вида ч .1 преяставленнуто как i и записанную в разрядной ( v vvVv . ), (-t) поясняется на конкретаом примера, V м t xt / V Ч ) ,o6 i«ioi...c) и V . 1 2n.i ... О ) -разрядные векторы, прецЗаписывают выражение (1) в {яазвер .нуТом виде при и 4 и К 3, Обозначают в выражении (2) векто ,.ii,i(il...lf i- .. Кажаый I -и paspsaoi искомого ве тора оС опреаеляется по выражению I: J I . :; Г, ,npvi 1 4 ,iH.2.,..,n, те - значение переносу из старше разряда вектора , опреа ляемого по выражению Vi4 , V I V V V .,.,. Vfl Г 1л , (. V i Лп {21 ... vii4n-t - X i li,i .Xjjj И1-ге величина, принимающая эначек . 2 , При 1 . Когаа 1-1Л -1. --О. Если при 1 -4i реализаоин выражения (4) и.воответственно (3) оказалось, чтоос ), а при послеауюшей реализации выражения (4) {т.е f« д41 знвчение переноса из ставшего разряда вектора в выражении (4) XU . S +2 (х,1 4Х41а -- -х равно единице, то п{яюимается, что edв вычислительный процесс продолжается аналогично (3-5). Когда в результате 4-го вычисления по выражению {4)& Ij а при последукяцей (+1)-4 реапизацйи по вь1ражению (4) вектор . больше или равен удвоенномувектору , т.е. выполняется неравенство S то далее выраженЕге J4) реализуется с удвоенным вектором 2,1 значение и считается равным нулювс О, а к значению Л добавляется единица. В основу критерия выполнения выражения (6) при .(Vl)t реализации выражения (4) поло жено следуккцее: (i , а также старший (начиная с первого Z) разряд Z вектоV, « а « . раЬ равен едга1иие (т.е. 7.«21 .MZ«0,, niinVnpH равенстве еаинипе rti-го . (оО разряаа вектора Ь. Работа устройства для деления проно ходит следующим образом. В исходном состоянии регистры & и 1О сдвига и тртггер 21 блока 6 ана« лнза находятся в нулевом if соответственно единичном состояниях. На входы 15р « 13; подаются соответственно разряд. Xg вектора Xg ( ,...,,.,,l) н входы 13j(,..., 1.3 подаются перлвые разряды J,.,. , УН векторов , - к соответствен1{ю, а на группу входов 16 подается вектор2 . В схеме протекает переходный процесс,- после окончания ко торого на выходах групп 4 элементов И образуются соответственно векторы X f Уе. поступающие на выходы сумматрра 1. В сумматоре 1 феализуегся сумма г- ,..1 которая поступает лекторов на вход сумматор вычислителя 2, на другой вход которого поступает вектор t По выражению (4) в сумматоревычитателе 2 реализуется разность 21 X Мд и 2, разуется вектор А), поступающий на йхоц регистра 9 савига, а на выхоае не {Этноса старшего разряаа сумматоравычитателя 2 по выражению (З) образуется значений старшего разряаа б искомого вектора с(, , которое поступает на третий вхоа блока 6 анализа. После этого на управляющий вхоа 11 noaaetc импульс, по переднему фронту которого реализуется запись в триггер 21 блока 6 еЬализа значения «; и запись в регистр 9 савига значения х) а по заднему фронт импульса реализуется савиг информации в сторону старших разряцов на раин разряд в регистре 9 сдвига. На входы 13| ..., 13k; устройст подаются очередные ййачения разряоов J i к векторов 5, м . 1 соответственнс1 а с первого выхода блока 6 анализа поступа ет нулевой сигнал Сложение или единичный - Вычитанию на второй управляющий вход сумматора-вычитателп 2, настраивая его в соответствии с выражением {5) на суммирование или вычитание, после чего в устройстве снов идет переходной процесс. В это же врем через промежуток ( (равный времени .суммирования в сумматоре 7) после поц чи первого имнульса на управляющий вход 12 подается второй. импульс, но переднему фронту которого значение od с второго выхоаа блока 6 анализа записывается в младший (и-1)- разряд регистра Ю сдвига, в И старших разрядов которого записывается информация с выхода сумматора 7, а по заднему фронту реализуется в нем сдвиг информации на один разряд в сторону старших разрядов. После окончания переходного про цесса на выходе сумматора 1 образуете ей суммах и Z. , на вы-, 2 по выходе сумматора-вычитателя ражению (4) - вектор , на выходе иэреноса старшего разряда его в ссиответствии с (3) образуется значение очередного разряда ui вектора еС и на управляющие входы 11, 12 и входы 14 подаю гся соответственно очередная пара импульсов и значения очередных разрядов « векторов 5g Таким образом, после подачи на управляющие входы 11 12 и пар импульсов в регистре 10 сдв№ га и, соответственно, на выходе 15 устройства образуются значения п разрадов искомого вектора oi. , Если же в результате поступления на управляющие входы 11 и 12 пар импульсов значение Ы ::; О , а после окончания перехоаного процесса в схеме оказалось, что на оцном из выходов переноса старшего разряаа сз мматора 1 образуется единичный сигнал, то он через элементИЛИ 8 поступает на вход млацшег разряаа сумматора 7, благодаря чемурб становится равным единице; кроме того, on через второй вхоц и первый выхоа блока 6 анализа поступает на второй управляющий вход сумматора-вычнтателя 2, настраивая его тем самым в со- ответствии с (5 ) на вычитание. Далее вычислительный процесс продолжается аналогично вьщ1еописанному. Если в .результате пост пления пар импульсов значения t , а после окончания переходного процесса оказалось, что зна чение (п-го разряда ( И1 ,..., ) сумматора- 1 равно единице при условии, что значение КМ -го разряда вектора Z также равно единице при равенстве нулю значений всех предшесгвующих разрядов, т.е. 2 «..- .,To в этом случае.на выходе блока 5 образуется единичный сигнал, поступающий на перм вый вход блока 6 анализа и первый управляющий вход сумматора-вычитателя 2. Благодаря этому вектор А , поступающий на второй вход сумматора-вычитагеля 2, сдвигается в нем в сторону старших разрядов на один разряд и выражение (4) реализуется соответственно с уивоенным вектором Z. При этом, если на выходе . переноса старшего разряда сумма горавычита1еля 2 образовался единичный снгяап, то он, после подачи первого импульса на первый управляющий вход 11 устройства очередной пары импульсов, поступает через третий выход блока 6 анализа на вход младшего разряда сумматора 7. Т.е. в этом случае к значению а добавляется еще одна единица, очередное значение Ы О , а на первом выходе блока 6 анализа образуется единичный сигнал, настраивающий сумматор-вычитатель 2 на вычитание. Если на выходе переноса старшего разряда сумматора-вычитателя 2 образовался нулевой сигнал, то после поступления первого импульса на втором, третьем и первом выходах блока анализа 6 образуются соответственно единичный и нулевые сигналы, что соответствует oi.. к значению §i ничего не добавляется, а сумматор-вычитатель 2 настраивается на сложение. После этого вычислительный процесс продолжается . аналогично описанному вьшю.

В преалагаёмом устрсЛстве расширены функцион€шьные |юзмо 1кности по сравнению с прототипом, в котором вычисляется только частное двух чисел, в данном же устройстве вычисляется частное суммы

Щ

парных произведений я произвольного числа. Этот факт способствует примене нию предлагаемого устройства в качестве элемента вычислительной схемы, функционально ориентированной яа решения класса задач, допускающих представление математической модели в виде совокупности сумм парных произведений.

15

Фиг.1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для деления двоичных чисел | 1978 |

|

SU748410A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР № 754415, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-10-30—Публикация

1981-09-28—Подача