Изобретение относится к вычислительной технике, может быть использовано при построении быстродействующих специализированных вычислительных устройств и информационно-измерительных систем и является усовершенствованием устройства по авт. ев Ms 1569827.

Цель изобретения - расширение класса решаемых задач за счет возможности извлечения квадратного корня из суммы и разности двух чисел.

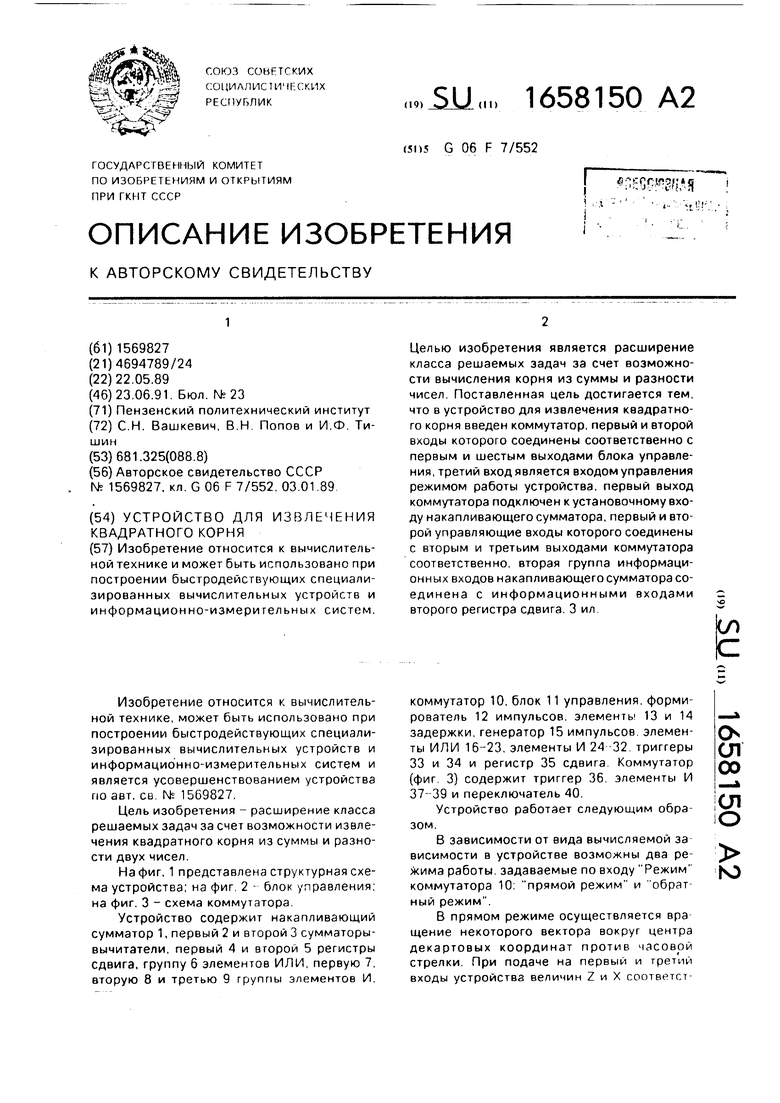

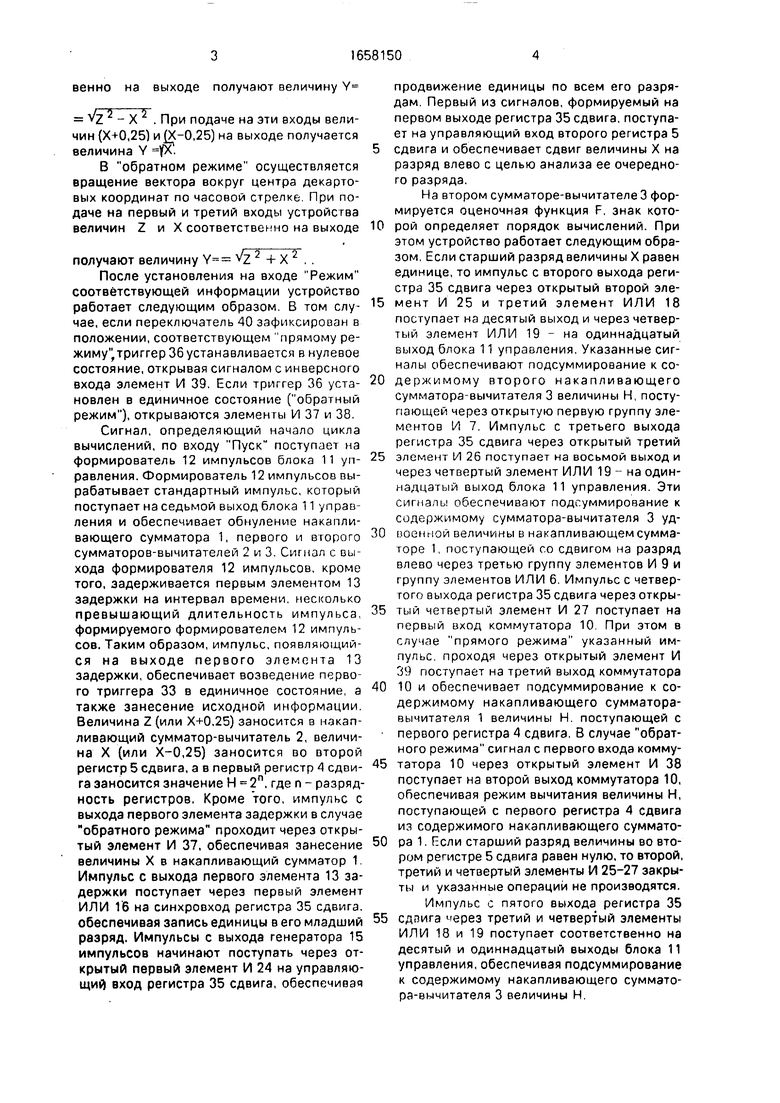

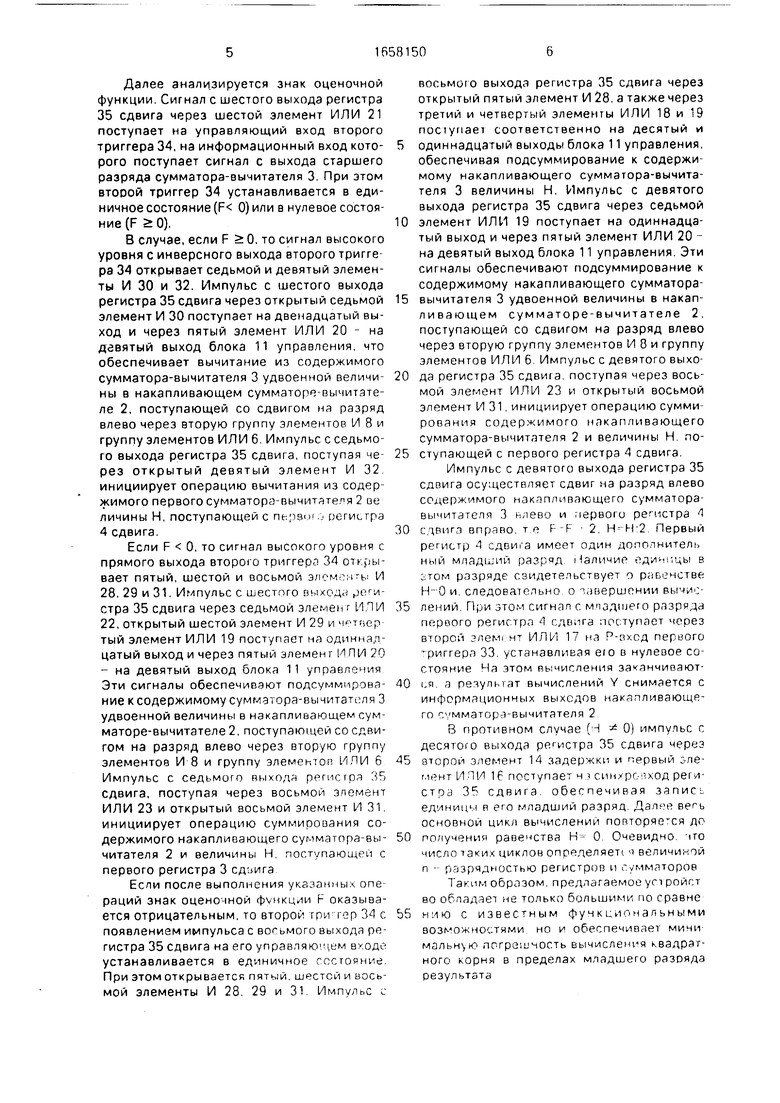

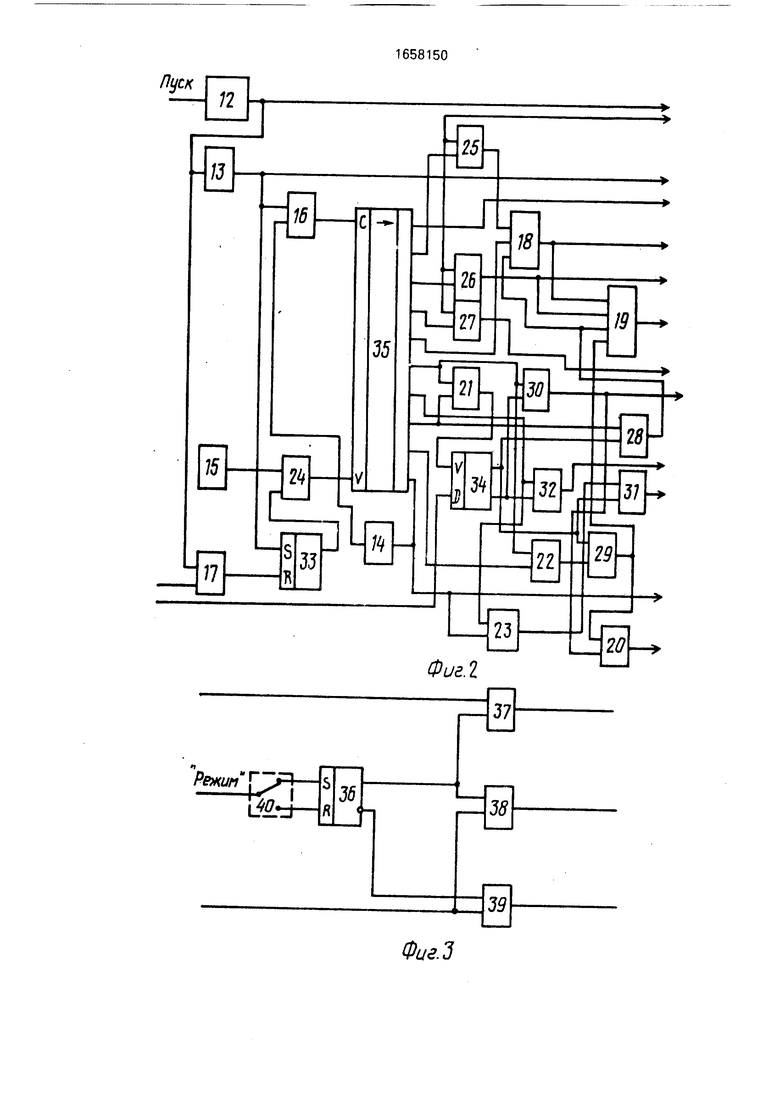

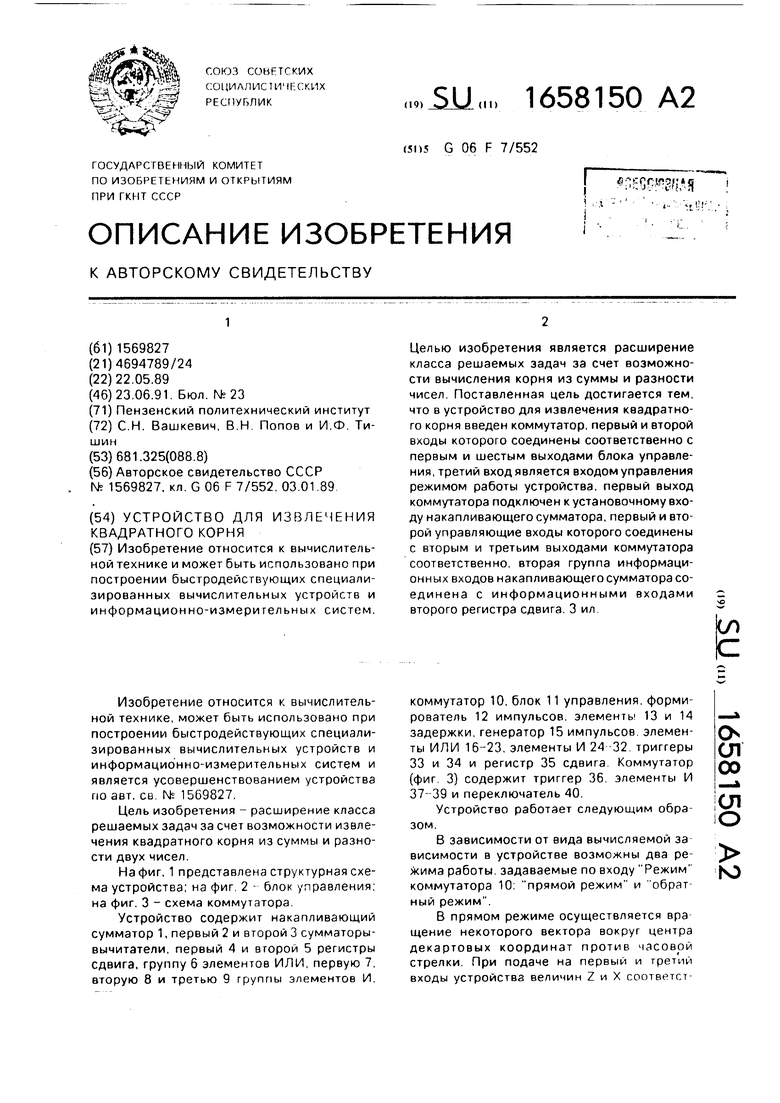

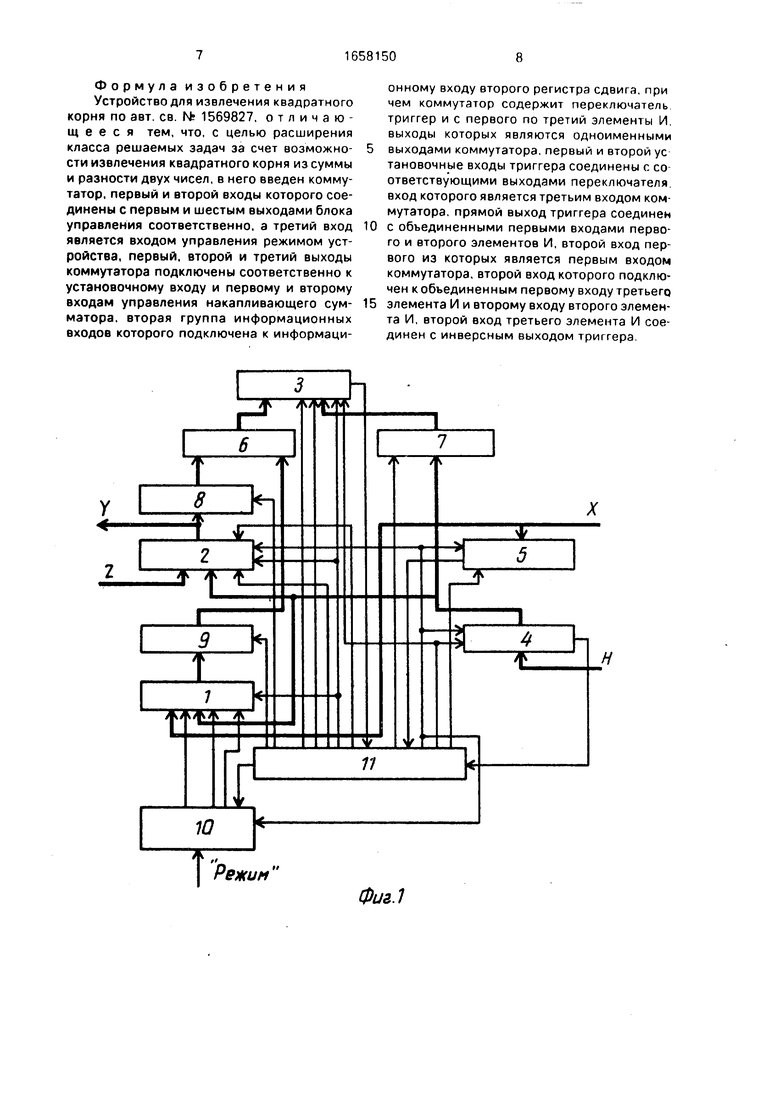

На фиг. 1 представлена структурная схема устройства; на фиг 2 - блок управления; на фиг. 3 - схема коммутатора

Устройство содержит накапливающий сумматор 1, первый 2 и второй 3 сумматоры- вычитатели, первый 4 и второй 5 регистры сдвига, группу 6 элементов ИЛИ, первую 7, вторую 8 и третью 9 группы элементов И,

коммутатор 10, блок 11 управления, формирователь 12 импульсов, элементы 13 и 14 задержки, генератор 15 импульсов элементы ИЛИ 16-23, элементы И 24 32 триггеры 33 и 34 и регистр 35 сдвига Коммутатор (фиг 3) содержит триггер 36 элементы И 37-39 и переключатель 40.

Устройство работает следующим образом.

В зависимости от вида вычисляемой за висимости в устройстве возможны два режима работы задаваемые по входу Режим1 коммутатора 10 прямой режим и обратный режим.

В прямом режиме осуществляется вра щение некоторого вектора вокруг центра декартовых координат против часовой стрелки. При подаче на первый и третий входы устройства величин Z и X соответстО

от

00

8

(О

венно на выходе получают величину Y

VZ - X . При подаче на эти входы величин (Х+0,25) и(Х-0,25) на выходе получается величина Y УХ.

В обратном режиме осуществляется вращение вектора вокруг центра декартовых координат по часовой стрелке. При подаче на первый и третий входы устройства величин Z и X соответственно на выходе

получают величину Y Z 2 + X . .

После установления на входе Режим соответствующей информации устройство работает следующим образом. В том случае, если переключатель 40 зафиксирован в положении, соответствующем прямому ре- жиму триггер 36 устанавливается в нулевое состояние, открывая сигналом с инверсного входа элемент И 39. Если триггер 36 установлен в единичное состояние (обратный режим), открываются элементы И 37 и 38.

Сигнал, определяющий начало цикла вычислений, по входу Пуск поступает на формирователь 12 импульсов блока 11 управления. Формирователь 12 импульсов вырабатывает стандартный импульс, который поступает на седьмой выход блока 11 управления и обеспечивает обнуление накапливающего сумматора 1, первого и вюрого сумматоров-вычитателей 2 и 3. Сигнал с выхода формирователя 12 импульсов, кроме того, задерживается первым элементом 13 задержки на интервал времени, несколько превышающий длительность импульса, формируемого формирователем 12 импульсов. Таким образом, импульс, появляющийся на выходе первого элемента 13 задержки, обеспечивает возведение первого триггера 33 в единичное состояние, а также занесение исходной информации, Величина Z (или Х+0,25) заносится в накапливающий сумматор-вычитатель 2, величина X (или Х-0,25) заносится во второй регистр 5 сдвига, а в первый регистр 4 сдвига заносится значение Н 2П, где п - разрядность регистров, Кроме того, импульс с выхода первого элемента задержки в случае обратного режима проходит через открытый элемент И 37, обеспечивая занесение величины X в накапливающий сумматор 1. Импульс с выхода первого элемента 13 задержки поступает через первый элемент ИЛИ 16 на синхровход регистра 35 сдвига, обеспечивая запись единицы в его младший разряд. Импульсы с выхода генератора 15 импульсов начинают поступать через открытый первый элемент И 24 на управляющий вход регистра 35 сдвига, обеспечивая

продвижение единицы по всем его разрядам. Первый из сигналов, формируемый на первом выходе регистра 35 сдвига, поступает на управляющий вход второго регистра 5

сдвига и обеспечивает сдвиг величины X на разряд влево с целью анализа ее очередного разряда.

На втором сумматоре-вычитателе 3 формируется оценочная функция F, знак кото0 рой определяет порядок вычислений. При этом устройство работает следующим образом. Если старший разряд величины X равен единице, то импульс с второго выхода регистра 35 сдвига через открытый второй эле5 мент И 25 и третий элемент ИЛИ 18 поступает на десятый выход и через четвертый элемент ИЛИ 19 - на одиннадцатый выход блока 11 управления. Указанные сигналы обеспечивают подсуммирование к со0 держимому второго накапливающего сумматора-вычитателя 3 величины Н, поступающей через открытую первую группу элементов И 7. Импульс с третьего выхода регистра 35 сдвига через открытый третий

5 элемент И 26 поступает на восьмой выход и через четвертый элемент ИЛИ 19 - на одиннадцатый выход блока 11 управления. Эти сигналы обеспечивают подсуммирование к содержимому сумматора-вычитателя 3 уд0 военной величины в накапливающем сумматоре 1, поступающей со сдвигом на разряд влево через третью группу элементов И 9 и группу элементов ИЛИ 6. Импульс с четвер- гого выхода регистра 35 сдвига через откры5 гый четвертый элемент И 27 поступает на первый вход коммутатора 10 При этом в случае прямого режима указанный импульс, проходя через открытый элемент И 39 поступает на третий выход коммутатора

0 10 и обеспечивает подсуммирование к содержимому накапливающего сумматора- вычитателя 1 величины Н. поступающей с первого регистра 4 сдвига. В случае обратного режима сигнал с первого входа комму5 татора 10 через открытый элемент И 38 поступает на второй выход коммутатора 10, обеспечивая режим вычитания величины Н, поступающей с первого регистра 4 сдвига из содержимого накапливающего суммато0 ра 1. Если старший разряд величины во втором регистре 5 сдвига равен нулю, то второй, третий и четвертый элементы И 25-27 закрыты и указанные операций не производятся. Импульс с пятого выхода регистра 35

5 сдпига «ерез третий и четвертый элементы ИЛИ 18 и 19 поступает соответственно на десятый и одиннадцатый выходы блока 11 управления, обеспечивая подсуммирование к содержимому накапливающего сумматора-вычитателя 3 величины Н.

Далее анализируется знак оценочной функции. Сигнал с шестого выхода регистра 35 сдвига через шестой элемент ИЛИ 21 поступает на управляющий вход второго триггера 34, на информационный вход кото- рого поступает сигнал с выхода старшего разряда сумматора-вычитателя 3. При этом второй триггер 34 устанавливается в единичное состояние (F 0) или в нулевое состояние ().

В случае, если F 0, то сигнал высокого уровня с инверсного выхода второго триггера 34 открывает седьмой и девятый элементы И 30 и 32. Импульс с шестого выхода регистра 35 сдвига через открытый седьмой элемент И 30 поступает на двенадцатый выход и через пятый элемент ИЛИ 20 - на девятый выход блока 11 управления, что обеспечивает вычитание из содержимого сумматора-вычитателя 3 удвоенной величи- ны в накапливающем сумматоре-вычитате- ле 2, поступающей со сдвигом на разряд влево через вторую группу элементов И 8 и группу элементов ИЛИ 6. Импульс с седьмого выхода регистра 35 сдвига, поступая че- рез открытый девятый элемент И 32. инициирует операцию вычитания из содержимого первого сумматора-вычитателя 2 ве личины Н, поступающей с первпг.-., регистра 4 сдвига.

Если F 0, то сигнал высокого уровня с прямого выхода второго триггера 34 открывает ПЯТЫЙ, ШеСТОЙ И ВОСЬМОЙ ЭЛОМОН Ы И

28, 29 и 31, Импульс с шестого выхода регистра 35 сдвига через седьмой элемент ИЛИ 22, открытый шестой элемент И 29 и ч твер- тый элемент ИЛИ 19 поступает на одиннад- цатый выход и через пятый элемент ИЛИ 20 - на девятый выход блока 11 управления Эти сигналы обеспечивают подсумммрова- ние к содержимому сумматора-вычитателя 3 удвоенной величины в накапливающем сум- маторе-вычитателе 2, поступающей со сдвигом на разряд влево через вторую группу элементов И-8 и группу элементов ИЛИ 6 Импульс с седьмого выхода регистра 35 сдвига, поступая через восьмой элемент ИЛИ 23 и открытый восьмой элемент И 31, инициирует операцию суммирования содержимого накапливающего сумматора-вы- читателя 2 и величины Н, поступающей с первого регистра 3 сдвига

Если после выполнения указанных операций знак оценочной функции F оказывается отрицательным, то второй гри1 гер 34 с появлением импульса с восьмого выхода регистра 35 сдвига на его управляющем входе устанавливается в единичное состояние. При этом открывается пятый, шестой и восьмой элементы И 28, 29 и 31. Импульс с

восьмого выхода регистра 35 сдвига через открытый пятый элемент И 28. а также через третий и четвертый элементы ИЛИ 18 и 19 поступает соответственно на десятый и одиннадцатый выходы блока 11 управления, обеспечивая подсуммирование к содержимому накапливающего сумматора-вычитателя 3 величины Н. Импульс с девятого выхода регистра 35 сдвига через седьмой элемент ИЛИ 19 поступает на одиннадцатый выход и через пятый элемент ИЛИ 20 - на девятый выход блока 11 управления. Эти сигналы обеспечивают подсуммирование к содержимому накапливающего сумматора- вычитателя 3 удвоенной величины в накапливающем сумматоре-вычитателе 2. поступающей со сдвигом на разряд влево через вторую группу элементов И 8 и группу элементов ИЛИ 6. Импульс с девятого выхода регистра 35 сдвига, поступая через восьмой элемент ИЛИ 23 и открытый восьмой элемент И 31, инициирует операцию суммирования содержимого накапливающего сумматора-вычитателя 2 и величины Н. поступающей с первого регистра 4 сдвига.

Импульс с девятого выхода регистра 35 сдвига осуществляет сдвиг на разряд влево содержимого накапливающего сумматора- вычитателя 3 влево и первого регистра 4 сдвига вправо, те F -F 2, Первый регистр 4 сдвига имеет один дополнитель ный младший разряд Наличие единицы в ;-,том разряде свидетельствует о равенстве и. следовательно о тавершении вычислений. При этом сигнал с мпздшего разряда первого регистра 4 сдвига поступает через второй элем нт ИЛИ 17 на Р-пхсд первого риггера 33. устанавливая ею в нулевое состояние Ча этом вычисления заканчиваются, а результат вычислений Y снимается с информационных выходов накапливающего сумматора-вычитателя 2

8 противном случае (Н 0) импульс с десятого выхода регистра 35 сдвига через аторой элемент 14 задержки и первый элемент И ПИ 16 поступает ч э синхролход perи- стра 35 сдвига, обеспечивая запись единиц1-. в его младший разряд. Далее вегь основной цикл вычислений повторяемся до получения равенства Н 0 Очевидно, что число таких циклов определяет, ч величиной п - разрядностью регистров и сумматоров

Таким образом, предлагаемое уп роист во обладает не только большими по сравне н и ю с известным Функциональными возможностями но и обеспечивает минимальную погрешность вычисления квадратного корня в пределах младшего разряда результата

Формула изобретения Устройство для извлечения квадратного корня по авт. св. № 1569827, отличающееся тем, что, с целью расширения класса решаемых задач за счет возможности извлечения квадратного корня из суммы и разности двух чисел, в него введен коммутатор, первый и второй входы которого соединены с первым и шестым выходами блока управления соответственно, а третий вход является входом управления режимом устройства, первый, второй и третий выходы коммутатора подключены соответственно к установочному входу и первому и второму входам управления накапливающего сумматора, вторая группа информационных входов которого подключена к информаци0

5

онному входу второго регистра сдвига, при чем коммутатор содержит переключатель триггер и с первого по третий элементы И выходы которых являются одноименными выходами коммутатора, первый и второй ус тановочные входы триггера соединены с со ответствующими выходами переключателя вход которого является третьим входом коммутатора, прямой выход триггера соединен с объединенными первыми входами первого и второго элементов И, второй вход первого из которых является первым входом коммутатора, второй вход которого подключен к объединенным первому входу третьего элемента И и второму входу второго элемента И, второй вход третьего элемента И соединен с инверсным выходом триггера

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня | 1988 |

|

SU1569827A1 |

| Интерполятор | 1988 |

|

SU1541557A1 |

| Устройство для вычисления логарифма | 1984 |

|

SU1179328A1 |

| Параболический интерполятор | 1984 |

|

SU1231512A1 |

| Функциональный преобразователь | 1991 |

|

SU1807498A1 |

| Функциональный преобразователь | 1988 |

|

SU1541629A1 |

| Устройство для вычисления математического ожидания | 1986 |

|

SU1322315A1 |

| Цифровой функциональный преобразователь | 1984 |

|

SU1188750A1 |

| Параболический интерполятор | 1984 |

|

SU1160370A1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих специализированных вычислительных устройств и информационно-измерительных систем. Целью изобретения является расширение класса решаемых задач за счет возможности вычисления корня из суммы и разности чисел. Поставленная цель достигается тем. что в устройство для извлечения квадратного корня введен коммутатор, первый и второй входы которого соединены соответственно с первым и шестым выходами блока управления, третий вход является входом управления режимом работы устройства, первый выход коммутатора подключен к установочному входу накапливающего сумматора, первый и второй управляющие входы которого соединены с вторым и третьим выходами коммутатора соответственно, вторая группа информационных входов накапливающего сумматора соединена с информационными входами второго регистра сдвига 3 ил (/) С

| Режим

Фиг.1

г гщ

9Ј

Я

| Устройство для извлечения квадратного корня | 1988 |

|

SU1569827A1 |

Авторы

Даты

1991-06-23—Публикация

1989-05-22—Подача