Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих специализированных вычислительных устройств и информационно-измерительных систем.

Цель изобретения - повышение быстродействия .

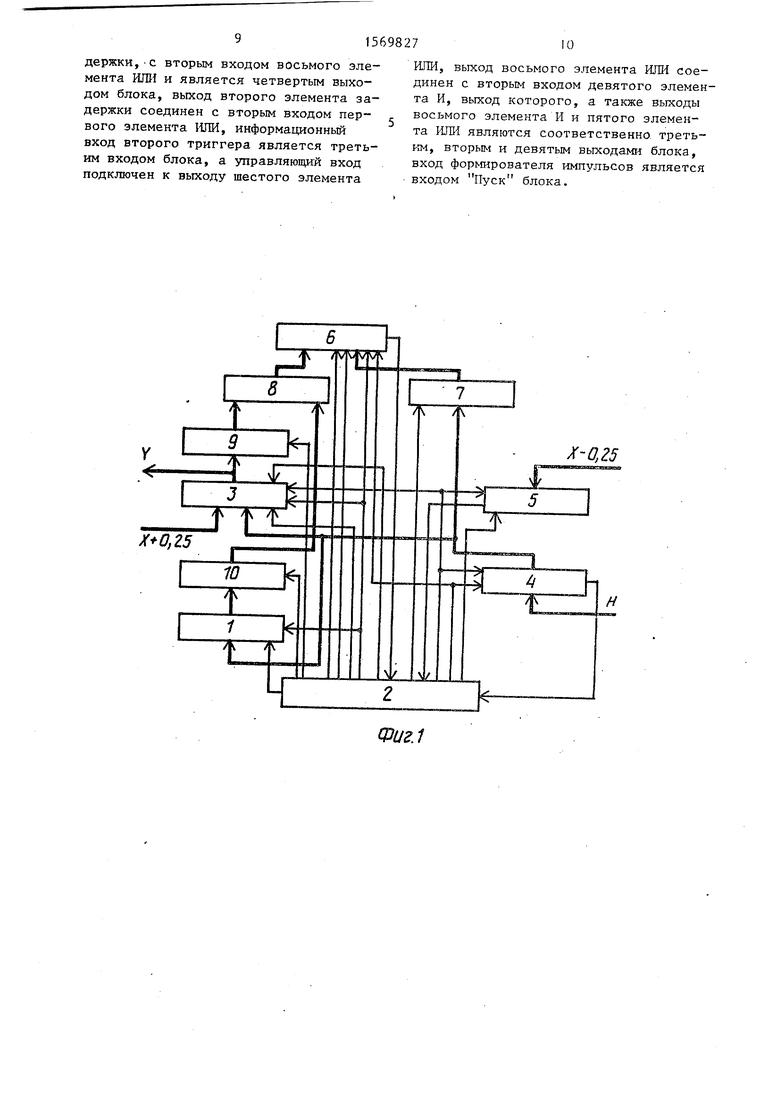

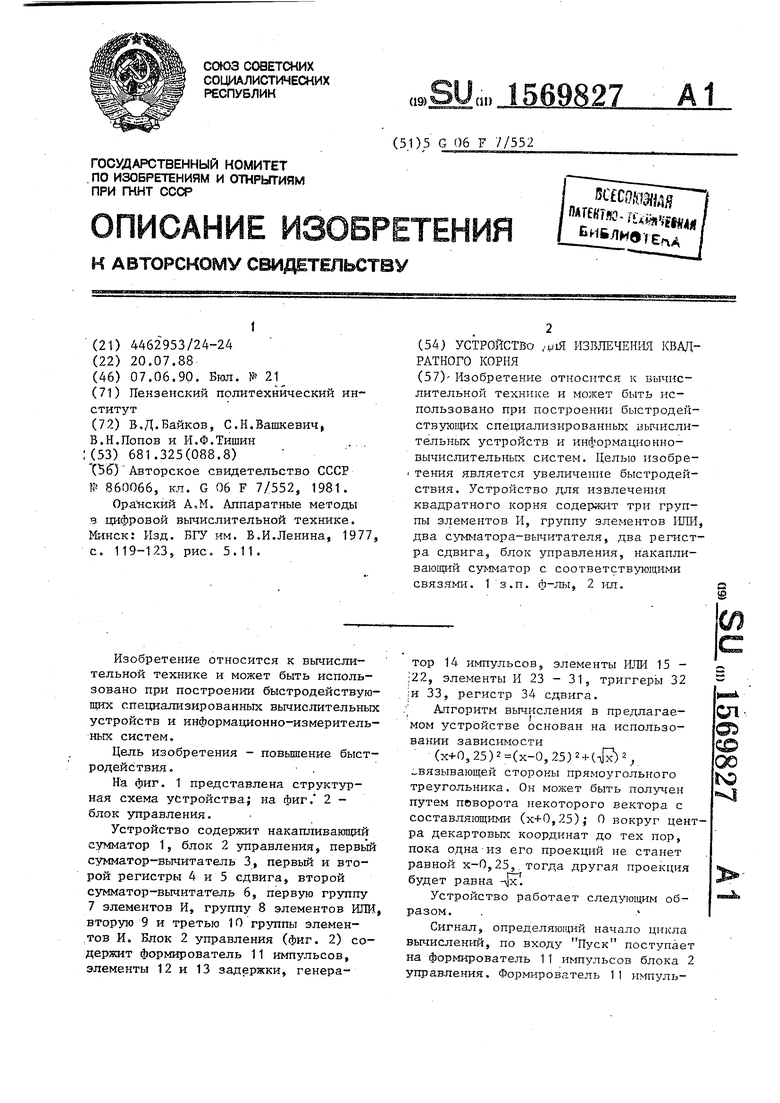

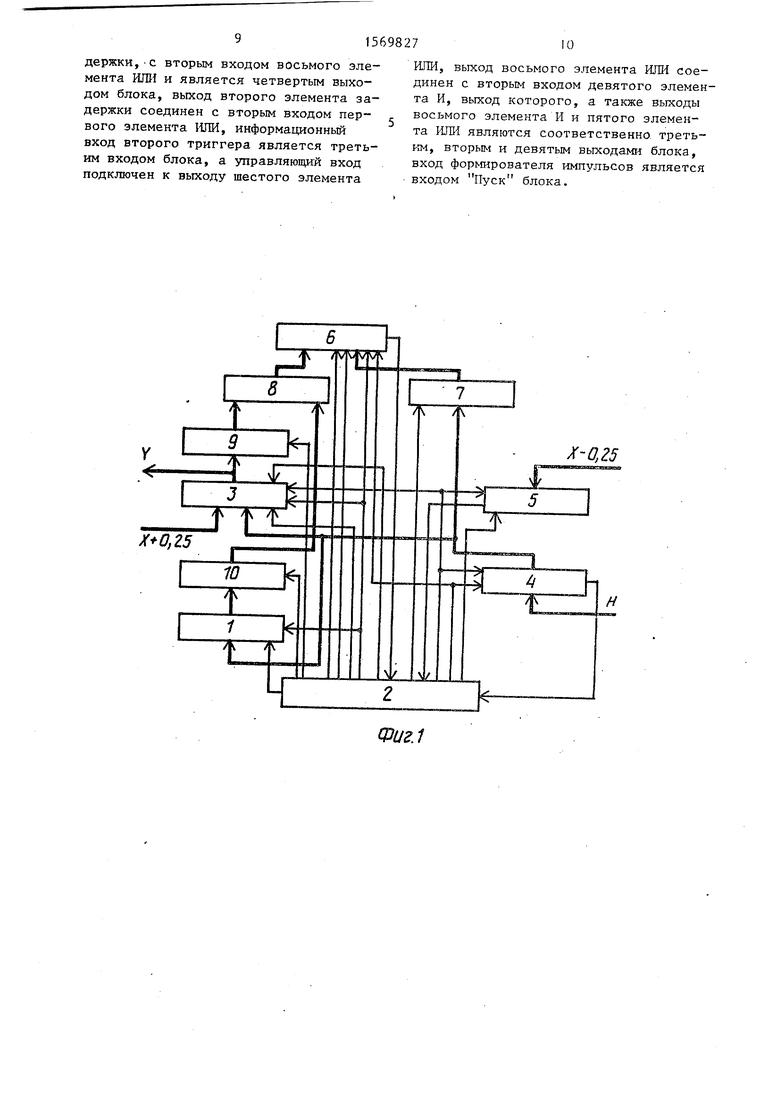

На фиг. 1 представлена структурная схема устройства; на фиг/ 2 - блок управления.

Устройство содержит накапливающий сумматор 1, блок 2 управления, первый сумматор-вычитатель 3, первый и второй регистры 4 и 5 сдвига, второй сумматор-вычитатель 6, первую группу 7 элементов И, группу 8 элементов ИЛИ, вторую 9 и третью 10 группы элементов И. Блок 2 управления (фиг. 2) содержит формирователь 11 импульсов, элементы 12 и 13 задержки, генератор 14 импульсов, элементы ИЛИ 15 - 22, элементы И 23 - 31, триггеры 32 и 33, регистр 34 сдвига.

Алгоритм вычисления в предлагаемом устройстве основан на использовании зависимости

(х+0,25)2 (х-0,25)2 + (лЈ)2; вязывающей стороны прямоугольного треугольника. Он может быть получен путем поворота некоторого вектора с составляющими (х+0,25); 0 вокруг центра декартовых координат до тех пор, пока одна из его проекций не станет равной х-0,25э тогда другая проекция будет равна .

Устройство работает следующим образом.

Сигнал, определяющий начало цикла вычислений, по входу Пуск поступает на формирователь 11 импульсов блока 2 управления. Формирователь 11 импульСП

00

ГС

сов вырабатывает стандартный импульс,, который поступает на седьмой выход блока 2 управления и обеспечивает обнуление накапливающих сумматора 15 сумматоров-вычитателей 3 и 6, Сигнал с выхода формирователя 11 импульсов задерживается первым элементом 12 задержки на интервал времени, несколько превышающий длительность импульса, формируемого формирователем 11 импульсов. Таким образом, импульс,, появляющийся на выходе первого элемента 12 задержкиэ обеспечивает взведение первого триггера 32 в единичное состоя- ние, а также занесение исходной информации. Величина x+0s 25 заносится в накапливающий сумматор-вычитатель 3, величина - во второй регистр 5 сдвига5 а в первый регистр 4 сдвига заносится значение )|) где п - раз- рядность регистров0. Кроме того5 импульс с выхода первого элемента 12 задержки поступает через первый элемент ИЛИ 15 на синхровход регистра 34 сдви ras обеспечивая запись единицы в его младший разряд. Импульсы с выхода генератора 14 импульсов начинают поступать через открытый первый элемент И 23 на управляющий вход регистра 34 Сдвигаз обеспечивая продвижение единицы по всем его разрядам. Первый из сигналов9 формируемый на первом входе регистра 34 сдвига;: поступает на управляющий вход второго регистра 5 Сдвига и обеспечивает сдвиг величины х-0S25 на разряд влево с целью анализа ее очередного разряда.

На втором сумматоре-вычитателе 6 будет формироваться так называемая оценочная функция Fp знак которой определяет ПОРЯДОК вычислений. При этом устройство работает следующим образом Если старший разряд величины х-0,25 равен единице то импульс с второго выхода регистра 34 сдвига через открытый второй элемент И 24 и третий элемент ИЛИ 17 поступает на десятый выход и через четвертый элемент ИЛИ 18 - на одиннадцатый выход блока 2 управления. Указанные сигналы обеспе- ччвают подсуммирование к содержимому второго накапливающего сумматора- вычитателя б величины Нэ поступающей через открытую первую группу элементов И 7, Импульс с третьего выхода регистра 34 сдвига через открытый третий элемент И 25 поступает на восьмой выход и через четвертый элемент

Q 5 Q 5

п ., 5

ИЛИ 18 - на одиннадцатый выход блока 2 управления. Эти сигналы обеспе- чгвагат подсуммирование к содержимому сумматора-вычитателя 6 удвоенной величины в накапливающем сумматоре 1, поступающей со сдвигом на разряд влево через третью группу элементов И 10 и группу элементов ИЛИ 8, Импульс с четвертого выхода регистра 34 сдвига через открытый четвертый элемент И 26 обеспечивает подсуммирование к содержимому накапливающего сумматора 1 величины Нэ поступающей с первого регистра 4 сдвига. Если старший разряд величины x-0s25 равен нулю, то второй, третий и четвертый элементы И 24, 25 и 26 закрыты и указанные операции не производятся.

Импульс с пятого выхода регистра 34 сдвига через третий и четвертый элементы ИЛИ 17 и 18 поступает соответственно на десятый и одиннадцатый выходы блока 2 управления, обеспечивая подсуммирование к содержимому дополнительного накапливающего сумматора-вычитателя 6 величины Н.

Далее анализируется знак оценочной функции. Сигнал с шестого выхода регистра 34 сдвига через шестой элемент ИЛИ 20 поступает на управляющий вход второго триггера 33s на информационный вход которого поступает сигнал с выхода старшего разряда сумматора-вы- читателя 6. При этом второй триггер 33 устанавливается в единичное состояние () или в нулевое состояние

(F3sl)).

В случае s если F то сигнал высокого уровня с инверсного выхода второго триггера 33 открывает седьмой и девятый элементы И 29 и 31. Импульс с шестого выхода регистра 34 сдвига через открытый седьмой элемент И 29 поступает на двенадцатый выход и через пятый элемент ИЛИ 19 - на девятый выход блока 2 управления, что обеспечивает вычитание из содержимого сум- матора-вычитателя 6 удвоенной величины в накапливающем сумматоре-вычитателе 3, поступающей со сдвигом на разряд влево через вторую группу 9 элементов И и группу 8 элементов ИЛИ. Импульс с седьмого выхода регистра 34 сдвигаэ поступая через открытый восьмой элемент И 30, инициирует операцию вычитания из содержимого первого сумматора-вычитателя 3 величины Н.

поступающей с первого регистра 4 сдвига.

Если , то сигнал высокого уров ня с прямого выхода второго триггера 33 открывает пятый, шестой и восьмой элементы И 27, 28 и 30. Импульс с шестого выхода регистра 34 сдвига через седьмой элемент ИЛИ 21, открытый шестой элемент И 28 и четвертый элемент ИЛИ 18 поступает на одиннадцатый выход и через пятый элемент ИЛИ 19 - на девятый выход блока 2 управления. Эти сигналы обеспечивают подсуммирование к содержимому сумматора-вычитателя 6 удвоенной величины в накапливающем сумматоре-вычитателе 3, поступающей со сдвигом на разряд влево через вторую группу 9 элементов И и группу 8 элементов ИЛИ. Импульс с седьмого выхода регистра 34 сдвига, поступая через восьмой элемент ИЛИ 22 и открытый девятый элемент И 31, инициирует операцию суммирования содержимого накапливающего сумматора-вычитателя 3 и величины Н, поступающей с первого регистра 4 сдвига.

Если после выполнения указанных операций знак оценочной функции F оказывается отрицательным, то второй триггер 33 с появлением импульса с восьмого выхода регистра 34 сдвига на его управляющем входе устанавливается в единичное состояние. При этом открываются пятый, шестой и восьмой элементы И 27, 28 и 30. Импульс с восьмого выхода регистра 34 сдвига через открытый пятый элемент И 27, а также через третий и четвертый элементы ИЛИ 17 и 18 поступает соответственно на девятый и одиннадцатый выходы блока 2 управления, обеспечивая подсуммирование к содержимому накапливающего сумматора-вычитателя 6 величины Н. Импульс с девятого выхода регистра 34 сдвига через седьмой элемент ИЛИ 21, открытый шестой элемент И 28 и четвертьй элемент ИЛИ 18 поступает на одиннадцатый выход и «через

10

20

лд45 98276

девятый элемент И 31, инициирует операцию суммирования содержимого накапливающего сумматора-вычитателя 3 и величины Н, поступающей с первого регистра 4 сдвига.

Импульс с десятого выхода регистра 34 сдвига осуществляет сдвиг на разряд содержимого накапливающего сумматора-вычитателя 6 влево и первого регистра 4 сдвига вправо, т.е. , Первый регистр 4 сдвига имеет один дополнительный младший разряд. Наличие единицы в этом разряде сви- 15 детельствует о равенстве , а следовательно, о завершении вычислений. При этом сигнал с младшего разряда первого регистра 4 сдвига поступает через второй элемент ИШ1 16 на R-иход первого триггера 32, устанавливая его в нулевое состояние. На этом вычисления заканчиваются, а результат вычислений снимается с информационных выходов накапчивающего сумматора-вычитателя 3.

В противном случае () импульс с десятого выхода регистра 34 сдвига через второй элемент 13 задержки и первый элемент ИЛИ 15 поступает на синхровход регистра 34 сдвига, обеспечивая запись единицы в его младший разряд. Далее весь основной цикл вычислений повторяется до получения равенства . Очевидно, что число таких циклов определяется п-разряднос- тью регистров и сумматоров.

25

30

35

Формула изобретения

1. Устройство для извлечения каад- ратного корня, содержащее накапливающий сумматор, управляющий вход которого подключен к первому выходу блока управления, второй и третий выходы которого соединены соответственно с первым и вторым управляющий входами первого сумматора-вычитателя, информационные входы первой и второй групп которого подключены к первому инфор-1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня | 1989 |

|

SU1658150A2 |

| Интерполятор | 1988 |

|

SU1541557A1 |

| Параболический интерполятор | 1984 |

|

SU1160370A1 |

| Функциональный преобразователь | 1991 |

|

SU1807498A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Устройство для деления | 1984 |

|

SU1259251A1 |

| Устройство для извлечения квадратного корня | 1983 |

|

SU1174923A1 |

| Параболический интерполятор | 1984 |

|

SU1231512A1 |

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Устройство для вычисления логарифма | 1984 |

|

SU1179328A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих специализированных вычислительных устройств и информационно-вычислительных систем. Целью изобретения является увеличение быстродействия. Устройство для извлечения квадратного корня содержит три группы элементов И, группу элементов ИЛИ, два сумматора-вычитателя, два регистра сдвига, блок управления, накапливающий сумматор с соответствующими связями. 1 з.п. ф-лы, 2 ил.

пятый элемент ИЛИ 19 на девятый выход 50 мационному входу устройства п инфор- блока 2 управления. Эти сигналы обеспечивают подсуммирование к содержимому накапливающего сумматора-вычитателя 3 удвоенной величины, поступающей

55

со сдвигом на разряд влево через вторую группу 9 элементов И и группу 8 элементов ИЛИ. Импульс с десятого выхода регистра 34 сдвига, поступая через восьмой элемент ИЛИ 22 и открытый

мационному входу первого регистра сдвига соответственно, вход управления сдвига которого соединен с четвертым выходом блока управления, пятый выход которого соединен с входом управления сдвига второго регистра сдвига, отличающееся тем, что, с целью повышения быстродействия в него введены группа элементов ПЛИ,

мационному входу устройства п инфор-

мационному входу первого регистра сдвига соответственно, вход управления сдвига которого соединен с четвертым выходом блока управления, пятый выход которого соединен с входом управления сдвига второго регистра сдвига, отличающееся тем, что, с целью повышения быстродействия в него введены группа элементов ПЛИ,

три группы элементов И и второй сум- атор-вычитатель, информационные вхоы первой и второй групп которого соединены с выходами соответственно эле- ентов И первой группы и элементов ЛИ группы, первые и вторые входы элементов ИЛИ группы подключены к выодам элементов И соответственно втоой и третьей групп, первые входы JQ элементов И которых соединены с выхо ами соответственно первого суммато- а-вычитателя и накапливающего сумматора; информационные входы которого объединены с первыми входами элемен- J5 тов И первой группы и подключены к выходам первого регистра сдвига, информационный вход которого соединен с вторым информационным входом устройства, а выход младшего разряда под- 20 Ключей к первому входу блока управления,, шестой выход которого соединен с входами синхронизации первого сумма™ тора-вычитателя, первого и второго регистров сдвига, информационный вход 25 которого соединен с третьим информационным входом устройства, а выход старшего разряда подключен к второму входу блока управления3 седьмой выход которого соединен с объединенными 30 входами установки в О накашшвающе™ го сумматора, первого и второго сумматоров-вычитателей, выход старшего (знакового) разряда последнего из которых подключен к третьему входу ,- блока управления, восьмой, девятый и десятый вяходы которого соединены с вторыми входами элементов И соответственно третьей,, второй к первой групп 9 а одиннадцатый s двенадцатый: 40 я четвертый выходы соединены с первыми входами второго сумматора-вычи™ тателя, выход первого сумматора-вычи- тателя соединен с выходом устройства

2, Устройство по п, 1, о т л и - 45 чающееся тем,, что блок управления содержит формирователь импульсов f первый и второй элементы задерж- хи9 генератор импульсов, с первого по восьмой элементы ИЛИ, первый и gg второй триггеры с первого по девятый элементы И и регистр сдвига, вход синхронизации которого соединен с выходом первого элемента ИЛИ первый «ход которого объединен с S-входом

55

первого триггера, подключен к выходу первого элемента задержки и является шестым выходом блока, седьмой выход которого является выходом формирова-

5 g

5

теля импульсов и соединен с входом первого элемента задержки и первым входом второго элемента ИЛИ, второй вход которого является первым входом блока., а выход подключен к R-входу первого триггера9 выход которого соединен с первым входом первого элемента И, второй вход и выход которого соединены соответственно с выходом генератора сдвига, первьй выход которого является пятым выходом блока, а второй подключен к первому входу второго элемента И, второй вход котб- рого соединен с вторым входом блока я первыми входами третьего и четвертого элементов Hs вторые входы которых подключены соответственно к одноименным выходам регистра сдвига, пятый выход которого подключен к первому входу третьего элемента ИЛИ, второй вход которого соединен с выходом второго элемента И9 третий вход подключен к объединенным первому входу четвертого элемента ИЛИ и выходу пятого элемента И, а выход является десятым выходом блока и подключен к второму входу четвертого элемента ИЛИЭ третий вход которого подключен к объединенным восьмому выходу блока и выходу третьего элемента И5 четвертый вход подключен к объединенным выходу шестого элемента И и первому ду пятого элемента ИЛИ, а выход является одиннадцатым выходом блока, первый выход которого соединен с выходом четвертого элемента И, а двенадцатый выход блока подключен к объединенным второму входу пятого элемента ИЛИ и выходу седьмого элемента И первый вход которого соединен с первыми входами шестого и седьмого элементов ИЛИ и шестым выходом регистра сдвига, седьмой выход которого подключен к первым входам восьмых элементов ИЛИ и И} второй вход последнего из которых соединен с вторым входом седьмого элемента И и инверсным выходом второго триггера, прямой выход которого соединен с первыми входами шестого, девятого и пятого элементов И, второй вход которого соединен с вторым входом шестого элемента ИЛИ и восьмым выходом регистра сдвига, девятый выход которого подключен к второму входу седьмого элемента ЮШ5 выход которого соединен с вторым входом шестого элемента И, десятый выход регистра сдвига соединен с входом второго элемента задержки, с вторым входом восьмого элемента ИЛИ и является четвертым выходом блока, выход второго элемента задержки соединен с вторым входом первого элемента ИЛИ, информационный вход второго триггера является третьим входом блока, а управляющий вход подключен к выходу шестого элемента

ИЛИ, выход восьмого элемента ИЛИ соединен с вторым входом девятого элемента И, выход которого, а также выходы восьмого элемента И и пятого элемента ИЛИ являются соответственно третьим, вторым и девятым выходами блока, вход формирователя импульсов является входом Пуск блока.

Фиг.1

| Цифровое устройство для извлечения квадратного корня | 1979 |

|

SU860066A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Оранский А,М | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Минск: Изд | |||

| БГУ им | |||

| В.И.Ленина, 1977, с | |||

| Способ получения камфоры | 1921 |

|

SU119A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1990-06-07—Публикация

1988-07-20—Подача