торого соединена с первой группой выходов первого блока формирования единиц, а вторая группа входов второ го блока сумматоров соединена с первой группой выходов второго блока формирования единиц, вторая группа выходов которого соединена с первой группой входов первого блока сумматоров, вторая группа входов которого соединена со второй группой выходов первого блока формирования-единиц, информационная шина которого соединена с группой разр.дных выходов регистра делимого и информационной шиной первого сдвигателя, информационная шина второго блока формирования единиц соединейа с группой разрядных выходов первого сдвигателя, группа разрядных входов регистра делителя соединена с группой разрядных выходов второго блока вычитателей, первая группа входов которого соединена с группой выходов третьего блока сумматоров, а вторая группа входов второго блока вычитателей соединена с выходом второго блока сумматоров, первая группа входов которого соединена с первой группой выходов тре его блока формирования единиц, а вторая группа входов четвертого -блока сумматоров соединена с первой группой выходов четвертого блока формирования единиц, вторая группа выходов которого соединена с первой группой входов третьего блока сумматоров, вторая группа входов которого соединена со второй группой выходов третьего блока формирования единиц, информационная шина которого соединена с группой разрядных вы ходов регистра, делителя и информационной шиной второго сдвигателя, информационная шина четвертого блок формирования единиц соединена с- гру пой разрядных выходов второго сдвигателя. Блок анализа содержит с первого четырнадцатый элементы И, первый, второй, третий и четвертый элементы ИЛИ, причем первый вход первого элемента И соединен с первым входом четырнадцатого элемента И и первым входом группы блока анализа, второй вход первого элемента И соединен с первыми входами третьего, шестого, седьмого и двенадцатого элементов И и вторым входом группы блока анализ третий вход первого элемента И соединен со вторыми входами шестого, девятого и четырнадцатого элементов и третьим входом группы блока анали за, первый вход второго элемента И соединен со вторыми входами третьег четвертого, пятого, шестого и седьмого элементов И, третьим входом шестого элемента И и входом группы блока анализа, второй вход этого эл мента И соединен с первыми входами восьмого,девятого, десятого и одиннадцатого элементов И, вторь м входом двенадцатого элемента И и пятым входом группы блока анализа, третий вход второго элемента И соединен со вторыми входами восьмого и тринадцатого элементов И, третьими входами девятого и четырнадцатого элементов И и шестым входом группы блока анализа, четвертый вход второго элемента И соединен с первыми входами четвертого и пятого элементов И, третьими входами третьего, седьмого, восьмого. Двенадцатого и тринадцатого элементрв И, вторыми входами десятого, одиннадцатого элементов И и седьмым входом группы блока анализа, пятый вход второго элемента И соединен с четвертыми входами третьего, седьмого, восьмого, двенадцатого и транадцатого элементов И, третьими входами |четвертого и одиннадцатого элементов И и восьмым входом группы блока анализа, шестой выход второго элемента.И соединен-с пятыми входами седьмого и тринадцатого элементов И и девятым входом группы блока анализа, седьмой вход второго элемента И соединен с пятыми входами третьего, восьмого и двенадцатого элементов И, шестыми входами седьмого и тринадцатого элементов И и десятым входом группы блока анализа, шестой вход третьего элемента И соединен с четвертьтш вхбдами четвертого, шестого, девятого одиннадцатого и третьими входами пятого и десятого элементов И, седьмыми входами седьмого и тринадцатого элементов И, шестым входом двенадцатого элемента И и одиннадцатым входом группы блока анализа, пятай вход четвертого элемента И соединен с пятым входом одиннадцатого элемента И и двенадцатым входом группы блока анализа, первый вход пятого элемента И соединен с четвертым входом десятого элемента И и тринадцатым входом группы блока анализа, выход первого элемента И соединен с первыми входами перво.го и третьего элементов ИЛИ, выход четвертого элемента И - с четвертыми входами первого и третьего элементов ИЛИ, выход пятого элемента И - с пятыми входами nejpsoro и третьего элементов ИЛИ,выход шестого элемента И с шестым входом первого элемента ИЛИ и первым входом второго элемента ИЛИ, выход седьмого элемента И - с седьмым входом первого элемента ИЛИ и вторым входом второго элемента ИЛИ, выход восьмого элемента И - с третьим входом второго элемента ИЛИ и первым входом четвертого элемента ИЛИ, выход девятого элемента И - с четвертым входом второго элемента ИЛИ и вторым входом четвертогоэлемента ИЛИ, выход десятого элемента И - с шестым входом третьего элемента ИЛИ и треть им входом четвертого элемента ИЛИ, выход одиннадцатого элемента И - с седьмым входом третьего элемента ИЛ и четвертым входом четвертого элемента ИЛИ, вьлход двенадцатого элемента И - с восьмым входом третьего элемента ИЛИ и пятым входом четвертого элемента ИЛИ, выход тринадцатого элемента И - с девятым входом, третьего элемента ИЛИ и шестым входом четвертого элемента ИЛИ, вьссод четырнадцатого элемента И - с деся-. тым входом третьего элемента ИЛИ и седьмым входом четвертого элемента ИЛИ, выходы первого и четвертого эле jMGHTOB ИЛИ соединены с первым и вторым выходами первой группы блока ана лиза, выходы второго и третьего элементов ИЛИ соединены соответственно с первым и вторым выходами второй группы выходов блока анализа. Блок формирования сдвига содержит г разрядов (г 1,2,...,п, где п разрядность устройства), каждый из которых содержит первый и второй эле менты И и элемент ИЛИ, причем в каждом разряде первый вход первого элемента И соединен с первым входом вто рого элемента И и информационной шиной блока формирования сдвига, вторы входы первых элементов И г-ых разрядов соединены между собой и с управляющей шиной блока формирования сдви га, вторые входы вторых элементов И г-ых разрядов соединены между собой и с управляющей шиной блока формирования сдвига, выходы первых элементов И г-ых разрядов соединены с первыми входами элементов ИЛИ г-ых разрядов, выходы вторых элементов И г-ых разрядов соединены со вторыми входами элементов ИЛИ {г-1)-ых разрядов, а выходы схем ИЛИ соединены с выходной шиной блока формирования сдвига. Блок формирования единиц содержит г разрядов, каждый из которых содержит первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой элементы И, первый, второй, третий и четвертый элементы ИЛИ, причем первый вход первого элемента И соединен с первым входом пятого элемента И и информационной шиной блока формирования единиц, первый вход второго элемента И соединен с первым входом шестого элемента И и информационной шиной блока формирования еди ниц, второй вход первого элемента И соединен со вторыми входами второго, пятого и шестого элементов И и информационной шиной блока формирования единиц, первый вход третьего эле мента И соединен с первым входом сед мого элемента И и информационной шиной блока формирования единиц. первый вход четвертого элемента И соединен с первым входом восьмого элемента И и информационной шиной бгока формирования единиц, второй вход третьего элемента И соединен со вторыми входами четвертого, седьмого и восьмого элементов И и информационной шиной блока формирования единиц, третьи входы первого, третьего, шестого и восьмого элементов И соединены между собой и с управляющей шиной блока формирования единиц, третьи входы второго, четвертого, пятого и седьмого элементов И соединены между собой и с управляющей шиной блока формирования единиц, первый вход первого элемента ИЛИ соединен с выходом первого элемента И, а второй вход первого элемента ИЛИ - с выходом элемента И, первый вход второго элемента ИЛИ соединен с выхо дом третьего элемента И, а второй вход второго элемента ИЛИ - с выходом четвертого элемента И, первый вход третьего элемента ИЛИ соединен |С выходом пятого элемента И, а второй вход третьего элемента ИЛИ - с выходом шестого элемента И, первый вход четвертого элемента ИЛИ соединен с выходом седьмого элемента И, а второй вход четвертого элемента ИЛИ - с выходом восьмого элемента И, выходы первого и второго элементов ИЛИ соединены с первой группой выходов блока формирования единиц, а выходы третьего и четвертого элементов ИЛИ - со второй группой выходов блока формирования единиц. Введенные в предлагаемое устройство блоки вычитателей, блоки счетчиков положительн л1х и отрицательных единиц, блоки формирования единиц, блок формирования сдвига и блок анализа позволяют производить вычисления в избыточной знакоразрядной системе счисления с основанием 2 и разрядными цифрами, принимающими значение -3, -2, -1, О, 1, 2, 3. Это позволяет во всех случаях при выполнении суммирования устранять распространение переносов через все п разряды, что обеспечивает сокращение времени деления в предлагаемом устройстве. На фиг. 1 изображена блок-схема предлагаемого устройства деления; на фиг. 2 - функциональная схема блока анализа; на фиг. 3 - функциональная схема блока формирования сдвига на три разряда; на фиг. 4 - функциональная схема блоков формирования единиц на один разряд; на фиг. 5 - функциональная схема блоков счетчиков положительных и отрицательных единиц (три счетчика), вариант; на фиг. 6 функциональная схема блоков вычитателей .

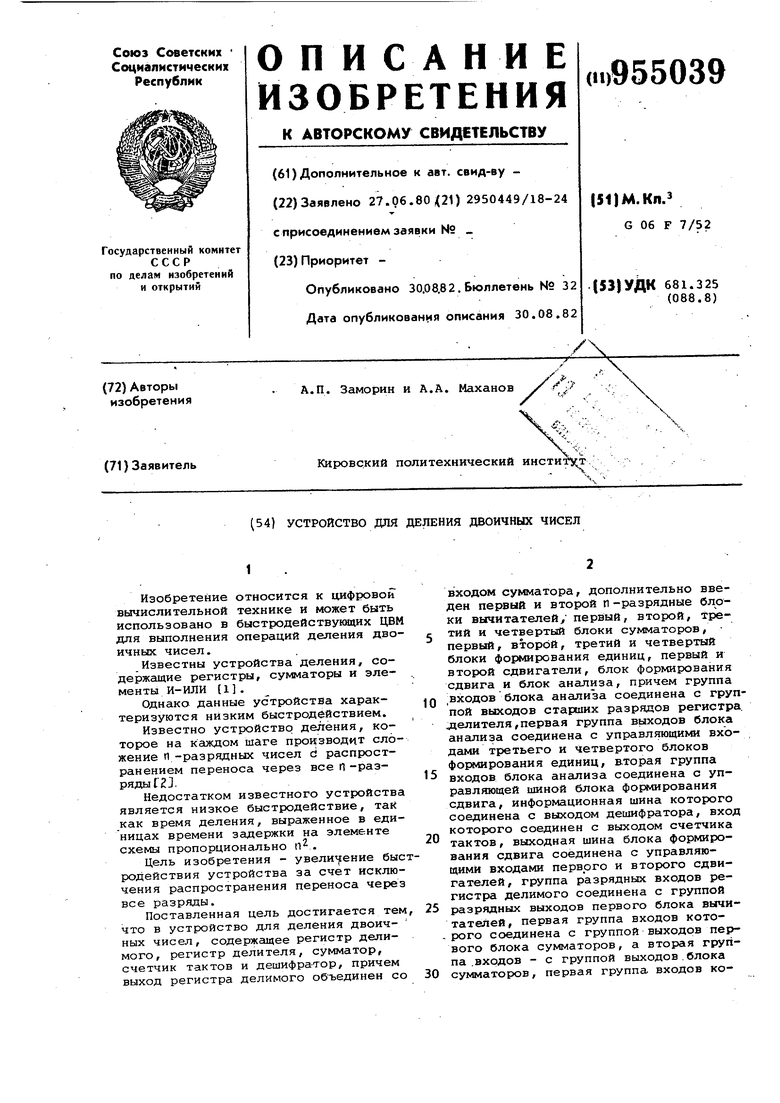

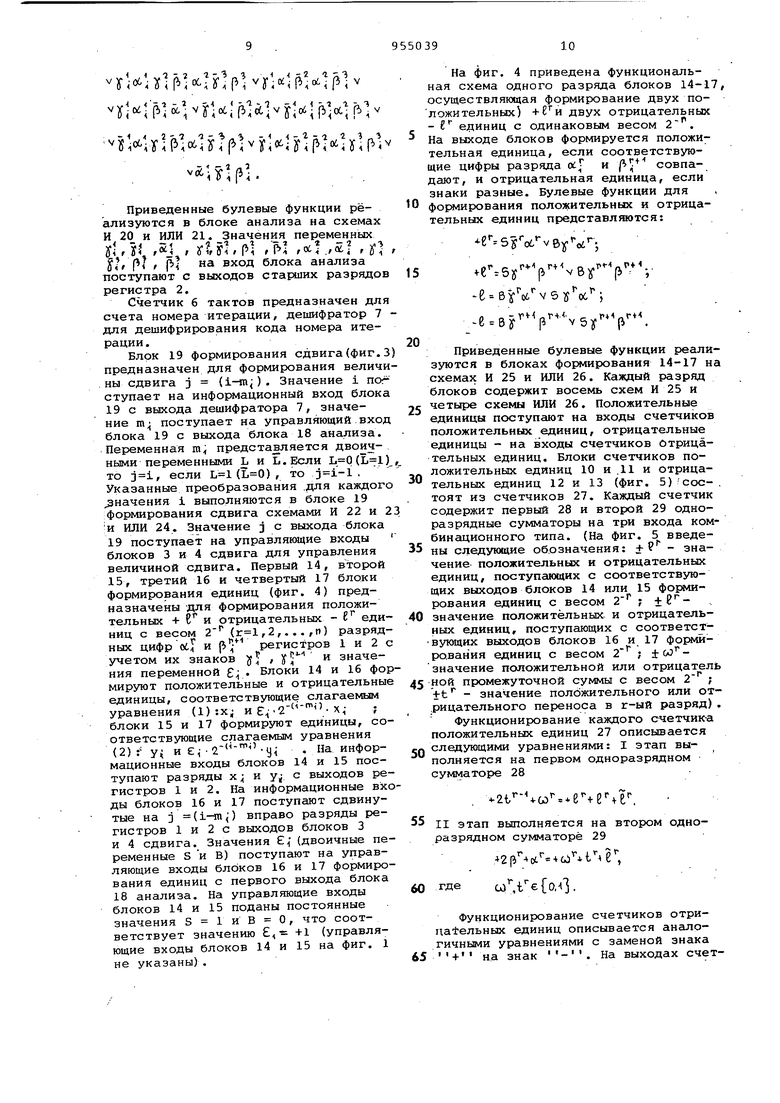

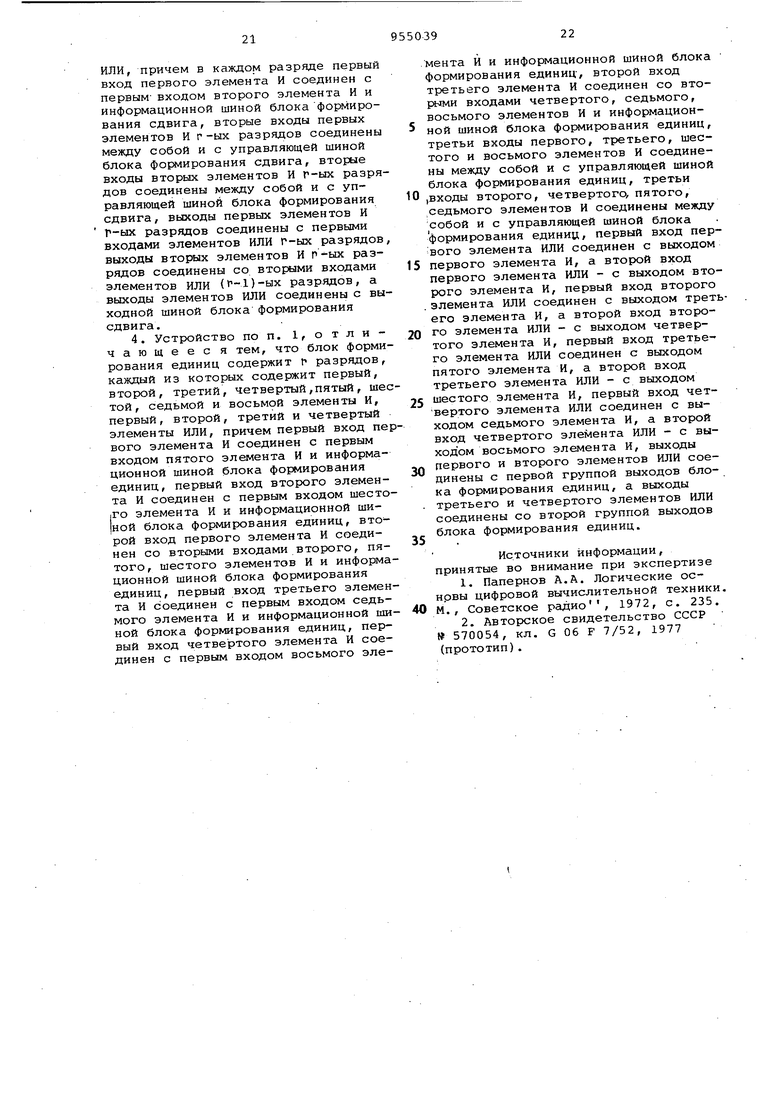

Устройство деления (фиг. 1) содержит регистр 1 делимого, регистр 2 делителя, первый 3 и второй 4 блоки сдвигателей, сумматор 5, счетчик б -тактов, дешифратор 7,первый 8 и второй 9 блоки вычитателей, первый 10 и второй 11 блоки счетчиков положительных единиц, первый 12 и второй 13 блоки счетчиков отрицательных единиц, первый 14 , второй 15 , третий 16 и четвертый 17 блоки формирования единиц, блок 18 анализа и блок 19 формирования сдвига.

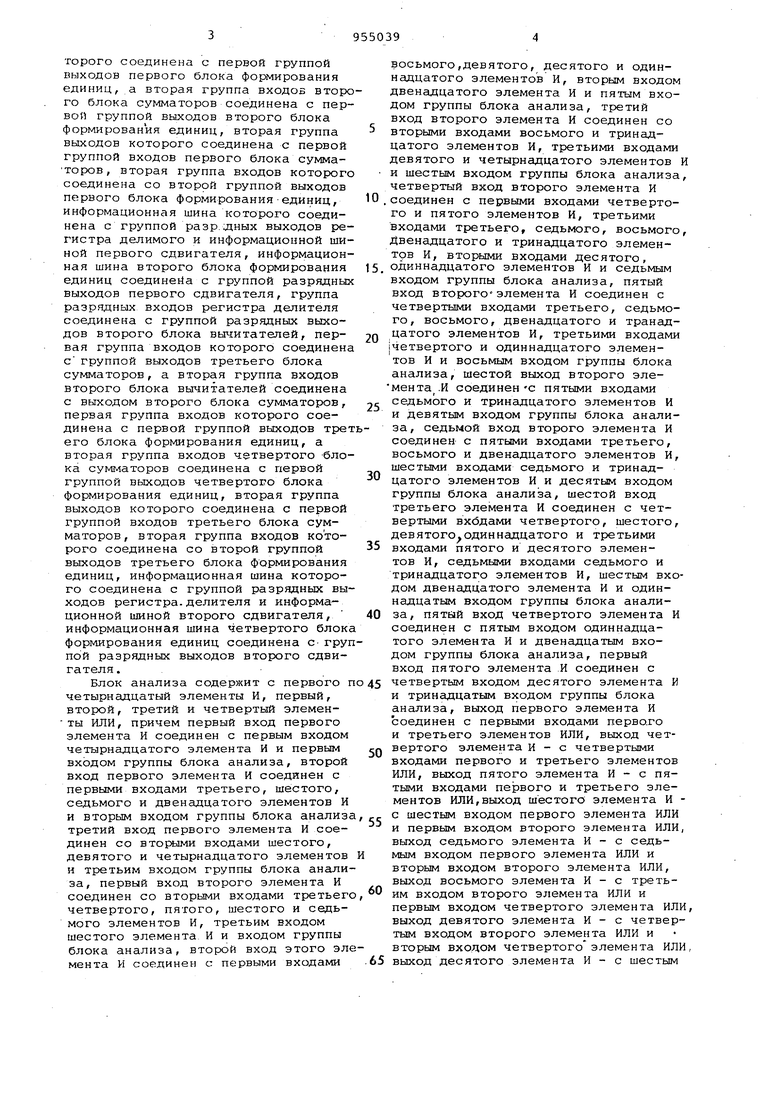

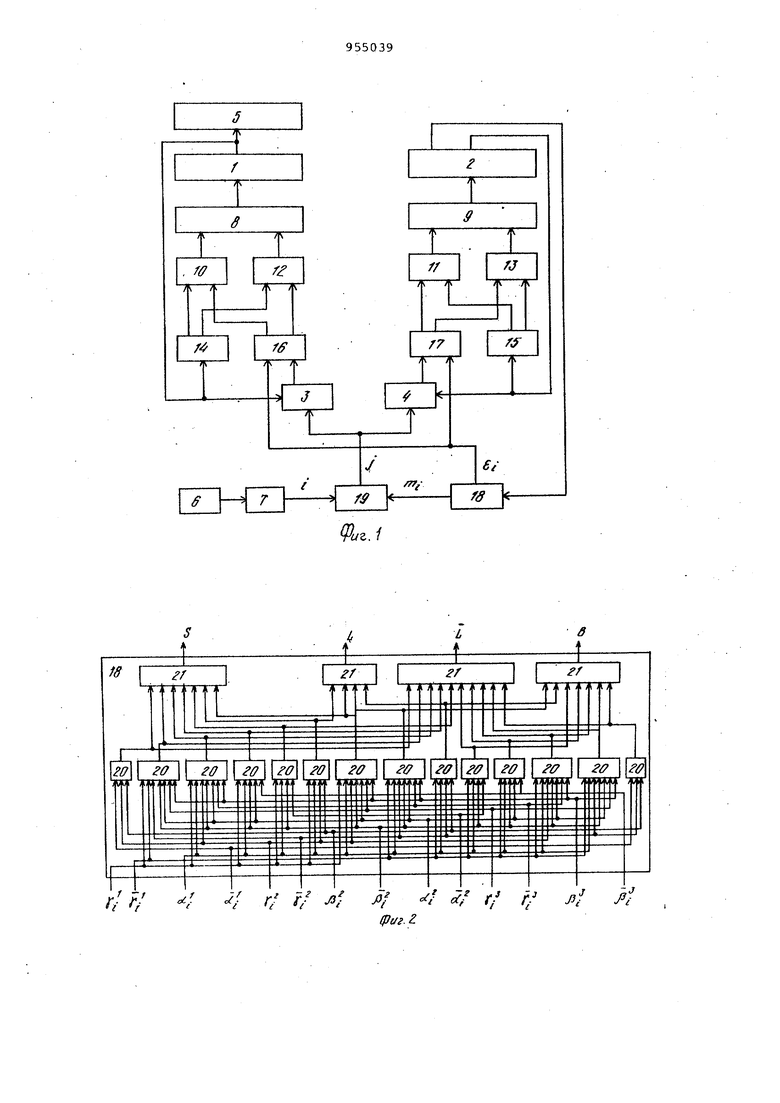

Блок 18 анализа (фиг. 2) содержит элементы И 20 и с.первого по четвертый элементы ИЛИ 21-24.

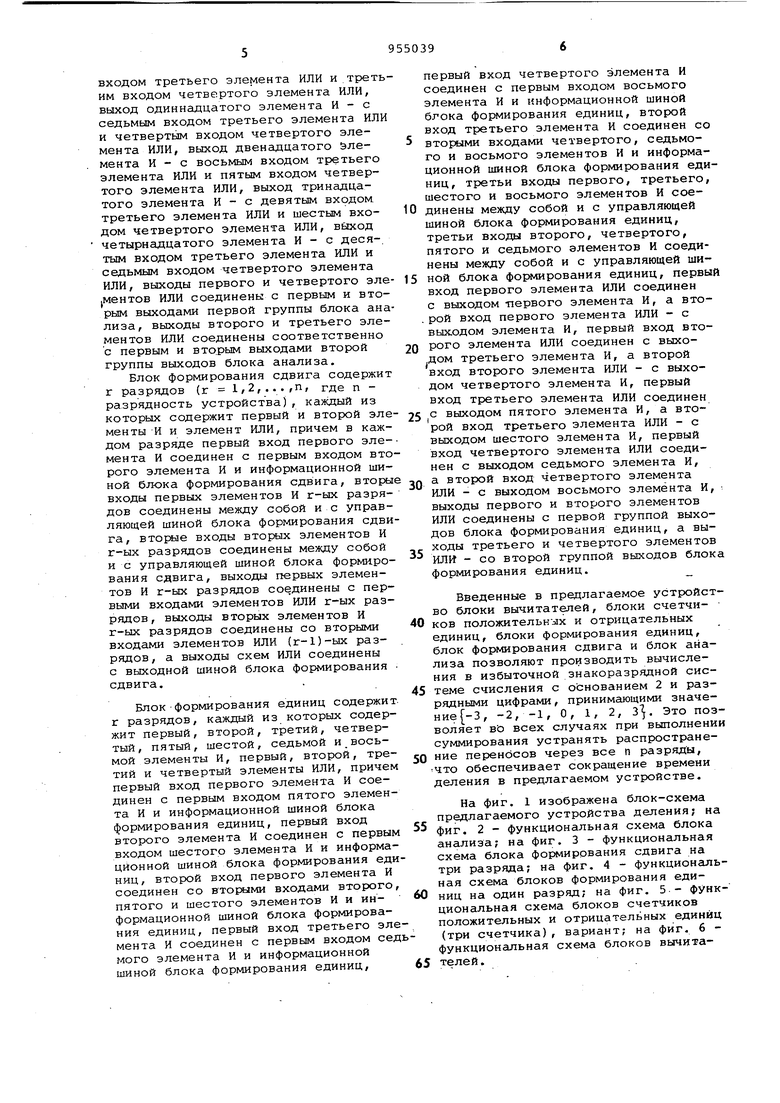

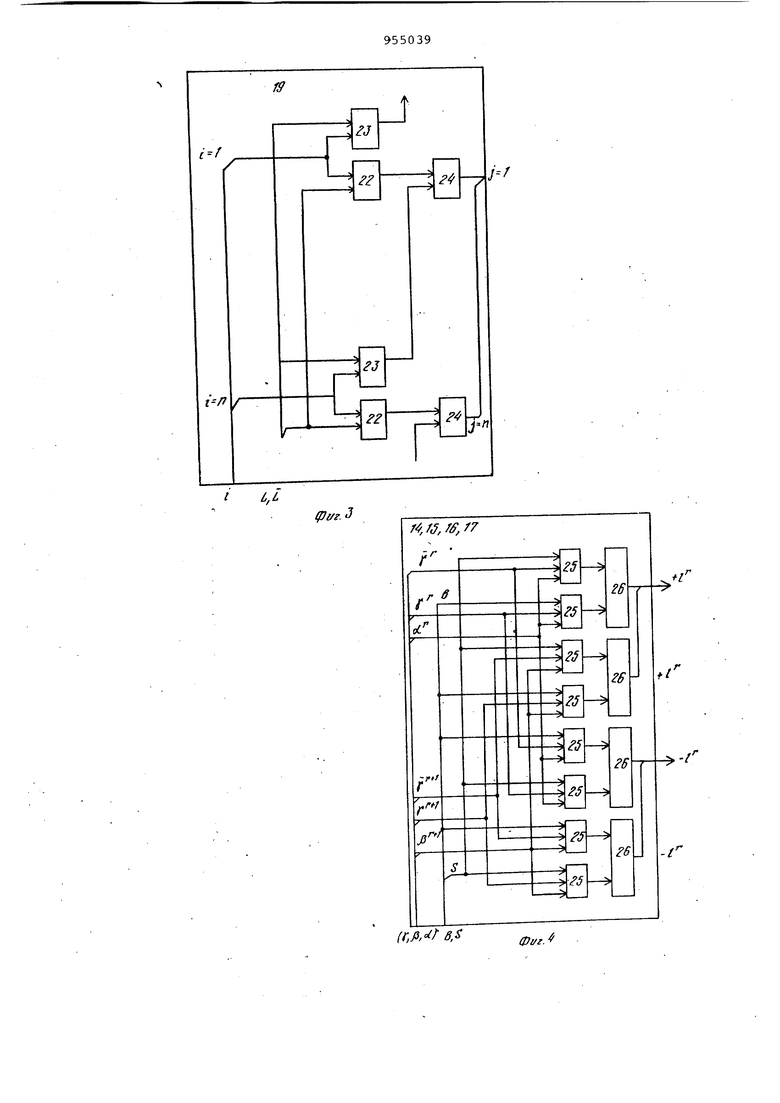

Блок 19 формирования сдвига (фиг. 3) содержит п разрядов, каждый разряд содержит первый и второй элементы схемы И 22 и 23 и элемент ИЛИ 24.

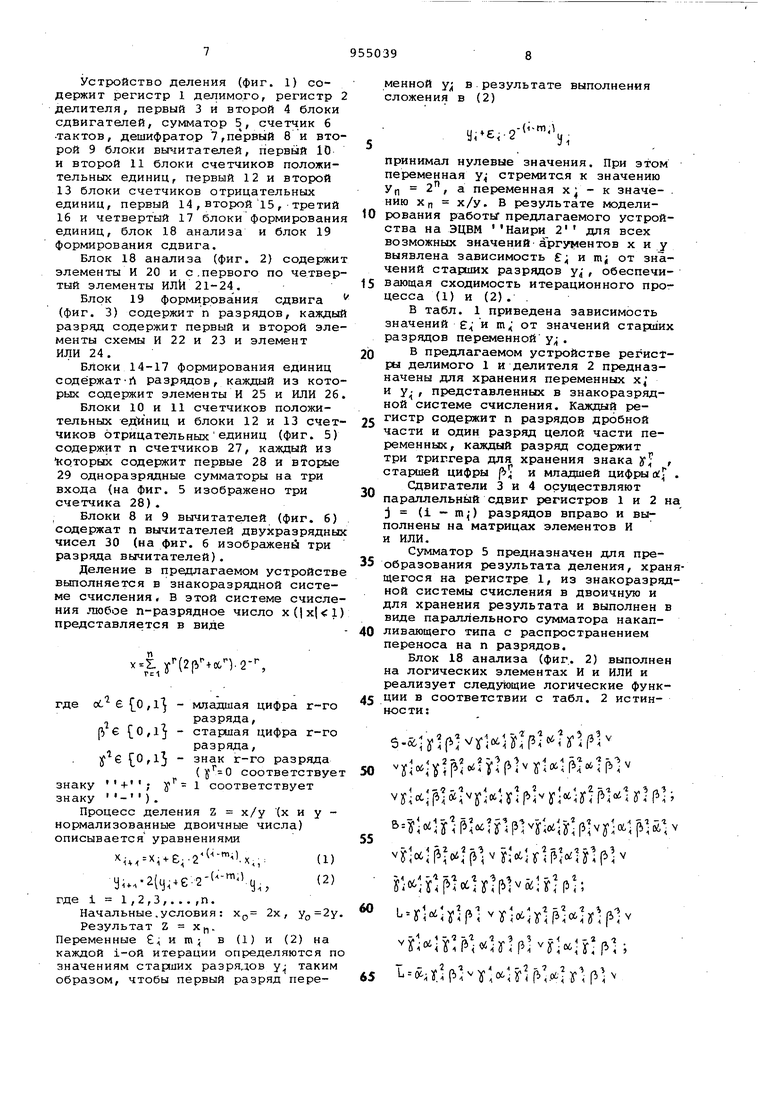

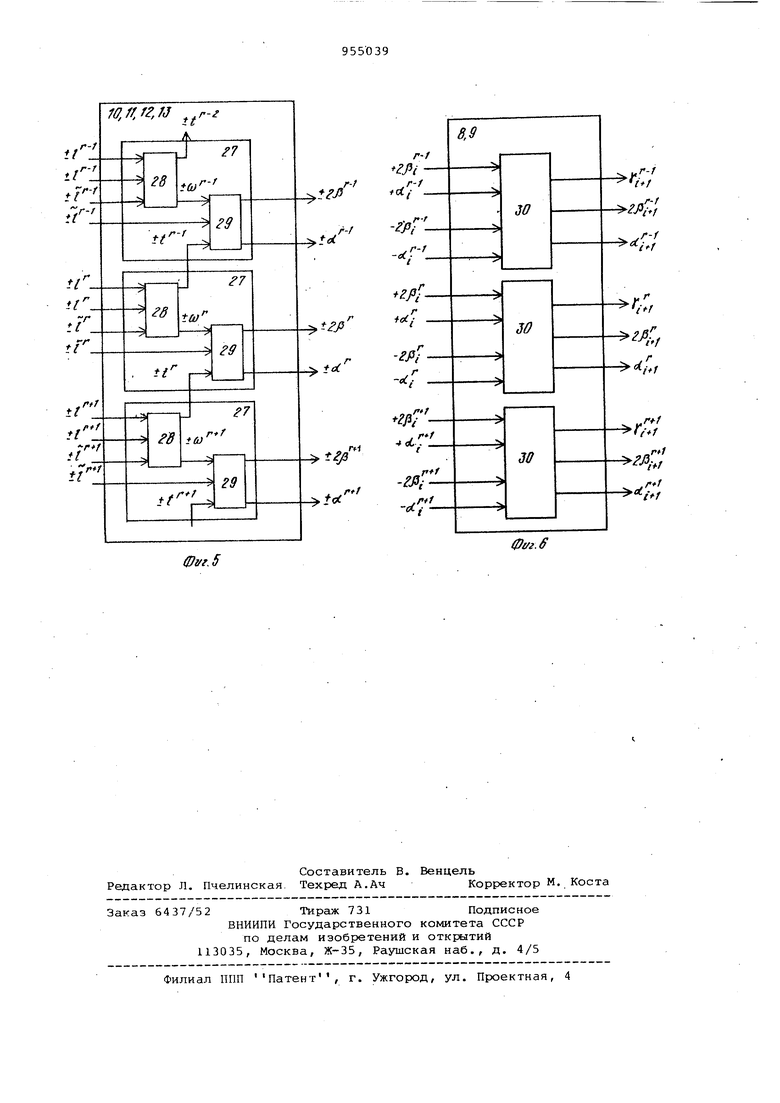

Блоки 14-17 формирования единиц содёржатЛ разрядов, каждый из которых содержит элементы И 25 и ИЛИ 26.

Блоки 10 и 11 счетчиков положительных единиц и блоки 12 и 13 счетчиков отрицательныхединиц (фиг. 5) содержит п счетчиков 27, каждый из которых содержит первые 28 и вторые 29 одноразрядные сумматоры на три входа (на фиг. 5 изображено три счетчика 28).

Блоки 8 и 9 вычитателей (фиг. 6) содержат п вычитателей двухразрядных чисел 30 (на фиг. 6 изображенй три разряда вычитателей).

Деление в предлагаемом устройстве выполняется в знакоразрядной системе счисления, В этой системе счисления любое п-разрядное число х(|х(1) представляется в виде

x (2f «V2где об е , 1 - младшая цифра г-го

разряда, е {0,1} - старшая цифра г-го

разряда, 0,1 - знак г-го разряда

( соответствует знаку +; у 1 соответствует

I I I

знаку

Процесс деления Z х/у (х и у нормализованные двоичные числа) описывается уравнениями

к- -X-4-P.)((1)

1 + -«, + t, ,

y...,.e., (2)

где ,2,3,...,n.

Начальные.условия : Хр 2х , .

Результат Z Xj,.

Переменные и т; в (1) и (2) на каждой i-ой итерации определяются по значениям старлих разрядов у таким образом, чтобы первый разряд переменной у в результате выполнения сложения в (2)

.., . У

принимал нулевые значения. При этом переменная стремится к значению УП 2, а переменная х - к значению Хп х/у. В результате моделирования работы предлагаемого устройства на ЭЦВМ Наири 2 для всех возможных значений- ёГргументов х и у выявлена зависимость и т от значений старших разрядов , обеспечивающая сходимость итерационного процесса (1) и (2). .

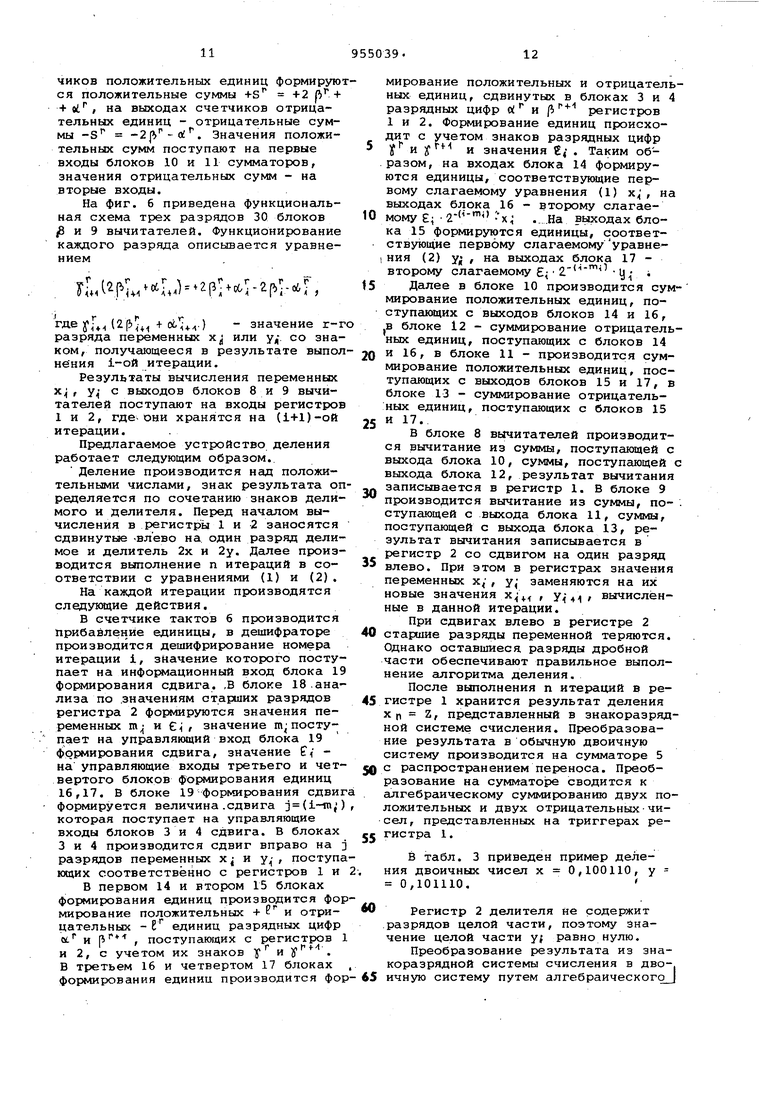

В табл. 1 приведена зависимость значений и т от значений старших разрядов переменной у.

В предлагаемом устройстве регистры делимого 1 и делителя 2 предназначены для хранения переменных х; и у, представленных в знакоразрядной системе счисления. Каждый регистр содержит п разрядов дробной части и один разряд целой части переменных, каждый разряд содержит три триггера для хранения знака yj , старицей цифры и младшей oij .

Сдвигатели 3 и 4 осуществляют параллельный сдвиг регистров 1 и 2 на j (i - m,) разрядов вправо и выполнены на матрицах элементов И и ИЛИ.

Сумматор 5 предназначен для преобразования результата деления, хранящегося на регистре 1, из знакоразрядной системы счисления в двоичную и для хранения результата и выполнен в виде параллельного сумматора накапливающего типа с распространением переноса на п разрядов.

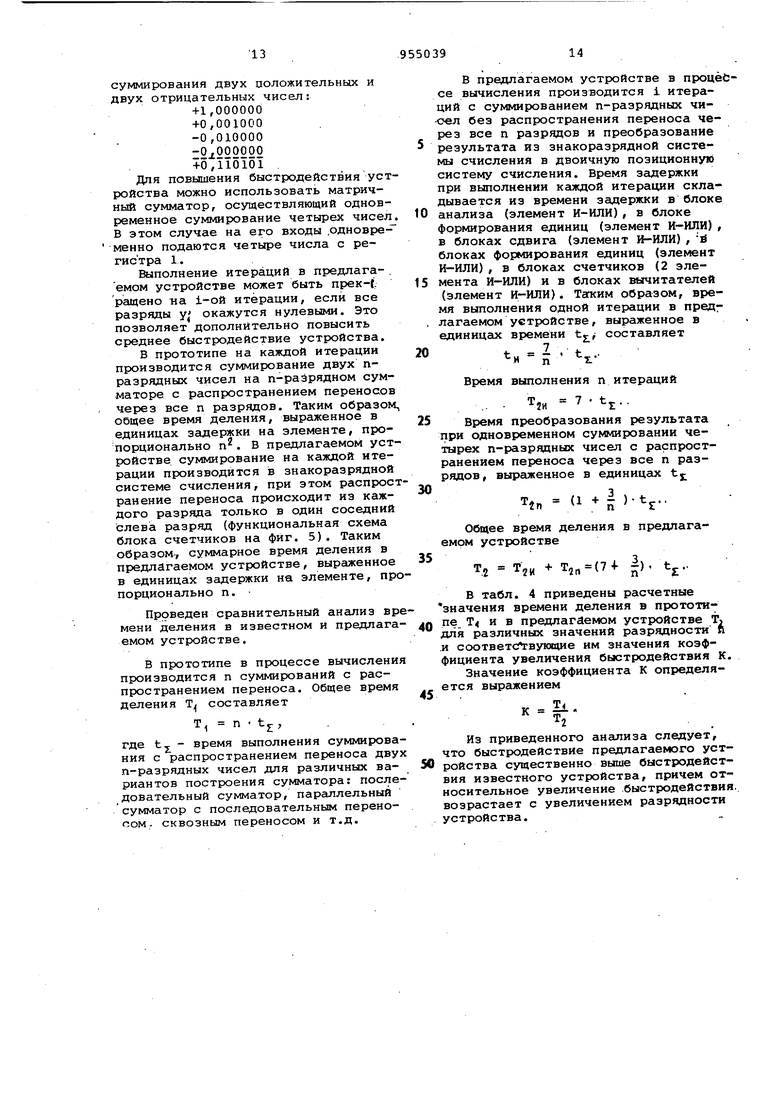

Блок 18 анализа (фиг.. 2) выполнен на логических элементах И и ИЛИ и реализует следующие логические функции в соответствии с табл. 2 истинное ти:

5-5.у1(.р (

vyl l5il4l :y fbb f df l lylf

b y Up: rP yXy f3 y; fi:°i

5l i o6 y f «;кJp;

I yl y | lvy ;y fblo6:y |blv

-K iY:pio.

-- yj P- Y y .o y P V

(ocly,..lplv

ni I S y ifilc l lpl fblv

XylMrt-yt vy rbploi ylf b

r..

Приведенные булевые функции реализуются в блоке анализа на схемах И 20 и ИЛИ 21. Значения переменных

fj , Й- ,об, , li I на вход блока анализа поступают с выходов старших разрядов регистра 2.

Счетчик 6 тактов предназначен для счета номера итерации, дешифратор 7 для дешифрирования кода номера итерации.

Блок 19 формирования сдвига(фиг.3 предназначен для формирования величи.ны сдвига j (i-TO). Значение i nor ступает на информационный вход блока 19 с выхода дешифратора 7, значение т поступает на управляющий вход блока 19 с выхода блока 18 анализа. Переменная т; представляется двоичными переменными L и Ь.Если () то , если (), то . Указанные преобразования .для каждого значения i выполняются в блоке 19 формирования сдвига схемами И 22 и 2 и ИЛИ 24. Значение j с выхода блока 19 поступает на управляницие входы блоков 3 и 4 сдвига для управления величиной сдвига. Первый 14, второй 15, третий 16 и четвертый 17 блоки формирования единиц (фиг. 4) предназначены для формирования положительных + Е и отрицательных - б единиц с весом 2 (,2,... ,11) разрядных цифробУ и ( регистров 1 и 2 с учетом их знаков J / и значения переменной . Блоки 14 и 16 формируют положительные и отрицательные единицы, соответствующие слагаемым уравнения (1) :xj и х, ; блоки 15 и 17 формируют единицы, соответствующие слагаемым уравнения (2): у( и е,-2 -у . На информационные входы блоков 14 и 15 поступают разряды х и Yj с выходов регистров 1 и 2. На информационные входы блоков 16 и 17 поступают сдвинутые на j (i-tn;) вправо разряды регистров 1 и 2 с выходов блоков 3 и 4 сдвига. Значения EI(двоичные переменные S и В) поступают на управляющие входы блоков 16 и 17 формирования единиц с первого выхода блока 18 анализа. На управляющие входы блоков 14 и 15 поданы постоянные значения S 1 и В О, что соответствует значению - +1 (управляющие входы блоков 14 и 15 на фиг. 1 не указаны).

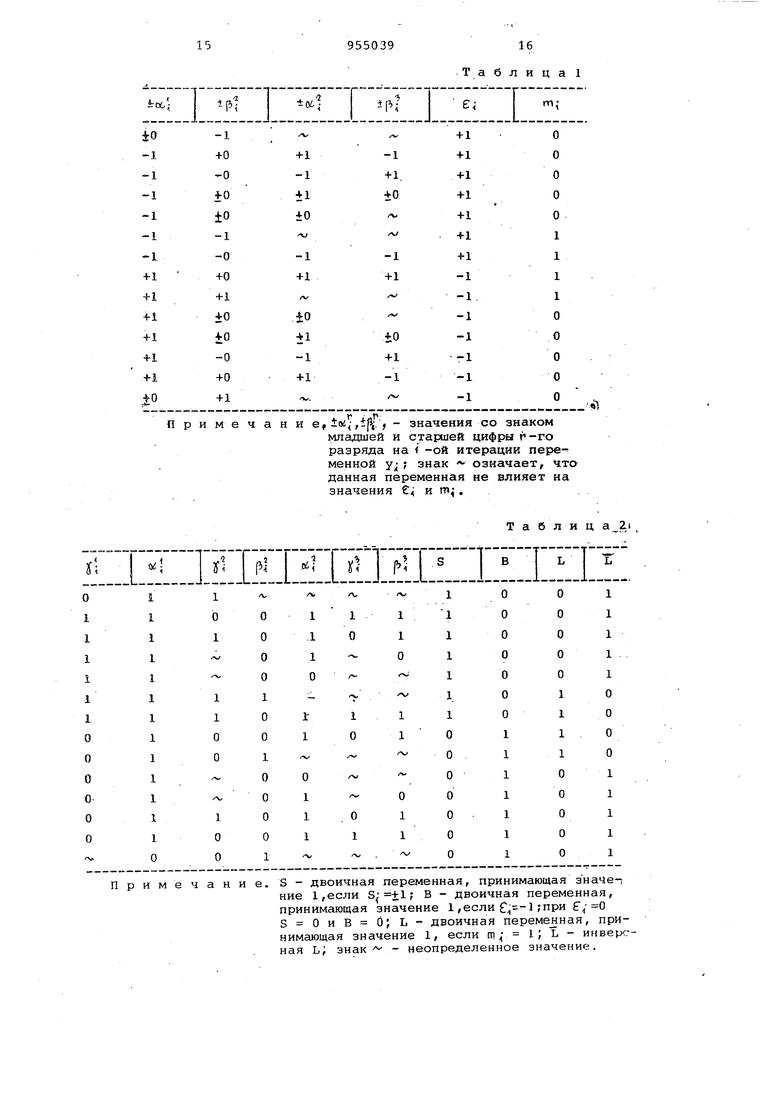

На фиг. 4 приведена функциональная схема одного разряда блоков 14-17, осуществляющая формирование двух положительных) +6и двух отрицательных - 1 единиц с одинаковым весом 2, На выходе блоков формируется положительная единица, если соответствующие цифры разряда ctj и совпадают, и отрицательная единица, если знаки разные. Булевые функции для О формирования положительных и отрицательных единиц представляются:

e 55V%ByV-,

5 ..

e-6YVv5 V

nY ,,r+

е вГ Г

Приведенные булевые функции реализуются в блоках формирования 14-17 на схемах И 25 и ИЛИ 26. Каждый разряд блоков содержит восемь схем И 25 и

четыре схемы ИЛИ 26. Положительные единицы поступают на входы счетчиков положительных единиц, отрицательные единицы - на входы счетчиков Отрицательных единиц. Блоки счетчиков положительных единиц 10 и .11 и отрицательных единиц 12 и 13 (фиг. 5)сое- . тоят из счетчиков 27. Каждый счетчик содержит первый 28 и второй 29 одноразрядные сумматоры на три входа комбинационного типа. (На фиг. 5 введены следукяцие обозначения: ± - значение- положительных и отрицательных единиц, поступающих с соответствующих выходов блоков 14 или 15 формирования единиц с весом 2 ; +8значение положительных и отрицательных единиц, поступающих с соответствующкх выходов блоков 16 и 17 фоЕ шрования единиц с весом 2 ; ±созначение положительной или отрицатель

ной промежуточной суммы с весом 2 ; - значение положительного или отрицательного переноса в г-ый разряд).

Функционирование каждого счетчик-а положительных единиц 27 описывается

следующими уравнениями: I этап выSOполняется на первом одноразрядном сумматоре 28

, 2t-4co% e%e%r.

II этап выполняется на втором одноразрядном сумматоре 29

+ , где a),t4{o,il.

Функционирование счетчиков отрииа ельных единиц описывается анало гичными уравнениями с заменой знака + на знак -. На выходах счетчиков положительных единиц Формируются положительные суммы +S +2 р + + ti I на выходах счетчиков отрицательных единиц - отрицательные суммы -S . Значения положительных сумм поступают на первые входы блоков 10 и 11 сумматоров, значения отрицательных сумм - на вторые входы.

На фиг. б приведена функциональная схема трех разрядов 30 блоков |8 и 9 вычитателей. Функционирование каждого разряда описывается уравнением

т1...2р% -г ь;-йГ,

где у П2р + + .) - значение г-г разряда переменных х или у. со знаком, получающееся в результате выполнения i-ой итерации.

Результаты вычисления переменнЕлх 4 , с выходов блоков 8 и 9 вычитателей поступают на входы регистров 1 и 2, где-они хранятся на (1+1)-ой итерации.

Предлагаемое устройство деления работает следующим образом.

Деление производится над положительными числами, знак результата определяется по сочетанию знаков делимого и делителя. Перед началом вычисления в регистры 1 и 2 заносятся сдвинутые -влево на один разряд делимое и делитель 2х и 2у. Далее производится выполнение п итераций в соответствии с уравнениями (1) и (2). На каждой итерации производятся следукицие действия.

в счетчике тактов 6 производится прибавление единицы, в дешифраторе производится дешифрирование номера итерации i, значение которого поступает на информационный вход блока 19 фосфшрования сдвига. ,В блоке 18 .анализа по .значениям старших разрядов регистра 2 формируются значения переменных га и , значение т поступает на управляющий вход блока 19 формирования сдвига, значение на управляющие входы третьего и четвертого блоков формирования единиц 16,17. В блоке 19 формирования сдвиг формируется величина .сдвига j (i-ro,) которая поступает на управляющие входы блоков 3 и 4 сдвига. В блоках 3 и 4 производится сдвиг вправо на j разрядов переменных х и , поступающих соответственно с регистров 1 и

В первом 14 и втором 15 блоках формирования единиц производится формирование положительных + f и отрицательных - Е единиц разрядных цифр ос и , поступающих с регистров 1 и 2, с учетом их знаков у и . В третьем 16 и четвертом 17 блоках формирования единиц производится формирование положительных и отрицательных единиц, сдвинутых в блоках 3 и 4 разрядных цифр и и /i регистров 1 и 2. Формирование единиц происходит с учетом знаков разрядных цифр

У и и значения ti . Таким образом, на входах блока 14 формируются единицы, соответствующие первому слагаемому уравнения (1) х; , на выходах блока 16 - второму слагаемому ; 2 v х .На выходах блока 15 формируются единицы, соответствующ ие первому слагаемомууравнеI ния (2) у , на выходах блока 17 второму слагаемому у .

5 Далее в блоке 10 производится суммирование положительных единиц, поступающих с выходов блоков 14 и 16, jB блоке 12 - суммирование отрицательных единиц, поступающих с блоков 14

0 и 16, в блоке 11 - производится суммирование положительных единиц, поступсиощих с выходов блоков 15 и 17, в блоке 13 - суммирование отрицательных единиц, поступающих с блоков 15

5 и 17В блоке 8 вычитателей производится вычитание из суммы, поступающей с выхода блока 10, суммы, поступающей с выхода блока 12, результат вычитания

Q записывается в регистр 1. В блоке 9 производится вычитание из суммы, по- . ступающей с выхода блока 11, суммы, поступающей с выхода блока 13, результат вычитания записывается в регистр 2 со сдвигом на один разряд

влево. При этом в регистрах значения переменных , у,- заменяются на их новые значения , вычисленные в данной итерации.

При сдвигах влево в регистре 2

0 старшие разряды переменной теряются. Однако оставшиеся разряды дробной части обеспечивают правильное выполнение алгоритма деления.

После выполнения п итераций в регистре 1 хранится результат деления Хр Z, представленный в знакоразрядной системе счисления. Преобразование результата в обычную двоичную систему производится на сумматоре 5

0 с распространением переноса. Преобргазование на сумматоре сводится к алгебраическому суммирюванию двух положительных и двух отрицательных-чисел, представленных на триггерах регистра 1.

В табл. 3 приведен пример деления двоичных чисел х 0,100110, у 0,101110.

Регистр 2 делителя не содержит .разрядов целой части, поэтому значение целой части yj равно нулю.

Преобразование результата из знакоразрядной системы счисления в дво-.

5 ичную систему путем алгебраического |

суммирования двух положительных и двух отрицательных чисел:

+1,000000

+0,001000

-0,010000

-0 000000

+0,110101

Для повышения быстродействия устройства можно использовать матричный сумматор, осуществляющий одновременное суммирование четырех чисел В этом случае на его входы .одновременно подаются четыре числа с регистра 1.

Выполнение итераций в предлага-. емом устройстве может быть прек-Г ращено на i-ой итерации, если все разряды окажутся нулевыми. Это позволяет дополнительно повысить среднее быстродействие устройства. В прототипе на каждой итерации производится суммирование двух празрядных чисел на п-райрядном сумматоре с распространением переносов через все п разрядов. Таким образом, общее время деления, выраженное в единицах задержки на элементе, пропорционально п. В предлагаемом устройстве суммирование на каждой итерации производится в знакоразрядной системе счисления, при этом распространение переноса происходит из каждого разряда только в один соседний слева разряд (функциональная схема блока счетчиков на фиг. 5). Таким образом-, суммарное время деления в предлагаемом устройстве, выраженное в единицах задержки на элементе, пропорционально п.

Проведен сравнительный анализ времени деления в известном и предлагаемом устройстве.

В прототипе в процессе вычисления производится п суммирований с распространением переноса. Общее время деления Т составляет

TI п .t,

где tj- - время выполнения суммирования с распространением переноса двух п-разрядных чисел для различных вариантов построения сумматора: последовательный сумматор, параллельный сумматор с последовательным переносом, сквозным переносом и т.д.

В предлагаемом устройстве в процессе вычисления производится i итераций с суммированием п-разрядных без распространения переноса через все п разрядов и преобразование

результата из знакоразрядной системы счисления в двоичную позиционную систему счисления. Время задержки при выполнении каждой итерации складывается из времени задержки в блоке

анализа (элемент И-ИЛИ), в блоке формирования единиц (элемент И-ИЛИ), в блоках сдвига (элемент И-ИЛИ), и блоках формирования единиц (элемент И-ИЛИ), в блоках счетчиков (2 элемента И-ИЛИ) и в блоках вычитателей (элемент И-ИЛИ). Тагким образом, время выполнения одной итерации в пред лагаемом устройстве, выраженное в единицах времени составляет

J4t.

Время выполнения п итераций

... Tj, 7 . t..

25 Время преобразования результата при одновременном суммировании четырех п-разрядных чисел с распространением переноса через все п разрядов, выраженное в единицах t

30

U + )-t,.,

tr

Общее время деления в предлагаемом устройстве

35

ги Т2„ ( ). tj...

Z

в табл. 4 приведены расчетные значения времени деления в прототипе Т и в предлагаемом устройстве Т, для различных значений разрядности п и соответС гвукхцие им значения коэффициента увеличения быстродействия К. Значение коэффициента К определяется выражением

к |1.

Из приведенного анализа следует, что быстродействие предлагаемого устройства существенно выше быстродействия известного устройства, причем относительное увеличение .быстродействия, возрастает с увеличением разрядности устройства.

95503916

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU911519A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 1988 |

|

SU1755650A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Вычислительное устройство | 1979 |

|

SU885994A1 |

| Устройство для умножения элементов поля Галуа GF(2 @ ) при образующем полиноме F(х)=х @ +Х @ +х @ +х @ +1 | 1989 |

|

SU1716504A1 |

| Арифметическое устройство | 1976 |

|

SU664171A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1750060A1 |

Примечание. S- двоичная переменная, принимающая эначе-i ние 1,если В - двоичная переменная, принимающая значение 1,если f -l;при f 0 S двоичная переме ная, принимающая значение 1, если m i; L - инверсная L; знак - неопределенное значение.

Формула изобретения

Таблица4

маторов, а вторая группа входов - с группой выходов второго блока сум0маторов, первая группа входов которого соединена с первой группой выходов первого блока формирования единиц, а вторая группа входов второго блока сумматоров соединена с

5 первой группой выходов второго блока формирования единиц, вторая груп- па выходов которого соединена с первой группой входов первого блока сумматоров, вторая группа входов ко0торого соединена со второй группой (ВЫХОДОВ первого блока формирования единиц, информационная шина которого соединена с группой разрядных выходов регистра делимого и информационной шиной первого сдвигателя, информационная шина второго блока формирования единиц соединена с группой разрядных выходов первого сдвигателя, группа разрядных входов регистра делителя соединена с группой разрядных

0 выходов второго блока вычитателей, первая группа входов которого соединена с группой выходов третьего блока сумматоров, а вторая группа входов второго блока вычитателей - с

5 выходом четвертого блока сумматоров, первая группа входов которого соединена с первой группой выходов третьего блока формирования единиц, а вторая группа входов четвертого блока

0 сумматоров соединена с первой груп- ; пой выходов четвертого блока фоЕ)МИрования единиц, вторая группа выходов которого соединена с первой группой входов третьего блока сумматоров, 5 вторая группа входов которого соедиг йена со второй группой выходов треть его блока формирования единиц, информационная агина которого соединена с группой разряднж ВЕЛХОДОВ регистра делителя и информационной шиной второго сдвигателя, информационная шина четвертого блока формирования единиц соединена с группой разрядных выходов второго сдвигателя. 2. Устройство по п. 1,отлич а ю. щ е е с я тем, что блок анал-иза содержит с первого по четырнадцатый элементы И, первый, второй,, третий и четвертый элементы ИЛИ, при ч;ем первый вход первого элемента И соединен с первым входом четырнадцатого, элемента И и первым входом труп иы блока анализа, второй вход первого элемента И соединен с первыми вхо дами третьего, шестого, седьмого и двенадцатого элемеЕ1тов И и вторым входом группы блока анализа, третий вход первого элемента И соединен со вторшли входами шестого, девятого и четырнадцатого элементов И и третьим входом группы блока анализа, первый вход второго элемента И соединен со вторыми входами третьего, четвертого, пятого и седьмого элементов И, третьим входом шестого элемента И и четвертым вх:одом группы блока анализа, второй вход второго элемента К соединен с первыми входами восьмого девятого, десятого, одиннадцатого и тринадцатого элементов И, вторым входом двенадцатого элемента И и пятым входом группы блока анализа, третий вход второго элемента И соединен со вторыми входами восьмого и тринадцатого элементов И, третьими входами девятого и четырнадцатого элементов И и шестым входом группы блока анализа, четвертый вход второго элемента И соединен с первыми входами четвертого и пятого элементов И, третьими входами третьего, седьмого, восьмого,-двенадцатого и тринадцатого элементов И,, вторыми .входами десятого и одиннадцатого элементов И и седьмым входом группы блока анализ а,пятый вход второго эле мента И соединен с четвертыми входами третьего, седьмого, восьмого, две надцатого и тринадцатого элементов третьими входами четвертого и одиннадцатого элементов И и восьмым входом группы блока анализа, шестой вхо второго элемента И соединен с пятыми входами седьмого и тринадцатого элементов и и девятым входом группы бло ка анализа, седьмой вход второго эл мента И соединен с пятыми входами третьего, восьмого и двенадцатого элементов И, шестыми входами седьмо тринадцатого элементов И десятым вхо дом группы блока анализа, шестой вход третьего элемента И соединен с четвертым; входами четвертого, шестого, девятого, одиннадцато о, треть ими входами пятого и десятого элементов И, седьмыми входами седьмого и тринадцатого элементов И, шестым входом двенадцатого элемента И и одиннадцатым входом группы блока ана лиза, пятый вход четвертого элемента И соединен с. пятым входом одиннадцатого элементаИ и двенадцатым входом группы .блока анализа, четвертый вход пятого элемента И соединен с четвертым входом десятого элемента И и тринадцатым входом группы блока анализа, выход первого элемента И соединен с первыми входами первого и TpeTbeto элементов ИЛИ, выход второго элемента И - со вторыми входами первого и Третьего элементов ИЛИ, выход третьего элемента И - с третьими входами первого и третьего элементов ИЛИ, выход четвертого элемента И - с четвертыми входами первого и третьего элементов ИЛИ, выход пятого элемента И - с пятыми входами первого и третьего элементов ИЛИ, выход шестого элемента И - с шестым входом первого элемента ИЛИ и первым входом второго злементэ ИЛИ, выход седьмого элемента И - с седьмым входом первого элемента ИЛИ и вторим входом второго элемента ИЛИ, выход восьмого элемента И - с третьим входом второго элемента ИЛИ и первым входом четвертого элемента ИЛИ, выход девятого элемента И - с четвертым входом второго элемента ИЛИ и вторым входом четвертого элемента ИЛИ, выход десятого элемента И - с шестым входом третьего элемента ИЛИ и третьим входом четвертого элемента ИЛИ, выход одиннадцатого элемента И - с седьмым входом третьего элемента ИЛИ и четвертым входом четвертого элемента ИЛИ, выход двенадцатого элемента И - с восьмым входом третьего элемента ИЛИ и пятым входом четвертого элемента ИЛИ, выход тринадцатого элемента И - с девятым вхором третьего элемента ИЛИ и шестым входом четвертого элемента ИЛИ, а .выход четырнадцатого элемента И - с .десятым входом третьего элемента ИЛИ и седьмым входом четвертого элемента ИЛИ, выходы первого и четвертого элементов ИЛИ соединены соответственно с nepBfcjM и вторым выходами первой группы выходов блока анализа, выходы второго и третьего элементов . ИЛИ соединены соответственно с первым и ВТО1ЖЛМ выходами второй группы выходов блока анализа, 3. Устройство по п. 1, о т л и чающеес я тем, что блок формирования сдвига содержит г разрядов ,2,.., ,п, где п.-разрядность устройства) , каждый из которых содержит шервый и второй элементы И и элемент

ИЛИ, причем в каждом разряде первый вход первого элемента И соединен с первым- входом второго элемента И и информационной шиной блока формирования сдвига, вторые входы первых элементов И р-ых разрядов соединены между собой и с управляющей шиной блока формирования сдвига, вторые входы вторых элементов И г-ых разрядов соединены между собой и с управляющей шиной блока формирования сдвига, выходы первых элементов И f-tjDc разрядов соединены с первыми входами элементов ИЛИ г-ых. разрядов выходы вторых элементов И р-ых разрядов соединены со вторыми входами элементов ИЛИ (-1)-ых разрядов, а выходы элементов ИЛИ соединены с выходной шиной блока формирования сдвига.

4, Устройство по п. 1,отличающеес я тем, что блок формирования единиц содержит t разрядов, каждый из которых содержит первый, второй, третий, четвертый,пятый, шестой, седьмой и восьмой элементы И, первый, второй, третий и четвертый элементы ИЛИ, причем первый вход первого элемента И соединен с первым входом пятого элемента И и информационной шиной блока формирования единиц, первый вход второго элемента И соединен с первым входом шестого элемента И и информационной шиной блока формирования единиц, вто рой вход первого элемента И соединен со вторыми входами второго, пятого, шестого элементов И и информационной шиной блока формирования единиц, первый вход третьего элемента И соединен с первым входом седьмого элемента И и информационной шиной блока формирования единиц, первый вход четвертого элемента И соединен с первым входом восьмого элемента И и информационной шиной блока формирования единиц, второй вход третьего элемента И соединен со вторыми входами четвертого, седьмого, восьмого элементов И и информационной шиной блока формирования единиц, третьи входы первого, третьего, шестого и восьмого элементов И соединены между собой и с управляющей шиной блока формирования единиц, третьи

0 (ВХОДЫ второго, четвертого, пятого, седьмого элементов И соединены между собой и с управляющей шиной блока формирования единиц, первый вход первого элемента ИЛИ соединен с выходом

5 первого элемента И, а второй вход первого элемента ИЛИ - с выходом второго элемента И, первый вход второго .элемента ИЛИ соединен с выходом третьего элемента И, а второй вход второго элемента ИЛИ - с выходом четвер0того элемента И, первый вход третьего элемента ИЛИ соединен с выходом пятого элемента И, а второй вход третьего элемента ИЛИ - с выходом шестого элемента И, первый вход чет5вертого элемента ИЛИ соединен с выходом седьмого элемента И, а второй вход четвертого элемента ИЛИ - с выходом восьмого элемента И, выходы первого и второго элементов ИЛИ сое0динены с первой группой выходов блока формирования единиц, а выходы третьего и четвертого элементов ИЛИ соединены со второй группой выходов блока формирования единиц.

5

Источники информации, принятые во внимание при экспертизе

0 М., Советское радио , 1972, с. 235.

(Риг. i

L,L

(pi/г.З

(r,ft,.S

(Diff,5

фуге

Авторы

Даты

1982-08-30—Публикация

1980-06-27—Подача