1

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях .

Цель изобретения - повышение быст родействия за счет сокращения числа требуемьпс для вычисления операций.

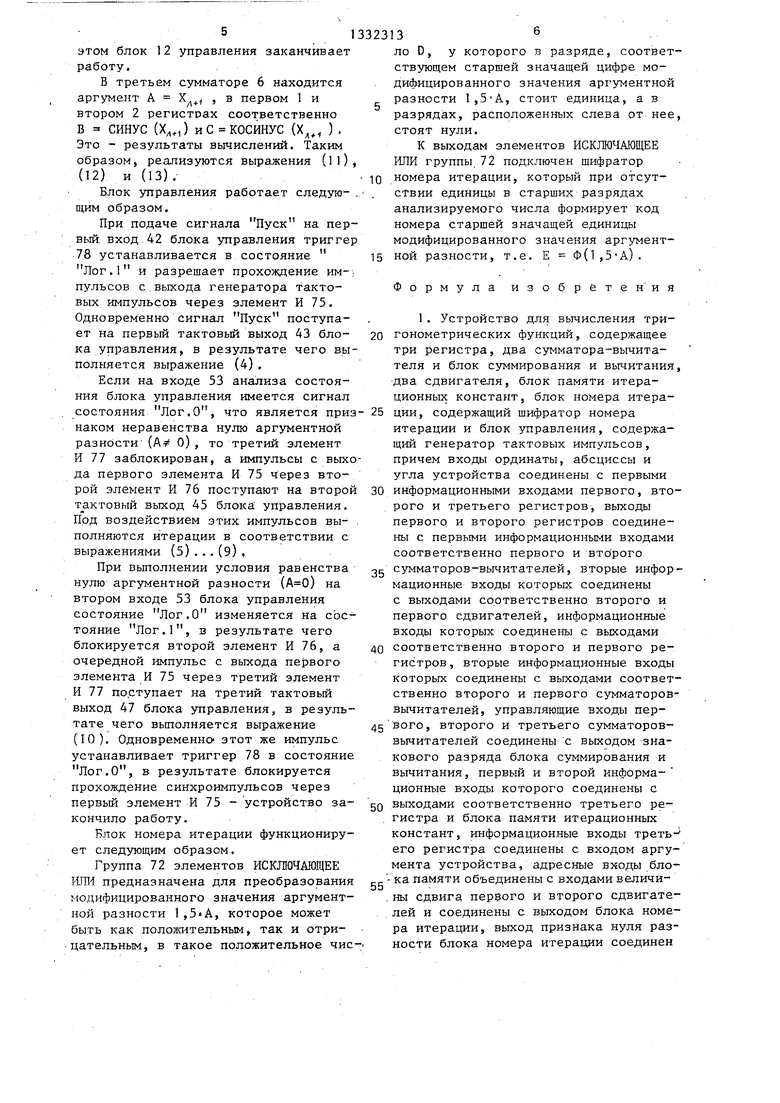

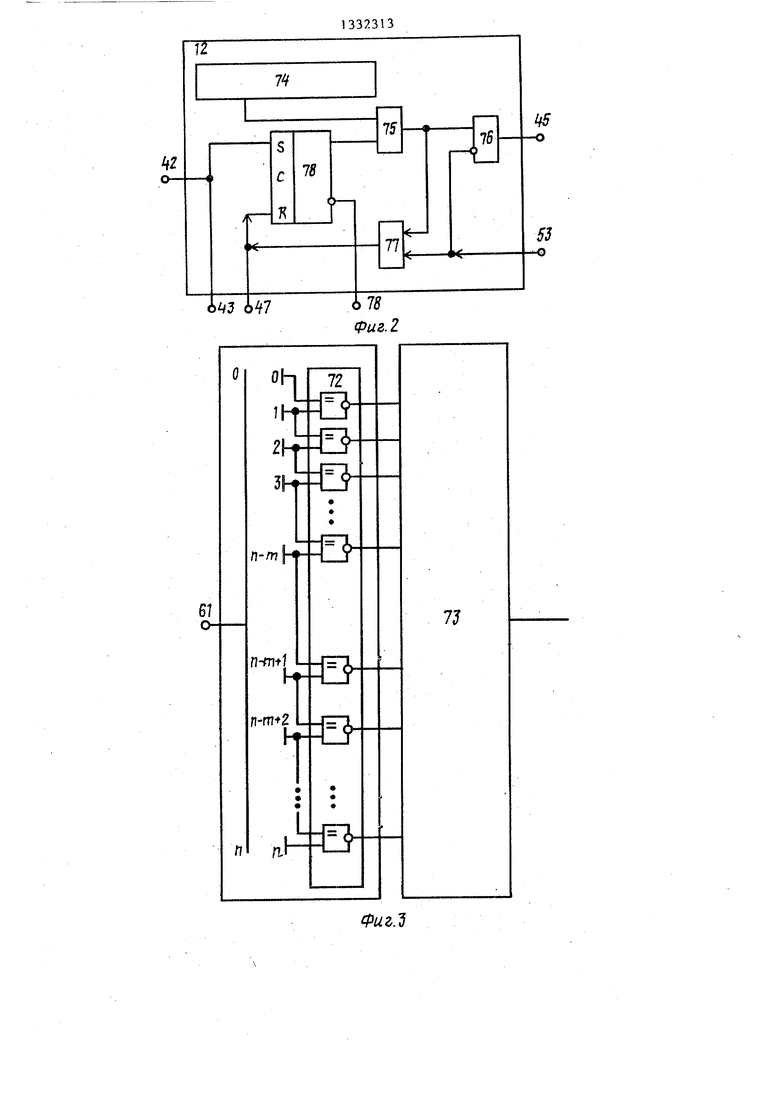

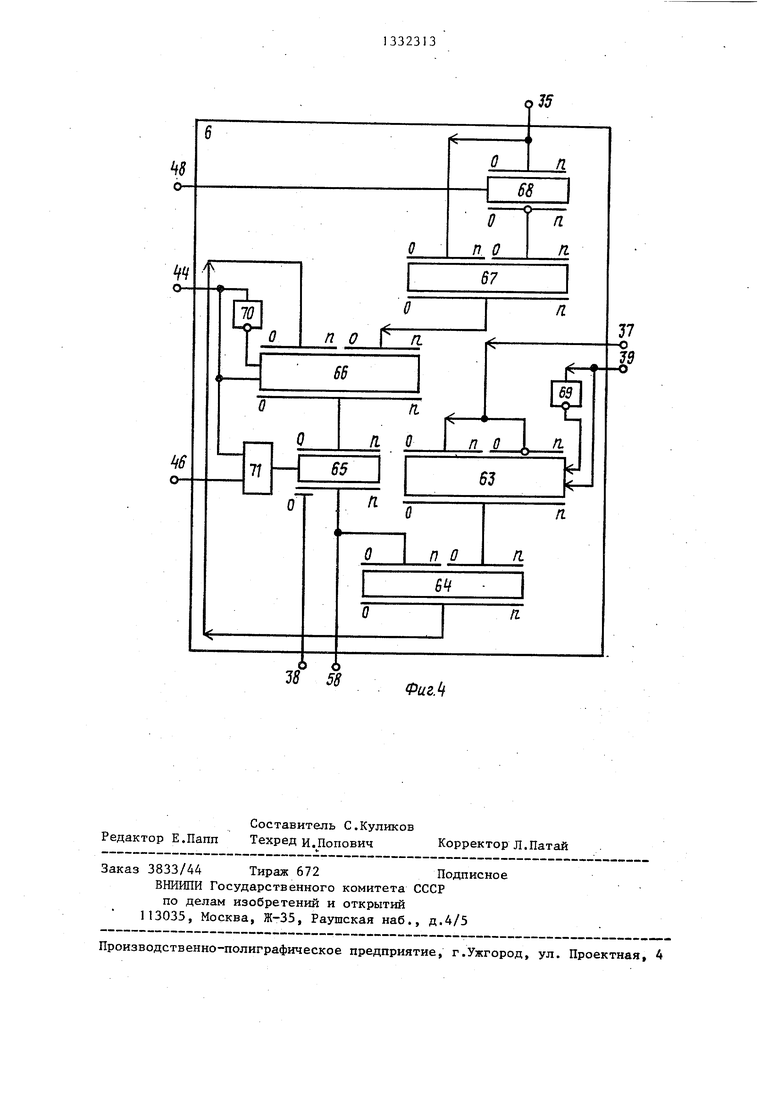

На фиг,1 представлена функциональная схема устройства; на фиг,2 - функциональная схема блока управления; на фиг.З - функциональная схема блока номера итераций; на фиг.4 - пример реализации схемы блока суммирования и вычитания.

Устройство содержит первый 1, вто рой 2 и третий 3 регистры, первый 4 и второй 5 сумматоры-вычитатели, блок 6 суммирования и вычитания, сум матор 7, первый 8 и второй 9 с двига- тели, -блок 10 памяти итерационных констант, блок 11 номера итерации, блок 12 управления, вход 13 ординаты вход 14 абсциссы, вход 15 угла, вход 16 запуска, первые информационные входы 17 - 19 соответственно первого второго и третьего регистров, выход 20 первого регистра, первый инфор- мационньй вход 21 первого сумматора- вычитателя, выход 22 ВТОРОГО регистра, первый информационНьй вход 23 второго сумматора-вычитателя, входы аргументов 24 и 25 соответственно первого и второго сдвигателей, выход 26 первого сдвигателя, второй информационный вход 27 второго сумматора- вычитателя, выход 28 второго сдвигателя, второй информационный вход 29 первого сумматора-вычитателя, выход 30 первого сумматора, второй инфор:- мационньш вход 31 первого регистра, выход 32 второго сумматора-вычитателя второй информационньй вход 33 второго регистра, выход 34 третьего регистра, первый информационный вход 35 блока суммирования и вычитания, выход 36 блока памяти итерационных констант, второй информационный, вход 37 блока суммирования и вычитания, выход 38 знакового разряда блока суммирования и вычитания, управляющий вход 39 блока суммирования и вьиитания,, управляющие входы 40 и 41 соответственно второго и первого сум маторов-вычитателей, вход 42 запуска блока управления, первый тактовый выход 43 блока управления, первый тактовый вход 44 блока суммирования и вычитания, второй тактовый выход

323132

45 блока управления, второй тактовьш вход 46 блока суммирования и вычитания, третий тактовый выход 47 блока управления, третий тактовый вход 48 блока суммирования и вычитания,синх- ронизирующие входы 49 и 50 соответственно первого и второго регистров, стробирующий вход 51 блока -памяти 10 итерационных констант, выход 52 признака нуля разности блока номера итерации, вход 53 анализа состояния блока управления, выход 54 блока номера итерации, входы 55 и 56 вели- 15 чины сдвига соответственно первого

и второго сдвигателей, адресный вход 57 блока памяти итерационных конс- тант, информационный выход 58 блока суммирования и вычитания, вход 59 20 первого слагаемого сумматора, выход 60 сумматора, вход 61 блока номера итерации, вход 62 второго слагаемого сумматора.

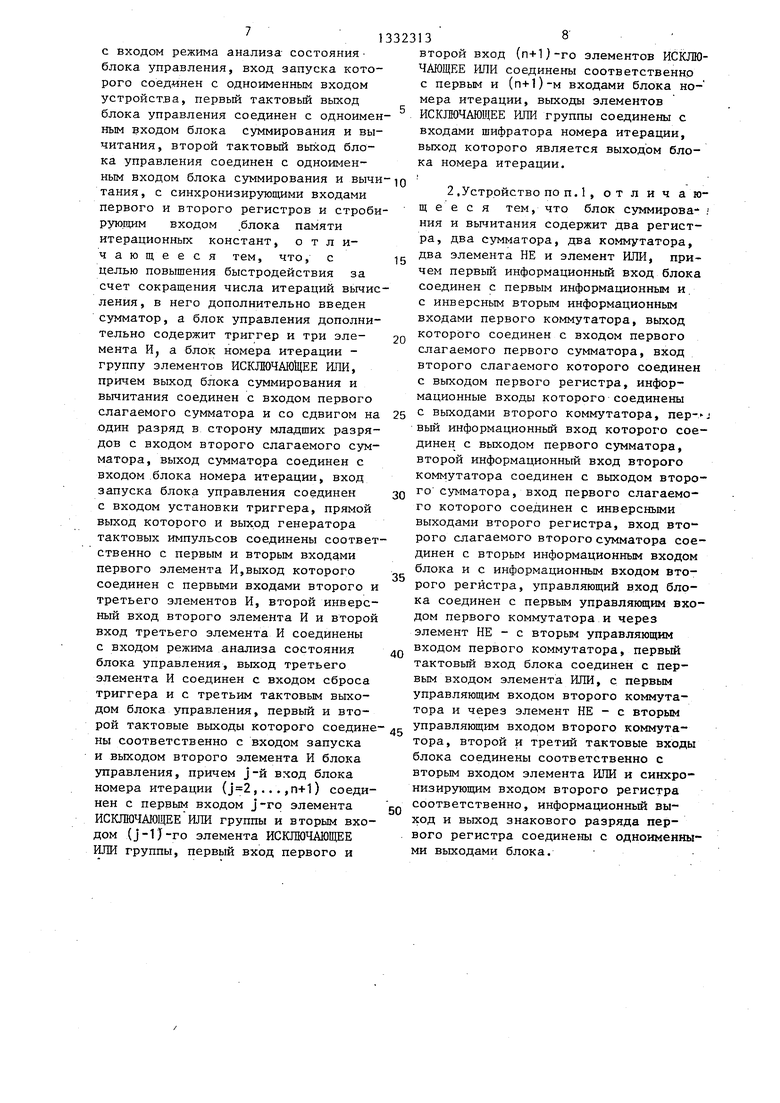

Блок суммирования и вычитания со- 25 держит первый коммутатор 63, первьш

сумматор 64, первый регистр 65, второй коммутатор 66, второй сумматор 67, второй регистр 68, первый 69 и второй 70 элементы НЕ, элемент ° ИЛИ 71..

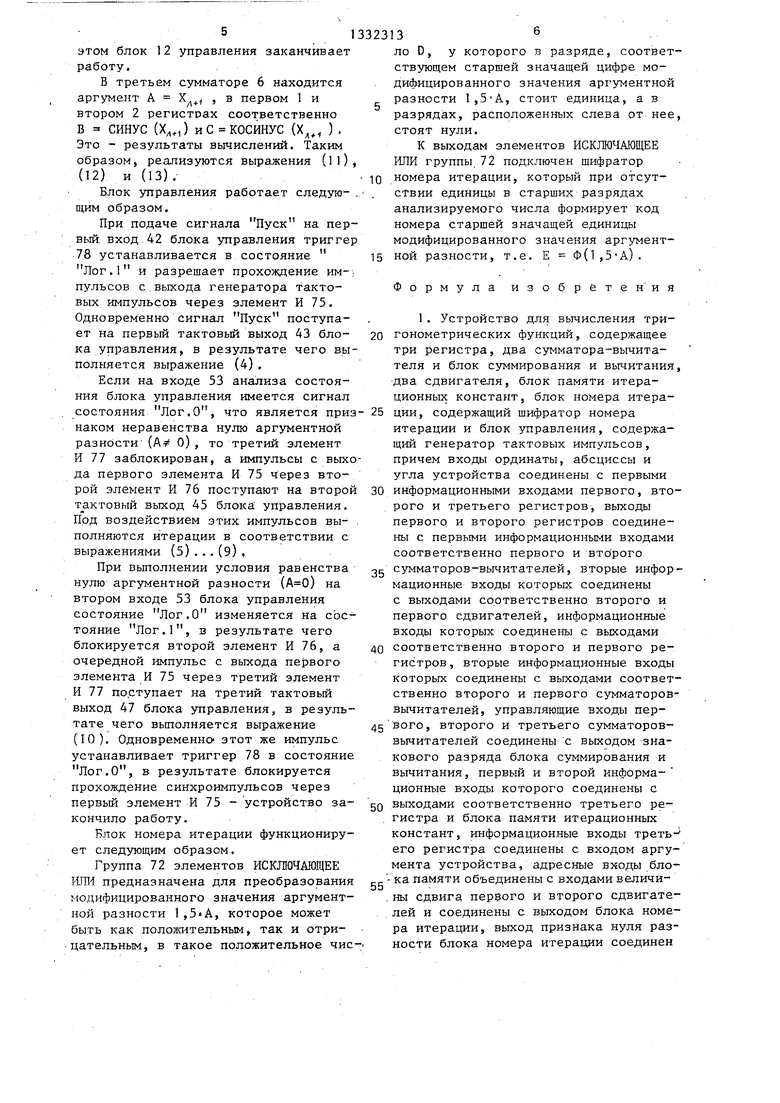

Блок номера итерации содержит группу 72 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, шифратор номера итераций 73.

Блок управления содержит генератор 35 74 тактовых импульсов, первьй 75, второй 76, третий 77 элементы И, триггер 78.

Устройство функционирует следующим образом.

В ходе вычислений приняты следующие обозначения:

sin(X) - СИНУС (X); cos(X) - КОСИНУС (Х); arctg(X) - AT (Х);

45 sign(X) - ЗНАК (X); А - угол (аргумент, аргументная разность); В - ордината вектора (синус); С - абсцисса вектора (косинус); Р е +1 i оператор направления поворота векто gQ pa; Е - номер выполняемой итерации; ф(Х) - преобразование формирования номера Е старшей значащей цифры числа X; АТ(2 ) -.угол, на который поворачивается вектор на Е-й итерации;

ее Хд - л-е значение аргумента во входном потоке; Хд,- (л+1)-е - значение аргумента во входном потоке.

Значения переменных до начала вычислений:

А X, ;

В СИНУС (Хд);

(1)

(2)

С КОСИНУС (XJ.(3)

Алгоритм вычисления СИНУС (Х ) 5 КОСИНУС (X ) .

Начальная установка:

„; ()

(А).(5)

(1,5 А);(б)

. (AT(2 f));(7)

B: B-t-P-C- ; .(8)

.В-2

(9)

если А Q, то идти к 1, иначе - заключительная установка:

(10)

Af1

Конец. Результаты:

. . (11)

В СИНУС (X,,,); (12) С КОСИНУС (Хд, ) . (13)

в исходном положении в блоке 6 суммирования и вычитания находится аргумент , в первом 1 и втором 2 регистрах - соответственно В СИНУС (Хд и С КОСИНУС (Хд). Таким образом, реализованы выражения (1),(2), (3).

В начале вычислений в третий регистр 3 заносится очередное значение аргумента X, , .

Далее по сигналу, поданному на вход 16 запуска устройства, блок 12 управления включается в работу.

По сигналу с первого тактового выхода 43 блока 12 управления, который поступает на первый тактовый вход 44 блока суммирования и вычитания , в нем формируется разность А очередного Х и. предьщущего Х зна- чений аргумента. Таким образом, реализуется начальная установка алгоритма (4).

Затем блок I2 управления вырабатывает последовательность сигналов на своем втором тактовом выходе 45. Эти сигналы поступают на второй тактовый вход 46 блока 6 суммирования. и вьиитания на вход 49 первого регист- ра 1, на вход 50 второго регистра 2, на стробирующий вход 51 блока 10 памяти итерационных констант и синхронизируют их работу.

1332313

5

0

5

0

5

0

0

5

Под воздействием каждого синхросигнала реализуются одна итерация алгоритма (5) - (9). Режимы работы (сложение или вычитание) первого 4, второго 5, третьего 6 сумматоров-вы- читателей задает сигнал с выхода 38 знакового разряда третьего сумматора б - выражение (З).

На каждой итерации сумматор 7 умножает аргументную разность А на коэффициент 1,5. Полученное модифицированное значение 1 ,5 -А аргументной разности анализируется блоком 11 номера итерации, на выходах 54 которого формируется номер Е выполняемой итерации - выражение ( 6 ).

По этому номеру Е из блока 10 памяти итерационных констант считывается соответствующая арктангенс- ная константа AT(2 ), а в первом 8 и втором 9 сдвигателях выполняется сдвиг соответственно ординаты В и абсциссы С вектора на Е разрядов вправо.

На первом 4 и втором 5 суммато- рах-вычитателях и блоке 6 суммирования и вычитания и формируются новые значения соответственно ординаты В, абсциссы С и аргументной разности А, которые фиксируются соответственно на первом 1, втором 2 регистрах и в блоке 6 суммирования и выполнения, Таким образом, реализуются выражения (8), (9) и (7) .

Все итерации выполняются в устройстве аналогично рассмотренному процессу.

Итерационный процесс прекращается, когда аргументная разность А становится равной нулю, что обнаруживается блоком 11 номера итерации, который формирует сигнал признака окончания итерационного процесса на выходе 52. Этот сигнал поступает на вход 53 анализа состояния блока 12 управления и обрывает последовательность сигналов на его втором выходе 45.

Блок 12 управления формирует сигнал на своем третьем тактовом выхр- де 47. Этот сигнал поступает на третий тактовьй вход 48 блока 6 суммирования и вычитания, в результате значение аргумента X ., принимается из третьего регистра 3 в блок 6 суммирования и вычитания. Таким образом реализуется заключительная установка алгоритма - выражение (10). На

этом блок 12 управления заканчивает работу.

В третьем сумматоре 6 находится аргумент А Х , в первом 1 и втором 2 регистрах соответственно В СИНУС (Х,) иС КОСИНУС {Х, ) . Это - результаты вычислений. Таким образом, реализуются выражения (П), (12) и (13).

Блок управления работает следую- . щим образом.

При подаче сигнала Пуск на первый вход 42 блока управления триггер 78 устанавливается в состояние Лог.1 и разрешает прохождение им-; пульсов с.выхода генератора тактовых импульсов через элемент И 75. Одновременно сигнал Пуск поступает на первый тактовый выход 43 блока управления, в результате чего выполняется выражение (4).

Если на входе 53 анализа состояния блока управления имеется сигнал

состояния Лог.О , что является приз- 25 ции, содержащий шифратор номера

наком неравенства нулю аргументной разности (А/ о), то третий элемент И 77 заблокирован, а импульсы с выхода первого элемента И 75 через второй элемент И 76 поступают на второй трактовый выход 45 блока управления. Под воздействием этих импульсов вы- полняются итерации в соответствии с выражениями (5). . . (э),

При выполнении условия равенства нулю аргументной разности () на втором входе 53 блока управления состояние Лог.О изменяется на состояние Лог.1, в результате чего блокируется второй элемент И 76, а очередной импульс с выхода первого элемента И 75 через третий элемент И 77 поступает на третий тактовый выход 47 блока управления, в результате чего выполняется выражение (10). Одновременна этот же импульс устанавливает триггер 78 в состояние Лог.О, в результате блокируется прохождение синхроимпульсов через первый элемент И 75 - устройство закончило работу.

Блок номера итерации функционирует следующим образом.

Группа 72 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ предназначена для преобразования модифицированного значения аргументной разности 1,, которое может быть как положительным, так и отри- цательным, в такое положительное чис

ло D, у которого в разряде, соответствующем старшей значащей цифре модифицированного значения аргументной разности 1,5 А, стоит единица, а в разрядах, расположенных слева от нее, стоят нули.

К выходам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы.72 подключен шифратор номера итерации, который при отсутствии единицы в старших разрядах анализируемого числа формирует код номера старшей значащей единицы модифицированного значения аргументной разности, т.е. Е Ф(1,5 А).

Формула изобретен ия

1. Устройство для вычисления три- гонометрических функций, содержащее три регистра, два сумматора-вычита- теля и блок суммирования и вычитания, два сдвигателя, блок памяти итерационных констант, блок номера итера0

0

итерации и блок управления, содержащий генератор тактовых импульсов, причем входы ординаты, абсциссы и угла устройства соединены с первыми информационными входами первого, второго и третьего регистров, выходы первого и второго регистров соединены с первыми информационными входами соответственно первого и вто рого 5 сумматоров-вычитателей, вторые информационные входы которых соединены с выходами соответственно второго и первого сдвигателей, информационные входы которых соединены с выходами соответственно второго и первого ре- гис:тров, вторые информационные входы которых соединены с выходами соответственно второго и первого сумматоров- вычитателей, управляющие входы пер- вого, второго и третьего сумматоров- вычитателей соединены с выходом знакового разряда блока суммирования и вычитания, первый и второй информа- ционные входы которого соединены с выходами соответственно третьего регистра и блока памяти итерационных констант, информационные входы треть- его регистра соединены с входом аргумента устройства, адресные входы бло- - ка памяти объединены с входами величи- ,ны сдвига первого и второго сдвигателей и соединены с выходом блока номера итерации, выход признака нуля разности блока номера итерации соединен

5

0

5

с входом режима анализа состояния блока управления, вход запуска которого соединен с одноименным входом устройства, первый тактовый выход блока управления соединен с одноименным входом блока суммирования и вычитания, второй тактовьй выход блока управления соединен с одноименным входом блока суммирования и вычитания, с синхронизирующими входами первого и второго регистров и строби руюпдим входом .блока памяти итерационных констант, отличающееся тем, что, с целью повышения быстродействия за счет сокращения числа итераций вычисления, в него дополнительно введен сумматор, а блок управления дополнительно содержит триггер и три элемента И, а блок номера итерации - группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, причем выход блока суммирования и вычитания соединен с входом первого слагаемого сумматора и со сдвигом на один разряд в сторону младших разрядов с входом второго слагаемого сумматора, выход сумматора соединен с входом блока номера итерации, вход запуска блока управления соединен с входом установки триггера, прямой выход которого и выход генератора тактовых импульсов соединены соответственно с первым и вторым входами первого элемента И,выход которого соединен с первыми входами второго и третьего элементов И, второй инверсный вход второго элемента И и второй вход третьего элемента И соединены с входом режима анализа состояния блока управления, выход третьего элемента И соединен с входом сброса триггера и с третьим тактовым выходом блока управления, первый и второй тактовые выходы которого соединены соответственно с входом запуска и выходом второго элемента И блока управления, причем j-й вход блока номера итерации (,...,п+1) соединен с первым входом j-ro элемента ИСКЛЮЧАЮЩЕЕ или группы и вторым входом (j-l)-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы, первый вход первого и

0

второй вход (п+1)-го элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с первым и (п+1)-м входами блока но- мера итерации, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ Труппы соединены с входами шифратора номера итерации, выход которого является выходом блока номера итерации.

2 .Устройство по п. 1 , отличающееся тем, что блок суммирова- . ния и вычитания содержит два регистра, два сумматора, два коммутатора,

f. два элемента НЕ и элемент ИЛИ, причем первый информационный вход блока соединен с первым информационным и. с инверсным вторым информационным входами первого коммутатора, выход которого соединен с входом первого слагаемого первого сумматора, вход второго слагаемого которого соединен с выходом первого регистра, информационные входы которого соединены

5 с выходами второго коммутатора, пер--: вьш информационньй вход которого соединен с выходом первого сумматора, второй информационный вход второго коммутатора соединен с выходом второ0 го сумматора, вход первого слагаемого которого соединен с инверсными выходами второго регистра, вход второго слагаемого второго сумматора соединен с вторым информационным входом блока и с информационным входом второго регистра, управляющий вход блока соединен с первым управляющим входом первого коммутатора и через элемент НЕ - с вторым управляющим входом первого коммутатора, первый тактовый вход блока соединен с первым входом элемента ИЛИ, с первым управляющим входом второго коммутатора и через элемент НЕ - с вторым управляющим входом второго коммутатора, второй и третий тактовые входы блока соединены соответственно с вторым входом элемента ИЛИ и синхронизирующим входом второго регистра соответственно, информационный выход и выход знакового разряда первого регистра соединены с одноименными выходами блока.

5

0

5

0

647

liS

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

| Устройство для вычисления функции | 1986 |

|

SU1348829A1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

| Устройство для вычисления функции @ | 1987 |

|

SU1456954A1 |

| Устройство для вычисления обратного гиперболического тангенса | 1987 |

|

SU1456952A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1370653A1 |

| Арифметическое устройство | 1978 |

|

SU780004A1 |

| Устройство для вычисления функций | 1986 |

|

SU1374219A1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Устройство для вычисления гиперболических синуса и косинуса | 1987 |

|

SU1462300A1 |

72

I| 2f

31

n-rn

67

fj-mt

L -1

T

r-€

Lj

/7

a

7

Фиг. З

8 58

Составитель С.Куликов Редактор Е.Папп Техред и.Попович Корректор Л.Патай

V

Заказ 3833/44 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, А

ФигЛ

| Устройство для вычисления тригонометрических функций | 1977 |

|

SU696476A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислитель тригонометрических функций | 1978 |

|

SU746538A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-08-23—Публикация

1986-01-22—Подача