ел

а

4

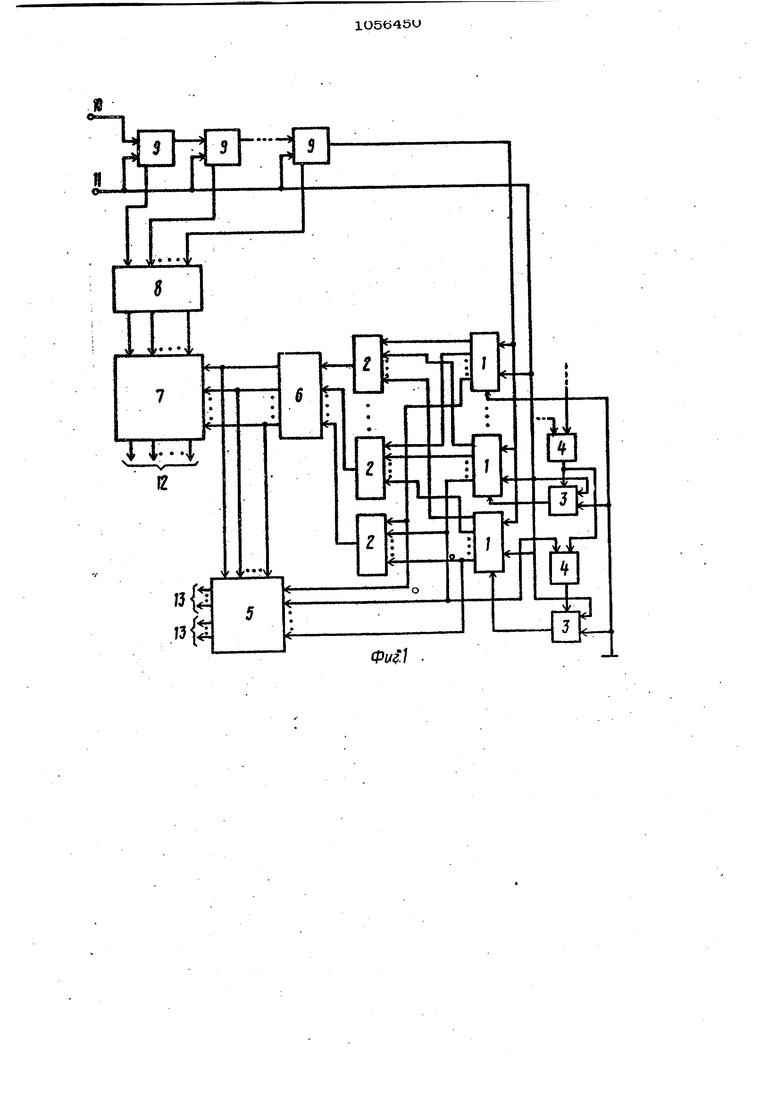

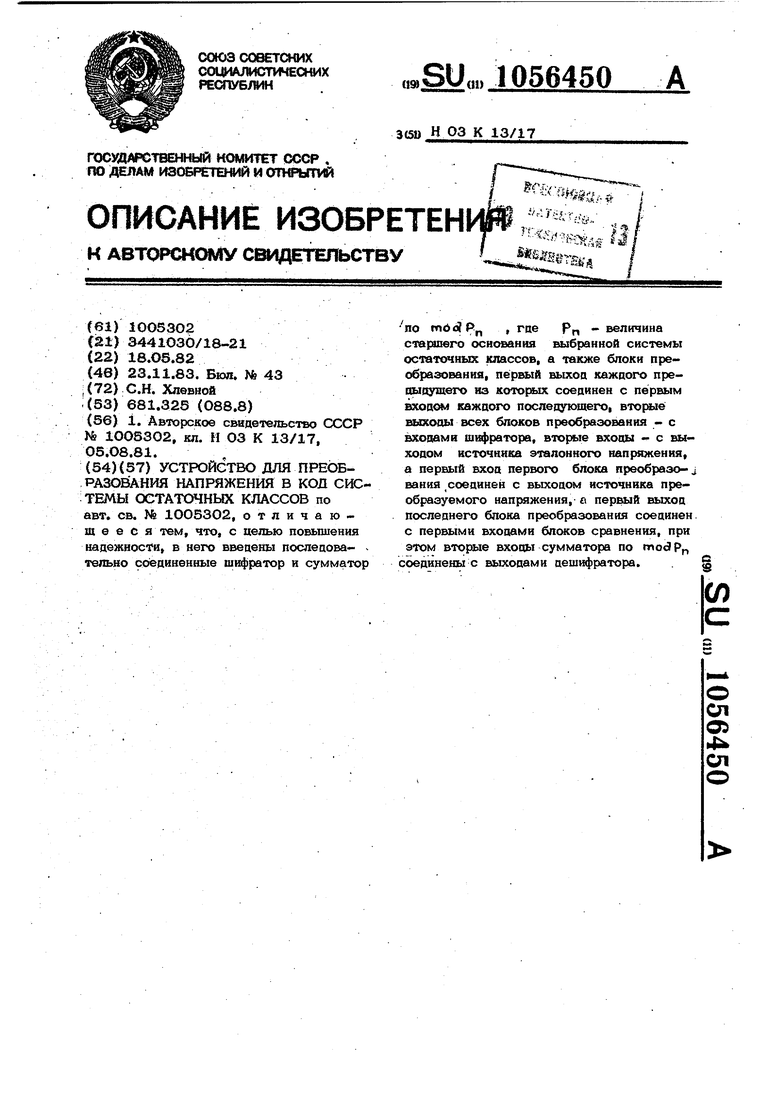

сл 10 Изобретение относится к вычислителЕьной технике и может быть использовано для сопряжения различных датчиков с вы числительными устройствами, функционирующими в системе остаточных классов (СОК), а также цля преобразования мгно венного значения переменного напряжения в цифровой коц СОК . По основному авт. св. М 1О05302 известно устройство аля преобразования напряжения в код системы остаточных классов, содержащее группы компаратор ров, первые входы которых соединены с выходом источника преобразуемого напря жения, вторые входы - с выходами соответствующих делителей эталонного напряжения, выходы младших компараторов каждой группы с первыми входами логического элемента, вторые входы которого соединены с выходами дешифратора, первые входы делителей соединены с источником эталонного напряжения, а второй вход делителя эталонного напряже ния старшей группы соединен с общей ши ной, переключатели,, первая и вторая группы элементов ИЛИ, входы первой vts которых соединены с соответствующими выходами компараторов, а выходь к входам дешифратора, при этом первые входы переключателей соединены с выходами источника эталонного напряжения, вторые входы с общей шиной, выходы соответственно с вторыми входами целителей эталонного напряжения, а управляющие входы переключателей соединены соответственно с выходами элементов / ИЛИ второй группы, первые входы KOTOJрых соединены с выходами соответствующих младших компараторов каждой, кроме младшей группы, а вторые входы - с выходами предыдущих элементов ИЛИ второй грулпы Cl3 . Недос-Латком известного устройства является его сложность, так как для СОК с ЧИСЛОЕ1ЫМ диапазоном Р необходимо, чтобы блоки сравнения в совокупности со держали Р- -1 компараторов, что значительно усло1 няет схему, при увеличении числового диапазона выбранный СОК, и приводит к снижению надежности непозиционного аналоп ч1ифрового преобразо- вателя. Цель изобретения - повьпиение надежностиПоставленная цель достигается тем, что в устройство для преобразования напряжения в код системы остаточных клас сов введены последовательно соединенны шифратор и сумматор по modPp, O где РМ величина старшего основания выбранной системы остаточных классов, а также блоки преобразования, nepi вый выход каждого предыдущего из которых соединен с первым входом каждого последующего, вторые выходы всех блоков поеобразования - с входами шифраторе вторые входы - с выходом источника эталонного напряжения, а первый вход первого блока преобразования соединен с выходом источника преобразуемого напряжения, а первый выход последнего блока преобразования соединен с первыми входа ми блоков сравнения, при этом вторые входы сумматора по mod Р соединены с выходами дешифратора. На фиг 1- приведена структурная схема устрсй1ства, на фиг. 2 - пример реализации блоков преобразования и блоков сравнения . Устройство содержит блоки 1 сравнения, первую группу элементов ИЛИ 2, , переключатели 3, вторую группу элемен- , тов ИЛИ 4, логический элемент 5, дешифратор 6, сумматор 7 по тосЗР„ шифратор 8, блоки 9 преобразования, источник 10 преобра ецого напряжения, источник 11 эталонного напряжения, шины 12 выдачи остатка, соответствующего старшему основанию, шины 13 выдачи оставшихся остатков, а также компараторы 14, резистивные дилители 15 эталонного напряжения, компараторы 16, ктоочи 17, вычитакщие устройства 18. Выходы блоков 1 с{)авнен№1 соединены с входами группы элементов ИЛИ 2, выходы которых соединены с входами дешифратора 6, выхощ которого соединены с вторыми входами сумматора 7 первые входы которого соединены с выходами дешифратора 8. Устройство работает следующим образом. Процесс ана ого-цифрового преобразования напряжения сводится к аопучеиию некоего цифрового эквивалента А, для ктброго выполняется следующее соотношеи, л±е,где и - величина шага квантования; . 6 - погрешность преобразования. В системе остаточных классов цифровой эквивалент А , преобразуемого нвпряжения Ux представляется разрядными цифрами ot , d.2 ...... м котор ые подучаются из соотношения гце Р - величина оснований вы ной СОК. Для однозначности представле бого числа в СОК необходимо соб взаимной/- простоты выбранных о кий. Представим число А в систем ления со смешанными основаниям При этом считаем, что 6 ПСС и темы оснований одинаковы, тогда ло А дет иметь вид:.. .. 1 21 3 1 2 о|,- - разрядные цифры в ПС Из (3) найдём разрядные циф в СОК )modrp;(o«JmoJP , ot (А) mod Р ( Rjjmod Р о1„.(А)тооГР(а, ,«п..пл it-t / i (AlmodP.-(o,, , 5-2 п-1 «п.,П П Р. mod Р„ iM V Из (4) следует, что член ПС Heo6xoBifM только для получения соотлетстаующего старшему осно .Переписывая (3) несколько иным бом, -гы А-В + Р. . где получим (4) с учетом (5) S 2 1 - °n-lV. d г (А1 moe Р S (в) mod Р et, г (А) mod Р в J mod Р . . L . . . г . . . . (Л)то(Р„.(в)шой. п ( р. (A)««odP, isi V Таким образом из (6) следуе если преобразуемое напряжение 74о« П Р. шить на величину ченное значение напряжения и, и,-ло. удет соответствовать всем младшим разрядньпи цифрам СОК за исключением соответствующей наибольшему основанию. Для получения остатка по старшему снованию, цифровой звовивалент В склап ывается помоаупюс величиной Р , которая таю({е предварительно преобразуется по старшему основанию. Преобразуемое напряжение Uy подается на вход последовательно соединенных, блоков 9 преобразования, каждый из которых уменьшает величину О j(j на величип-1 . . п-1 ну4П р. , если и... /г1П Р, . .Это - . Ы достигается за счет того, что компарато{ад 16 проверяют выполнение усло(. вия (J /Д П Р. I. и если условие выполняется, то компаратор 16 открывает ключ 17, через который с источника 11 этaлoннo o напр51жения поступает эталонное напряжение, имеющее величину П Р. , --1 1 которое далее и вычитается из Ux Е1Ычитаняцим устройс-гаом 18. Если же окажется, что на входе какого-либо блока 9 п-1.. Xi Пл ® выходе этого блока напряжение передается без изменения. Число последовательно соединенных блоков преобразования по мудулю для любой СОК. составит Р п . И на выходе последнего блока 9 преобразования образуется напряжение (J , определяемое напряжением (7). Величина ct в параллельном унитарном коде снимается с шдходов компараторов 16 и подаётся на вход шифратора 8, преобразует его в единичный код, определяемый выражением к / . moolP, И единичный код величины ot поступает на первую группу входов сумматора 7 по mod РП . Напряжение Uf с выхода последнего блока 9 поступает на входы всех компараторов 14, составляющих блоки 1 сравнения, на. вторые входы компараторов 14 подаются напряжения с выходов резис1увнь1Х делителей 15 эталонного напряжения. При этом в состав каждого , блока сравнения входит число компараторов 14, равное величине наибольшего основания Рр за исключением старшего блока 1 сравнения Общее число коМпараторов 14 в блоках 1 сравнения состак как тавляет величину следует из (3), рличина ,В не превышаетПараметры реэистивных делителей 15 выбираются таким образом, чтобы при подключении всех выходов переключателей 3 на общую щину, напряжение, подаваемое на входы компараторов 14 перво го блока 1 сравнения увеличивалось от компаратора к компаратору на Л и на старшем компараторе 14 первого блока сравнения составило (, во второ блоке 1 сравнения эталонные напряжения смещены на величину ЛР и так долее. Если величина Р,Л , то срабатывают компараторы 14 только первого бл ка сравнения. При этом параллельный унитарный код величины В посггупает через элеьяента ИЛИ 2 на входы дешифратора, который преобразует его рэбым известным образом в единичный код. Число входных и выходных шин дешифраторов одинаково и равно величине Р Если величина U окажется Р, то срабатывают и Ux РП компараторы 14 второго блока 1 сравне ния. При этом, сигнал с младшего комнаг ратора 14 второго блока 1 сравнения,, воздействуя через элемент ИЛИ на управ ляющий.вход переключателя 3, переключит его в такое состояние, что на резис тивный делитель 15, соответствдтощий первому блоку 1 сравнения, поступит наП-Т:пряженяе i П Р которое всегда больше УХ вследствие чего все ком параторы 14 первого блока сравнения выключатся,; и на выходах элементов ИЛИ 3 появится унитарный код числа 8 по модулю. КЦ. Если величина U увеличится еще больше, то поочередно будут выклв чаться все более младшие блоки 1 сравнения, и на выходе элементов ИЛИ 2 всегда будет унитарный код операции , (BfmodP Единичные коды, поступающие на вхо9Ы сумматоры 7, складываются по наибольшему модулю, к на выходе его появ ляются остаток по наибольшему основанию, полученный на основе выражения (6). Сумматор 7 по1яо Р„м6жет быть реализован извес-шым способом, например матри шым. Оста-иси по всем оставшимся основаниям получаются логическим элементом 5 по следующему правиду.. . Число ё можно представить так: itJ , Величина образуется на выходе дешифратора 6. Остатки по оставшимся основаниям подучаются из (9) на основаl- YНИИ (6), Информация с дается на логический элемент 5 с. младших выходов блоков 1 сравнения. Логический элемент 5 может быть реализован любым комбинационньш способом, например, на матричных сумматорах. Полученные значения остатков по ши- нам 13 вьэдаются устройством. Таким образом, предлагаемое усярс ство является асинхронным устройством, в котором продесс преобразования заканчивается по прекращению переходных процессов во свех блоках. 1Гехнико-экономаческай эффект предла гаемсячэ устройства за1шючается в. его более высокой нааеяшос«1 Надежность устройства определяется в основном надежностью аналоговых уст ройств, в шстности устройств сравнения (компараторов), из fоторых состоят блоки равнения. В изеесадом объекте число ; компараторов оавно числу уровней квантования, т.е. П р. В предлагаемом устройству tjHcno компараторов рав.-, п-1 о п +Р . 1-1 Цифроиые части известного объекта и предлагаемого устройства отяичаюгя только ум1 атором 7, который выполняется на цифроетлх. элементах И и которые более надежны по сравнению о наежностью аналогошдх устройств.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования напряжения в код системы остаточных классов | 1981 |

|

SU1005302A1 |

| Устройство для преобразования напряжения в код системы остаточных классов | 1981 |

|

SU1029410A1 |

| Аналого-цифровой логарифматор-антилогарифматор | 1986 |

|

SU1697089A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1990 |

|

SU1765891A1 |

| Преобразователь напряжения в код системы остаточных классов | 1983 |

|

SU1181139A1 |

| Аналого-цифровой преобразователь напряжения в код системы остаточных классов | 1990 |

|

SU1732470A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1983 |

|

SU1211881A1 |

| Непозиционный цифроаналоговый преобразователь | 1983 |

|

SU1173558A1 |

| Устройство для преобразования кода системы остаточных классов в десятичный код | 1984 |

|

SU1167600A1 |

| Устройство для вычисления позиционных характеристик модулярного кода | 1984 |

|

SU1244797A1 |

УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ НАПРЯЖЕНИЯ в код СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ по авт. св. № 1ОО53О2, отличающееся тем, что, с целью по пиения надежности, в него введены после аова- тельно соединенные шифратор и сумматор по гпЪо)Р , гпе РП - величина старшего основания выбранной системы осгаточных классов, a также блоки преобразования, первый выход каждого прещйкута/его нз соединен с первым входом каждого последующего, вторые выходы всех блоков преобразования - с входами шифратора, вторые входы - с выходом источника эталонного напряжения, a первый вход первого блока преобразо-j вания соединен с выходом источника преобразуемого напряжения, a первый выход последнего блока преобразования соединен, с первыми входами блоков сравнения, при этом вторые входы сумматора по modpp соединены с выходами дешифратора. (Л с

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Насос | 1917 |

|

SU13A1 |

Авторы

Даты

1983-11-23—Публикация

1982-05-18—Подача