Изобретение относится к вычислительной технике и может быть использовано для сопряжения вычислительных устройств, функционирующих в системе остаточных классов (СОК) с различными оконечными устройствами, требующими аналогового вывода, а также в технике связи в случае использования кодов СОК в цифровой телефонии.

Целью изобретения является повышение быстродействия.

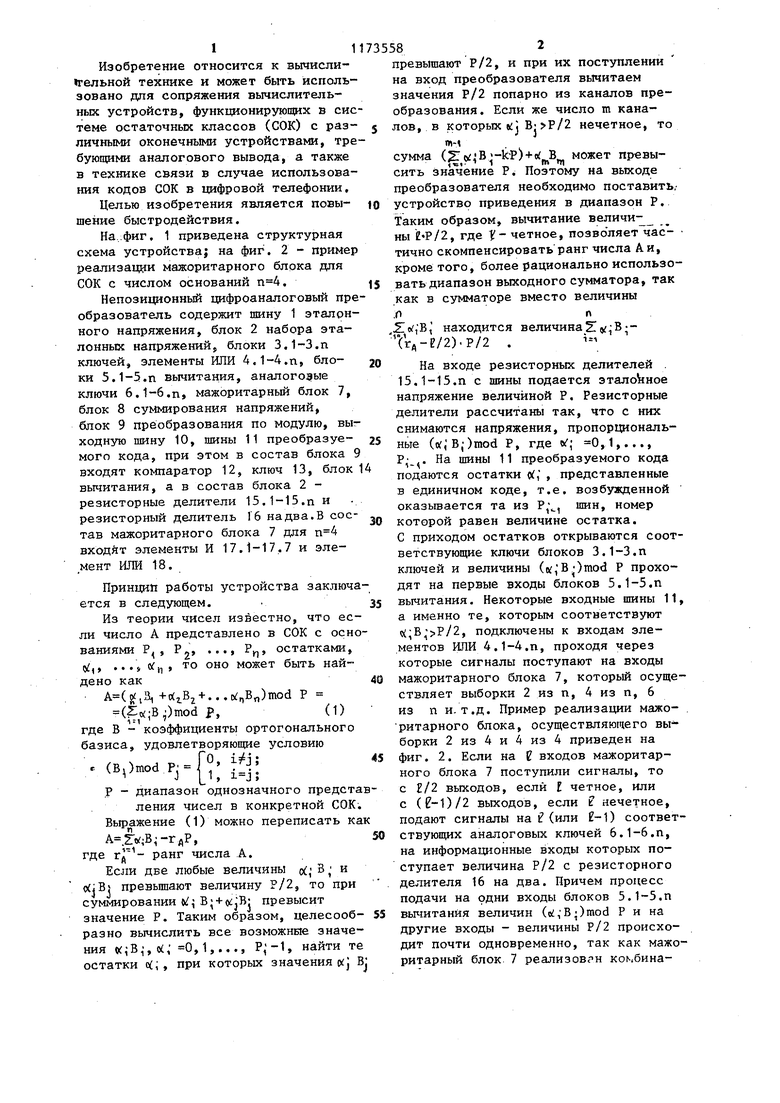

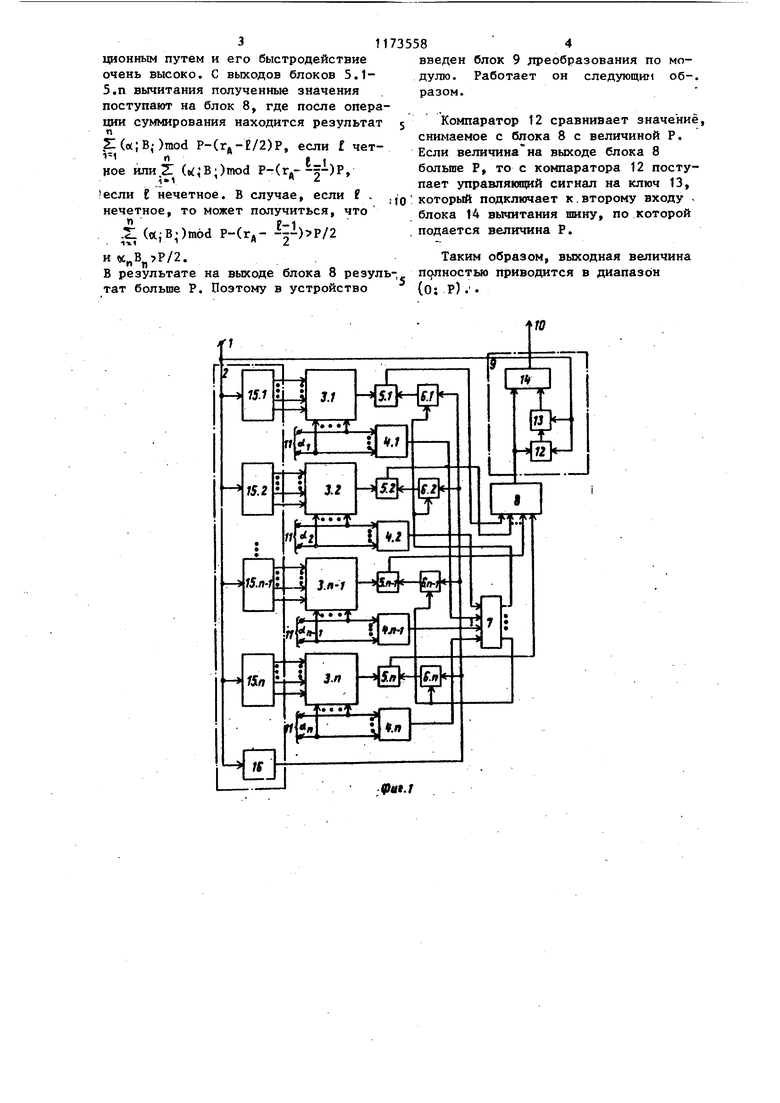

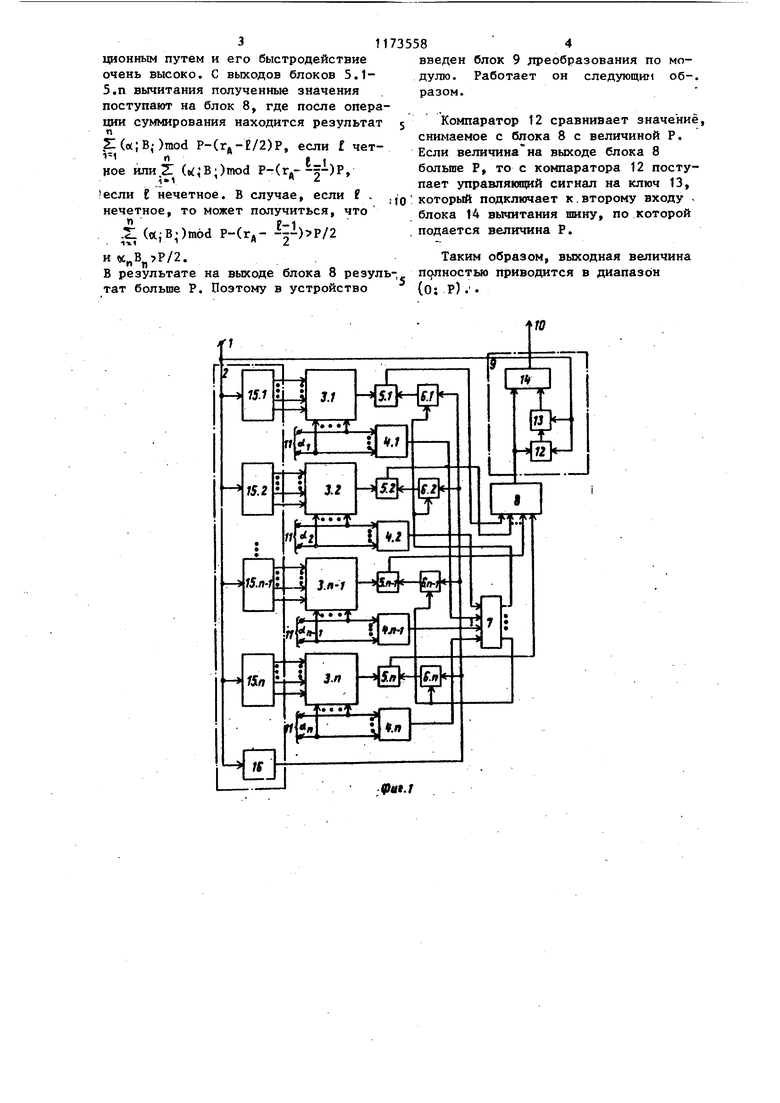

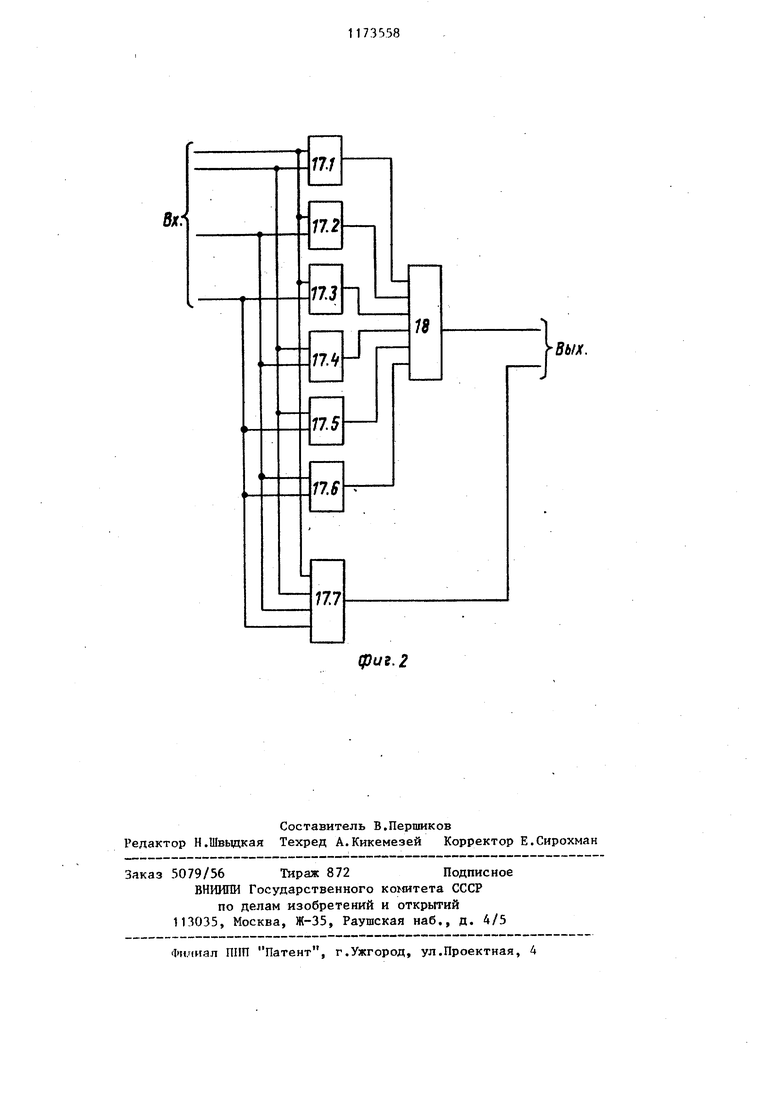

На,:фиг. 1 приведена структурная схема устройства; на фиг. 2 - пример реализации мажоритарного блока для СОК с числом оснований .

Непозихщонный цифроаналоговый преобразователь содержит шину 1 эталонного напряжения, блок 2 набора эталонных напряжений, блоки 3.1-З.п ключей, элементы ИЛИ 4.1-4.П, блоки 5.1-5.П вычитания, аналоговые ключи 6.1-6.П, мажоритарный блок 7, блок 8 суммирования напряжений, блок 9 преобразования по модулю, выг ходную шину 10, шины 11 преобразуемого кода, при этом в состав блока 9 входят компаратор 12, ключ 13, блок 1 вычитания, а в состав блока 2 резисторные делители 15.1-15.п и резисторный делитель 16 на два. В соетав мажоритарного блока 7 для входят элементы И 17.1-17.7 и ИЛИ 18,

Принцип работы устройства заключается в следующем.

Из теории чисел известно, что если число А представлено в СОК с основаниями Р, Р, ..., Р, остатками, lji, .. ., of f, , то оно может быть найдено как

A(5fi3i+o(iB2 + ...K:nBn)mod Р

(о;;В )mod р,(1)

где В - коэффициенты ортогонального базиса, удовлетворяющие условию

- тО:й;

Р - диапазон однозначного представления чисел в конкретной СОК.

Вьфажение (1) можно переписать как

А Г« ;В--ГдР,

где ранг числа А.

Если две любые величины о( В и о(;В| превьш1ают величину Р/2, то при суммировании B; + (x;jB превысит значение Р. Таким образом, целесообразно вычислить все возможные значения «iB, о(, 0,1,..., Р;-1, найти те остатки с(; , при которых значения ccj В:

ревышают Р/2, и при их поступлении а вход преобразователя вычитаем начения Р/2 попарно из каналов преобразования. Если же число m канаов, в которых : нечетное, то

m-t

сумма (,)) + может П1 евысить значение Р. Поэтому на выходе преобразователя необходимо поставить/ стройство приведения в диапазон Р.

Таким образом, вычитание величи-;

ны «Р/2, где у- четное, позволяет час- тично скомпенсировать ранг числа Аи, кроме того, более рационально использовать диапазон выходного сумматора, так как в сумматоре вместо величины пп

, находится величинаZy Вгд-г/2).р/2 . На входе резисторных делителей . 15.1-15.п с шины подается эталонное напряжение величиной Р. Резисторные делители рассчитаны так, что с них снимаются напряжения, пропорциональные (iv,B;)mod Р, где 0,1,..., Р. На шины 11 преобразуемого кода подаются остатки , представленные в единичном коде, т.е. возбужденной оказьгеается та из Р, шин, номер которой равен величине остатка. С приходом остатков открываются соответствующие ключи блоков 3.1-З.п ключей и величины (i,B)mod Р проходят на первые входы блоков 5.1-5.П вычитания. Некоторые входные шины 11, а именно те, которым соответствуют (1(;Б,, подключены к входам элементов ИЛИ 4.1-4.П, проходя через которые сигналы поступают на входы мажоритарного блока 7, который осуществляет выборки 2 из п, 4 из п, 6 из п и. т.д. Пример реализации мажо- . ритарного блока, осуществляющего выборки 2 из 4 и 4 из 4 приведен на фиг. 2. Если на входов мажоритарного блока 7 поступили сигналы, то с 1/2 выходов, если Е четное, или с (0-1)/2 выходов, если нечетное, подают сигналы на f (или -1) соответствующих аналоговых ключей 6.1-б.п, на информационные входы которых поступает величина Р/2 с резисторного елителя 16 на два. Причем процесс подачи на одни входы блоков 5.1-5.П вычитания величин (et,Bj)mod Р и на другие входы - величины Р/2 происходит почти одновременно, так как мажоритарный блок 7 реализован кокбинационным путем и его быстродействие очень высоко. С выходов блоков 5.15.П вычитания полученные значения поступают на блок 8, где после опера ции суммирования находится результат .2:(o(;B-)mod Р-(гд-Е/2)Р, если f чет t Ное или.21 (())mod P-()P, если t нечетное. В случае, если t , нечетное, то может получиться, что -Г (otiBOmod Р-(гд- -)Р/2 Ibl1i В результате на выходе блока 8 резул тат больше Р. Поэтому в устройство

fj.rt-i

З.я-f

введен блок 9 лреобразования по модулю. Работает он следующип об-, разом. Компаратор 12 сравнивает значение, снимаемое с блока 8 с величиной Р. Если величинана выходе блока 8 больше Р, то с компаратора 12 поступает управлякяций сигнал на ключ 13, который подключает к.второму входу . блока 14 вычитания шину, по которой подается величина Р. Таким образом, выходная величина полностыо приводится в диапазон (О; Р).«

Вь/х.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь напряжения в код системы остаточных классов | 1983 |

|

SU1181139A1 |

| Устройство для преобразования напряжения в код системы остаточных классов | 1982 |

|

SU1056450A2 |

| Аналого-цифровой преобразователь напряжения в код системы остаточных классов | 1990 |

|

SU1732470A1 |

| Преобразователь непозиционного кода в двоичный код | 1984 |

|

SU1179547A1 |

| Устройство для преобразования напряжения в код системы остаточных классов | 1981 |

|

SU1029410A1 |

| Преобразователь непозиционного кода в двоичный код | 1982 |

|

SU1083179A1 |

| Цифроаналоговый преобразователь | 1982 |

|

SU1070689A1 |

| Преобразователь кода системы остаточных классов в напряжение | 1983 |

|

SU1175034A1 |

| Преобразователь кода числа из системы остаточных классов в напряжение | 1982 |

|

SU1069155A1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1990 |

|

SU1765891A1 |

НЕПОЗИЦИОННЫЙ ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий блок набора эталонных напряжений, блок суммирования напряжений, отлит чающийся тем, что, с целью повышения быстродействия, в него введены г блоков ключей, где П- число оснований непозиционной системы счисления, п элементов ИЛИ, п аналоговых ключей, п блоков вычитания, мажоритарный блок, блок преобразования по модулю, при этом соответствующие п группвыходов блока набора эталонных напряжений подключены к соответствующим аналоговым входам соответствующих блоков ключей, выходы которых подключены к первым входам соответствующих блоков вычитания, выходы которых подключены к соответствующим входам блока суммирования напряжения, выход которого подключен к первому входу блока преобразования по модулю, выход которого подключен к выходной шине цифроаналогового преобразовате-. ля, шины преобразуемого кода подключены к управляющим входам соответствующих блоков ключей, соответствующие шины преобразуемого кода подключены ко входам соответствующих элес S ментов ИЛИ, выходы которых подключе ны к соответствующим входам мажоритарного блока, выходы которого подключены к управлянмцим входам соответствующих пар аналоговых ключей, выходы которых подключены ко вторым входам соответствующих блоков вычитания, а аналоговые входы объединены и подключены к (п+1)-му выходу блока набора эталонных напряжений, вход которого объединен со вторым входом блока преобразования по модулю и подключен к шине эталонного напряжения.

| Абрамсон И.Т | |||

| и др | |||

| Принципы построения преобразователей информации в системе остаточных классов | |||

| Автометрия, 1969, № 2, с | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| ЦИФРО-АНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ;: •:Г.'>&пч->&зн^Я• • •*>&•<» ^* •••••«•••f-*F<,|A ;!!•> v>&<<iib I .nriVi ;1-.'Кй]1! | 0 |

|

SU282767A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-08-15—Публикация

1983-04-07—Подача