Изобретение относится к измерительной и вычислительной технике и может использоваться в информационно- измерительных устройствах, а также в системах автоматического управления и ЭВМ, работающих на технических целочисленных логарифмах

Цель изобретения - расширение диапазона преобразования

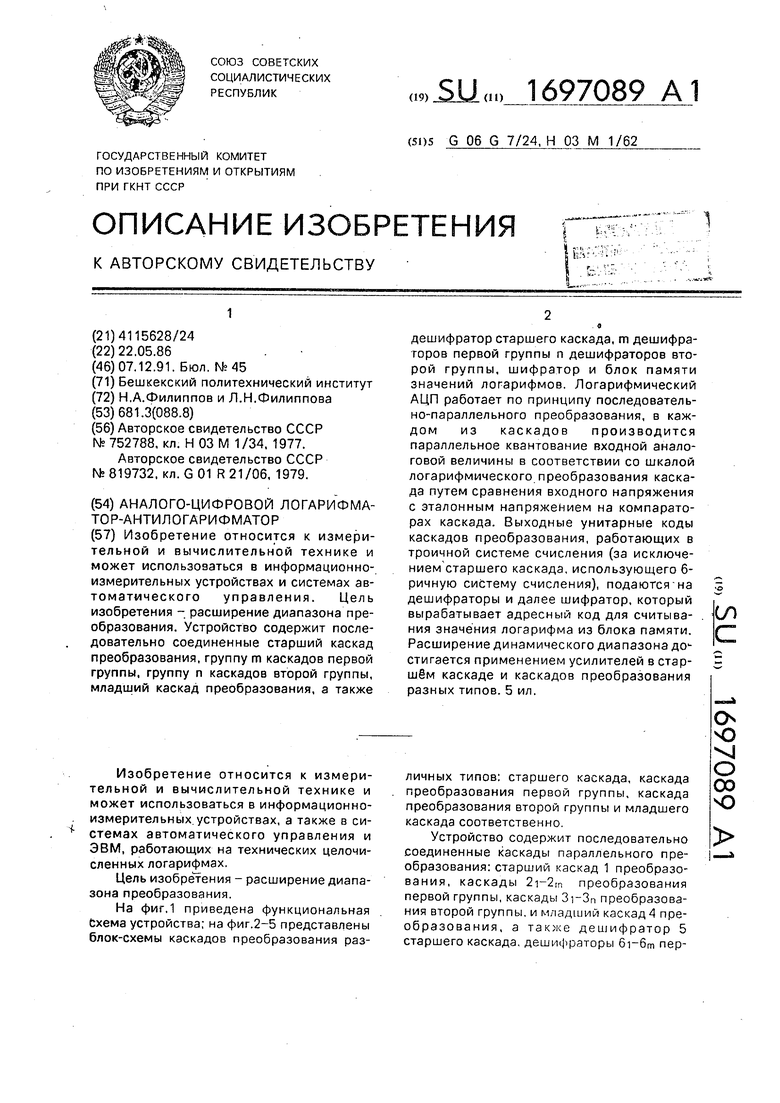

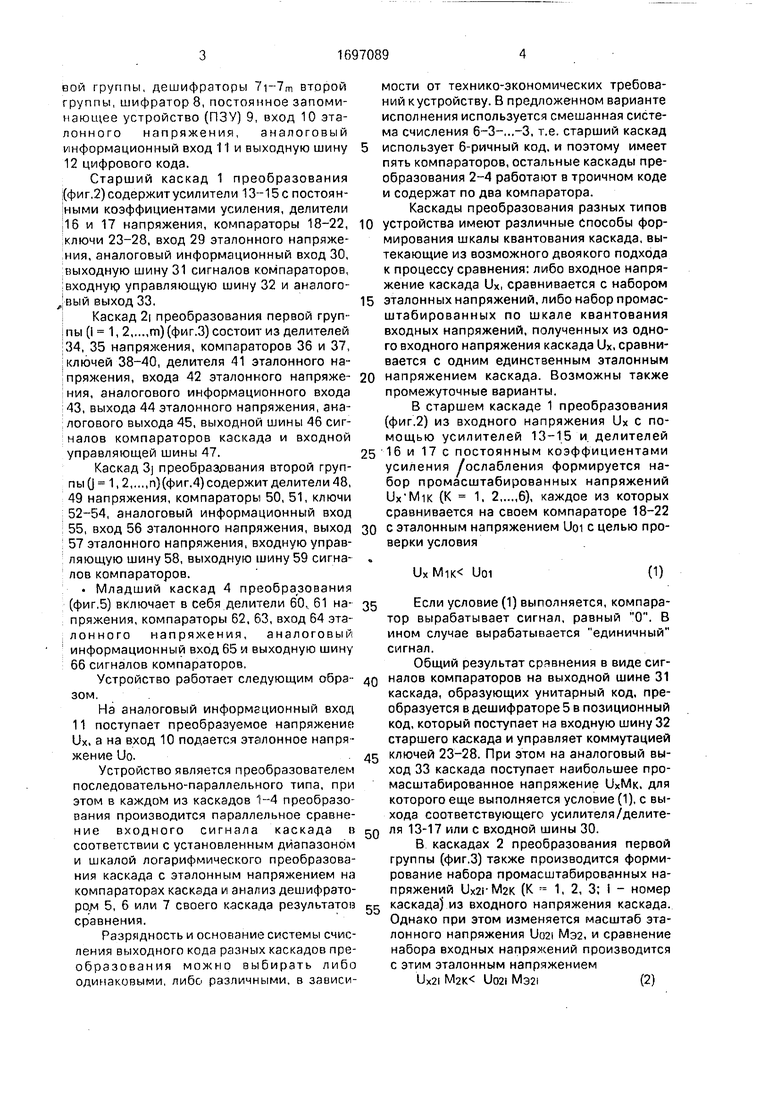

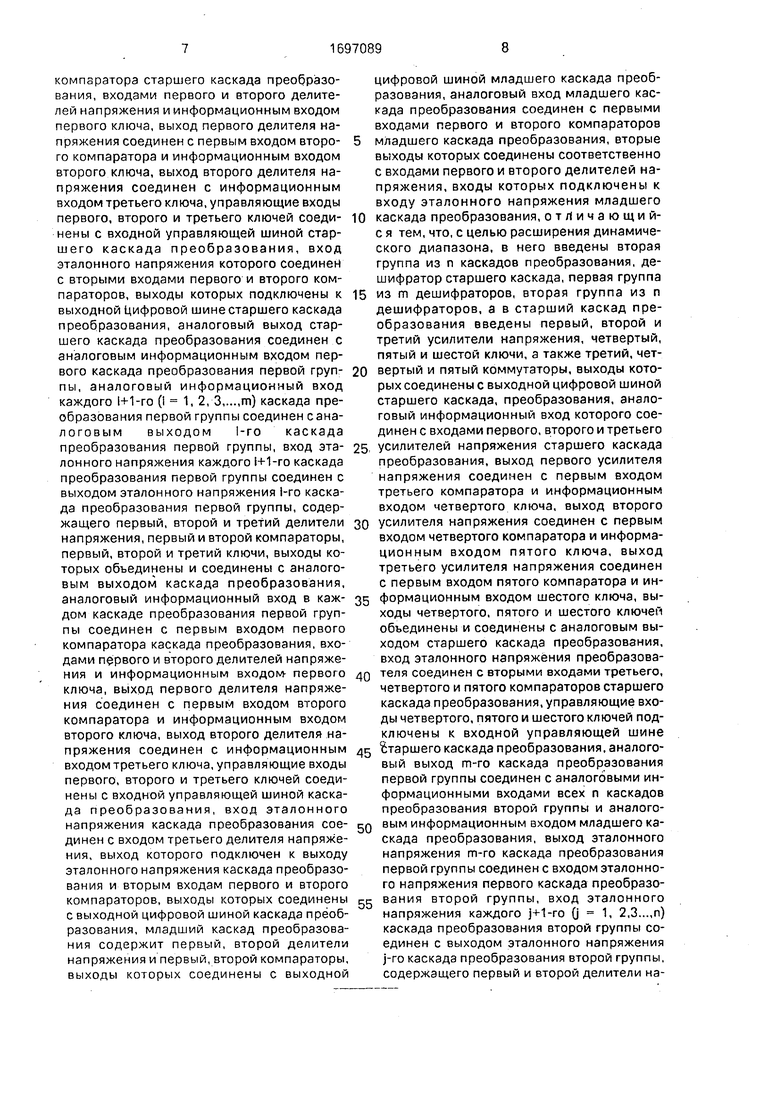

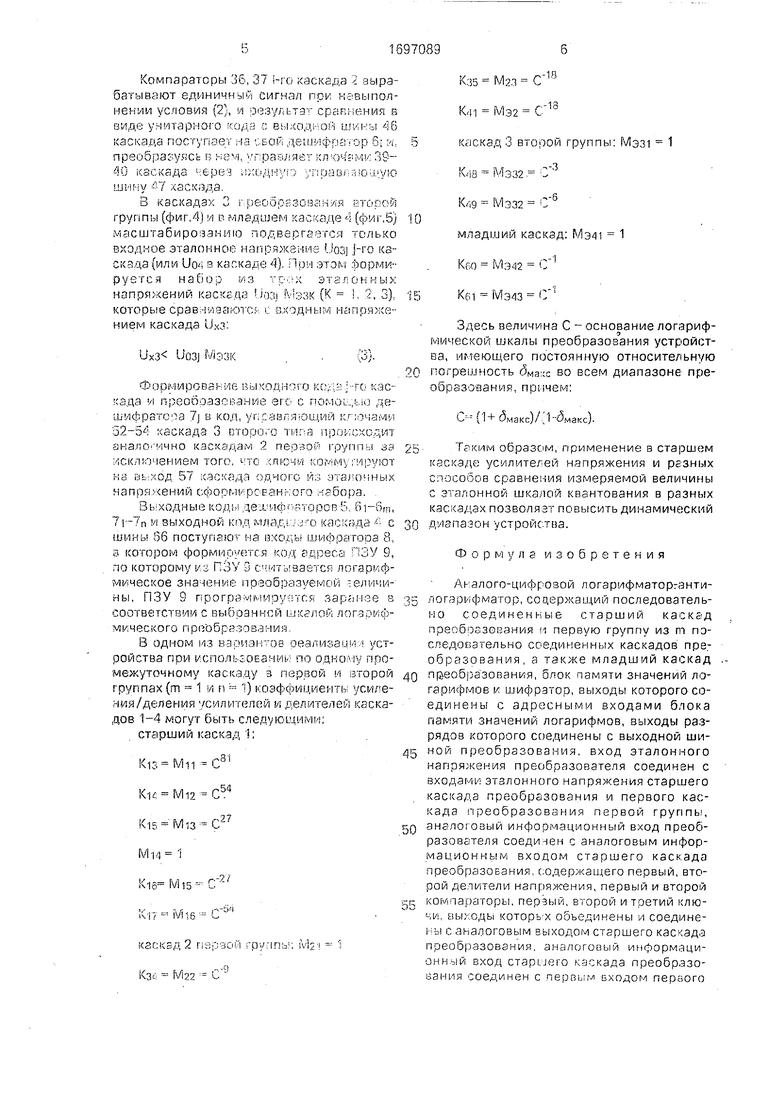

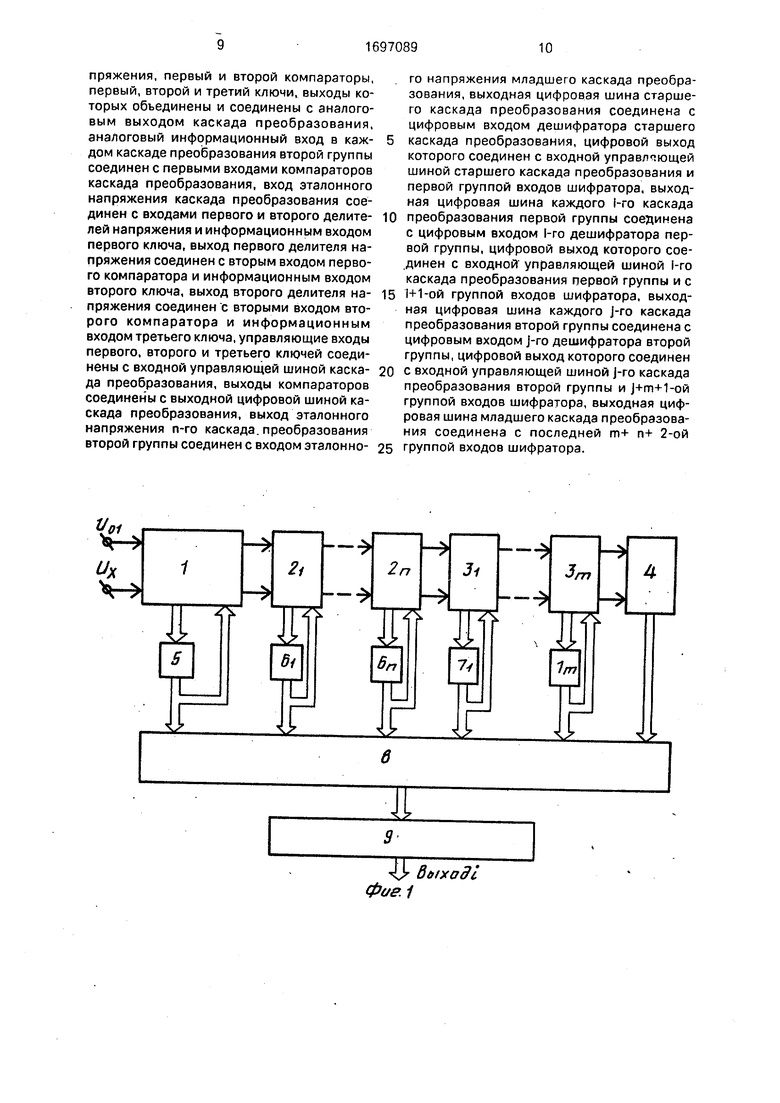

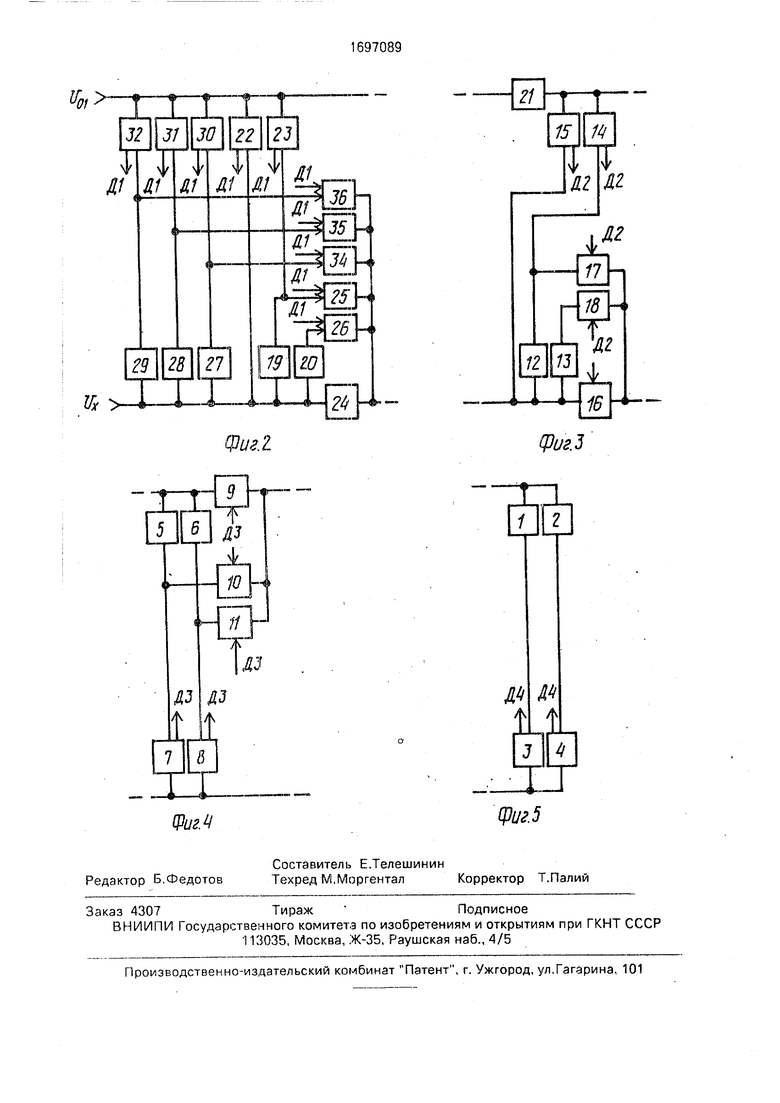

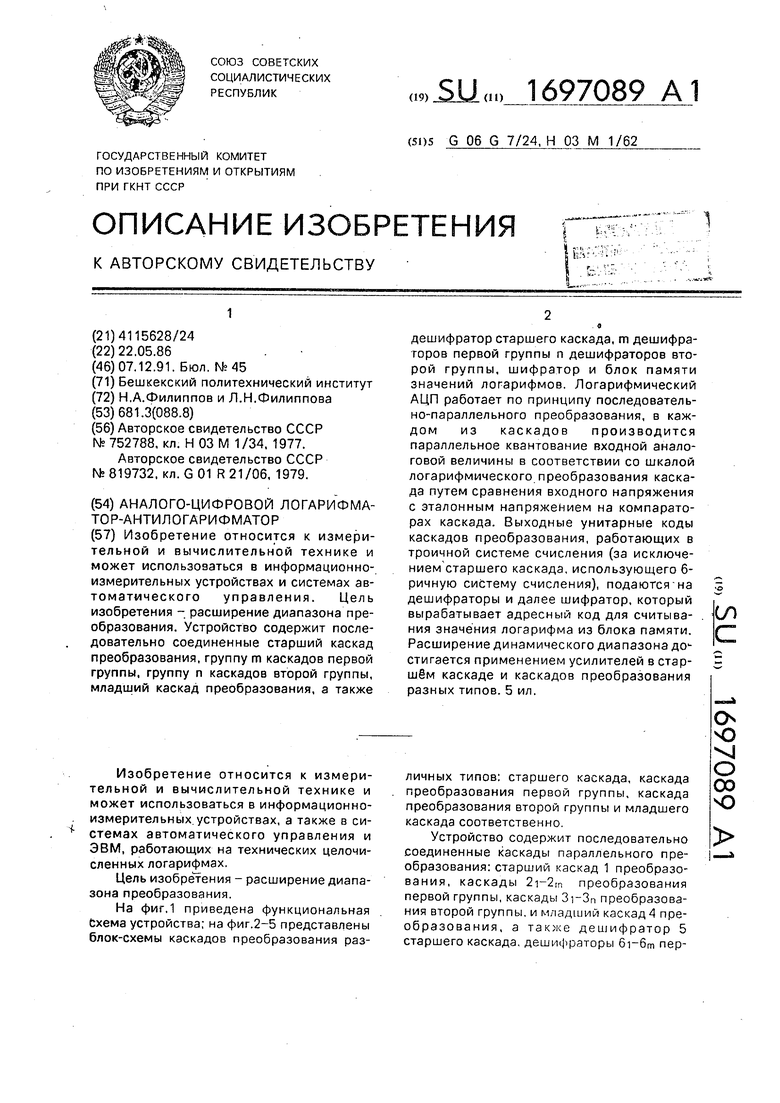

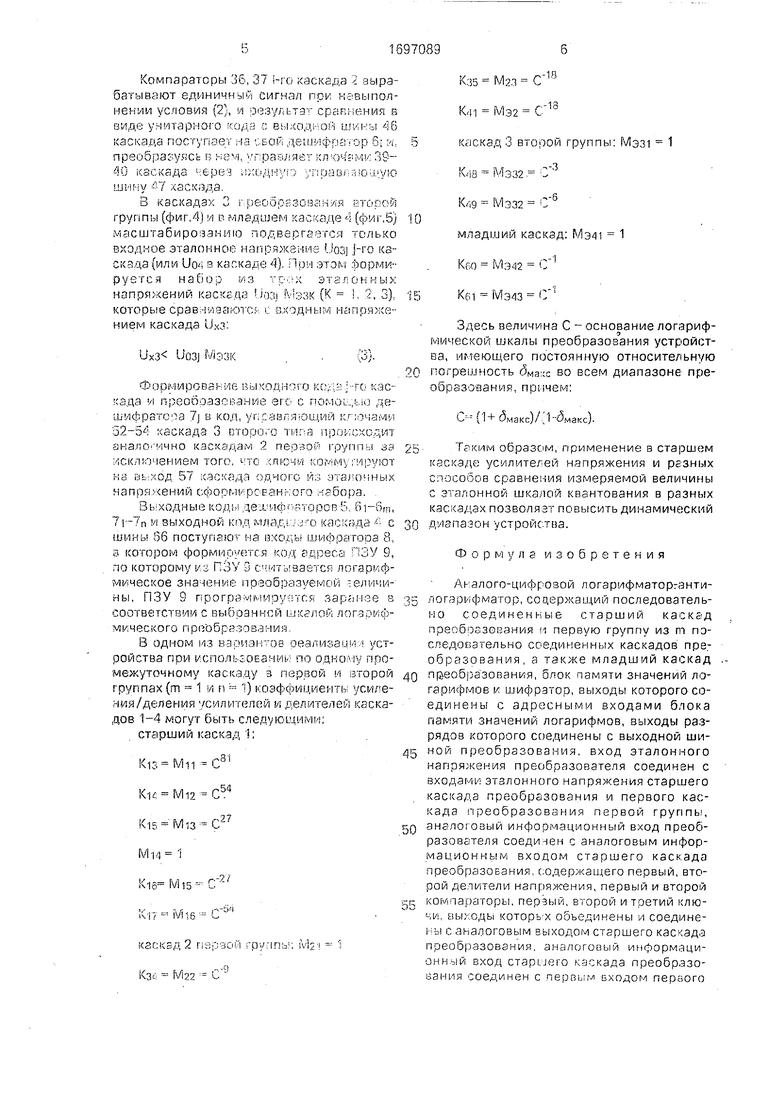

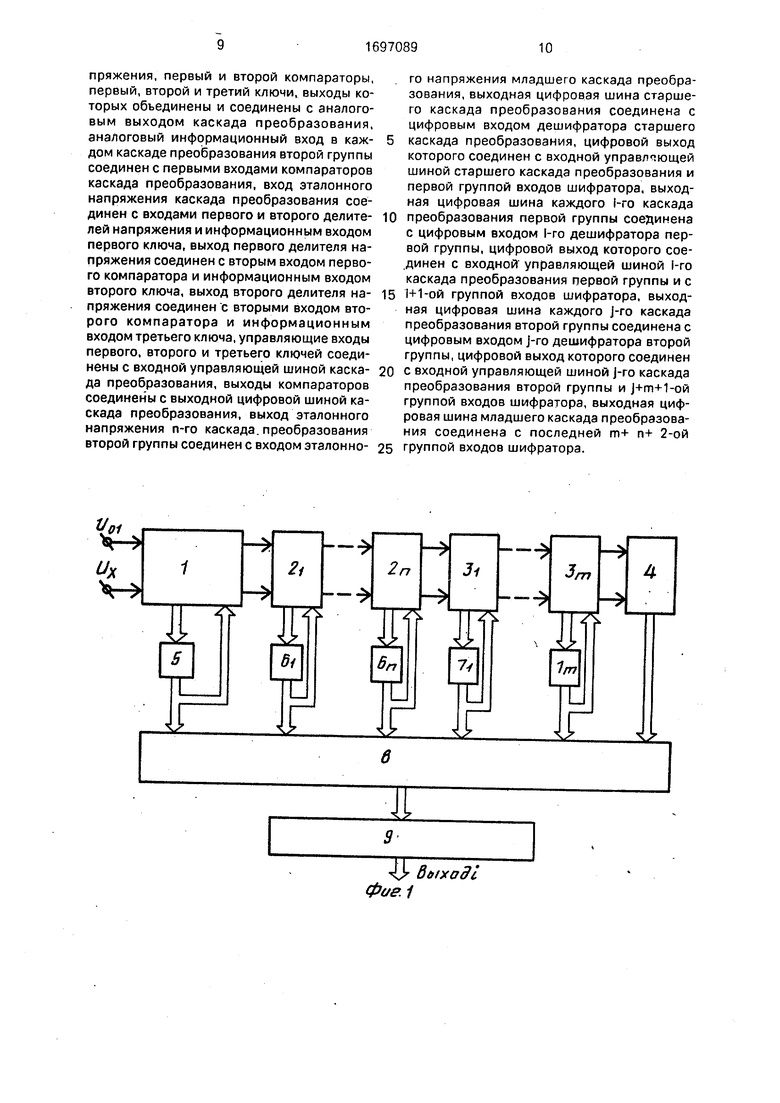

На фиг.1 приведена функциональная схема устройства, на фиг 2-5 представлены блок-схемы каскадов преобразования различных типов: старшего каскада, каскада преобразования первой группы, каскада преобразования второй группы и младшего каскада соответственно

Устройство содержит последовательно соединенные каскады параллельного преобразования старший каскад 1 преобразования, каскады 2i-2,n преобразования первой группы, каскады 3i-3n преобразования второй группы и младший каскад 4 пре- образования, а также дешифратор 5 старшего каскада дешифраторы 6i-6m перо о VJ

о

00

о

вой группы, дешифраторы 7i-7m второй группы, шифратор 8, постоянное запоминающее устройство (ПЗУ) 9, вход 10 эталонного напряжения, аналоговый информационный вход 11 и выходную шину 12 цифрового кода.

Старший каскад 1 преобразования (фиг.2) содержит усилители 13-15с постоянными коэффициентами усиления, делители 16 и 17 напряжения, компараторы 18-22, ключи 23-28, вход 29 эталонного напряжения, аналоговый информационный вход 30, выходную шину 31 сигналов компараторов, входнук управляющую шину 32 и аналого- вый выход 33.

Каскад 2| преобразования первой группы (i 1, 2,...,m) (фиг.З) состоит из делителей 34, 35 напряжения, компараторов 36 и 37, ключей 38-40, делителя 41 эталонного напряжения, входа 42 эталонного напряжения, аналогового информационного входа 43, выхода 44 эталонного напряжения, аналогового выхода 45, выходной шины 46 сигналов компараторов каскада и входной управляющей шины 47.

Каскад 3j преобразования второй группы (j 1,2п) (фиг.4) содержит делители 48,

49 напряжения, компараторы 50, 51, ключи 52-54, аналоговый информационный вход 55, вход 56 эталонного напряжения, выход 57 эталонного напряжения, входную управляющую шину 58, выходную шину 59 сигналов компараторов.

. Младший каскад 4 преобразования (фиг.5) включает в себя делители 60, 61 напряжения, компараторы 62, 63, вход 64 эталонного напряжения, аналоговый информационный вход 65 и выходную шину 66 сигналов компараторов.

Устройство работает следующим образом.

На аналоговый информационный вход 11 поступает преобразуемое напряжение Ux, а на вход 10 подается эталонное напряжение Do.

Устройство является преобразователем последовательно-параллельного типа, при этом в каждом из каскадов 1-4 преобразования производится параллельное сравнение входного сигнала каскада в соответствии с установленным диапазоном и шкалой логарифмического преобразования каскада с эталонным напряжением на компараторах каскада и анализ дешифраторе 5, 6 или 7 своего каскада результатов сравнения.

Разрядность и основание системы счисления выходного кода разных каскадов пре- образования можно выбирать либо одинаковыми, либо различными, в зависимости от технико-экономических требований кустройству. В предложенном варианте исполнения используется смешанная система счисления 6-3-...-3, т.е. старший каскад

использует 6-ричный код, и поэтому имеет пять компараторов, остальные каскады преобразования 2-4 работают в троичном коде и содержат по два компаратора.

Каскады преобразования разных типов

устройства имеют различные способы формирования шкалы квантования каскада, вытекающие из возможного двоякого подхода к процессу сравнения: либо входное напряжение каскада Ux, сравнивается с набором

эталонных напряжений, либо набор промас- штабированных по шкале квантования входных напряжений, полученных из одного входного напряжения каскада Ux. сравнивается с одним единственным эталонным

напряжением каскада. Возможны также промежуточные варианты.

В старшем каскаде 1 преобразования (фиг,2) из входного напряжения Ux с помощью усилителей 13-15 и. делителей

16 и 17с постоянным коэффициентами усиления /ослабления формируется набор промасштабированных напряжений Ux MiK (К 1, 2,...,6), каждое из которых сравнивается на своем компараторе 18-22

с эталонным напряжением Uoi с целью проверки условия

ихМж Uoi

(1)

Если условие (1) выполняется, компаратор вырабатывает сигнал, равный О. В ином случае вырабатывается единичный сигнал.

Общий результат сравнения в виде сигналов компараторов на выходной шине 31 каскада, образующих унитарный код, преобразуется в дешифраторе 5 в позиционный код, который поступает на входную шину 32 старшего каскада и управляет коммутацией

ключей 23-28. При этом на аналоговый выход 33 каскада поступает наибольшее про- масштабированное напряжение ихМк. для которого еще выполняется условие (1), с выхода соответствующего усилителя/делителя 13-17 или с входной шины 30.

В каскадах 2 преобразования первой группы (фиг.З) также производится формирование набора промасштабированных напряжений Ux2i-M2K (К 1, 2, 3; i - номер

каскада),из входного напряжения каскада. Однако при этом изменяется масштаб эталонного напряжения Uo2i Мэ2 и сравнение набора входных напряжений производится с этим эталонным напряжением

Ux2i M2K U02I (2)

компаратора старшего каскада преобразования, входами первого и второго делителей напряжения и информационным входом первого ключа, выход первого делителя напряжения соединен с первым входом второго компаратора и информационным входом второго ключа, выход второго делителя напряжения соединен с информационным входом третьего ключа, управляющие входы первого, второго и третьего ключей соединены с входной управляющей шиной старшего каскада преобразования, вход эталонного напряжения которого соединен с вторыми входами первого и второго компараторов, выходы которых подключены к выходной Цифровой шине старшего каскада преобразования, аналоговый выход старшего каскада преобразования соединен с аналоговым информационным входом первого каскада преобразования первой группы, аналоговый информационный вход каждого i+1-ro (,2, 3,...,m) каскада преобразования первой группы соединен с ана- логовым выходом 1-го каскада преобразования первой группы, вход эталонного напряжения каждого 1+1-го каскада преобразования первой группы соединен с выходом эталонного напряжения 1-го каскада преобразования первой группы, содержащего первый, второй и третий делители напряжения, первый и второй компараторы, первый, второй и третий ключи, выходы которых объединены и соединены с аналоговым выходом каскада преобразования, аналоговый информационный вход в каждом каскаде преобразования первой группы соединен с первым входом первого компаратора каскада преобразования, входами первого и второго делителей напряжения и информационным входом- первого ключа, выход первого делителя напряжения соединен с первым входом второго компаратора и информационным входом второго ключа, выход второго делителя напряжения соединен с информационным входом третьего ключа, управляющие входы первого, второго и третьего ключей соединены с входной управляющей шиной каскада преобразования, вход эталонного напряжения каскада преобразования соединен с входом третьего делителя напряжения, выход которого подключен к выходу эталонного напряжения каскада преобразования и вторым входам первого и второго компараторов, выходы которых соединены с выходной цифровой шиной каскада преобразования, младший каскад преобразования содержит первый, второй делители напряжения и первый, второй компараторы, выходы которых соединены с выходной

цифровой шиной младшего каскада преобразования, аналоговый вход младшего каскада преобразования соединен с первыми входами первого и второго компараторов

младшего каскада преобразования, вторые выходы которых соединены соответственно с входами первого и второго делителей напряжения, входы которых подключены к входу эталонного напряжения младшего

0 каскада преобразования, отЛичающий- с я тем, что, с целью расширения динамического диапазона, в чего введены вторая группа из п каскадов преобразования, дешифратор старшего каскада, первая группа

5 из m дешифраторов, вторая группа из п дешифраторов, а в старший каскад преобразования введены первый, второй и третий усилители напряжения, четвертый, пятый и шестой ключи, а также третий, чет0 вертый и пятый коммутаторы, выходы которых соединены с выходной цифровой шиной старшего каскада, преобразования, аналоговый информационный вход которого соединен с входами первого, второго и третьего

5 усилителей напряжения старшего каскада преобразования, выход первого усилителя напряжения соединен с первым входом третьего компаратора и информационным входом четвертого ключа, выход второго

0 усилителя напряжения соединен с первым входом четвертого компаратора и информа- ционным входом пятого ключа, выход третьего усилителя напряжения соединен с первым входом пятого компаратора и ин5 формационным входом шестого ключа, выходы четвертого, пятого и шестого ключей объединены и соединены с аналоговым выходом старшего каскада преобразования, вход эталонного напряжения преобразова0 теля соединен с вторыми входами третьего, четвертого и пятого компараторов старшего каскада преобразования, управляющие входы четвертого, пятого и шестого ключей подключены к входной управляющей шине

5 Старшего каскада преобразования, аналоговый выход т-го каскада преобразования первой группы соединен с аналоговыми информационными входами всех п каскадов преобразования второй группы и аналого0 вым информационным входом младшего каскада преобразования, выход эталонного напряжения т-го каскада преобразования первой группы соединен с входом эталонного напряжения первого каскада преобразо5 вания второй группы, вход эталонного напряжения каждого j+1-го (j 1, 2,3...,п) каскада преобразования второй группы соединен с выходом эталонного напряжения j-ro каскада преобразования второй группы, содержащего первый и второй делители наКомпараторы 36, 37 i-ro каскада 2 вырабатывают единичный сигнал при невыполнении условия (2), и результат сравнения в виде унитарного кода с выходной шины 46 каскада поступает на свой дешифратор 6t и, преобразуясь в нем, управляет ключами 39- 40 каскада через аходную управляющую шину 47 каскада.

В каскадах 3 преобразования второй группы (фиг.4) и в младшем каскаде 4 (фиг,5) масштабированию подвергается только входное эталонное напряжение Uo3j j-ro каскада (или Uo4 в каскаде 4). При этом формируется набор из трех эталонных напряжений каскада Uo3i Мэзк (К 1, 2, 3), которые сравниваются с входным напряжением каскада ихз:

Ux3 Uosj Мэзк

Формирование выходного кода j-ro каскада и преобразование его с помощью де- шифратспа 7j в код, управляющий ключами 52-54 каскада 3 второго типа происходит аналогично каскадам 2 первой группы за исключением того, что ключи коммутируют на выход 57 каскада одного из эталонных напряжений сформированного набора.

Выходные коды дешифраторов 5, 6i-8m, 7i-7n и выходной код младшего каскада 4 с шины 66 поступают на входы шифратора 8, в котором формируется код адреса ПЗУ 9, по которому из ПЗУ 9 считывается логарифмическое значение преобразуемой величины. ПЗУ 9 программируется заранее в соответствии с выбранной шкалой логарифмического преобразования.

В одном из вариантов реализации устройства при использовании по одному промежуточному каскаду в первой и второй группах (т 1 и п 1) коэффициенты усиления/деления усилителей и делителей каскадов 1-4 могут быть следующими:

старший каскад 1:

Ki3 Mn C

81

К14 М12 С

л-54

C27

М14 1

Kl«rMl5 C 27

Ki7 SVti6 C 54

каскад 2 первой группы: М21 1

К34 М22 С

Кз5 Маз С

-18

-18

К41 МЭ2 С

каскад 3 второй группы: Мэзт 1

-з

К48 МЭ32 С К49 МЭ32

младший каскад: 1

КбО МЭ42 С

Кб1 Мэ43 С

-1

-1

20

25

30

35

40

45

50

55

Здесь величина С - основание логарифмической шкалы преобразования устройства, имеющего постоянную относительную погрешность (5Макс во всем диапазоне преобразования, причем:

С(1+(5Макс)/(1- 5макс).

Таким образом, применение в старшем каскаде усилителей напряжения и разных способов сравнения измеряемой величины с эталонной шкалой квантования в разных каскадах позволяет повысить динамический диапазон устройства.

Формула изобретения

Аналого-цифровой логарифматорганти- логарифматор, содержащий последовательно соединенные старший каскад преобразования и первую группу из m последовательно соединенных каскадов пре,- образования, а также младший каскад преобразования, блок памяти значений логарифмов и шифратор, выходы которого со- единены с адресными входами блока памяти значений логарифмов, выходы разрядов которого соединены с выходной шиной преобразования, вход эталонного напряжения преобразователя соединен с входами эталонного напряжения старшего каскада преобразования и первого каскада преобразования первой группы, аналоговый информационный вход преобразователя соединен с аналоговым информационным входом старшего каскада преобразования, содержащего первый, второй делители напряжения, первый и второй компараторы, первый, второй и третий ключи, выходы которых объединены и соединены с аналоговым выходом старшего каскада преобразования, аналоговый информационный вход старшего каскада преобразования соединен с первым входом первого

пряжения, первый и второй компараторы, первый, второй и третий ключи, выходы которых объединены и соединены с аналоговым выходом каскада преобразования, аналоговый информационный вход в каждом каскаде преобразования второй группы соединен с первыми входами компараторов каскада преобразования, вход эталонного напряжения каскада преобразования соединен с входами первого и второго делителей напряжения и информационным входом первого ключа, выход первого делителя напряжения соединен с вторым входом первого компаратора и информационным входом второго ключа, выход второго делителя напряжения соединен с вторыми входом второго компаратора и информационным входом третьего ключа, управляющие входы первого, второго и третьего ключей соединены с входной управляющей шиной каскада преобразования, выходы компараторов соединены с выходной цифровой шиной каскада преобразования, выход эталонного напряжения n-го каскада.преобразования второй группы соединен с входом эталонного напряжения младшего каскада преобразования, выходная цифровая шина старшего каскада преобразования соединена с цифровым входом дешифратора старшего

каскада преобразования, цифровой выход которого соединен с входной управляющей шиной старшего каскада преобразования и первой группой входов шифратора, выходная цифровая шина каждого 1-го каскада

преобразования первой группы соединена с цифровым входом 1-го дешифратора первой группы, цифровой выход которого соединен с входной управляющей шиной 1-го каскада преобразования первой группы и с

l+1-ой группой входов шифратора, выходная цифровая шина каждого J-ro каскада преобразования второй группы соединена с цифровым входом j-ro дешифратора второй группы, цифровой выход которого соединен

с входной управляющей шиной j-ro каскада преобразования второй группы и j+m+1-ой группой входов шифратора, выходная цифровая шина младшего каскада преобразования соединена с последней т+ п+ 2-ой

группой входов шифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1973 |

|

SU711676A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1193808A1 |

| Устройство для преобразования напряжения в код системы остаточных классов | 1982 |

|

SU1056450A2 |

| Аналого-цифровой преобразователь последовательного приближения | 1981 |

|

SU1018228A1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ УГЛА ПОВОРОТА ВАЛА В КОД | 1993 |

|

RU2108663C1 |

| Параллельно-последовательный преобразователь напряжения в код | 1975 |

|

SU588628A1 |

| Параллельный аналого-цифровой преобразователь | 1986 |

|

SU1332533A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1983 |

|

SU1211881A1 |

| Преобразователь напряжение-код | 1983 |

|

SU1403370A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1494218A2 |

Изобретение относится к измерительной и вычислительной технике и может использоваться в информационно- измерительных устройствах и системах автоматического управления. Цель изобретения - расширение диапазона преобразования. Устройство содержит последовательно соединенные старший каскад преобразования, группу m каскадов первой группы, группу п каскадов второй группы, младший каскад преобразования, а также дешифратор старшего каскада, m дешифраторов первой группы п дешифраторов второй группы, шифратор и блок памяти значений логарифмов Логарифмический АЦП работает по принципу последовательно-параллельного преобразования, в каждом из каскадов производится параллельное квантование входной аналоговой величины в соответствии со шкалой логарифмического преобразования каскада путем сравнения входного напряжения с эталонным напряжением на компараторах каскада Выходные унитарные коды каскадов преобразования, работающих в троичной системе счисления (за исключением старшего каскада использующего 6- ричную систему счисления), подаются на дешифраторы и далее шифратор, который вырабатывает адресный код для считывания значения логарифма из блока памяти. Расширение динамического диапазона достигается применением усилителей в старшем каскаде и каскадов преобразования разных типов 5 ил. 00 С

Ж

Выход} Фае. 1

«6/

К

Фиг2

фиг.З

№

№

м..-J

фм.5

| Быстродействующий аналогоцифровой преобразователь | 1978 |

|

SU752788A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой ваттметр | 1978 |

|

SU819732A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-12-07—Публикация

1986-05-22—Подача