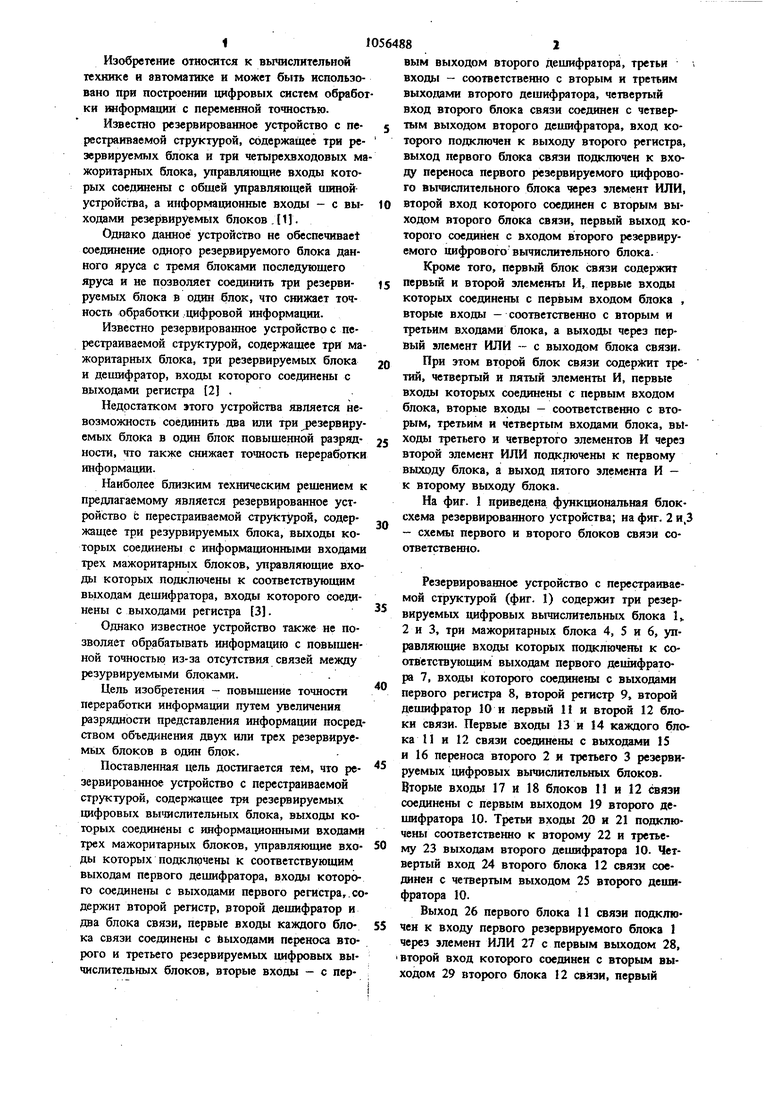

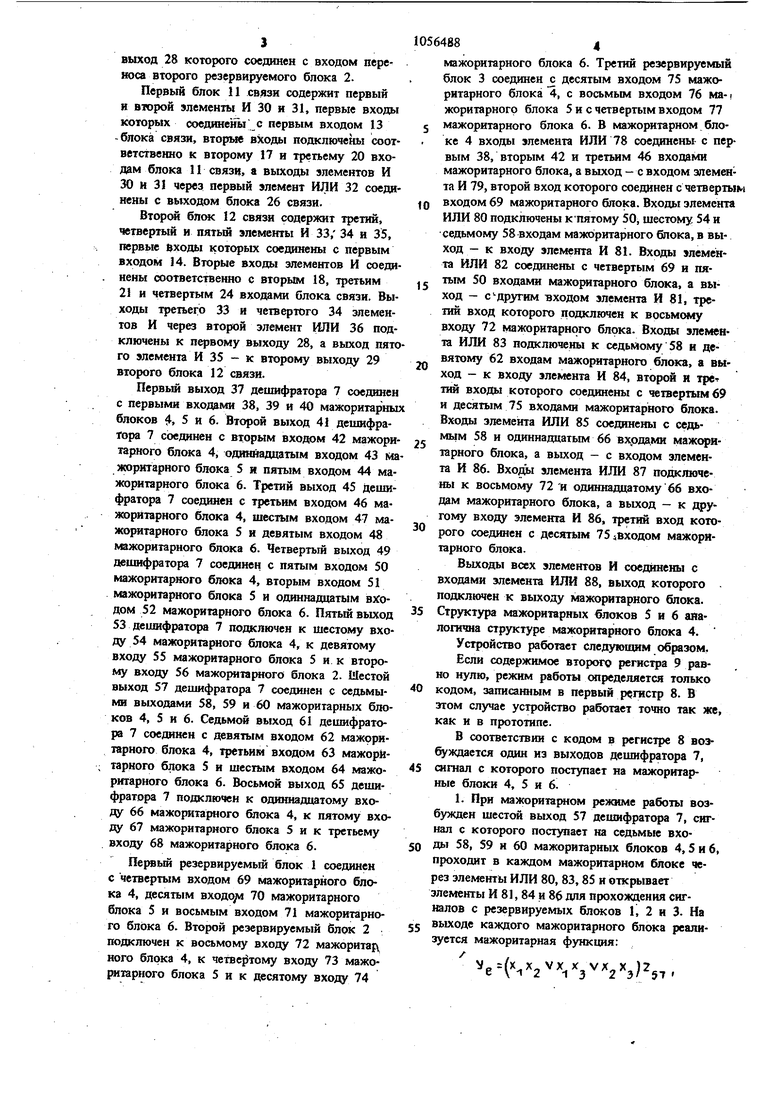

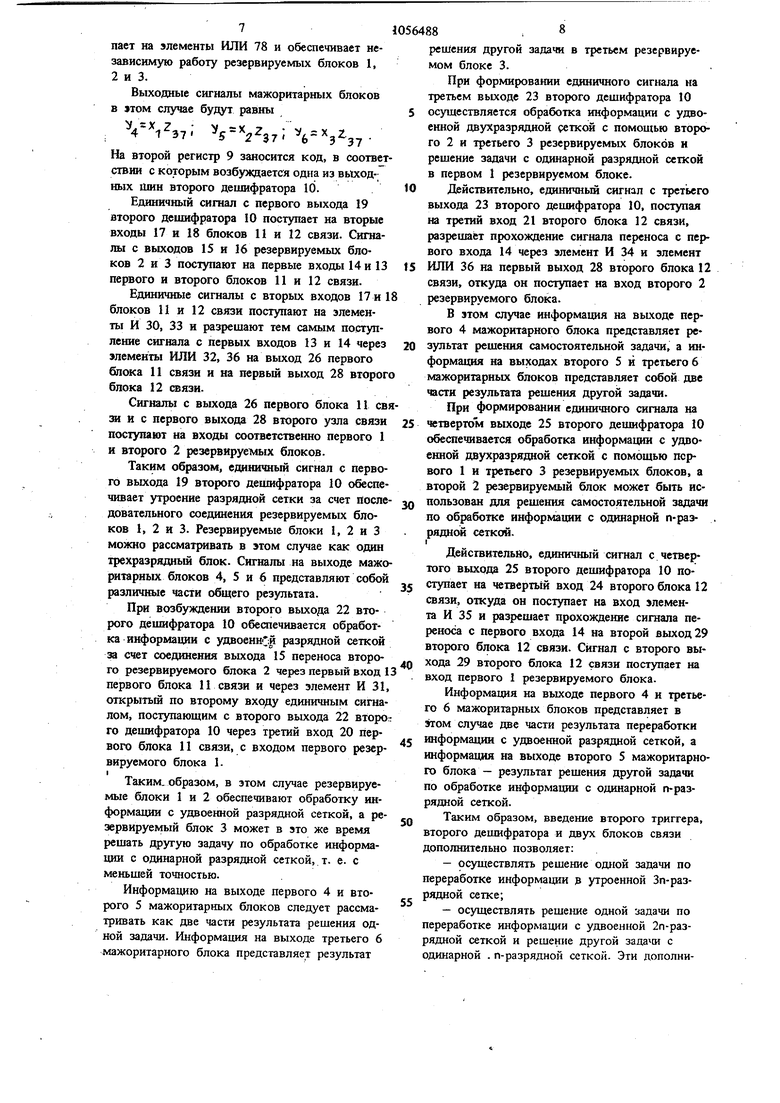

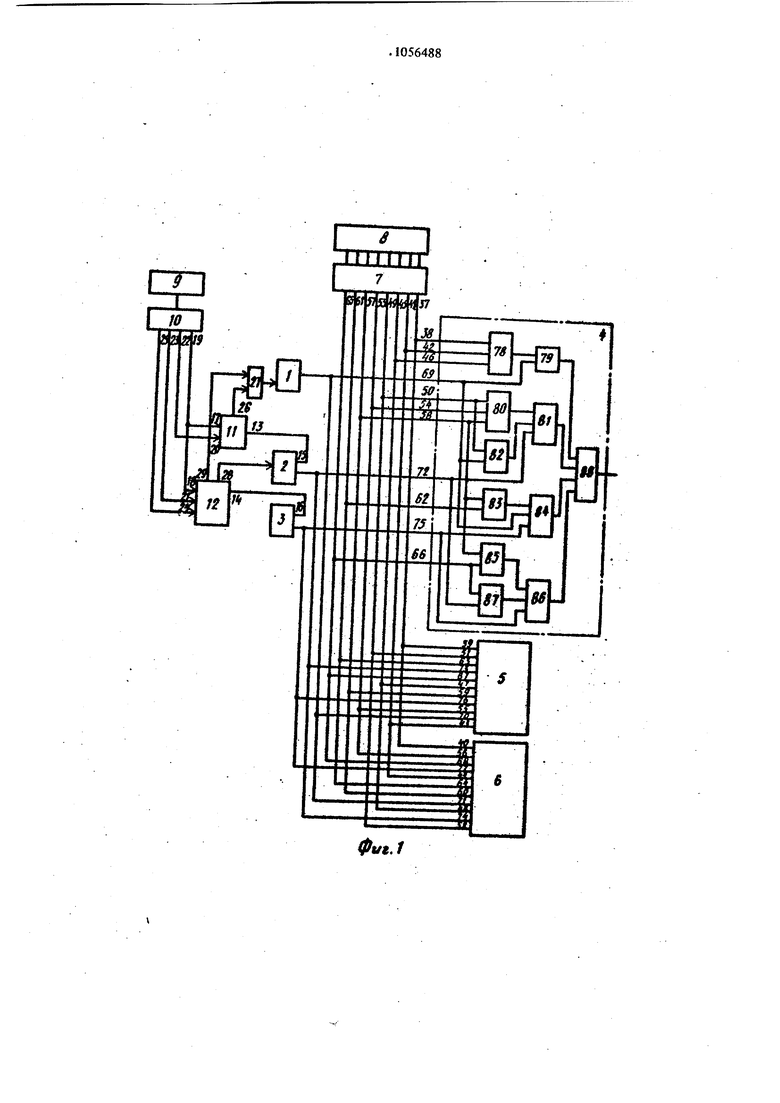

Изобретение отнооттся к вычислительной технике и автоматике и может быть использовано при построении цифровых систем обработ ки информации с перемегаюй точностью. Известно резервированное устройство с перестраиваемой стрз ктурой, содержащее три резервируемых блока и три четырехвходовых ма жоритарных блока, управляющие входы которых соединены с обшей управляющей иогаой устройства, а информационные входы - с выходами резервируемых блоков , 1 . Од1ико данное устройство не обеспечивае соединение одного резервируемого блока данного яруса с тремя блоками последующего яруса и не позволяет соединить три резервируемых блока в один блок, что снижает точность обработки цифровой информации. Известно резервированное устройство с перестраиваемой структурой, содержащее три мажоритарных блока, три резервируемых блока и дешифратор, входы которого соединены с выходами регистра (2 . Недостатком этого устройства является невозможность соединить два или три резервируемых блока в один блок повышенной разрядности, что также снижает точность переработки информации. Наиболее близким техническим решением к предлагаемому является резервированное устройство с перестраиваемой стрзтстурой, содержащее три резурвируемых блока, выходы которых соеданены с информационными входами трех мажоритарных блоков, управляющие входы которых подключены к соответствующим вьцсодаМ дешифратора, входы которого соединены с выходами регистра 3. Однако известное устройство также не позволяет обрабатывать информацию с повышенной точностью из-за отсутствия связей между резурвнруемыми блоками. Цель изобретения - повышение точности переработки информации путем увеличения разрядности представления информации посредством объединения двух или трех резервируемых блоков в один блок. Поставленная цель достигается тем, что резервированное устройство с перестраиваемой структурой, содержащее три резервируемых цифровых вычислительных блока, выходы которых соединены с информационными входами трех мажоритарных блоков, управляющие входы которых подключены к соответствующим выходам первого дешифратора, входы которого соединены с выходами первого регистра,.со держит второй регистр, второй дешифратор и два блока связи, первые входы каждого блока связи соединены с выходами переноса второго и третьего резервируемых цифровых вычислительных блоков, вторые входы - с первым выходом второго дешифратора, третьи входы - соответственно с вторым и третьим выходами второго дешифратора, четвертый вход второго блока связи соединен с четвертым выходом второго дешифратора, вход которого подключен к выходу второго регистра, выход первого блока связи подключен к входу переноса первого резервируемого цифрового вычислительного блока через элемент ИЛИ, второй вход которого соединен с вторым выходом второго блока связи, первый выход которого соединен с входом в торого резервируемого цифрового вычислительного блока. Кроме того, первый блок связи содержит первый и второй элементы И, первые входы которых соединены с первым входом блока , вторые входы - соответственно с вторым и третьим входами блока, а выходы через первый элемент ИЛИ - с выходом блока связи. При этом второй блок связи содержит третий, четвертый и пятый элементы И, первые входы которых соединены с первым входом блока, вторые входы - соответственно с вторым, третьим и четвертым входами блока, выходы третьего и четвертого элементов И через второй элемент ИЛИ подключены к первому выходу блока, а выход пятого элемента И - к второму выходу блока. На фиг. 1 приведена функциональная блоксхема резервированного устройства; на фиг. 2 и,3 - схемы первого и второго блоков связи соответствешад. Резервированное устройство с перестраиваемой структурой (фиг. 1) содержит три резервируемых цифровых вычислительных блока 1,. 2 и 3, три мажоритарных блока 4, 5 и 6, управляющие входы которых подключены к соответствующим выходам первого децшфратора 7, входы которого соединены с выходами первого регистра 8, второй регистр 9, второй дешифратор 10 и первый Ни второй 12 блоки связи. Первые входы 13 и 14 каждого блока П и 12 связи соединены с выходами 15 и 16 переноса второго 2 и третьего 3 резервируемых цнфровых вычислительных блоков. Вторые входы 17 и 18 блоков 11 и 12 связи соединены с первым выходом 19 второго дешифратора 10. Третьи входы 20 и 21 подключены соответственно к второму 22 и третьему 23 выходам второго дешифратора 10. Четвертый вход 24 второго блока 12 связи соединен с четвертым выходом 25 второго дешифратора 10. Выход 26 первого блока 11 связи подключен к входу первого резервируемого блока 1 через элемент ИЛИ 27 с первым выходом 28, Второй вход которого соединен с вторым выходом 29 второго блока 12 связи, первый

выход 28 которого соединен с входом переноса второго резервируемого блока 2.

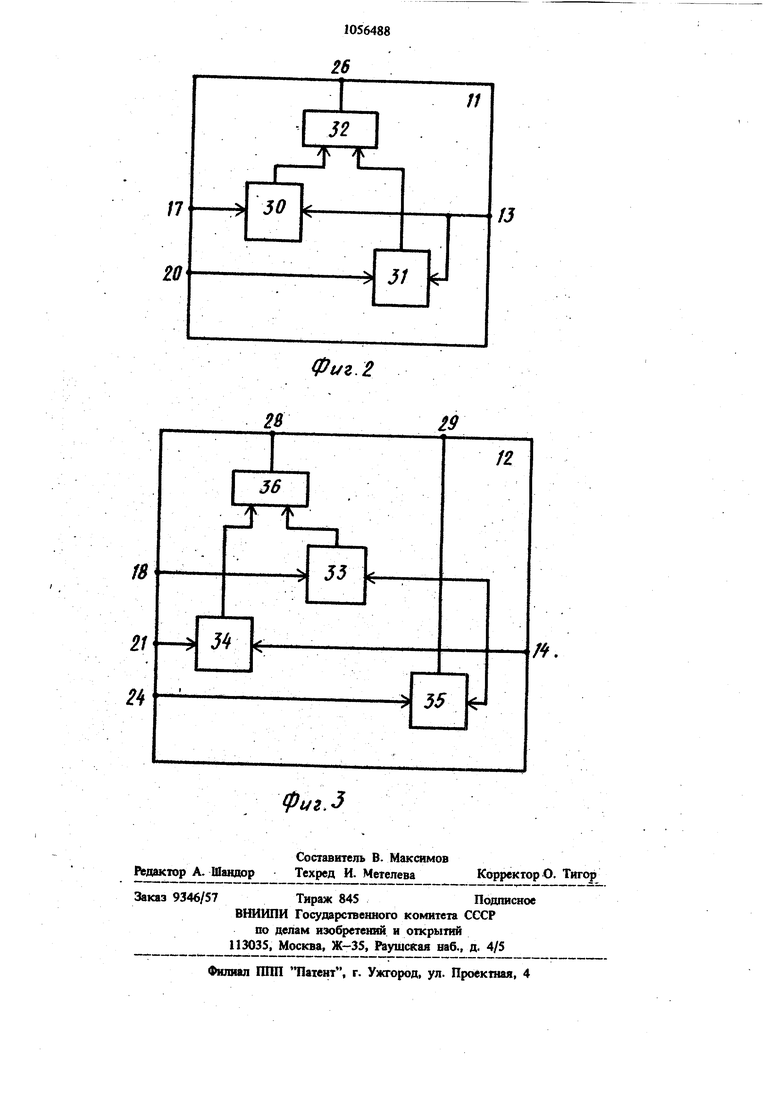

Первый блок И связн содержит первый к второй элементы И 30 и 31, первые входы которых соединены с первым входом 13 -блока связи, вторые входы подаслючены соответственно к второму 17 и третьему 20 входам блока 11 связи, а выходы элементов И 30 и 31 через первый элемент ИЛИ 32 соединены с выходом блока 26 связи.

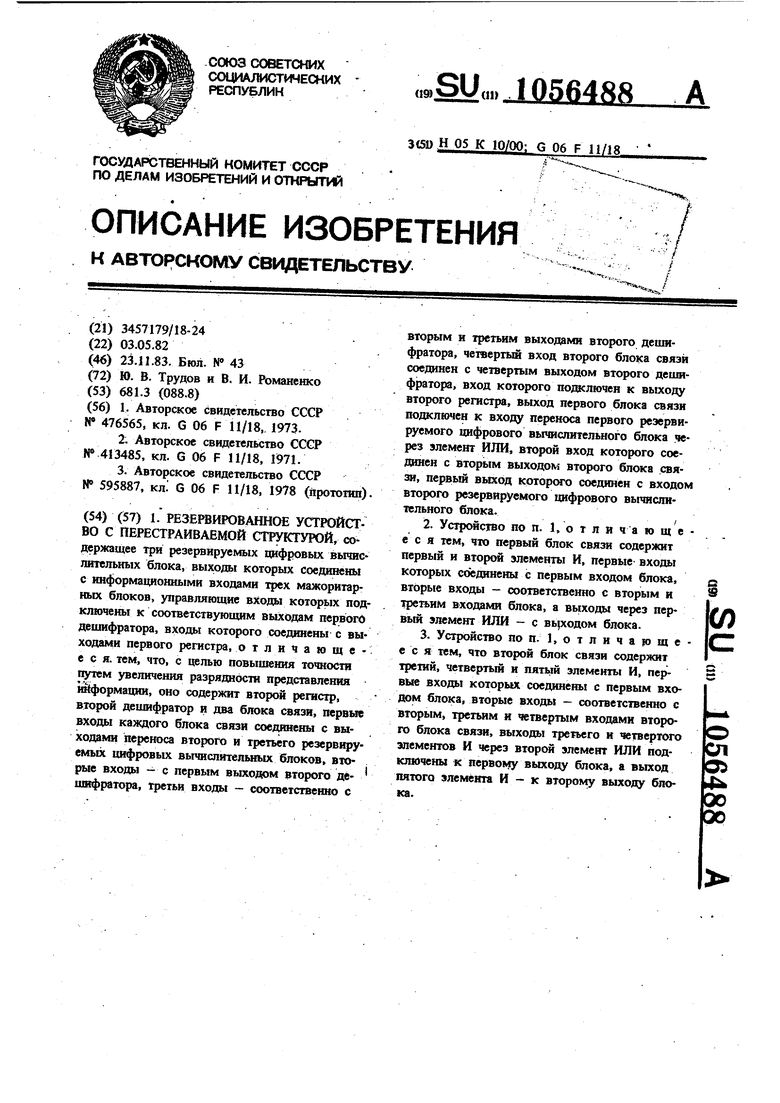

Втар(ж бпок 12 связи содержит третий, четвертый и пятый элементы И 33/ 34 и 35, первые входы которых соеданены с первым входом 14. Вторые входы элементов И соединены соответственно с вторым 18, третьим 21 и четвертым 24 входами блока связи. Выходы третьего 33 и четвертого 34 элементов И через второй элемент ИЛИ 36 подключены к первому выходу 28, а выход пятого элемента И 35 - к второму выходу 29 второго блока 12 связи.

Первый выход 37 дешифратора 7 соединен с первыми входами 38, 39 и 40 мажоритарны блоков 4 5 и 6. Второй выход 41 дешифратора 7 соединен с вторым входом 42 мажоритарного блока 4, одиннадцатым входом 43 мажоритарного блока 5 и пятым входом 44 мажоритарного блока 6. Третий выход 45 дешифратора 7 соединен с третьим входом 46 мажоритарного блока 4, шестым входом 47 мажоритарного блока 5 и девятым входом 48 мажоритарного блока 6. Четвертый выход 49 дешифратора 7 соединен с пятым входом 50 мажоритарного блока 4, вторым входом 51 мажоритарного блока 5 и одиннадцатым входом 52 мажоритарного блока 6. Пятый выход 53 дешифратора 7 подключен к шестому входу 54 мажоритарного блока 4, к девятому входу 55 мажоритарного блока 5 и к второму входу 56 мажо1жтарного блока 2. Шестой выход 57 дешифратора 7 соединен с седьмыми выходами 58, 59 и 60 мажоритарных блоков 4, 5 и 6. Седьмой выход 61 дешифратора 7 соединен с девятым входом 62 мажоритарного блока 4, третьим входом 63 мажоритарного блока 5 и шестым входом 64 мажоритарного блока 6. Восьмой выход 65 дешифратора 7 подключен к одиннадцатому входу 66 мажоритарного блока 4, к пятому входу 67 мажоритарного блока 5 и к третьему входу 68 мажоритарного блока 6.

Пертэый резервируемый блок 1 соединен с четвертым входом 69 мажоритарного блока 4, десятым ВХОДОД1 70 мажоритарного блока 5 и восьмым входом 71 мажоритарного блока 6. Второй резервируемый блок 2 подключен к восьмому входу 72 мажоритару ного блока 4, к четвертому входу 73 мажоритарного блока 5 и к десятому входу 74

564884

мажоритарного блока 6. Третнй резервируемый блок 3 соединен десятым входом 75 мажоритарного блока 4, с восьмым входом 76 ма-1 жоритарного блока 5 и с четвертым входом 77

5 мажоритарного блока 6. В мажоритарном бло, ке 4 входы элемента ИЛИ 78 соеданены с первым 38, вторым 42 н третьим 46 входами мажоритарного блока, а выход - с входом элемента И 79, второй вход которого соединен с четвертым

10 входом 69 мажоритарного блока. Входы элемента ИЛИ 80 подключены кпятому 50, шестому 54 и седьмому 58 входам мажоритарного блока, в выход - к входу элемента И 81. Входы элемента ИЛИ 82 соединены с четвертым 69 и пя.- тым 50 входами мажо штарного блока, а выход - с другим входом элемента И 81, третий вход которого подключен к восьмому вхо 72 мажоритарного блока. Входы элемента ИЛИ 83 подключены к седьмому 58 и девятому 62 входам мажоритарного блока, а вы20ход - к входу элемента И 84, второй и трСт тнй входы которого соединены с четвертым 69 и десятым 75 входами мажоритарного блока. Входы элемента ИЛИ 85 соединены с седьмь1М 58 н oдкннaдцaтьпv( 66 вхрда.ми мажсфи25тарного блока, а выход - с входом элемента И 86. Входа элемента ИЛИ 87 подключены к восьмому 72 и одиннадцатому 66 входам мажоритарного блока, а выход - к другому входу элемента И 86, третий вход кого рого соединен с десятым 755Входом мажоритарного блока.

Выходы всех элементов И соединены с входами элемента ИЛИ 88, выход которого . подключен к выходу мажоритарного блока.

5 Структура мажоритарных блоков 5 и 6 аналогична структуре мажоритарного блока 4. Устройство работает следующим образом, Если содержимое второго регистра 9 равно нулю, режим работы слределяется только

40 кодом, записанным в первый регистр 8. В этом случае устройство работает точно так же, как и в прототипе.

В соответствии с кодом в регис1фе 8 возбуждается один из выходов дешифратора 7,

45 сигнал с которого поступает на мажоритарHbie блоки 4, 5 и 6.

1. При мажоритартом режиме работы возбужден шестой выход 57 дешифратора 7, сигнал с которого nociynaer на седьмые вхо50 ды 58, 59 и 60 мажоритарных блоков 4,5 и 6, проходит в каждом мажоритарном блоке через элементы ИЛИ 80, 83,85 и открывает элементы И 81, 84 и 86 для прохождения сигналов с резервируемых блсжов 1, 2 и 3. На

jij выходе каждого мажоритарного блока реализуется мажоритарная функция:

(, гдеУ - выходной сигнал мажоритарного блока (Ур 1, 2, 3); X - выходные сигналы резервируемых блоков 1, 2 и 3; i,-- сигнал на шестом выходе 57 дешифратора 7. 2. При возбуждении одного из выходов: второго 41, четвертого 49 и восьмого 65 выходов дешифратора 7 выходной сигнал на выходе всех мажоритарных блоков равен выходному сигналу одного из резервируемых блоков 1, 2 и 3 соответственно. Действительно, при возбуждении второго выхода 41 дешифратора 7 сигнал поступает через второй вход 42 мажоритарного блока 4 на элемент ИЛИ 78, через одиннадцатый вход 4 мажоритарного блока 5 - на элемент ИЛИ 85 87 и через пятый вход 44 мажоритарного блока 6 - на элементы ИЛИ 80, 82. Сигнал с выхода элемента ИЛИ 78 мажоритарного блока 4 открывает элемент И 79, на второй вход которого поступает сигнал от резервируемого блока 1 через четвертый вход 6 мажоритарного блока 1. Таким образом, выходной сигнал мажоритарного блока 41 будет равен. . 241Сигналы с выходов элементов ИЛИ 80, 82 мажоритарного блока 6 открьшаютэлементИ.8 на третий вход которого через восьмой вход 7 мажоритарного блока 6 поступает сигнал с вы хода резервируемого блока 1. Выходной сигнал мажоритарного блока 6 будет равен

Х 2.

Ч 4

Аналогично можно сказать, что при возбуждении восьмого выхода 65 дешифратора 7 выходные сипилы мажоритарных блоков будут равны

V 3f4.

а при возбуждении четвертого выхода 49

4

Такой режим позволяет сохранить работоспособность устройства до тех пор, пока исправен хотя бы один резервируемый блок.

3. При возбуждении первого выхода 37 дешифратора 7 обеспечивается независимая ра-, бота резервируемых блоков 1, 2 и 3. Сигнал с первого выхода 37 дешифратора 7 через первые входы 38, 39 и 40 мажоритарных блоков 4, 5 и 6 открьтает элементь И 79, на другие входы которых поступает сигнал через четвертые входы .резервируемых блоков 1, 2 и 3 соответстве шо.

Выходные сигналы мажоритарных блоков в этом случае будут равны: 1

Сигнал с выхода-элемента ИЛИ 83 мажоритарного блока 6 поступает на вход элемента И 84, на второй и третий входь5 которого через четвертью вход 77 и десятый вход 74 поступают сигналы с выходов третьего 3 и второго 2 резервируемых блоков. Выходной сигнал мажоритарного блока 6 будет равен

6

2 3 45Аналогично можно показать, что при возбуждении пятого выхода 53 дешифратора 7 выходные сигналы мажоритарных блоков будут равны

6

а при возбужденоии седьмого выхода 61 дешифратора 7

V -у 7

.

5-2 41

Для обработки информации с повышенной точностью в регистр 8 заносится код, при котором возбуждается первый выход 36 дешифратора 7. Едшшчный сигнал с первого Bbixdда 37 деишфратора 7 через первые входы 38, : 39 и 40 мажоритарных блоков 4, 5 и 6 посту86 режим используется для повьш ения производительности устройства и для повышения точности вычислений. 4. При возбуждении третьего 45 или пятого 53, или седьмого 61 выходов дешифратора 7 обеспечивается независимая работа одного из резервируемых блоков и совместная работа двух других блоков. Сигнал с третьего выхода 45 дешифратора 7 поступает через третий вход 46 мажоритарного блока 4 на эле- мент ИЛИ 78, через шестой вход 47 мажоритарного блока 5 - на элемент ИЛИ 80 и через девятьш вход 48 мажоритарного блока 6 на элемент ИЛИ 83. Сигнал с выхода элемента ИЛИ 78 м жоритарного блока 4 открьтает элемент И 79, на другой вход которого через четвертый вход 69 мажоритарного блока 4 поступает сигнал с выхода резервируемого блока 1. Выходной сигнал мажоритарного блока 4 будет равен Ч Сигнал с выхода элемента ИЛИ 80 мажоритарного блока 5 поступает на вход элемента И 81, на второй вход которого через элемент ИЛИ 82 и четвертый вход 73 мажоритарного блока 5 поступает сигнал с выхода второго резервируемого блока 2, а на третий вход - через восьмой вход 55 мажоритарного бл(жа 5 сигнал с выхода третьего резервируемого блока 3. Выходной сигнал мажоритарного блока 5 будет равен

пает на элементы ИЛИ 78 и обеспечивает независимую работу резервируемых блоков 1, 2 и 3.

Выходные сигналы мажоритарных блоков в этом случае будут равны

.

На второй регистр 9 заносится код, в соответствии с которым возбуждается одна из выход-; ных ишн второго дешифратора 10.

Единичный сигнал с первого выхода 19 второго дешифратора 10 поступает иа вторые входы 17 и 18 блоков 11 и 12 связи. Сигналы с выходов 15 и 16 резервируемых блоков 2 и 3 поступают на первые входы 14 и 13 первого и второго блоков 11 и 12 связи.

Единичные сигналы с вторых входов 17 и 18 блоков 11 и 12 связи поступают на элементы И 30, 33 и разрешают тем самым поступление сигнала с первых входов 13 и 14 через элементы ИЛИ 32, 36 на выход 26 первого бл(жа И связи и на первый выход 28 второго блока 12 связи.

Сигналы с выхода 26 первого блока 11 связи и с первого выхода 28 второго узла связи поступают на входы соответственно первого 1 и второго 2 резервируетиых блоков.

Таким образом, единичный сигнал с первого выхода 19 второго дешифратора 10 обеспечивает утроение разрядной сетки за счет Последовательного соединения резервируемых блоков 1, 2 и 3. Резервируемые блоки 1, 2 и 3 можно рассматривать в этом случае как один трехразрядный блок. Сигналы иа выходе мажоритарных блоков 4, 5 и 6 представляют собой различные части общего результата.

При возбуждении второго выхода 22 второго дешифратора 10 обеспечивается обработка информации с удвоенной разрядной сеткой за счет соединения выхода 15 переноса второго резервируемого блока 2 через первый вход 1 первого блока И связи и через элемент И 31, открытый по второму входу единичным сигналом, поступающим с второго выхода 22 второго дешифратора 10 через третий вход 20 первого блока 11 связи, с входом первого резервируемого блока 1.

Таким, образом, в этом случае резервируемые блоки 1 и 2 обеспечивают обработку информации с удвоенной разрядной сеткой, а резервируемый блок 3 может в это же время решать другую задачу по обработке информации с одинарной разрядной сеткой, т. е. с меньшей точностью.

Информацию на выходе первого 4 и второго 5 мажоритарных блоков следует рассматривать как две части результата решения одной задачи. Информация на выходе третьего 6 мажоритарного блока представляет результат

решения другой задачи в третьем резервируемом блоке 3.

При формировании еданичного сигнала на третьем выходе 23 второго дешифратора 10 осуществляется обработка информации с удвоенной двухразрядиой сеткой с помощью второго 2 и третьего 3 резервируемых блоков и решение задачи с одинарной разрядной сеткой в первом 1 резервируемом блоке.

Действительно, единичный сигнал с третьего выхода 23 второго дешифратора 10, поступая на третий вход 21 второго блока 12 связи, разрешает прохождение сигнала переноса с первого входа 14 через элемент И 34 и элемент ИЛИ 36 на первый выход 28 второго блока 12 связи, откуда он поступает на вход второго 2 резервируемого блока.

В этом случае информация на вььходе первого 4 мажоритарного блока представляет результат решения самостоятельной задачи, а ин0формация на выходах второго 5 и третьего 6 мажоритарных блоков представляет собой две части результата решения другой задачи.

При формировании единичного сигнала на четвертом выходе 25 второго дешифратора 10

5 обеспечивается обработка информации с удвоенной двухразрядиой сеткой с помощью первого 1 и третьего 3 резервируемых блоков, а второй 2 резервируемый блок может быть использован для решения самостоятельной задачи

0 по обработке информации с одинарной п-рз- .

рядной сеткой.

I

Действительно, единичный сигнал с четвертого выхода 25 второго дешифратора 10 поступает иа четвертьш вход 24 второго блока 12 связи, откуда он поступает на вход элемента И 35 и разрешает прохождение сигнала переноса с первого входа 14 на второй выход 29 второго блока 12 связи. Сигнал с второго выхода 29 второго блока 12 связи поступает на

0 вход первого 1 резервируемого блока.

Информация на выходе первого 4 и третьего 6 мажоритарных блоков представляет в этом случае две части результата переработки информации с удвоенной разрядной сеткой, а

5 информация на выходе второго 5 мажоритарного блока - результат решения другой задачи по обработке информации с одинарной п-разрядной сеткой.

Таким образом, введение второго триггера,

0 второго дешифратора и двух блоков связи дополнительно позволяет:

- осуществлять решение одной задачи по переработке информации в утроенной Зп-разрядной сетке;

5

- осуществлять решение одной задачи по переработке информации с удвоенной 2п-разрядной сеткой и решение другой задачей с одинарной . п-разрядной сеткой. Эти дополни9тельные возможности и определяют повыше е точности переработки информации. ДействителЕ но« точность представлення и переработки ци фовой информации в значительной степени определяется разрядностью (п) резервируемых блрков. Известно, что точность представления, цифровой информация 01феделяется ценой младшего разряда разрядной сетки, т. е. погрешносп величины не превосходит значетш ff Р - основание системы счисления. Прн объе нешш двух или трехразрядных резервируемых блоков в один блок с 2п-или Зп-разрядной сеткой погрешности представления: будут отределяться величинами f Следовательно, выигрыш в точности представления и переработки информации можно оценивать величинами8, Т. е. точность представления величины X в предлагаемом устройстве может быть увеличена либо в , либо в .. « Таким образом, устройство позволяет производить переработку информации с повышенной точностью и получить в зависимости от KOHKpetHbtx условий систему не только пере, производительности и достоверности, но {и А(еременной точности. Ввведение второго регистра, второго дешифратора и двух блоков связи не требует первстройки технологии таких устройств, так как они могут быть выполнены по тЫ1 же технологии и ш той же элементной базе, что и известное устройство.

l,,

ЧГ

t/t.f

/7

/J

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированная система | 1982 |

|

SU1089771A1 |

| Резервированное устройство с перестра-иВАЕМОй СТРуКТуРОй | 1978 |

|

SU805503A2 |

| Резервированное устройство с перестраиваемой структурой | 1981 |

|

SU993502A1 |

| Устройство для оперативной реконфигурации резервированной системы | 1990 |

|

SU1727125A1 |

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

| Резервированная система | 1982 |

|

SU1084802A1 |

| Резервированное устройство для управления электропневмоклапанами | 1989 |

|

SU1647512A1 |

| Многоканальное резервированное устройство | 1983 |

|

SU1111263A1 |

| МАЖОРИТАРНО-РЕЗЕРВИРОВАННЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2015617C1 |

| Резервированное устройство с перестраиваемой структурой | 1975 |

|

SU595887A1 |

1. РЕЗЕРВИЮВАННОЕ УСТРОЙСТВО С ПЕРЕСТРАИВАЕМОЙ СТРУКТУГОЙ, содержащее три резервируемых цифровых вычислительных блока, выходы которых соединены с информационными входами трех мажоритарных блоков, управляющие входы которь1Х подключены к соответствующим выходам первого дещифратора, BXOJV I которого соеданены с выходами первого регистра, отличающе е с я. тем, что, с целью повышения точности увеличения разрядности представления 1№ формации, оно содержит второй регистр, второй дешифратор и два блока связи, первые входы каждого блока связи соединены с выходами переноса второго и третьего резервируемых цифровых вычислительных блоков, вторые входы - с первым выходом второго дешифратора, третьи входы - соответственно с вторым и третьим выходами второго дешифратора, четаертый вход второго блока связи соединен с четвертым выходом второго деишфратора, вход которого подключен к выходу второго регистра, выход первого блока связи подключен к входу переноса первого резервируемого цифрового вычислнтельного блока через элемент ИЛИ, второй вход которого соединен с вторым выxoдo i второго блока .связи, первый выход которого соединен с входом второго резервируемого цифрового вычислительного блока. 2.Устройство по п. 1. о т л и ч а ю щ е е с я тем, что первый блок связи содержит первый и второй элементы И, первые- входы которых соединены с первым входом блока, вторые входы - соответственно с вторым и Третьим входами блока, а вькоды через первый элемент ИЛИ - с вьрсодом блока. 3.Устройство по п. 1, о т л и ч а ю Щ е е с я тем, что второй блок связи содержит третий, четвертый и пятый элементы И, первые входы которых соединены с первым входом блока, вторые входы - соответственно с вторым, третьим и четвертым входами второго блока связи, выходы третьего и четвертого сл элементов И через второй элемент ИЛИ пода ключены к первому выходу блока, а выход пятого элемента И - к второму выходу бло00 ЕХ) ка.

.2

2B

i9

J

55

IB

54

21

2

/.

55

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Резервированное устройство с управляемой структурой | 1973 |

|

SU476565A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Резервированное устройство с перестраиваемой структурой | 1975 |

|

SU595887A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-11-23—Публикация

1982-05-03—Подача