третьей выходной шиной блока управления, вторые входы третьих и четвертых элементов И каждого разряда соединены 9 соответствующими выходными шинами блока управления, третьи входы четвертых элементов И в каждом разряде соединены с выходами первых элементов ИЛИ, выход блока свертки по модулю 2 соединен с ftepвой входной шиной блока управления, выходы элементов совпадения соединены с соответствующими входными шинами блока управления.

2. Устройство по п. 1, о т л и чающе.еся тем, что блок управления содержит генератор импульсов, уформирователь импульсов, распределитель сигналов, третий триггер, третий элемент ИЛИ, шестой, седьмой и восьмой элементы И, третий и четвертый инверторы, второй и третий элементы задержки, выход генератора импульсов соединен с первым входом шестого элемента И, выход которого соединен с первым входом распределителя сигналов и входо второго элемента задержки, а второй

вход - с выходом третьего триггера, вход сброса которого соединен со вторым входом распределигеля сигналов и вькодом третьего инвертора, а вход установки-- с выходом седьмого элемента И, первый вход которого соединен с выходом формирователя импульсов, а второй вход с выходом четвертого инвертора, выход второго элемента задержки соединен с первым выходом блока и со вторым входом третьего элемента задержки, выход которого соединен с первым входом восьмого элемента И, выход которого соединен со вторым выходом блока, вход четвертого инвертора соединен с выходом третьего элемента ИЛИ и с третьим выходом блока, выходы распределителя Ьигналов соединены с соответствующими остальными выходами блока, а вход формирователя импульсов соединен со входом третьего инвертора, вторым входом восьмого элемента И и с первым входом блока, входы третьего элемента ИЛИ соединены с соответствующими остальными входами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное резервированное устройство | 1984 |

|

SU1164712A1 |

| Многоканальное резервированное устройство | 1981 |

|

SU991628A1 |

| Многоканальное резервированное устройство | 1982 |

|

SU1034209A1 |

| Резервированная система | 1988 |

|

SU1584137A1 |

| Резервированное устройство | 1983 |

|

SU1124459A1 |

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

| Резервированное устройство | 1982 |

|

SU1121795A1 |

| Резервированное устройство | 1991 |

|

SU1830575A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1368923A1 |

| Устройство для мажоритарного включения резервируемых логических блоков | 1985 |

|

SU1325727A1 |

1. МНОГОКАНАЛЬНОЕ РЕЗЕРВИРОВАННОЕ УСТРОЙСТВО, содержащее в каждом разряде по числу каналов элементы неразнозначности, первые триггеры и резервируемые блоки, выХод каждого из которых соединен в Каждом разряде с соответствующим информационным входом мажоритарного элемента и с первым входом элемента неравнозначности, второй вход которого подключен к выходу резервируемого блока последующего канала, выход мажоритарного элемента каждого разряда соединен с первым входом первого элемента И, с соответствующим входом блока свертки по модулю 2 и со входом первого инвертора, выход которого соединен с первым входом второго элемента И, второй вход которого соединен через второй инвертор со вторым входом первого элемента И, с выходом элемента совпадения, первый вход которого соединен с выходом блока свертки и по модулю 2, а остальные входы с соответствующими входами первого элемента ИЛИ и с выходами соответствующих первых триггеров, входы сброса которых соединены с шиной сброса, выходы первого и второго элементов И каждого разряда подключены к соответствующим входам второго элемента ИЛИ, выход которого соединен с соответствующей первой выходной шиной устройства, вторая выходная шина которого соединена с выходом первого элемента ИЛИ, отличающееся тем, что, :с целью уменьшения моп1ности, потребляемой устройством, оно содержит блок управления и в каждом разряде первый элемент задержки, ключ, второй триггер, третий и четвертый элементы И и в каждом канале - пятый элемент И, выход которого соединен § с входом установки соответствующего первого триггера, его первый (Л вход - с выходом соответствующего элемента неравнозначности, а второй вход в каждом разряде - с управляющим входом мажоритарного элеftMh Ч. мента и выходом первого элемента задержки, вход которого соединен с управляющим входом ключа и выходом второго триггера, первые входы установки и сброса которого соединены соответственно с выходами трею тьего и четвертого элементов И, втоО) рой вход сброса - с шиной сброса, Юо шины питания резервируемых блоков каждого канала, начиная со второго, соединены в каждом разряде через ключ с шиной питания устройства, Первые входы третьих элементов И всех разрядов соединены с первой выходной шиной блока управления, первые входы четвертых элементов И всех разрядов соединены со второй выходной шиной блока управления, вторые входы установки вторых триггеров всех разрядов соединены с

Изобретение относится к вычисл тельной технике и может быть испол зовано в управляющих вычислительнь машинах повышенной надежности. Известно устройство включения резервированного оборудования, в котором для повьш1ения надежности применяется трехкратное резервирование с подключением резервируемых блоков к мажоритарному элементу. Устройство содержит элемент ИЛИ и в каждом канале резервируемый блок подключенный через мажоритарный элемент к соответствующему ключу, элемент неравнозначности, элемент триггер и элемент ИЖ, причем выход резервируемого блока каждого канала соединен с первым входом элемента неравнозначности, второй вход которого подключен к выходу резервируемого блока (vT + 1)-ro канала, а третий вход - к выходу эле мента И, первый вход которого соединен с соответствующим входом элемента И (h + 1)-ro канала и выходом триггера (п + 1)-го канала, а второй вход - с выходом триггера (л+1)-го канала и соответствующим входом элемента И (ri + 1)-ro канала, при йтом выход элемента неравнозначности каждого канала подключен ко входу триггера, другой вход которого соединен с шиной сброса, а выход через элемент ИЛИ - с входом соответствующего ключа и соответствующим входом общего элемента ИЛИ, выход которого подключен к общей шине. Другие входы элементов ИЛИ всех каналов соединены с управляющими шинами t11. Однако это устройство недостаточно надежно вследствие того, что при двух отказах резервируемых блоков устройство выходит из строя. Наиболее близким к изобретению является многоканальное резервированное устройство, содержащее в каждом разряде по числу каналов элементы неравнозначности, первые триггеры и резервируемые блоки, выход каждого из которых соединен в каждом разряде с соответствующим информационным входом мажоритарного элемента и с первым входом элемента неравнозначности, второй вход которго подключен к выходу резервируемог блока последующего канала, а выход ко входу триггера, выход мажоритарного элемента каждого рязряда соединен с первым входом первого элемента И, с соответствующим входом блока свертки по МОДУЛЮ 2 и с входо первого инвертора, выход которого соединен с первым входом второго элемента И, второй вход которого соединен через второй инвертор со вторым входом первого элемента И и с выходом элемента совпадения, первый вход которого соединен с выходом блока свертки по модулю 2, а остальные входы - с соответствующими входами первого элемента ИЛИ и с выходами соответствующих первых триггеров, входы сброса которых соединены с шиной сброса, выходы первого и второго элементов И каждого раз1ряда подключены к соответствующим входам второго элемента ИЛИ, выход которого соединен с соответствующей первой выходной шиной устройства, вторая выходная шина которого соединена с вь1х од ом первого элемента ИЛИ. В данном устройстве повышение надежности обеспечивается за счет осуществления контроля информации, вьявления ошибки, возникающей в случае появления отказов двух резервируемых блоков в одном из разрядов, и коррекции ошибок С23.

Недостатком устройства является большое, потребление мощности питания

Цель изобретения - уменьшение мощности, потребляемой устройством.

Поставленная цель достигается тем, что в многоканальное резервированное устройство, содержащее в каждом разряде по числу каналов элементы неравнозначности, первые триггеры и резервируемые блоки, выход каждого из которых соединён в каждом разряде с соответствующим информационным входом мажоритарного элемента и с первым входом элемента неравнозначности, второй вход которого подключен к выходу резерви. руемого блока последующего канала, выход мажоритарного элемента каждого разряда соединен с первым входом первого элемента И, с соответствуюй(им входом блока свертки по модулю 2 и со входом первого инвертора, выход которого соединен с первым входом второго элемента И, второй вход которого соединен через второй инвертор со вторым входом первого элемента И, с выходом элемента совпадения, первый вход которого соединен с выходом блока свертки по модулю 2, а остальныеВХОДЫ - с соответствующими входами первого элемента ИЛИ и с выходами соответствующих первых триггеров, входы сброса которых соединены с шиной сброса,

0 выходы первого и второго элементов И каждого разряда подключены к соответствующим входам второго элемента ИЛИ, выход которого соединен с соответствующей первой выходной

шиной устройства, вторая выходная шина которого соединена с выходом первого,элемента ИЛИ, введены блок управления, и в каждый разряд - первый элемент задержки, ключ, второй

0 триггер, третий и четвертый элементы И и в каждый канал - пятый элемент И, выход которого соединен с входом установки соответствующего первого триггера, его первый

5 вход - с выходом, соответствующего элемента неравнозначности, а второй вход в каждом разряде - с упранляющшвходом мажоритарного элемента и выходом первого элемента задержки,

0 вход которого соединен с управляющим входом ключа и выходом второго триггера, первые входы установки и сброса которого соединены соответственно с выходами третьего и четвертого

5 элементов И, второй вход сброса с шиной сброса, шины питания резервируемых блоков каждого канала, начиная со второго, соединены в каждом разряде через ключ с шиной пита0 ния устройства, первые входы третьих элементов И всех разрядов соединены с первой выходной шиной блока управления первые входы четвертых элементов И всех разрядов соединены со

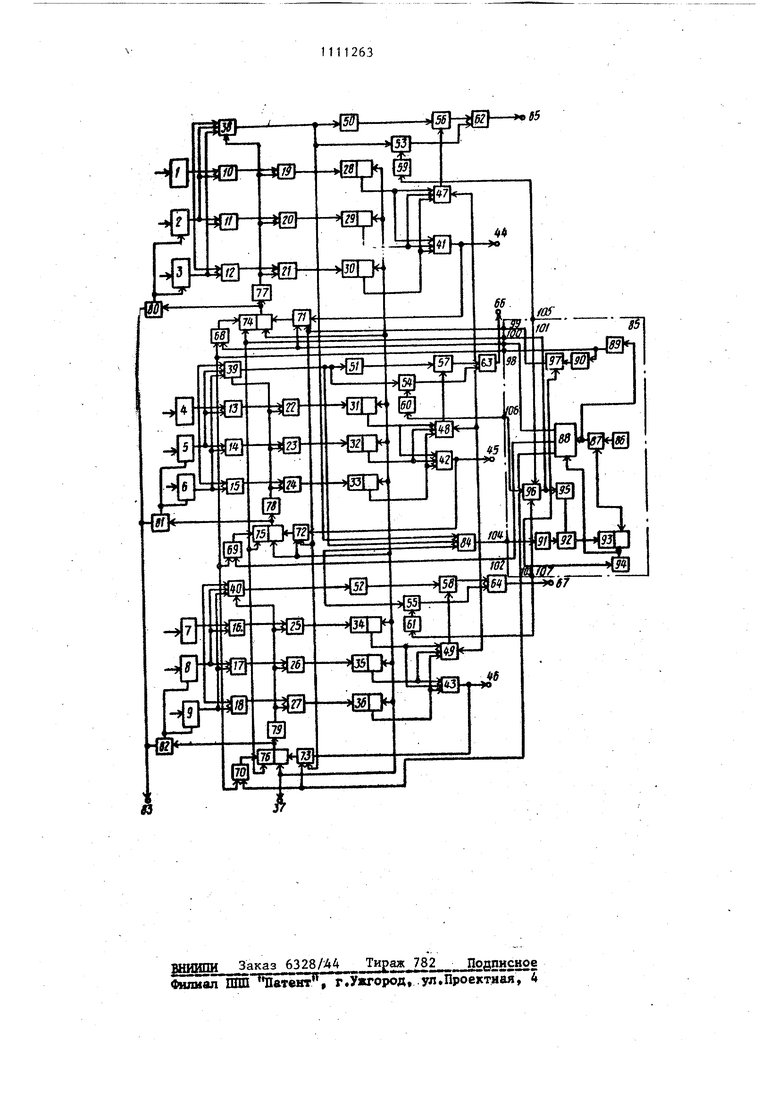

5 второй выходной шиной блока управления, вторые входы установки вторых триггеров всех разрядов соединены с третьей выходной шиной блока управления, вторые входы третьих и четвертых элементов И каждого разря да соединены с соответствующими выходными шинами блока управления, третьи входы четвертых элементов И в каждом разряде соединены с выхода ми первых элементов ИЛИ, выход блок свертки по модулю 2 соединены с первой входной шиной блока управления, выходы элементов совпадения соединены с соответствующими входными шинами блока управления. Блок управления содержит генератор импульсов, формирователь импуль сов, распределитель сигналов, третий триггер, третий элемент ИЛИ, ше той, седьмой и восьмой элементы И, третий и четвертый инверторы, второ и третий элементы задержки, выход генератора импульсов соединен с пер вым входом шестого элемента И, выхо которого соединен с первым входом распределителя сигналов и входом вт рого элемента задержки, а второй вход - с выходом третьего триггера, вход сброса которого соединен со вторым входом распределителя сигналов и выходом третьего инвертора, а вход установки - с выходом седьмо го элемента И, первый вход которого соединен с выходом формирователя импульсов, а второй вход - с выходо четвертого инвертора, выход второго элемента ..задержки соединен с первым выходом блока и со входом третьего элемента задержки, выход которого соединен с первым входом восьмого элемента И, выход которого соединен со вторым выходом блока, вход четвертого инвертора соединен с выходом третьего элемента ИЛИ не третьим выходом блока, выходы распределителя сигналов соединены с соответствующими остальными выходам блока, а вход формирователя импульсов соединен со входом третьего инвертора, вторым входом восьмого элемента И и с первым входом блока, входы третьего элемента ИЛИ соединены с соответствующими .остальными входами блока. Многоканальное резервированное устройство содержит в каждом разряде по числу каналов резервируемые блока 1-3 (4-6, 7-9), элементы неравнозначности 10-12 (13-15, 16-18) пятые элементы И 19-21 (22-24, 25-2 и первые триггеры 28-30 (31-33, 34-36), входы сброса которых подключены к шине сброса 37, а также мажоритарный элемент 38 (39 40), первый элемент ИЛИ 41 (42,43), выход которого соединен со второй выходной шиной устройства 44 (45,46), элемент совпадения 47 (48,49), первый инвертор 50 (51,52), первый элемент И 53 (54,55), второй элемент И 56 (57,58), вторО|й инвертор 59 (60,61), второй элемент ИЛИ 62 (63,64) выход которого соединен с первой выходной шиной устройства 65 (66, 67), третий элемент И 68 (69,70), четвертый элемент И 71 (72,73), второй триггер 74 (75, 76), первый элемент задержки 77 (78,79), ключ 80 (81,82), через который шины питания резервируемых блоков 2,3 (5,6; 8,9) соединены с шиной питания устройства 83. Кроме того, устройство содержит блок 84 свертки по модулю 2 и блок управления 85, состоящий из генератора импульсов 86, шестого элемента И 87, распределителя сигналов 88 (реализованного, например, в виде регистра сдвига с начальной установкой состояния 1000), второго 89 и третьего 90 элементов задержки, формирователя импульсов 91, седьмого элемента И 92, третьего триггера 93, третьего 94 и четвертого 95 инверторов, третьего элемента ИЛИ 96 и восьмого элемента И 97, причем выход второго элемента задержки 89 соединен с первым выходом 98 блока управления 85 и со входом третьего элемента задержки 90, выход которого соединен с первым входом восьмого элемента И 97, выход которого соединен со вторым выходом 99 блока управления 85. Вход четвертого инвертора 95 соединен с выходом третьего элемента ИЛИ 96 и с третьим выходом 100 блока управления 85. Первый, второй и третий вьпсоды. распределителя сигналов 88 соединены соответственно с выходами 101-103 блока управления 85. Вход формирователя импульсов 91 соединен с входом третьего инвертора 94, вторым входом восьмого элемента И 97 и с первым входом 104 блока управления 85, входы третьего элемента ИЛИ 95 соединены с соответствующими входами 105-107 блока управления 85. Выход формирователя импульсов 91 соединен с первым входом седьмого элемента И 92, второй вход которого подклю7

чен к выходу четвертого инвертора 9 а выход - ко входу установки третьего триггера 93. Вход сброса триггера 93 соединен с выходом третьего инвертора 94 и вторым входом рас- пределителя сигналов 88, а выход подключен ко второму входу шестого элемента И 87. В казкдом разряде резервируемые блоки 1-3 (4-6, 7-9) подключены к первым и вторым входам элементов неравнозначности 10-12 (13-15, 16-18) и к информационным входам мажоритарного элемента 38 (39-40). Выход элементов неравнозначности 10-12 (13-15, 16-18) соединены с первъми входами пятых элементов И 19-21 (22-24, 25-27), выходы которых подключены ко входам установки триггеров 28-30 (31-33, 3436), выходы которых подключены к соответствующим.входам первого элемента ИЛИ 41 (42,43) и первым трем входам элемента совпадения . 47 (48,49). Выход мажоритарного элемента 38 (39,40) подключен через первый инвертор 50 (51,52) к первом входу второго элемента И 56 (57, 58) и непосредственно к первому входу первого элемента И 5.3 (54,55) Выход элемента совпадения 47 (48, 49) соединен через второй инвертор 59 (60,61) со вторым входом первого элемента И 53 (54,55), со вто.рым входом второго элемента И 56 (57,58) и со входом 106 (106,107) блока управления 85. Выходы первого 53 (54,55) и второго 56 (57,58) элементов И подключены ко входам второго элемента ИЛИ 62 (63,64). Управляющий вход мажоритарного элемента 38 (39,40) соединен со вторыми входами пятых элементов И 19-21 (22-24, 25-27) и выходом первого элемента задержки 77 (78,79), вход которого подключен к управляющему входу ключа 80 (.81,82) и к выходу второго триггера 74 (75,76). Первый вход установки второго триггера 74 (75,76) соединен с выходом третьего элемента И 68 (69,70), первьпЧ вход сброса - с выходом четвертого элемента И 71 (72,73), вторые входы установки вторых триггеров 74-76 соединены с третьим выходом 100 блока управления 85. Первые вхсГды третьих элементов И 68-70 соединены между собой и с первым выходом 98 блока управления 85, а первые входы четверть1х элементов И 71-73 соеди 638

нены между собой и со вторым выходом 99 блока управления 85. Вторые входы третьего 68 (69,70) и четвертого 71 () элементов И соединены между собой и с выходом 101 (102, 103) блока управления 85, а третий вход четвертого элемента И 71 (72,73) соединен с выходом первого элемента ИЛИ 41 (42,43) Входы

О блока 84 свертки по модулю 2 подключены к выходам соответствующих мажоритарных элементов 38-40, а выход соединен с четвертьми входами элементов совпадения 47-49 и первым

5 входом 104 блока управления 85.

Устройство работает следующим образом.

Z начальный момент все триггеры 28-36, 74-76 и 93 находятся в сбро0 шенном состоянии, в которое они

предварительно устанавливаются сигналом с шины сброса 37. При этом сигналы с выходов триггеров.74-76 закрывают элементы И 19-27 и ключи

5 80-82, в результате чего отключаются от питания резервируемые блоки 2,3,5,6,8,9 и сигналы неравенства, которые могут возникнуть на выходах элементов неравнозначности 10 0 18, не проходят через закрытые элементы И 19-27 на входы триггеров 28-36. Кроме того,мажоритар цые элементы 38-40 по сигналам с выходов соответствующих триггеров 74-76 включаются таким образом,

что значение сигналов на их выходах зависит толькоот значения сигнала на вьтходе соответствующего одного резервируемого блока 1,4,7. На выходах первых элементов ИЛИ 41-43

соединенных с выходными шинами 44-46 вьщаются сигналы О, свидетельствующие об отсутствии ошибок в разрядах. Одновременно на выходе блока 84 свертки по модулю 2 вьдается

сигнал О, свидетельствующий р оответствии значения разряда четности

с четностью- информационных разрядов, т.е. об отсутствии ошибок на выходах

мажоритарных элементов 38-40.

Этот сигнал поступает на четвертые входы элементов совпадения 47-49, на выходе которых образуется сигнал О, который, проходя через инверторы 59-61, открывает элементы И 5355 и информация с выходов мажоритарных элементов 38-40 через открытые элементы И 53-55 и через элементы ИЛИ 62-64 поступает на выходные шины устройства 65-67. При отказе одного из резервируемых блоков, например, блока 4, с выхода мажоритарного элемента 39 на вход блока 84 свертки по модулю 2 поступает неверная информация, в результате чего на вмходе этого блока устанавливается сигнал 1. Это переключение значения сигнала на выходе блока 84 с О на 1 приводит к формированию импульса на выходе формирователя импульсов 91. Импульсный сигнал с выхода формирователя импульсов 91, пройдя через открытый элемент И 92, опрокидывается тригге 93 в состояние, при котором открывается элемент И 87, и импульсы с выхода генератора импульсов 86 начинают поступать в распределитель сигналов 88 и на вход элемента задержки 89. В результате поступления на вход распределителя сигналов 88 первого импульса на его первом выходе появляется сигнал 1, поступающий на входы элементов И 68 и 71. Через время задержки, несколько большее, чем время установки разрешающего сигнала на определенном выходе распределителя 88, с выходов элемента задержки 89 на первый вход элемента И 68 поступает импульс, 30 на

который, пройдя на первый вход установки триггера 74, устанавливает его в состояние, при котором открывается ключ 80 и на резервируемые блоки 2 и 3 подается питание. Кроме того, сигнал разрешения через время задержки, достаточное для срабатывания резервируемых блоков после включения питания, обеспечиваемое элементов задержки 77, открывает элементы И 19-21 и включает мажоритарный элемент 38 в режим мажорирвания. Так как блоки 1-3 функционируют нормально, то на выходе блока 84 свертки по модулю 2 изменения сигнала не происходит и элемент И 97 остается . В результате этого через время задержки, достаточное для срабатывания блока. свертки 84 по модулю 2, импульс с выхода элемента задержки 90 проходит через открытые элементы И 97 и 71 и сбрасывает триггер 74 в начальное состояние. При этом закрывается ключ 80, элементы И 19 - 21 и мажоритарный эле38 проходят в начальный режим. 1

свертки по модулю 2 образуется сигнал О, который закрывает элемент И 97, В результате этого импульс с выхода элемента задержки 9Э не проходит

на вход элемента И 72, и триггер 75 сохраняет состояние, при котором подается питание на резервируемые блоки 5 и 6. Одновременно с этим сигнал О с выхода блока свертки 84

по модулю 2, пройдя через инвертор 94, сбрасывает триггер 93 в состояние, при котором закрывается элемент И 87, и сбрасывает распределитель сигналов 88 в первоначальное состояние.

Если при дальнейшей работе произойдет отказ еще одного из резервируемых блоков, например блока 7, то устройство будет работать аналогично тому, что было рассмотрено до отказа блока 4, последовательно проверяя работоспособность разрядов.

Однако в этом случае сброса триггера 75 не произойдет, так как сигнал Ощибка с выхода- элемента ИЛИ 42 закрывает элемент И 72. Окончательным состояние устройства в этом случае будет установка триггеров 75 и 76 в положение, при котором от3 ° Второй импульс с генератора импульсов 86, пройдя открытый элемент И 87 переводит распределитель сигналов 88 в следующее состояние, при котором сигнал разрешения появится на выходе, соединенном с выходной шиной 102 блока управления 85 и откроет элементы И 69 и 72. Кроме того, импульс с выхрда элемента И 87 поступает на вход элемента задержки 89 и через время задержки, пройдя . через открытый элемент И 69, устаКс вливает триггер 75 в состояние, при котором открывается ключ 81, и через время, обеспечиваемое элементом задержки 78, открываются элементы И 22-24, и мажоритарный элемент. 39 переходит в состояние мажорирования. В результате этого на выходе элементов неравнозначности 13 и 15 появляются сигналы несравнения, так как блок 4 отказал. Эти сигналы устанавливают триггеры 31 и 33 в состояние 1 , в результате чего на выходе элемента ИЛН 42. появляется сигнал 1, свидетельствующий о наличии отказа в данном разряде. Кроме того, сигнал на выходе мажоритарного элемента 39 изменяется Верный и на выходе блока 84 крыты ключи 81 и 82 и питание подается на резервируемые блоки 1-9. При возникновении отказа второго из резервируемых блоков в разряде, Например блока 5, с выхода элемента неравнозначности 14 выдается сигнал 1, который, пройдя через открытый элемент И 28, устанавливает триггер 32 в состояние 1. Таким образом, все триггеры 31-33 оказывак1тся в состоянии 1. Кроме того, отказ двух резервируемых бг:эков 4 и 5 приводит к появлению ошибочной информации на выходе мажоритарного элемента 39, в результате чего на выходе блока 84 свертки по модулю 2 устанавливается сигнал 1. Этот сигнал поступает на четвертые входы элементов совпадения 47-49, на входы формирователя импульсов 91 и элемента И 97. Так как на всех четьфех входах элемента совпадения 48 оказывается сигнал 1 то на его выходе также формируется сигнал 1, который открывает элемент И 57, при этом закрывается эле мент И 54. Ошибочная информация, из мененная на правильную с помощью инвертора 51, с выхода мажоритарного элемента 39 проходит через эле мент 57. Таким образом происходит исправ ление ошибки и на выходной шине 66 информация будет правильной при отказе двух резервируемых блоков в одном разряде. Кроме того, сигнал с выхода элемента совпадения 48 проходит через элемент ИЛИ 96 и второй инвертор 95 на вход элемента И 92 и закрывае его. В результате этого импульс с выхода формирователя импульсов 91 не проходит на вход триггера 93. Си нал 1 с выхода элемента ИЛИ 96 поступает на вторые входы установки вторых триггеров 74-76, в результате чего они устанавливаются в состояние, при котором все резервируемые блоки 1-9 оказываются включенными. Уменьшение потребляемой мощности питания в предлагаемом устройстве по сравнению с прототипом при сохранении аналогичных исправляющих ошибок свойств обеспечивается за счет того, что в начальном состоянии питание подается только на один резервируе- мый блок из м в каждом разряде, а в дальнейтпем питание на все резервируемые блоки разряда подается только при появлении отказа какого-либо резервируемого блока данного разряда или двух отказах в любом разряде. Запоминающее устройство (ЗУ) на интегральных схемах на основе структуры прототипа с числом каналов резервирования, равным трем, характеризуется потребляемой мощностью питания, равной приблизительно 46 Вт, а реализация ЗУ на основе изобретени ; обеспечивает снижение потребляемой МОПЦ1ОСТИ до 16 Вт при аналогичных остальных параметрах ЗУ. Появление отказа в одном из разрядов предлагаемого устройства приводит к увеличению потребляемой мощности приблизительно на 2 Вт. В функциональном модуле ЗУ с объемом памяти 16 К слов, разрядност ью 16, вероятностью безотказной работы Р (t) 0,8 за 1000 ч работы, в предлагаемом устройстве потребляемая мощность питания при трехкратном резервировании приблизительно в 3 раза меньше, чем в прототипе.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № 754721, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3316761/24, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1984-08-30—Публикация

1983-01-06—Подача