1П

И-и|Г11: стение относится к нмчясли- тельной технике и может быть использовано для аппаратной реализации операций вычисления степенной функции с показателем 2 и 1/2 в универсальных и спепиализированных вычислителях ,

Цель изобретения - повышение точности при воспроизведении cтeпe п oй функции с показателем 1/2.

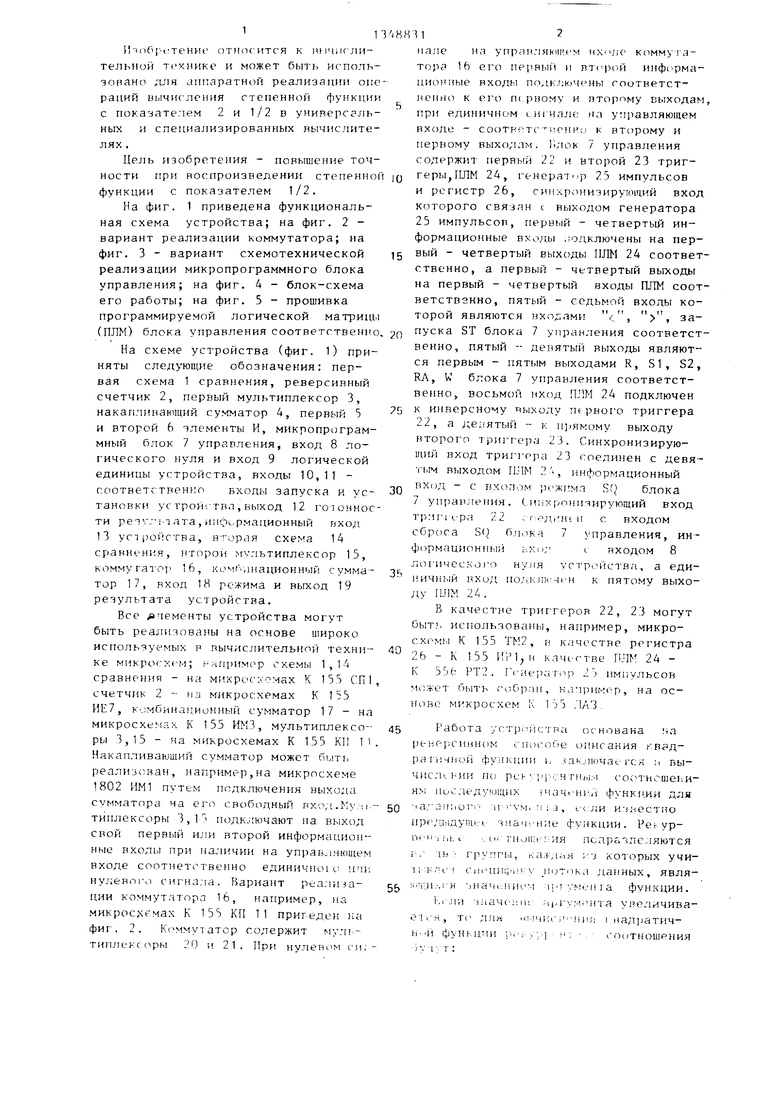

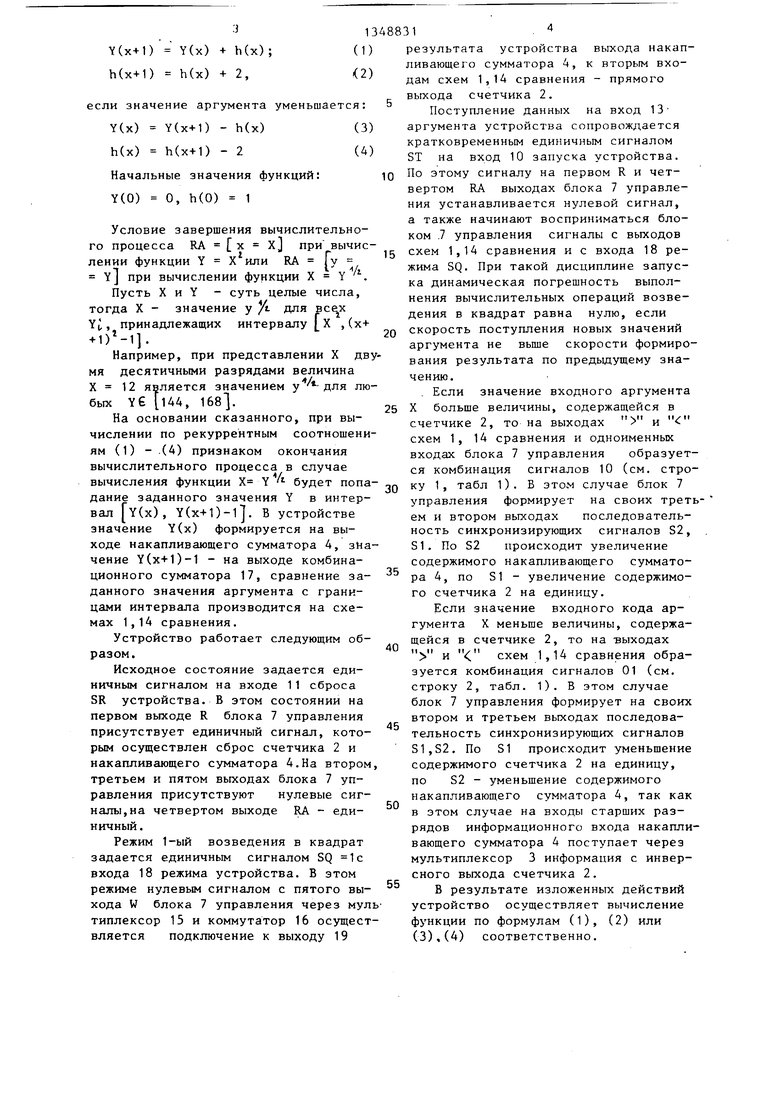

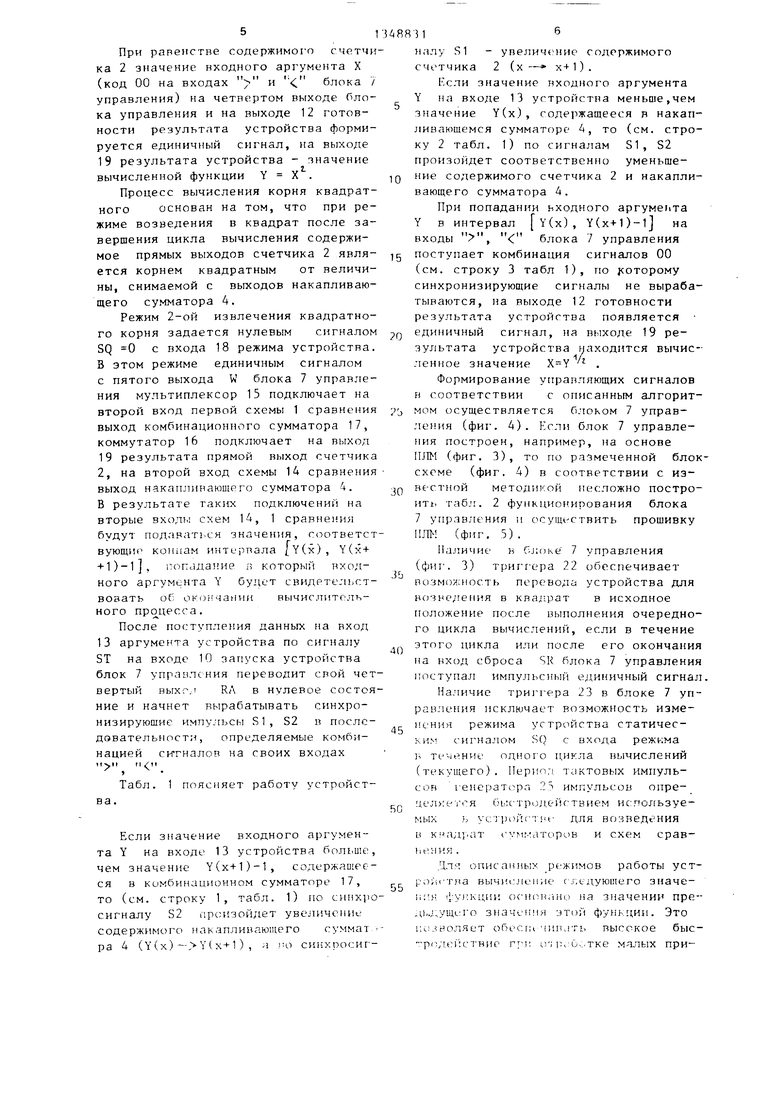

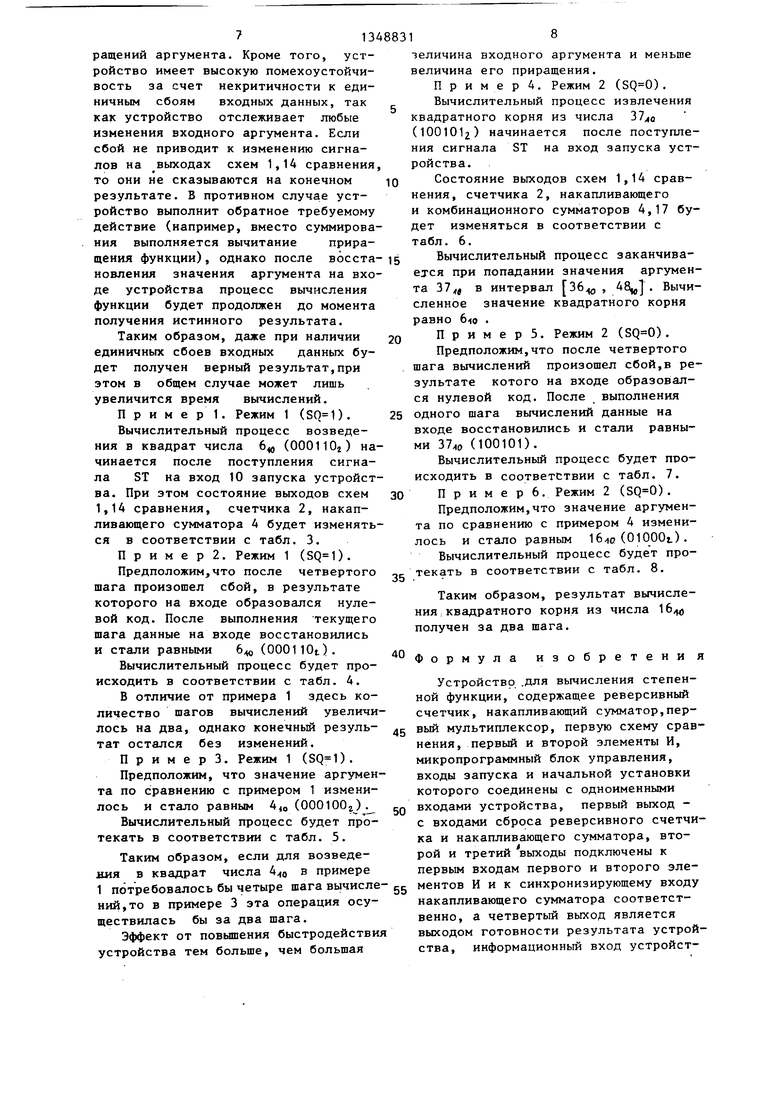

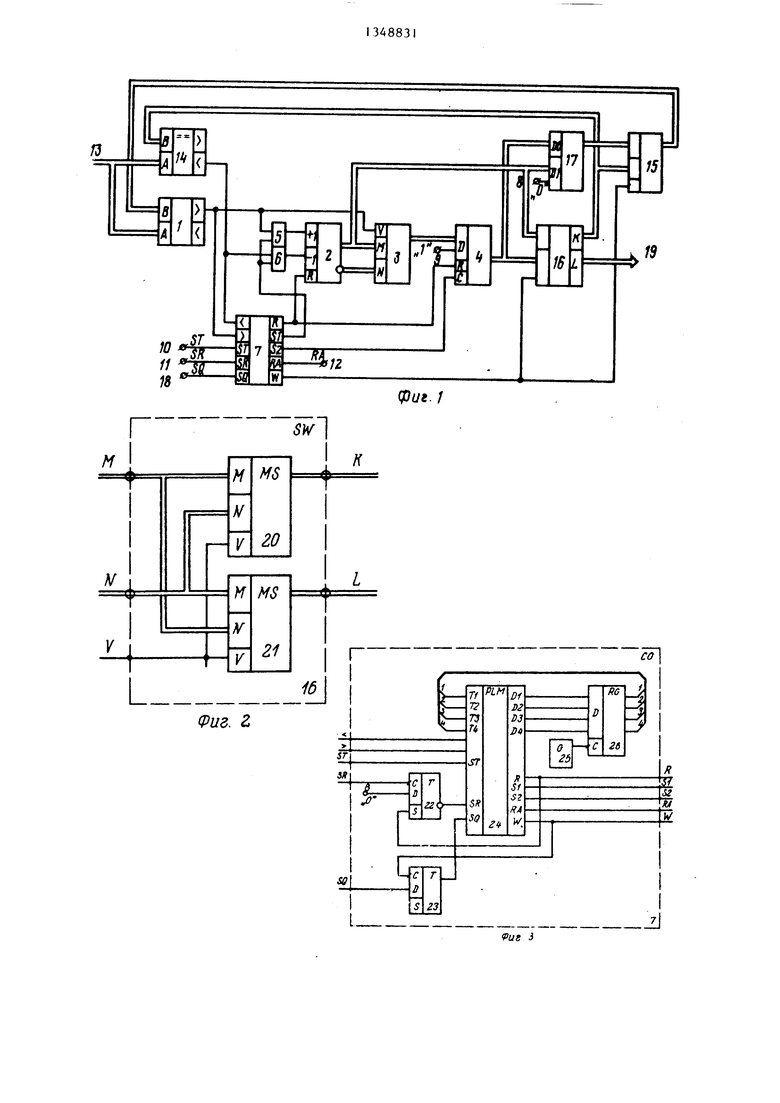

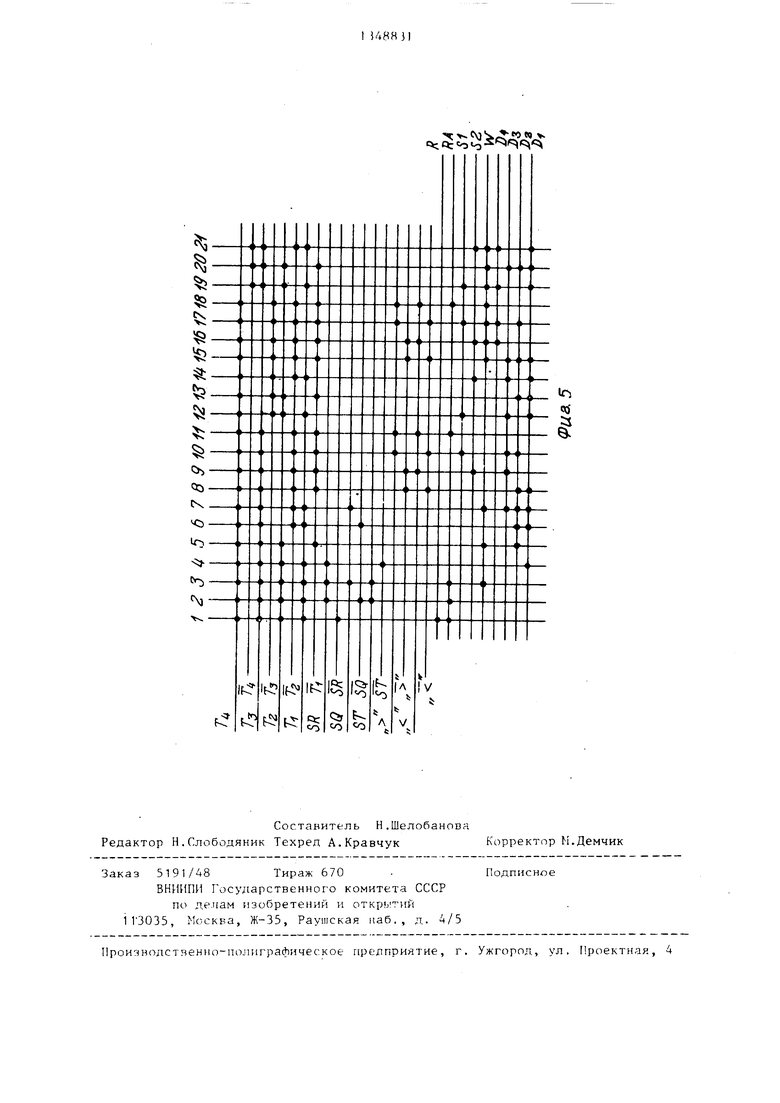

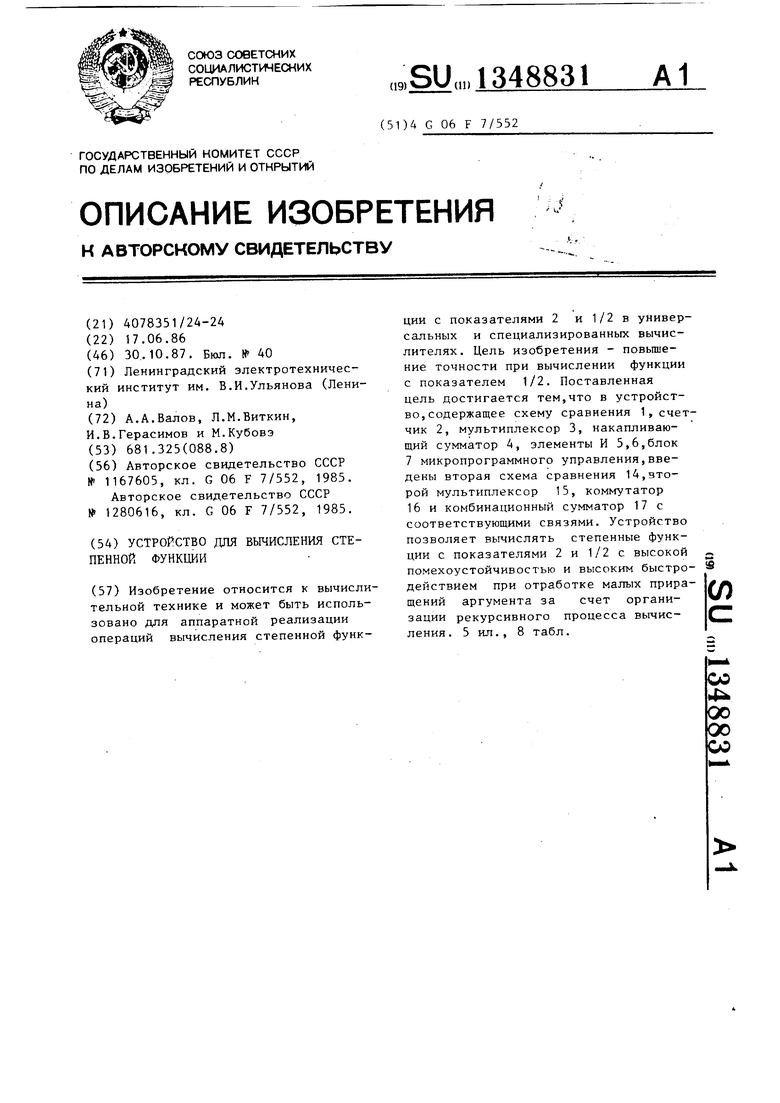

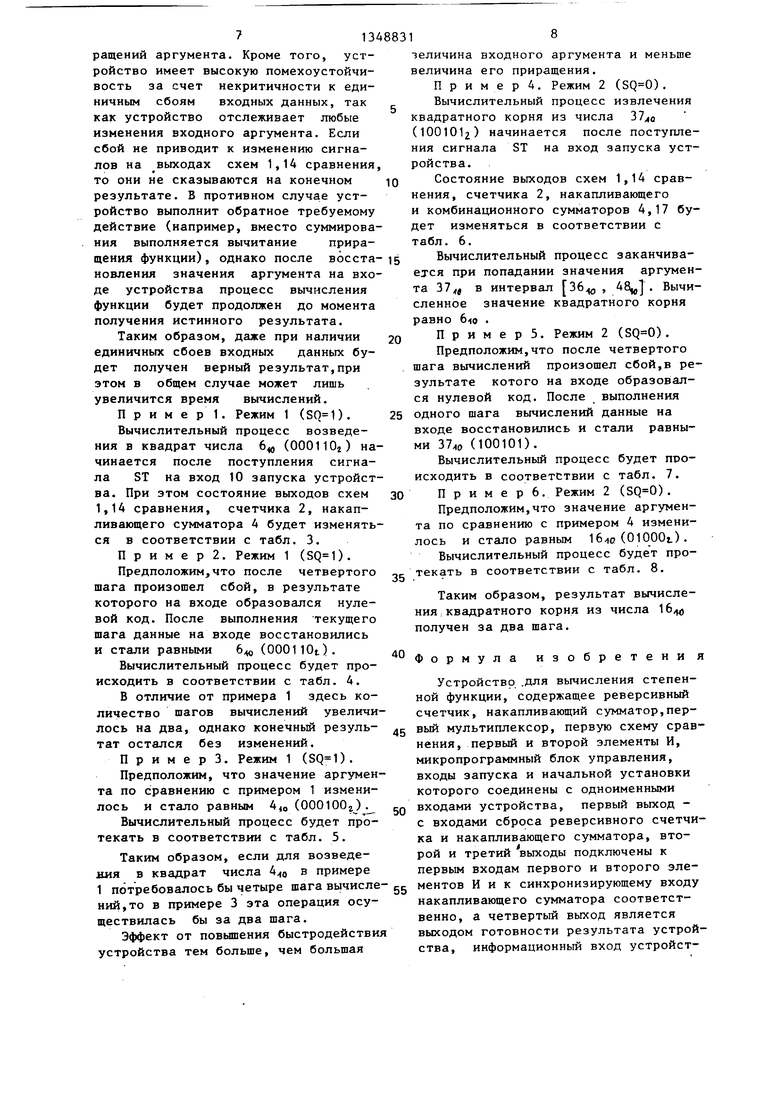

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - вариант реализации коммутатора; на фиг. 3 - вариант схемотехнической реализации микропрограммного блока управления; на фиг. 4 - блок-схема его работы; на фиг. 5 - прошивка программируемой логической матриць (ПЛМ) блока управления соответственно

На схеме устройства (фиг. 1) приняты следующие обозначения: первая схема 1 сравнения, реверсивный счетчик 2, первыр мультиплексор 3, накапливан1щий сумматор 4, первый 5 и второй 6 -элементы И, микропрограммный блок 7 управления, вход 8 логического нуля и вход 9 логической единицы устройства, входы 10, 11 - соответственно входы запуска и ус- тановки ус тройства,выход 12 готовности рету, ата , информационный вход 13 уст poitcTBa, вторая схема 14 сравнения, второй му;1тзтиплексор 15, коммутатор 16, .,lнaциoнный сумма- тор 17, вход 18 режима и выход 19 результата устройства.

Все (вчементы устройства могут быть реализованы на основе широко используемых Р вычислительной техни- ке микросхем; ..члримср схемы 1,14 сравнения - на микросхемах К 155 СП счетчик 2 - на микрос:хемах К 155 ИЕ7, К :мбина1 ионныГ1 сумматор 17 - на микросхемах К 155 ИМЗ, мультиплексо-- ры 3,15 - на микросхемах К 155 KI 1 1 Накапливающий сумматор может быть реализован, например,на микросхеме 1802 ИМ1 путем подключения выхода с мматора на его свобстдный вход.Ку о.- типлексоры 3,15 подк.; ючают на выход свой первый или второй информащюн-- ные входы при на;шчии на yпpaFjJiнющeм входе соответственно единичжп о ЦПУ. нулевого сигнала. Вариант реализа- ции коммутатора 16, например, на микросхемах К 155 КП 11 пригеден на фиг. 2. К мму1атор содержит му:гт,- типлексоры 20 и 21. При нулевом си;112

пале ил упраи.пяюп ем ихг лс комму га- тора 1Ь его Г1Р 1НЫГ1 и втс|)ой инфгфма- циоиные входы полк.г;юч(ны гоответст- ncruid к его П(.р1юму и пторпму выходам при единичрк. М Lurnajif; на утптавляющем входе - cooTPi TC iiriiR;. к второму и первому выходам. li;ioK 7 угтравления содержит пернь й 22 н второй 23 триггеры,11ЛМ 24, генератор 25 импульсов и регистр 26, сиихр;1ни:зирую1ций вход которого связан с выходом генератора

25импульсов, первый - четвертый информационные входы .юдключены на первый - четвертый выходы ИЛМ 24 соответственно, а первый - четвертый выходы на первый - четвертый входы ПЛМ соответственно, пятый - седьмой входы которой являются 1 хпдамР с, , запуска ST блока 7 управления соответственно, пятый - девятый выходы являются первым - пятым выходами R, S1, S2, RA, W блока 7 управления соответственно), восьмой вход ПЛМ 24 подключен

к инверсному яыходу не рвого триггера 22, а девятый - к njjHMOMy выходу второго триггера 23. Синхронизирующий вход трип-ера 23 соединен с девя т(,1м выходом ПЛМ 2, информационный вход - с вхопом режима SO блока 7 управления, t и ::-; ;оничирующий вход трмпх-ра 22 . .nt и с входом сброса S(J б.покч 7 управления, информационны 1;Х.(); t входом 8 логического нуля устройствгч, а единичный иход no/iKji/c icH к пятому выходу ПЛМ 24.

В качестве тригтеров 22, 23 могут быть использованы, например, микро- схг-мы К 155 ТМ2, Fi качестве регистра

26 К 155 И; 1;,н качестве ГО1 24 - К 556 РТ2 . оператор 25 импульсов может б1,1ть ri)6pan, качрикг-р, на основе мг кросхем К 155 ЛАЗ,

Г абота yc rpoj iCTPa основана ;;а pei-iP{;cH)(HoM ci iot oOe описания рагичпо i, заключав-1ч;к :. вы- ЧИСЛ1-ьии по РСЬ Р1: снт1и,1.ч с оотнсшег.и- ям Последующих о . функции для 4a; aii;ioi ;1Г м, п;л, ч 1;и ичьестпо прг-;;1;1ду111(:ч- змач : мие функции. Реьур- ги П , i.hi -. (11 I4ioii;i ;:мя псл,ра )Деляются ;/ группы, Ka. ко1чэрых учи- п-вло . i i;iToKa данных, явля- si i ,H;-.( H )Нач1;П1||..1 li ivMenia функции.

1-.1 ли ч;и-чс:;1и .4)..I v:-itЛ i T у1 еличива- e ii ,4. То дли чмчсо i I иад,ратич- 1-1-й функции ;-.т;.;-1 : соотношения V Ч т :

Y(x-H) Y(x) + h(x); h(x-t-l) h(x) + 2,

если значение аргумента уменьшается: 5 Y(x) Y(x4.1) - h(x)(3)

h(x) h(x+1) - 2(4)

Начальные значения функций: ю Y(0) О, h(0) 1

l, принадлежащих интервалу

х .

(x-tУсловие завершения вычислительного процесса RA х Xj при вычислении функции Y X или RA 1у Y при вычислении функции X Y .

Пусть X и Y - суть целые числа, тогда X - значение у /L для всех I, прин -И)-.

Например, при представлении X двмя десятичными разрядами величина X 12 является значением любых YG l44, 168.

На основании сказанного, при вычислении по рекуррентным соотношениям (1) -.(4) признаком окончания вычислительного процесса в случае вычисления функции Х Y будет попадание заданного значения Y в интервал Y(X), Y(x+1)-l. В устройстве значение Y(x) формируется на выходе накапливающего сумматора 4, значение Y(x+1)-1 - на выходе комбинационного сумматора 17, сравнение заданного значения аргумента с границами интервала производится на схемах 1,14 сравнения.

Устройство работает следующим образом.

Исходное состояние задается единичным сигналом на входе 11 сброса SR устройства. В этом состоянии на первом выходе R блока 7 управления присутствует единичный сигнал, которым осуществлен сброс счетчика 2 и накапливающего сумматора 4.На втором третьем и пятом выходах блока 7 управления присутствуют нулевые сигналы, на четвертом выходе RA - единичный .

Режим 1-ый возведения в квадрат задается единичным сигналом SQ 1с входа 18 режима устройства. В этом режиме нулевым сигналом с пятого выхода W блока 7 управления через мултиплексор 15 и коммутатор 16 осуществляется подключение к выходу 19

5

ю

, ь15

20

25

30

35

40

45

50

55

результата устройства выхода накапливающего сумматора 4, к вторым входам схем 1,14 сравнения - прямого выхода счетчика 2.

Поступление данных на вход 13 аргумента устройства сопровождается кратковременным единичным сигналом ST на вход 10 запуска устройства. По этому сигналу на первом R и четвертом RA выходах блока 7 управления устанавливается нулевой сигнал, а также начинают восприниматься блоком .7 управления сигналы с выходов схем 1,14 сравнения и с входа 18 режима SQ. При такой дисциплине запуска динамическая погрешность выполнения вычислительных операций возведения в квадрат равна нулю, если скорость поступления новых значений аргумента не вьш1е скорости формирования результата по предыдущему значению.

Если значение входного аргумента X больше величины, содержащейся в счетчике 2, то на выходах и схем 1, 14 сравнения и одноименных входах блока 7 управления образуется комбинация сигналов 10 (см. строку 1, табл 1). В этом случае блок 7 управления формирует на своих третьем и втором выходах последовательность синхронизирующих сигналов S2, S1. По S2 происходит увеличение содержимого накапливающего сумматора 4, по S1 - увеличение содержимого счетчика 2 на единицу.

Если значение входного кода аргумента X меньше величины, содержащейся в счетчике 2, то на выходах и схем 1,14 сравнения образуется комбинация сигналов 01 (см. строку 2, табл. 1). В этом случае блок 7 управления формирует на своих втором и третьем выходах последовательность синхронизирующих сигналов S1,S2. По S1 происходит уменьшение содержимого счетчика 2 на единицу, по S2 - уменьшение содержимого накапливающего сумматора 4, так как в этом случае на входы старших разрядов информационного входа накапливающего сумматора 4 поступает через мультиплексор 3 информация с инверсного выхода счетчика 2.

В результате изложенных действий устройство осуществляет вычисление функции по формулам (1), (2) или (3),(А) соответственно.

При равенстве содержимого счетчи ка 2 значение входного аргумента X (код 00 на входах и блока 7 управления) на четвертом выходе блока управления и на выходе 12 готовности результата устройства формируется единичный сигнал, на выходе 19 результата устройства - значение вычисленной функции Y X .

Процесс вычисления корня квадратного основан на том, что при режиме возведения в квадрат после завершения цикла вычисления содержимое прямых выходов счетчика 2 является корнем квадратным от величины, снимаемой с выходов накапливающего сумматора 4.

Режим 2-ой извлечения квадратного корня задается нулевым сигналом SQ 0 с входа 18 режима устройства. В этом режиме единичным сигналом с пятого выхода W блока 7 управления мультиплексор 15 подключает на второй вход первой схемы 1 сравнения выход комбинационного сумматора 17, коммутатор 16 подключает на выход 19 результата прямой выход счетчика 2, на второй вход схемы 1Д сравнения выход накаплинаюшего сумматора 4. В результате таких подключений на вторые входь схем 14, 1 сравнения будут подаваться значения, соответствующие концам инти 5пала У(х), Y(x + + 1)-1, 1топада1 ие в который входного аргумента Y будет свидете. 1ьст- вовать об oKOriqaHviH вычислительного процесса.

После поступления данных на вход 13 аргумента устройства по сигналу ST на входе 10 запуска устройства блок 7 управления переводит СРОЙ четвертый вьгхг, RA в нулевое состояние и начнет вырабатывать синхронизирующие импульсы S1, S2 в последовательности, определяемые комбинацией сигналов на своих входах

гI /и

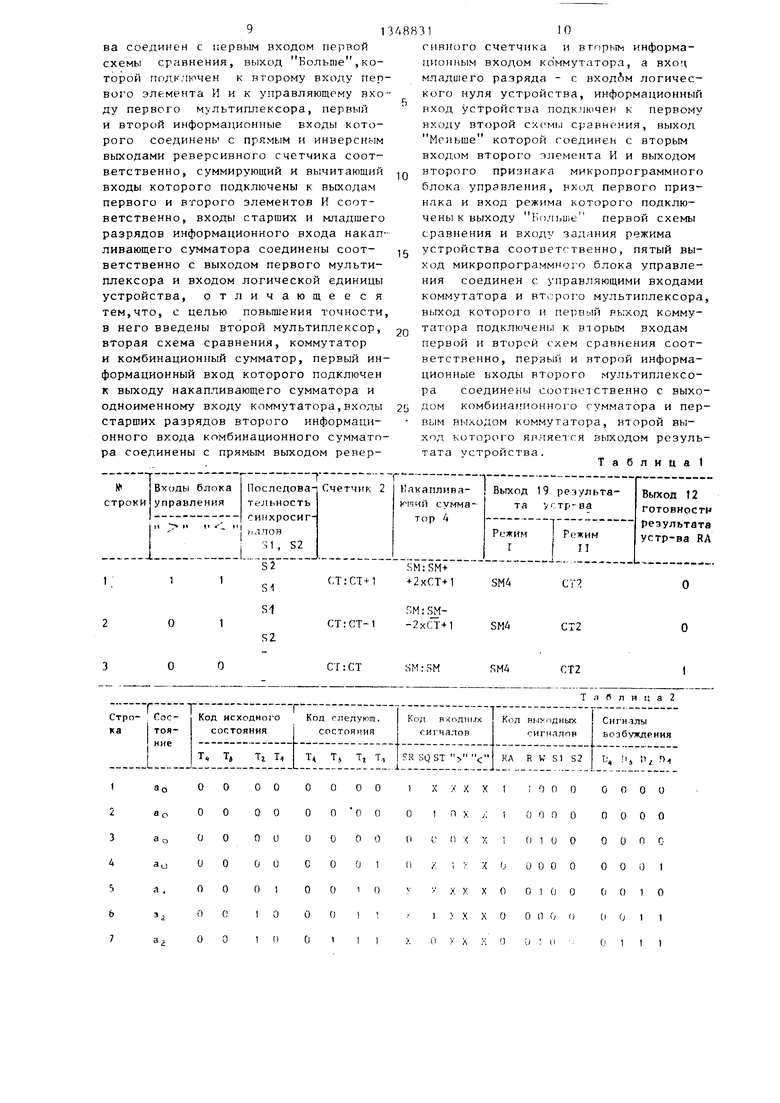

Табл. 1 поясняет работу устройства.

Если значение входного аргумента У на входе 13 устройства больше, чем значение У(х+1)-1, содержаи1ее- ся в комбинационном сумматоре 17, то (см. строку 1, табл. 1) цо ouixpo сигналу S2 прсизойдет увеличение содержимого накапливающего суммах ра 4 (Y (х)-- У (х+1) , а мо синхросиг10

-

3488 П6

налу S1 - увеличе} ие содержимого счетчика 2 ( х+1) .

Ксли значение входного аргумента У на входе 13 устройства меньше,чем значение У(х), содержащееся в накапливающемся сумматоре 4, то (см. строку 2 табл. 1) по сигналам S1, S2 произойдет соответственно уменьще- ние содержимого счетчика 2 и накапливающего сумматора 4.

При попадании ьходного аргумента У в интервал У(х), Y(x+1)-l на входы , блока 7 управления поступает комбинация сигналов 00 (см. строку 3 табл 1), по } оторому синхронизирующие сигналы не вырабатываются, на выходе 12 готовности результата устройства появляется единичный сигнал, на выходе 19 результата устройства находится вычис- v A

15

0

30

ЗЬ

40

45

50

55

-ченное значение .

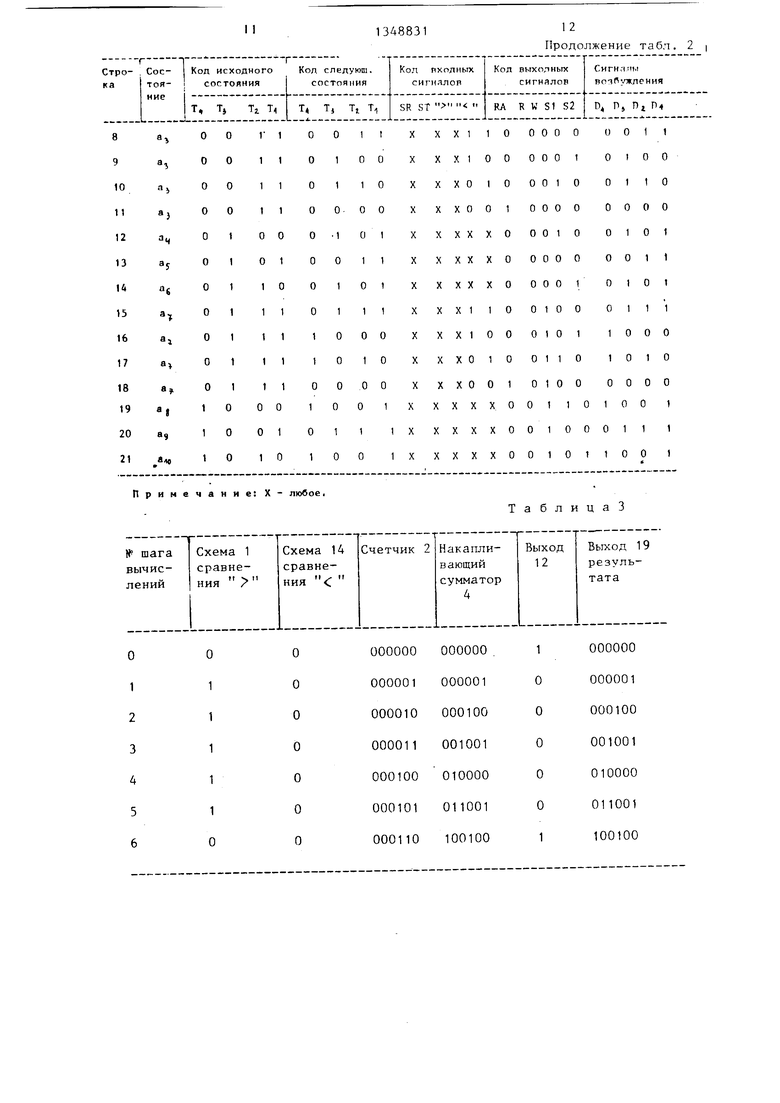

Формирование управляющих сигналов в соответствии с описанным алгоритмом осуществляется блоком 7 управления (фиг. 4). Ксли блок 7 управления построен, например, на основе ПЛМ (фиг. 3), то по размеченной блок- схеме (фиг. 4) в соответствии с известной методикой несложно построить таб.Г. 2 фyнкциot иpoвaния блока 7 управления и осуществить прошивку ИЛ (фиг. 5) .

Наличие н блоке 7 управления (фиг. 3) триггера 22 обеспечивает возможность перевода устройства для возне/гения в квадрат в исходное положение после выполнения очередного цикла вычислений, если в течение этого цикла или после его окончания на вход сброса SR блока 7 управления поступал импульсный единичный сигнал.

Наличие триггера 23 в блоке 7 управления исключает возможность изменения режима устройства статическим сигналом SQ с входа режима )i течение одного цикла вычислений (текущего). Иериоп тактовых импульсов генерат(;;рп 25 импульсов опре- цел :еуся Оьк-тро действием и с: пользуемых ь усч рш пч е для возведения в .ат rvMr- cVropoB и схем срав- 1 It;мня .

.Цлч описанных режимов работы уст- poiicTjia вычисление ,едуюшего значе- ;:у1;кции ocMii n.iHt) на значени пре-- дьа,ущс;го значения этой функции. Это 1и)ноляет обесги чипать высокое быс- ,еГ:ствие гги о ; .: Тке М Т.пых при713

ращений аргумента. Кроме того, устройство имеет высокую помехоустойчивость за счет некритичности к единичным сбоям входных данных, так как устройство отслеживает любые изменения входного аргумента. Если сбой не приводит к изменению сигналов на выходах схем 1,14 сравнения то они не сказываются на конечном результате. В противном случае устройство выполнит обратное требуемому действие (например, вместо суммирования выполняется вычитание приращения функции), однако после восста новления значения аргумента на входе устройства процесс вычисления функции будет продолжен до момента получения истинного результата.

Таким образом, даже при наличии единичных сбоев входных данных будет получен верный результат,при этом в общем случае может лишь увеличится время вычислений.

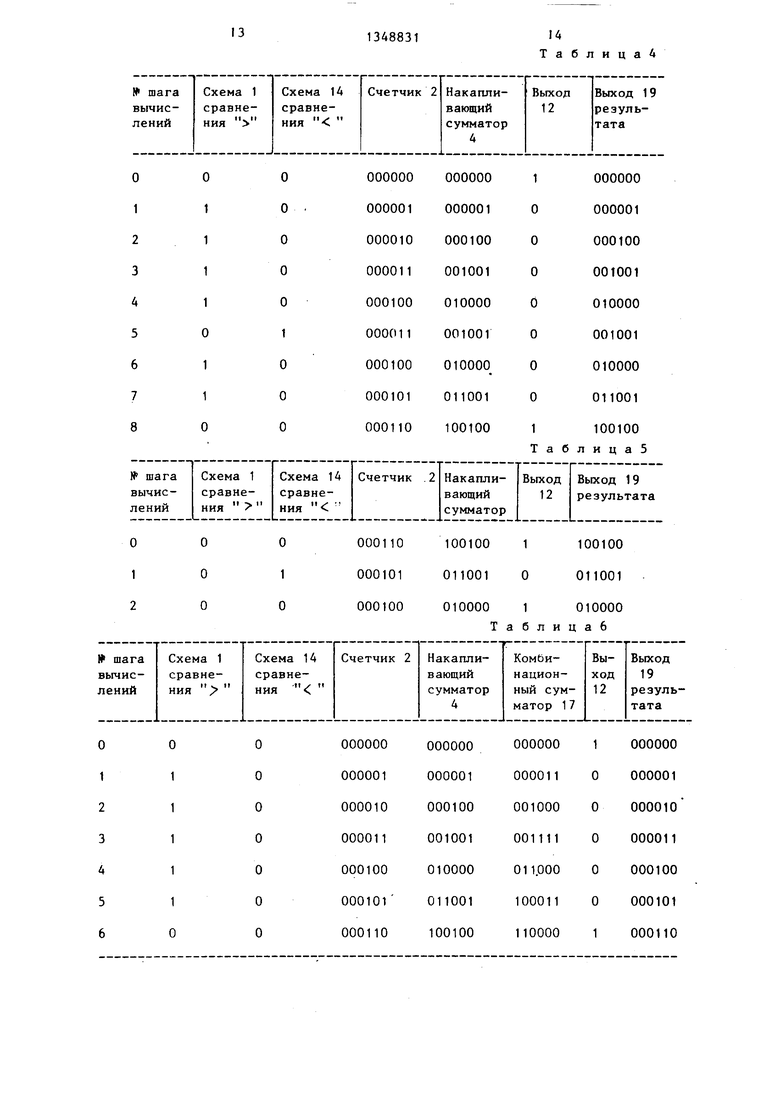

Пример 1. Режим 1 ().

Вычислительный процесс возведения в квадрат числа 6« (OOOllOj) начинается после поступления сигнала ST на вход 10 запуска устройства. При этом состояние выходов схем 1,14 сравнения, счетчика 2, накапливающего сумматора 4 будет изменяться в соответствии с табл. 3.

П р и м е р 2. Режим 1 ().

Предположим,что после четвертого шага произошел сбой, в результате которого на входе образовался нулевой код. После выполнения текущего шага данные на входе восстановились и стали равными 6 (0001lOt).

Вычислительный процесс будет происходить в соответствии с табл. 4.

В отличие от примера 1 здесь количество шагов вычислений увеличилось на два, однако конечный резуль- тат остался без изменений.

П р и м е р 3. Режим 1 ().

Предположим, что значение аргумента по сравнению с примером 1 изменилось и стало равным (OOOIOOj).

Вычислительный процесс будет протекать в соответствии с табл. 5.

Таким образом, если для возведения в квадрат числа в примере 1 потребовалось бы четыре шага вычисле НИИ,то в примере 3 эта операция осуществилась бы за два шага.

Эффект от повышения быстродействи устройства тем больше, чем большая

8

5

о

0

g

Q

g

5

зеличина входного аргумента и меньше величина его приращения.

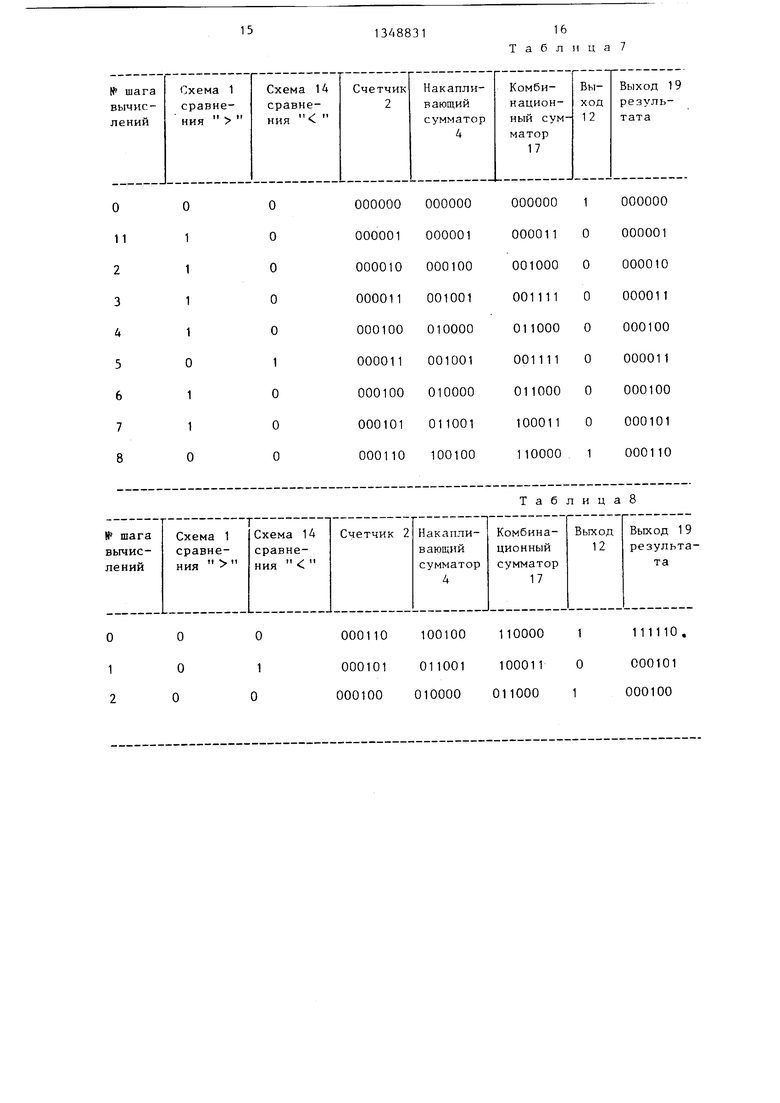

П р и м е р 4. Режим 2 ().

Вычислительный процесс извлечения квадратного корня из числа (1001012) начинается после поступления сигнала ST на вход запуска устройства.

Состояние выходов схем 1,14 сравнения, счетчика 2, накапливающего и комбинационного сумматоров 4,17 будет изменяться в соответствии с табл. 6.

Вычислительный процесс заканчивается при попадании значения аргумента в интервал 36 , Вычисленное значение квадратного корня равно бло .

П р и м е р 5. Режим 2 ().

Предположим,что после четвертого шага вычислений произошел сбой,в результате котого на входе образовался нулевой код. После выполнения одного шага вычислений данные на входе восстановились и стали равными (100101).

Вычислительный процесс будет происходить в соответствии с табл. 7.

П р и м е р 6. Режим 2 ().

Предположим,что значение аргумента по сравнению с примером 4 изменилось и стало равным (OlOOOi).

Вычислительный процесс будет протекать в соответствии с табл. 8.

Таким образом, результат вычисления ; квадратного корня из числа 16 получен за два шага.

Формула изобретени я

Устройство .для вычисления степенной функции, содержащее реверсивный счетчик, накапливающий сумматор,первый мультиплексор, первую схему сравнения, первый и второй элементы И, микропрограммный блок управления, входы запуска и начальной установки которого соединены с одноименными входами устройства, первый выход - с входами сброса реверсивного счетчика и накапливающего сумматора, второй и третий выходы подключены к первым входам первого и второго элементов И и к синхронизирующему входу накапливающего сумматора соответственно, а четвертый выход является выходом готовности результата устройства, информационный вход устройства соединен с первым входом первой схемы сравнения, выход Больше,которой подключен к второму входу первого элемента И и к управляющему входу первого мультиплексора, первый и второй информационные входы которого соединены с прямым и инверсным выходами реверсивного счетчика соответственно, суммирующий и вь читающий входы которого подключены к выходам первого и второго элементов И соответственно, входы старших и младшего разрядов информационного входа накапливающего сумматора соединены соответственно с выходом первого мультиплексора и входом логической единицы устройства, отличающееся тем,что, с целью повышения точности, в него введены второй мультиплексор, вторая схема сравнения, коммутатор и комбинационный сумматор, первый информационный вход которого подключен к выходу накапливающего сумматора и одноименному входу коммутатора,входы старших разрядов второго информационного входа комбинационного сумматора соединены с прямым выходом ревер

5

0

G

гивиого счетчика и вторым информационным входом ко ммутатора, а вхог; младшего разряда - с входЛм логического нуля устройства, информационный вход устройства подключен к первому входу второй cxt Mbi сравнения, вьгход Меньше которой соединен с вторым входом второго элемента И и выходом второго признака микропрограммного блока управления, вход первого приз нака и вход режима которого подключены к выходу Больше первой схемы сравнения и входу задания режима устройства соответственно, пятый выход микропрограммного блока управления соединен с управляющими входами коммутатора и второго мультиплексора, выход которого и первый выход коммутатора подключены к вторым входам первой и второй схем сравнения соответственно, первый и второй информационные входы второго мультиплексора соединены соответственно с выходом комбинационного сумматора и первым выходом коммутатора, второй выход KOTopciro является выходом результата устройства.

Таблица 1

Таблица

(jowz.;

Г

Составитель Н.Шелобанова Редактор Н.Слободяник Техред А.КравчукКорректор М.Демчик

Заказ 5191/48 Тираж 670

ВНИИПИ Государственного комитета СССР

по делам изобретенир и открытий 11-3035, Мсскка, Ж-35, Раушская наб., д. 4/5

Произнодственно-полиграфнческое предприятие, г. Ужгород, ул. Проектная, 4

in

OS

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в квадрат | 1985 |

|

SU1280616A1 |

| Цифровое устройство для вычисления синусно-косинусных зависимостей | 1983 |

|

SU1104510A1 |

| Устройство для вычисления функций двух аргументов | 1986 |

|

SU1413626A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1185329A1 |

| Устройство для вычисления полинома @ -й степени | 1987 |

|

SU1418708A1 |

| Устройство для вычисления тригонометрических и гиперболических функций | 1983 |

|

SU1113798A1 |

| Устройство для вычисления значения полинома @ -й степени | 1983 |

|

SU1134947A1 |

| Цифровое устройство для воспроизведения функций | 1988 |

|

SU1532945A1 |

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| Генератор функций | 1984 |

|

SU1241219A1 |

Изобретение относится к вычислительной технике и может быть использовано для аппаратной реализации операций вычисления степенной функции с показателями 2 и 1/2 в универсальных и специализированных вычислителях. Цель изобретения - повьше- ние точности при вычислении функции с показателем 1/2. Поставленная цель достигается тем,что в устройство, содержащее схему сравнения 1, счетчик 2, мультиплексор 3, накапливающий сумматор 4, элементы И 5,6,блок 7 микропрограммного управления,введены вторая схема сравнения 14,второй мультиплексор 15, коммутатор 16 и комбинационный сумматор 17 с соответствующими связями. Устройство позволяет вычислять степенные функции с показателями 2 и 1/2 с высокой помехоустойчивостью и высоким быстродействием при отработке малых приращений аргумента за счет организации рекурсивного процесса вычисления. 5 ил., 8 табл. S (Л оо 4 00 00 00

| Вычислительное устройство | 1983 |

|

SU1167605A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для возведения в квадрат | 1985 |

|

SU1280616A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-10-30—Публикация

1986-06-17—Подача