импульсов, первый,, второй и третий выходы которого через первый, второй и третий формирователи тактовых импульсов подключены к второму выходу блока, вход блока подключен к информационным входам первого, второго и третьего дешифраторов, выходы первого и второго дешифраторов подключены соответственно к пятому и первому выходам блока, второ выход генератора фазовых импульсов соединен с управляющим входом второго дешифратора и с первыми входами первого и второго элементов И,

вторые входы которых соединены соответственно с первым и вторым выходами третьего дешифратора, выход первого элемента И подключен к третьему и восьмому выходам блока, выход второго элемента И подключен к четвертому и шестому выходам блока, третий выход генератора фазовых импульсов подключен к первому входу третьего элемента И, второй вход которого соединен с вторым выходом третьего дешифратора, а выход третьего элемента Исоединен с седьмым входом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1985 |

|

SU1330634A1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Микропрограммное устройство управления | 1990 |

|

SU1798781A1 |

| Устройство для синтаксически-управляемого перевода | 1982 |

|

SU1062721A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| 8-Битный микропроцессор | 1982 |

|

SU1161950A1 |

| Устройство для обучения | 1987 |

|

SU1559366A1 |

| Микропрограммное устройство сопряжения | 1984 |

|

SU1179359A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

1. МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее блок микропрограммной памяти, выход которого подключен к информационному вхо.- ду регистра микрокоманд, а адресный вход подключен к выходу регистра адреса и первому информационному входу стека адресов возврата, блок формирования адреса, первый, второй и третий информационные входы которого подключены соответственно к выходу адресной части регистра микрокоманд, выходу стека адресов возврата и входу условий перехода устройства, а выход подключен к информационному входу регистра адреса, первый указатель стека, информационный вход которого соединен с информационным входом устройства, блок управления, вход которого соединен с операционньлм выходом регистра микрокоманд, первый выход блока управления соединен с управляющим входом блока формирования адреса, второй выход - с управляияцими входами блока микропрограммной памяти, регистра микрокоманд, стека гщресов возврата, регистра адреса, третий и четвертый выходы - с перв|лм и вторым управляющими входами первого указателя стека, пятый выход блока управления соединен с выходом уст;ройства-, отличающееся тем, целью повышения быстроцействия и расишрения функциональных возможностей за счет обеспечения перемещаемости микропрограмм, оно содержит второй указатель стека и мультиплексор, выход которого соединен с вторым информационным входом стека адресов возврата, управляющий вход мультиплексора соединен с шесты1 1 выходом блока управления, седьмой и восьмой выходы которого подключены соответственнок первому и второму управляющим входам второго указателя стека, выход которого соединен с первым, информационным вхо;дом мультиплексора, второй информационный вход которого соединен с выходом первого указателя стека и информационным входом второго указа- § теля стека,, выход регистра адреса (Л подключен к четвертому информационному входу блока формирования адреса содержащего арифметико-логический блок, первый и второй входы которого подключены к выходеил первого и второго мультиплексоров, причем выход арифметико-логического блока является выходом блока формирования адре са, первый и второй информационные входы первого мультиплексора являются первым и третьим информационными входами блока формирования адреса, первый информационный вход второго мультиплексора является вторым информационным входом блока формирования адреса, второй информационный вход второго мультиплексора подключен к третьему информационному входу первого мультиплексора, и является четвертым информационным входом блока формирования адреса, а управляющие входы арифметико-логического блока и мультиплексоров являются упрайляющим входам блока формирования адреса. 2. Устройство по п. 1, о т л и,чающееся тем, что блок уп равления содержит генератор фазовых

1

Изобретение относится к вычис лительной технике и предназначено для применения в устройствах управления цифровых вычислительных машин .

Известно микропрограммное устройство управления, содержащее блок микропрограммной памяти, регистр адреса, регистр микрокоманд, регист адреса возврата или стек адресов возврата, указатель стека, блок формирования адреса и блок местного управления ij .

Недостатком устройства является ограниченные функциональные возможности, не позволяющие увеличивать число возложенных программ.

Наиболее близким к предлагаемому по технической сущности является устройство микропрограммного управления, содержащее последовательно соединенные указатель стека, стек адресов возврата, блок формирования адреса, регистр адреса, блок микропрограммного управления, регистр, микрокоманд 2J .

Недостатками известного устройства являются дополнительные задержки -времени и формировании адреса микрокоманды при необходимости перехода на программу и ограниченные функциональные возможности. Действительно, помимо затрат времени, необходимых в обычных микрокомандах на формирование адреса в блоке формирования адреса и записи на регист адреса микрокоманд при переходе на подпрограмму необходимо время на увеличение указателя стека и запись в стек.

В то же время развитие интеграль ной технологии и все более широкое применение принципа динамического микропрограммирования на основе оперативной микропрограммной памяти требуют расширения функциональных

возможностей блока формирования адреса. При этом наиболее важной из них представляется обеспечение перемещаемости микропрограмм, что наиболее эффективно достигается при сочетании естественной адресации и принудительной по алгебраическому приращению адреса, указанному в адресной части мш рокоманды.

Целью изобретения является увеличение быстродействия и расширение функциональных возможностей микропррграммного устройства управления.

Поставленная цель достигается тем, что в микропрограммное устройjCTBO управления, содержащее блок миропрограммной памяти, выход которог подключен к информационному входу регистра микрокоманд, а адресный вход подключен к выходу регистра адреса и первому информационному входу стека адресов возврата, блок формирования адреса, первый, второй и третий информационные входы которого подключены соответственно к выходу адресной части регистра микрокоманд, выходу стека адресов возврата и входу условий перехода устройства , а выход подключен к информационному входу регистра адреса, первый указатель стека, информационный вход которого соединен с информационным входом устройства, блок управления, вход которого соединен с операционным выходом регистра, микрокоманд, первый выход блока управления соединен с управляющим входом блока формирования адреса, второй выход - с управляющим входами блока микропрограммной памяти, регистра микрокоманд, стека адресов возврата регистра адреса, третий и четвертый выходы - с первыгл и вторым управляющими входаг/1и первого указателя стека, пятый выход блока управления соединен с выходом устройства, внедены второй указатель стека и мультиплексор, выход которого соединен с вторым информационным входом стека адресов возврата, управляющий вход мультиплексора соединен с шестым выходом блока управления, седьмой и восьмой выходы которого подклк1чены соответственно к первому и второму управляющим входам второго указателя стека, выход, которого соединен с первым информационным входом мультиплексора, второй информационный вход которого соединен с выходом первого указателя стека и информационным входом второго указателя стека, выход регистра адреса подключен к четвертому информационному входу блока формирования адреса , содержащего арифметико-логический блок, первый и второй входы которого подключены к выходам первого и второго мультиплексоров, причем вцход арифметико-логического блока является выходом блока формирования адреса, первый и второй информационные входы первого мультиплексора являются первым и третьим информационными входами -блока формирования адреса, первый информационный вход второго мультиплексора является вторым информационным входом блока формирования адреса, второй информационный вход второго мультиплексора подключен к третьему информационному входу первого мультплексора и является четвертым информационным входом блока формирования адреса, а управляющие входы арифметико-логического блока и мультиплексоров являются управляющим входом блока формирования адреса.

Причем блок управленияГ содержит генератор фазовых импульсов, первый второй и третий выходы которого через первый, второй и третий формирователи таковых импульсов подключены к второму выходу блока, вход блока подключен к информационным входам первого, второго и третьего дешифраторов, выходы первого и второго дешифраторов подключены соотвественно к пятому и первому выходам. блока, второй выход генератора фазовых импульсов соединен с управляющим входом второго дешифратора и с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с первым и вторым выходами третьего дешифратора , выход первого элемента И подключен к третьему и восьмому выхода блока, выход второго элемента И подключен к четвертому и шестому выходам блока, третий выход генератора фазовых импульсов подключен к первому входу третьего элемента И, второй вход которого соединен с вторым выходом третьего дешифратора

а выход третьего элемента И соединен с седьмым входом блока.

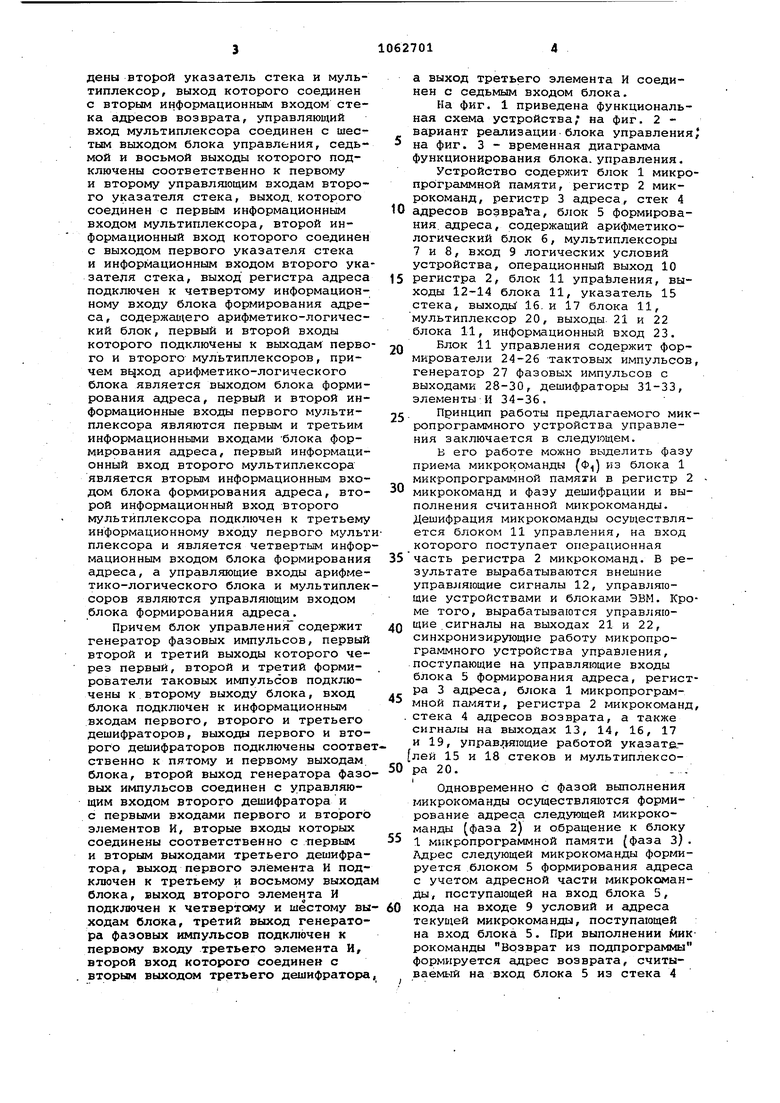

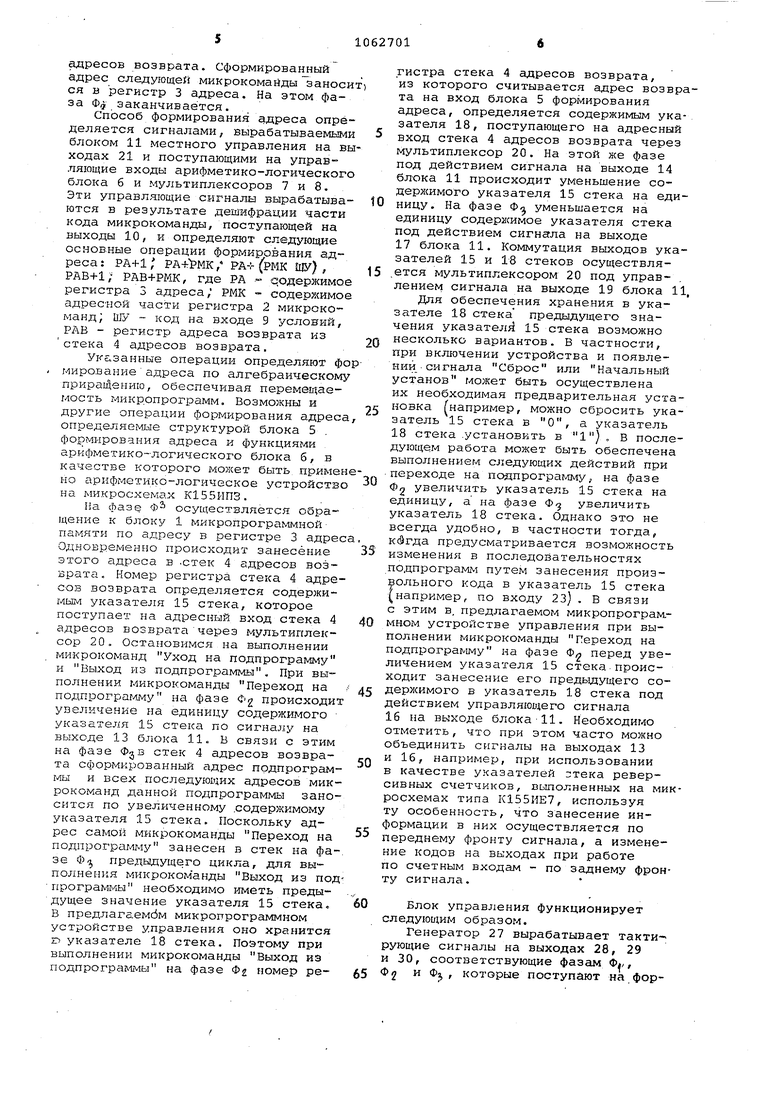

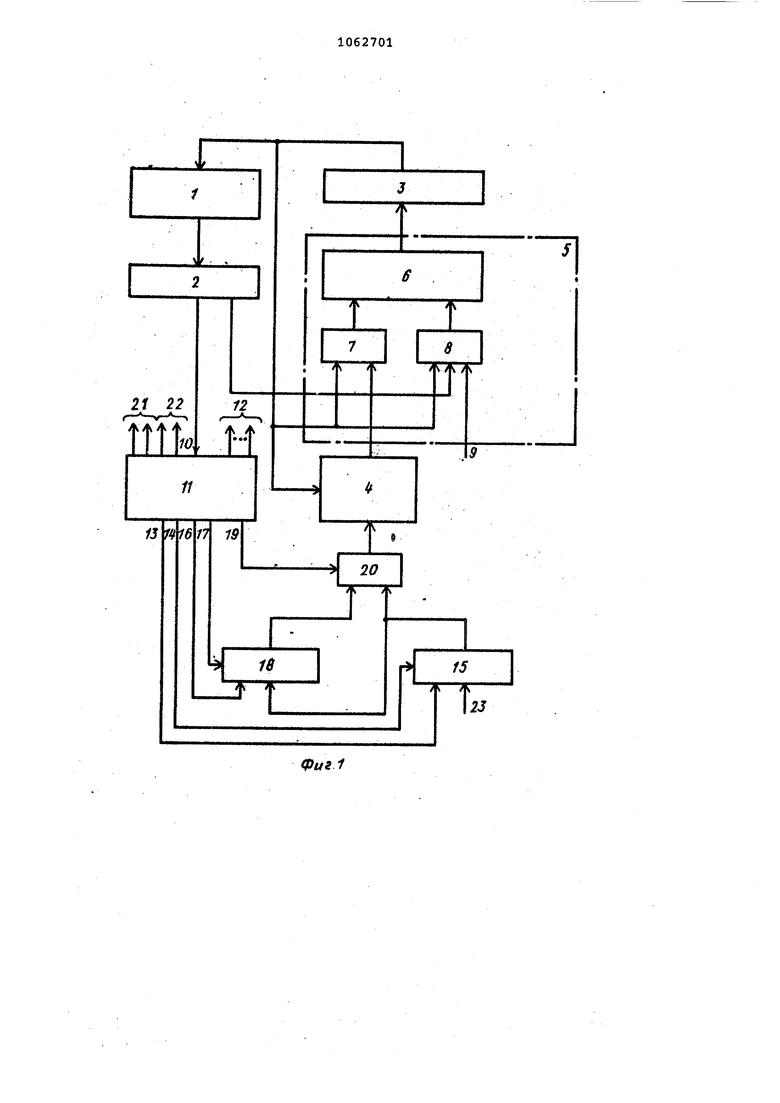

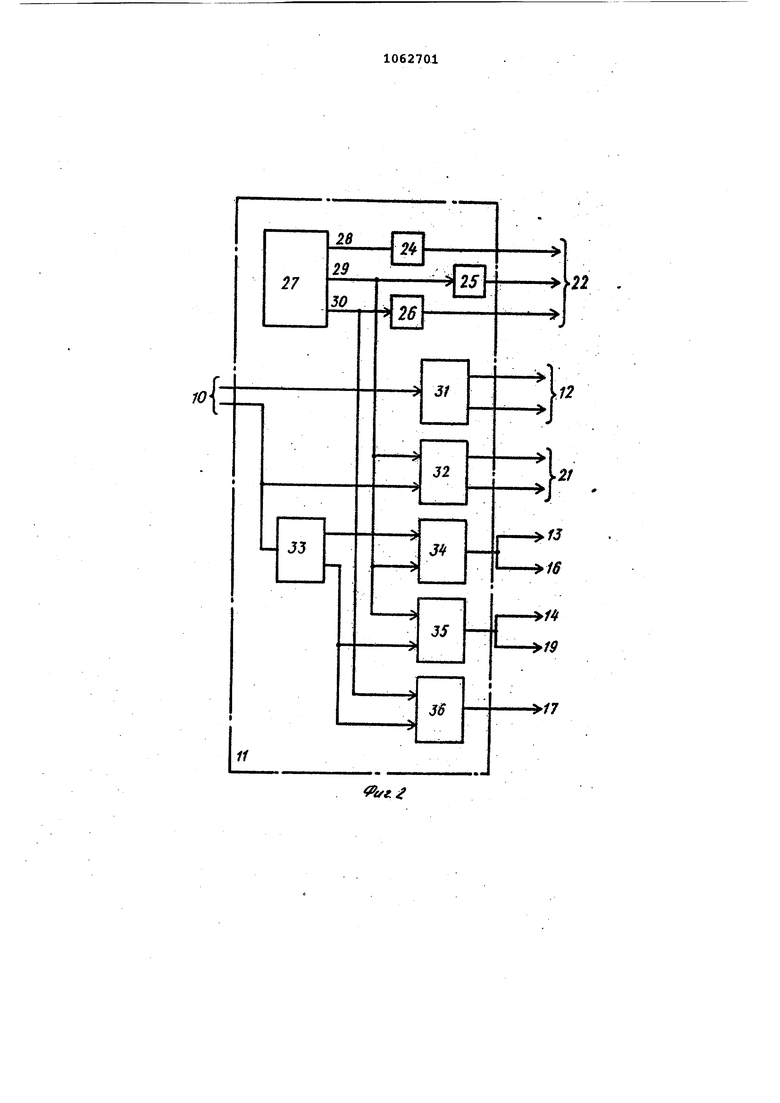

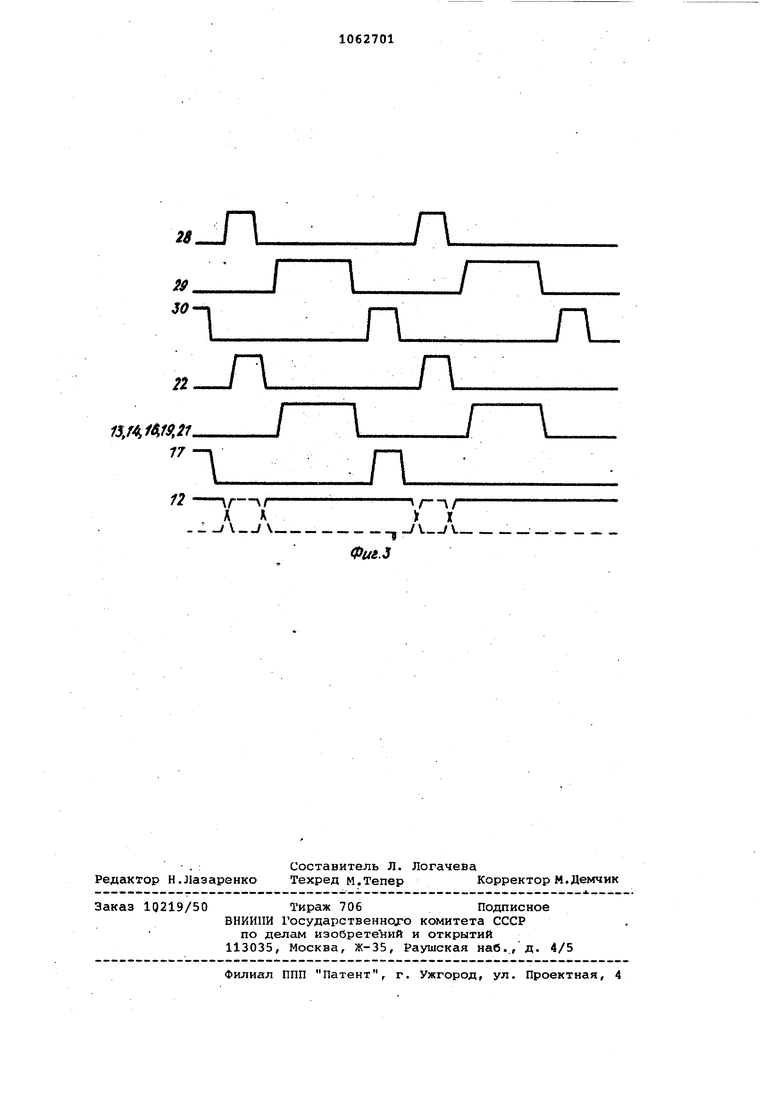

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 вариант реализации блока управления; на фиг. 3 - временная диаграмма функционирования блока, управления.

Устройство содержит блок 1 микропрограммной памяти, регистр 2 микрокоманд, регистр 3 адреса, стек 4

0 адресов возвраТга, блок 5 формирования, адреса, содержащий арифметикологический блок б, мультиплексоры 7 и 8, вход 9 логических условий устройства, операционный выход 10

5 регистра 2, блок 11 упраЬления, выходы 12-14 блока 11, указатель 15 стека, выходьГ 16. и 17 блока 11, мультиплексор 20, выходы. 21 и 22 блока 11, информационный вход 23.

Q Блок 11 управления содержит формирователи 24-26 -тактовых импульсов, генератор 27 фазовых импульсов с выходами 28-30, дешифраторы 31-33, элементы И 34-36.

Принцип работы предлагаемого микропрограммного устройства управления заключается в следующем.

Б его работе можно выделить фазу приема микрокоманды (Ф) из блока 1 микропрограммной памяти в регистр 2

0 микрокоманд и фазу дешифрации и выполнения считанной микрокоманды. Дешифрация микрокоманды осуществляется блоком 11 управления, на вход которого поступает операционная

5часть регистра 2 микрокоманд. В результате вырабатываются внешние управляющие сигналы 12, управляющие устройствами и блоками ЭВМ. Кроме того, вырабатываются управляюQ щие сигналы на выходах 21 и 22, синхронизирующие работу микропрограммного устройства управления, поступающие на управляющие входы блока 5 формирования адреса, регистра 3 адреса, блока 1 микропрограм мной ПШ-1ЯТИ, регистра 2 микрокоманд, . стека 4 адресов возврата, а также сигналы на выходах 13, 14, 16, 17 и 19, управ7 яющие работой указата{лей 15 и 18 стеков и мультиплексо0 ра 20.- .

Одновременно с фазой вьшолнения микрокоманды осуществляются формирование адрес.а следующей микрокоманды (фаза 2) и обращение к блоку

5 микропрограммной памяти (фаза 3) . Адрес следующей микрокоманды формируется блоком 5 формирования адреса с учетом адресной части микрокоманды, поступающей на вход блока 5,

0 кода на входе 9 условий и адреса текущей микрокоманды, поступающей на вход блока 5. При выполнении Мик рокоманды Возврат из подпрограммы формируется адрес возврата, считываемый на вход блока 5 из стека 4 адресов возврата. Сформированный адрес следующей микрокоманды заноси ся в регистр 3 адреса. На этом фаза Ф, заканчивается. Способ формирования адреса опре деляется сигналами, вырабатываемыми блоком 11 местного управления на вы ходах 21 и поступающими на управляющие входы арифметико-логического блока б и мультиплексоров 7 и 8. Эти управляющие сигналы вырабатыва ются в результате дешифрации части кода микрокоманды, поступающей на выходы 10, и определяют следующие основные операции формирования адреса: PA+I; , рА-;-(рмк щу), РАВ+1, РАВ+РМК, где РА - содержимое регистра 3 адреса, РМК - содержимое адрес-вой части регистра 2 микрокоманд; МУ - код на входе 9 условий, РАВ - регистр адреса возврата кз стека 4 адресов возврата, Укс занные операции определяют фо мирование адреса по алгебраическому прира1Дени1о, обеспечивая перемещаемость микропрограмм. Возможны и другие операции формирования адреса определяемал1е структурой блока 5 . формирования адреса и функциями арифметико-логического блока б, в качестве рсоторого может быть примен но арифметико-логическое устройство на микросхемах К155ИПЗ. lia фазе Ф осуществляется обращение к блоку 1 микропрограммной памяти по адресу в регистре 3 адрес Одновременно происходит занесение этого адреса в .стек 4 адресов возврата. Номер регистра стека 4 адресов возврата определяется содержимым указателя 15 стека, которое поступает на адресный вход стека 4 адресов возврата через мультиплексор 20. Остановимся на выполнении микрокоманд Уход на подпрограмму и Выход из подпрограммы. При выполнении микрокоманды Переход на подпрограглму на фазе Ф происходи увеличение на единицу содержимого указателя 15 стека по сигналу на выходе 13 блока 11. В связи с этим на фазе Фдв стек 4 адресов возврата сформированный адрес подпрограм мы и всех последующих адресов мик рокоманд данной подпрограммы зано сится по увеличенному .содержимому указателя 15 стека. Поскольку адрес самой микрокоманды Переход на подпрогрггмму занесен в стек на фа зе Фо, предыдущего цикла, для выполнения микрокоманды Выход из под программы необходимо иметь предыдущее значение указателя 15 стека. В предлагаемом микропрограммном устройстве управления оно хранится Е) указателе 18 стека. Поэтому при выполнении микрокоманды .Выход из подпрограммы на фазе Фг номер регистра стека 4 адресов возврата, из которого считывается адрес возврата на вход блока 5 формирования адреса, определяется содержимым указателя 18, поступающего на адресный вход стека 4 адресов возврата через Мультиплексор 20. На этой же фазе под действием сигнала на выходе 14 блока 11 происходит уменьшение содержимого указателя 15 стека на единицу. На фазе Ф уменьшается на единицу содержимое указателя стека под действием сигнагла на выходе 17блока 11. Коммутация выходов указателей 15 и 18 стеков осуществля.ется мультиплексором 20 под управ- . лением сигнала на выходе 19 блока 11, Для обеспечения хранения в указателе 18 стека предыдущего значения указатели 15 стека возможно несколько вариантов. В частности, при включении устройства и появлении -сигнала Сброс или Начальный установ может быть осуществлена их необходимая предварительная установка например, можно сбросить указатель 15 стека в О, а указатель 18стека .установить в 1) . В последующем работа может быть обеспечена выполнением следующих действий при переходе на подпрограмму, на фазе Фд увеличить указатель 15 стека на единицу, а на фазе Ф- увеличить указатель 18 стека. Однако это не всегда удобно, в частности тогда, ксЭгда предусматривается возможность изменения в последовательностях подпрограмм путем занесения произ ольного кода в указатель 15 стека (например, по входу 23). В связи с этим в. предлагаемом микропрограммном устройстве управления при выполнении микрокоманды Переход на подпрограмму на фазе Ф перед увеличением указателя 15 стека происходит занесение его предьщущего содержимого в указатель 18 стека под действием управляющего сигнала 16 на выходе блока-11. Необходимо отметить, что при этом часто можно объединить сигналы на выходах 13 и 16, например, при использовании в качестве указателей -тека реверсивных счетчиков, выполненных на микросхемах типа К155ИЕ7, используя ту особенность, что занесение информации в них осуществляется по переднему фронту сигнала, а изменение кодов на выходах при работе по счетным входам - по заднему фронту сигнала. Блок управления функционирует следующим образом. Генератор 27 вырабатывает такти- рующие сигналы на выходах 28, 29 и 30, соответствующие фазам Ф|/, Ф и Ф, которые поступают на формирователи 24, 25 и 26 для выработки управляющих сигналов. На выходе синхронизирующих работу регистра 2 микрокоманд, регистра 3 адреса, стека 4 адресов возврата, блока 1 микропрограммной памяти.

Дешифратор 31 вырабатывает внешние управляющие сигналы 12, В качестве формирователей 24-26 могут использоваться, например, элементы серии K155JIA12.

Дешифратор 32 на фазе Ф вырабатывает сигналы на выходе 21, управляющие работой блока формирования адреса. Дешифратор 33 вырабатывает на своих выходах признаки ухода и выхода на подпрограммы соответственно, В результате элемент н 34 на фазе Фл вырабатывает сигналы на выходах 13 и 16, элемент И 35 - сигналы на выходах 14 и 19, а элемент И 36 ка фазе Ф, - сигнал на выходе 17, управляющие работой указателей стеков 15 и 18 и мультиплексора 20,

Положительный эффект предлагаемого микропрограммного устройства управления заключается в увеличении быстродействия и функциональных возможностей по сравнению с известными устройствами.

Увеличение быстродействия достигается тем, что при переходе на подпрограмглу отсутствуют дополнительные потери времени, связанные с увеличением указателя стека и записи в стек, так как запись в стек осуществляется не в начале цикла микрокоманды Переход на подпрограмму, а на фазе обращения к блоку микропрограмг.1ной памяти (Фд) предыдущего цикла. Увеличение х;е указателя стека осуществляется параллельно с фазой формирования следующего адреса (Ф)

Кроме того, следует .иметь в виду, что запоминание Текущего адреса происходит всегда, а не только при переходах на подпрограммы. В связи

с этим создаются удобства для работы предлагаемого микропрограммного устройства управления при прерываниях внутри микропрограмм, в частности при возникновении различных

ошибок.

Увеличение функциональных возможностей достигается за счет универсальной структуры блока 5 формирования адреса, обеспечивающего как

традиционные способы формирования адреса, так и его формирование по алгебраическому приращению, заданному в адресной части микрокоманды. Этим обеспечивается перемещаемость

микропрограмм, что особенно важно при динамическом микропрограммиро/вании, ..

При использовании современной элементной базы, в частности микросхем

серии К155, время сокращения цикла микропрограммного устройства управления будет не менее 50 «с.Для цикла, например, 300 не это означает .его сокращение приблизительно на

17% и соответствующее увеличение быстродействия ЭВМ,

f V r/ii / V

2i 22

12

Ш

Ю.

13

19

ni6

n

16

Фиг1

-Л

6

15

IT

п п

1ЛГ

п п п

Фиг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Хассон С | |||

| Микропрограмг ное управление. | |||

| М | |||

| , Мир, 1973, с | |||

| Способ изготовления звездочек для французской бороны-катка | 1922 |

|

SU46A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Вычислительная техника, 1974, № 20, с | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

Авторы

Даты

1983-12-23—Публикация

1981-10-19—Подача