мирователя адреса, блока управления и блока асинхронного обмена соответственно, первый управляющий выход формирователя адреса подключен к четвертому входу блока управления и к управляющему входу блока оперативной памяти, а второй и третий управляющие выходы формирователя адреса соединены соответственно с пятым и шестым входами блока управления, отличающийся тем, что с целью повышения быстродействия и точности, в него введены блок управления выборкой, причем третий выход дешифратора микрокоманд подключен к группе управляющих входов блока управления выборкой, первьй, второй, третий и четвертый управляющие входы которого соединены с четвертым, седьмым .выходами блока управления, третьим выходом блока микропрограммного управления и первым выходом блока асинхронного обмена соответственно, управляющий вьпсод блока управления выборкой соединен с седьмым и пятым входами блока управления и блока асинхронного обмена соответственно, третий выход блока микропрограммного управления соединен с восьмым входом блока управления, причем блок управления выборкой содержит первый и второй триггеры, первьй и второй элементы И, первый и второй элементы ИЛИ, элемен НЕ и элемент задеряоки, первый управляющий вход блока управления выборкой подключен к первому входу первого элемента И, выход которого соединен с первым входом первого элемента ИЛИ-НЕ, выход которого соединен с входом элемента НЕ и входом элемента задержки, выход которого подключен к первому входу второго элемента И, выход которого подключен к информа ционному входу первого триггера, выход которого является управляющим выходом блока управления выборкой и подключен к первому входу второго элемента ИЛИ, выход которого соединен с информационным входом-второго триггера, выход которого подключен к второму входу первого элемента И, третий вход которого является третьим входом блока управления выборкой, в трой управляющий вход блока управления выборкой соединен с вторым входом второго элемента ИЛИ ,и входом сброса первого триггера, вход которого является четвертым управляющим входом

1

50

блока управления выборкой, группа управляющих входов блока подключена к второму и третьему входам первого элемента ИЛИ-НЕ и к синхровходу второго триггера, выход элемента НЕ соединен с вторым входом второго элемента И.

2. Микропроцессор по п. 1, о т ли чающийся тем, что блок управления содержит первьй, второй, третий, четвертый, пятый, шестой и седьмой триггеры, первый, второй, третий, четвертый, пятый и шестой, седьмой и восьмой элементы И, элемент ИЛИ, первьй, второй, третий и четвертьй элементы НЕ, первьй, второй и третий элементы задержки, причем первый выход блока соединен с выходом первого элемента И, первьй вход которого соединен с выходом первого элемента НЕ, вход которого соединен с пятым входом блока, второй выход блока соединен с выходом первого триггера и первыми входами второго и третьего триггеров, выход третьего триггера подключен к первому входу второго элемента И, выход которого соединен с вторым входом первого -элемента И,третий выход которого подключен к выходу второго элемента НЕ, вход которого соединен с четвертым входом блока, шестой выход блока соединен с выходом четвертого триггера и с первым входом третьего элемента И, выход которого подключе.н к первому входу элемента ИЛИ, выход которого подключен к входу третьего элемента НЕ и к входу первого элемента задержки, выход .которого соединен с первым входом четвертого элемента И, выход которого является первым входом пятого триггера, первьй выход которого соединен с пятым выходом блока и подключен к первому входу пятого -элемента И, выход которого является третьим выходом блока, четвертьй выход блока соединен с выходом шестого триггера, первый вход которого подключен к одному из входов группы управляющих входов блока, седьмой выход блока соединен с выходом шестого элемента И и, с первым входом первого триггера, второй вход которого соединен с входом пуска блока, вход сброса блока соединен с входом второго триггера, выход которого соединен с входом четвертого элемента НЕ и первым входом

шестого элемента И, второй вход которого через второй элемент задержки соединен с выходом четвертого элемента НЕ, первый вход блока соединен с вторыми входами третьего, пятого и шестого триггеров и с первыми входами четвертого и седьмого триггеров, выход седьмого триггера соединен с первым входом восьмого элемента И, выход которого подключен к второму входу элемента ИЛИ, управляющий входвыход блока соединен с вторыми входами третьего элемента И и второго элемента И, третий вход блока соединен с первым входом седьмого элемента И, выход которого соединен с вторым входом седьмого триггера, второй вход

11

50

блока соединен с вторым входом седьмого элемента И, третий вход которого соединен с шестым входом блока, другой из входов группы управляющих входов блока соединен с вторым входом четвертого триггера, седьмой вход блока соединен с вторым входом седьмого элемента И, восьмой вход блока соединен с четвертым входом первого элемента И, причем вькод третьего элемента НЕ подключен к второму входу четвертого элемента И, второй выход пятого триггера соединен,с входом третьего элемента задержки, выход которого подключен к второму входу пятого элемента и.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1979 |

|

SU894715A1 |

| Устройство генерации тестовых последовательностей для контроля оперативных накопителей | 1989 |

|

SU1636858A1 |

| Микропроцессор | 1985 |

|

SU1330634A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Контроллер памяти команд | 1988 |

|

SU1617440A1 |

| Система для контроля микропроцессорных устройств | 1983 |

|

SU1228108A1 |

| Микропрограммный процессор с самоконтролем | 1980 |

|

SU1007109A1 |

| Микропрограммный процессор | 1972 |

|

SU474008A1 |

| Микропрограммный процессор | 1978 |

|

SU741269A1 |

1. 8-БИТНЫЙ МЖРОПРОЦЕССОР, содержащий арифметико-логический блок, блок управления, блок микропрограммного управления, блок оперативной памяти, формирователь адреса, блок асинхронного обмена, дешифратор микрокоманд, причем информационные входы-выходы микропроцессора подключены к информационным входам-выходам арифметико-логического блока, блока оперативной памяти и к первому адресному входу блока микропрограммного управления, выход кода микрокоманд которого соединен с информационными входами дешифратора микрокоманд и арифметико-логического блока, первый информационньй выход которого подключен к адресному входу блока микропрограммного управления, а второй информационный выход арифметико-логического блока подключен к информационному входу формирователя адреса, первый информационный выход которого соединен с адресным входом блока оперативной памяти, второй информационный выход подключен к выходу микропроцессора, а группа управляющих входов формирова-. теля адреса соединена с первым выходом дешифратора команд, второй выход которого подключен к первой группе управляющих входов блока управления, первый, второй, третий, четвертый, пятьй, щестой и седьмой выходы которого подключены соответственно к первому и второму входам блока микропрограммного управления, к первому управляющему входу формирователя адреса, к первому, второму и третьему управляющим входам блока асинхронного обмена, седьмой выход блока управления соединен с вторым управляющим входом формирователя адреса, с первым управляющим входом арифметикологического блока и с третьим входом блока микропрограммного управления, СО первый и второй выход которого подключены соответственно к второму и третьему управляющим входам арифметико-логического блока, первый и второй выходы которого соединены с четвертым и пятым входами блока микройрограммного управления, щестой Од вход которого подключен к четвертому, третьему, первому управляющим входам со ел ар тик о-логического блока, формирователя адреса и блока управления соответственно и к первому выходу блока асинхронного обмена, второй и третий выходы которого соединены соответственно с пятым и вторым управляющими входами арифметико-логического блока и блока управления, входвыход которого подключен к управляющим входам-выходам арифметико-логического блока и блока асинхронного обмена, третий выход арифметико-логического блока соединен с третьим и четвертым управляющими входами фор

1

Изобретение относится к вычислительной технике, в частности к микропроцессорам, осуществляющим обработку цифровой информации.

Цель изобретения - повьш1ение быстродействия устройства.

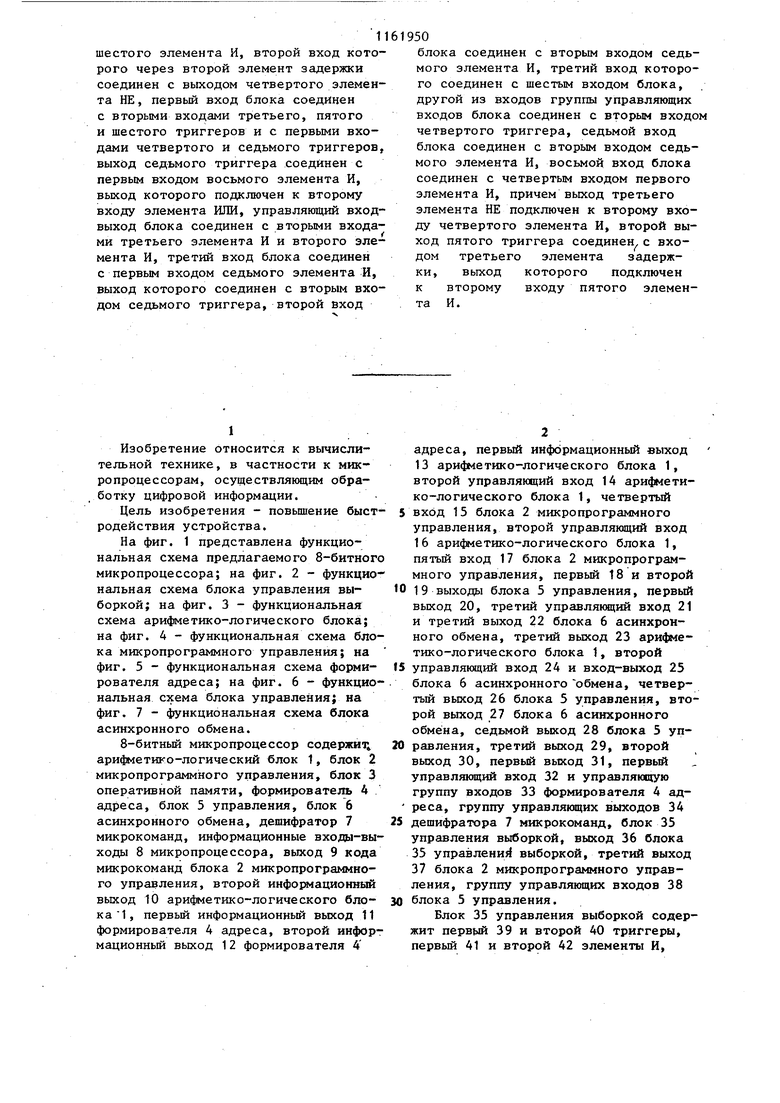

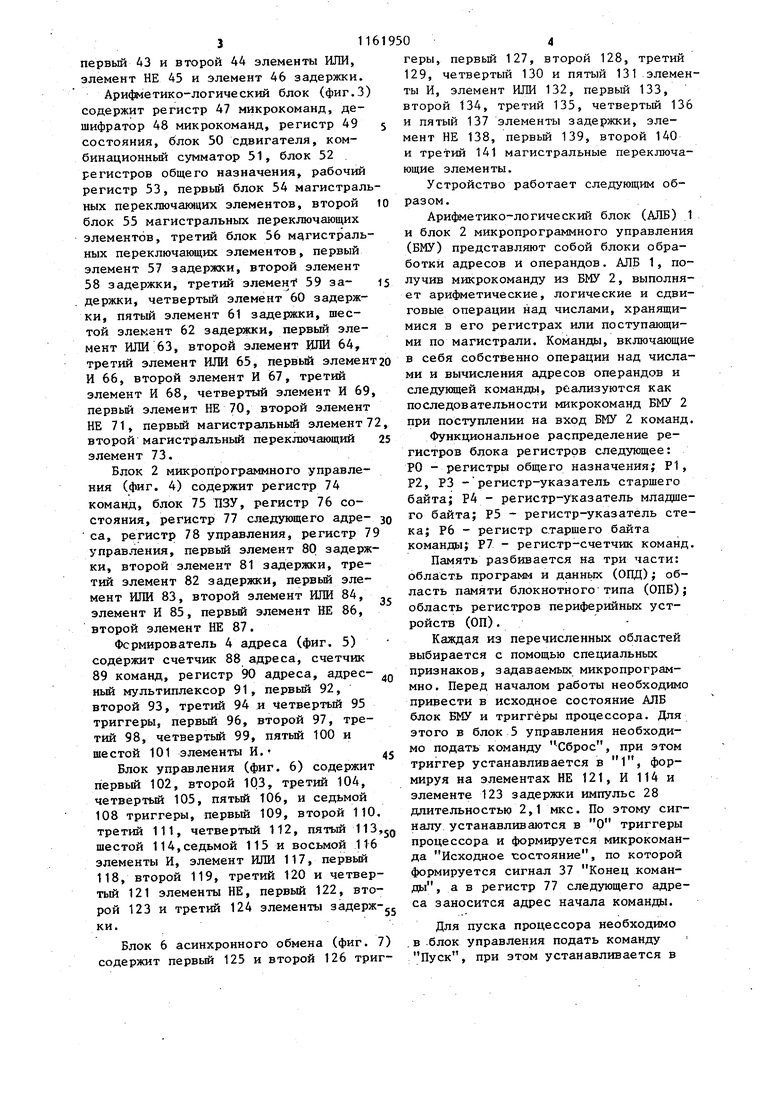

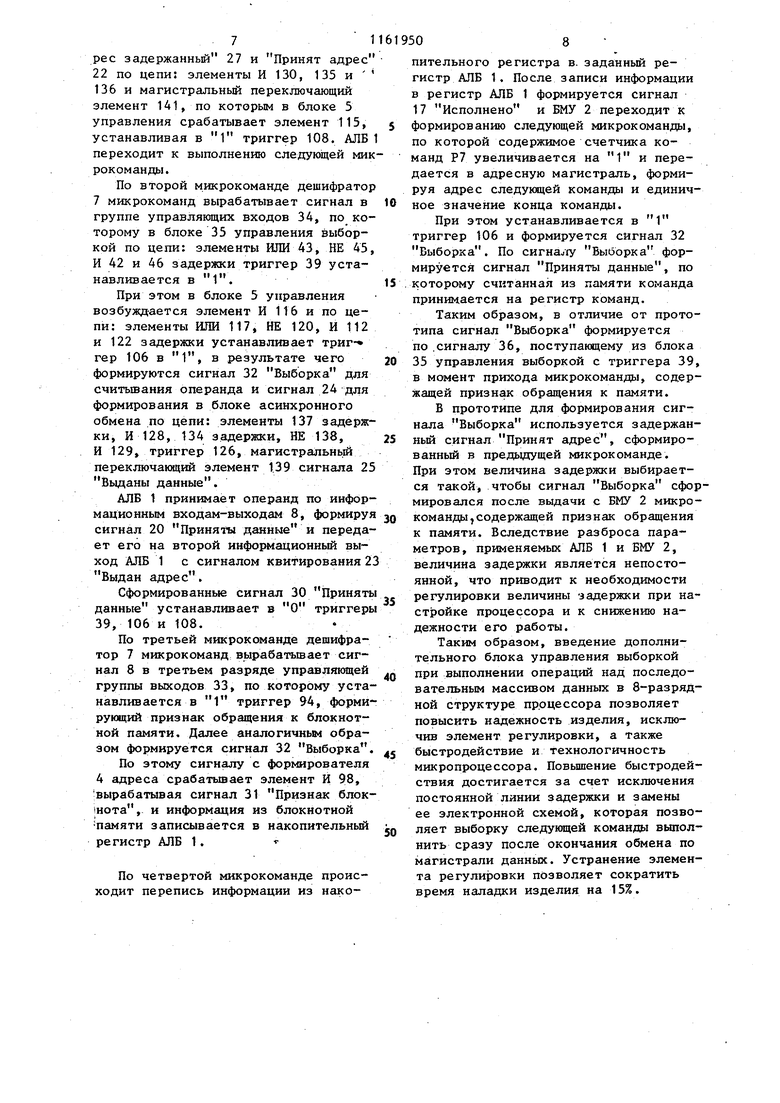

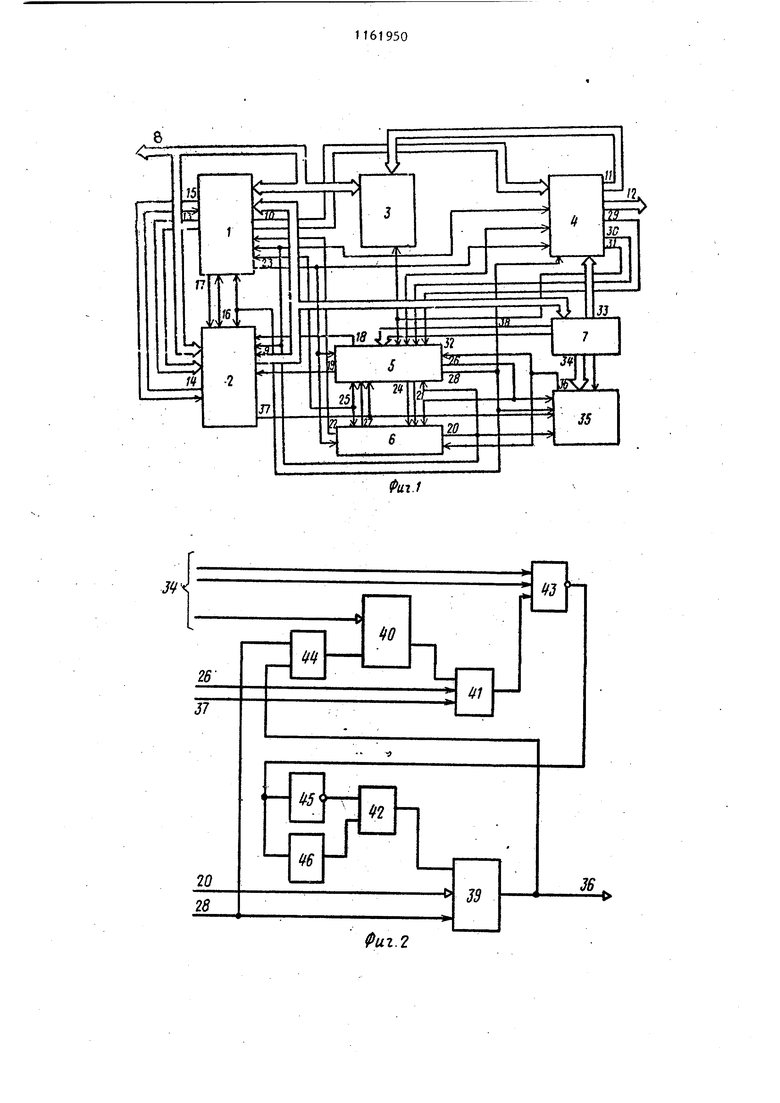

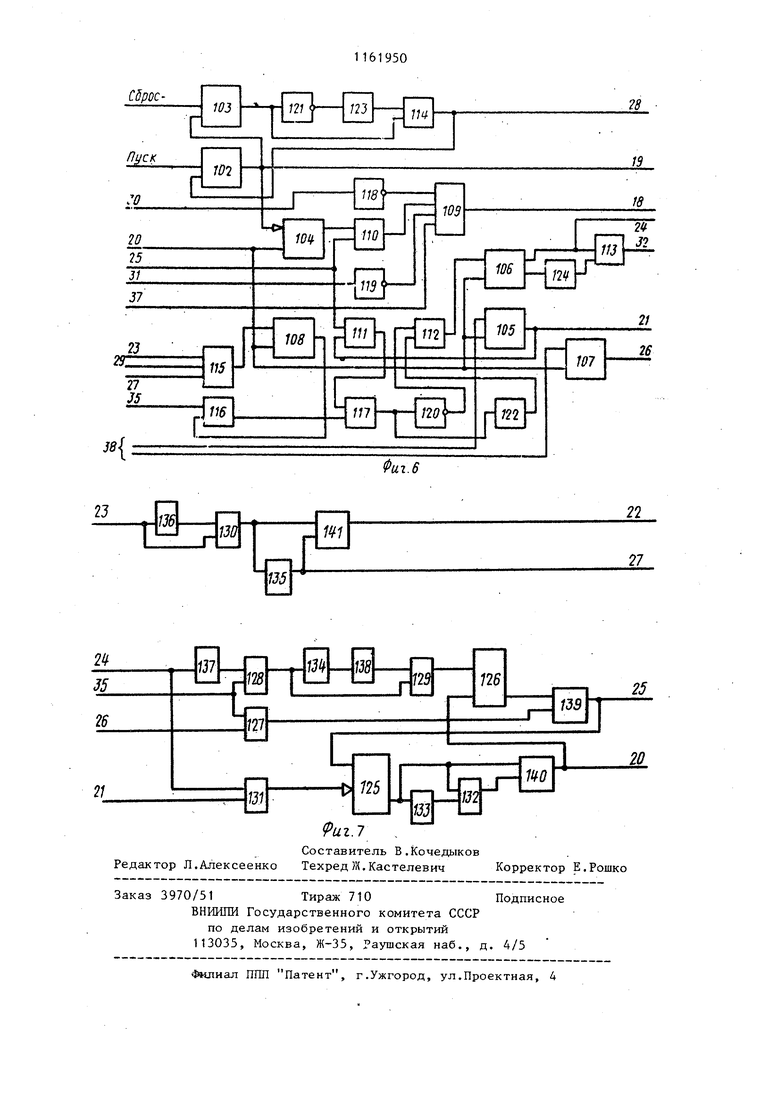

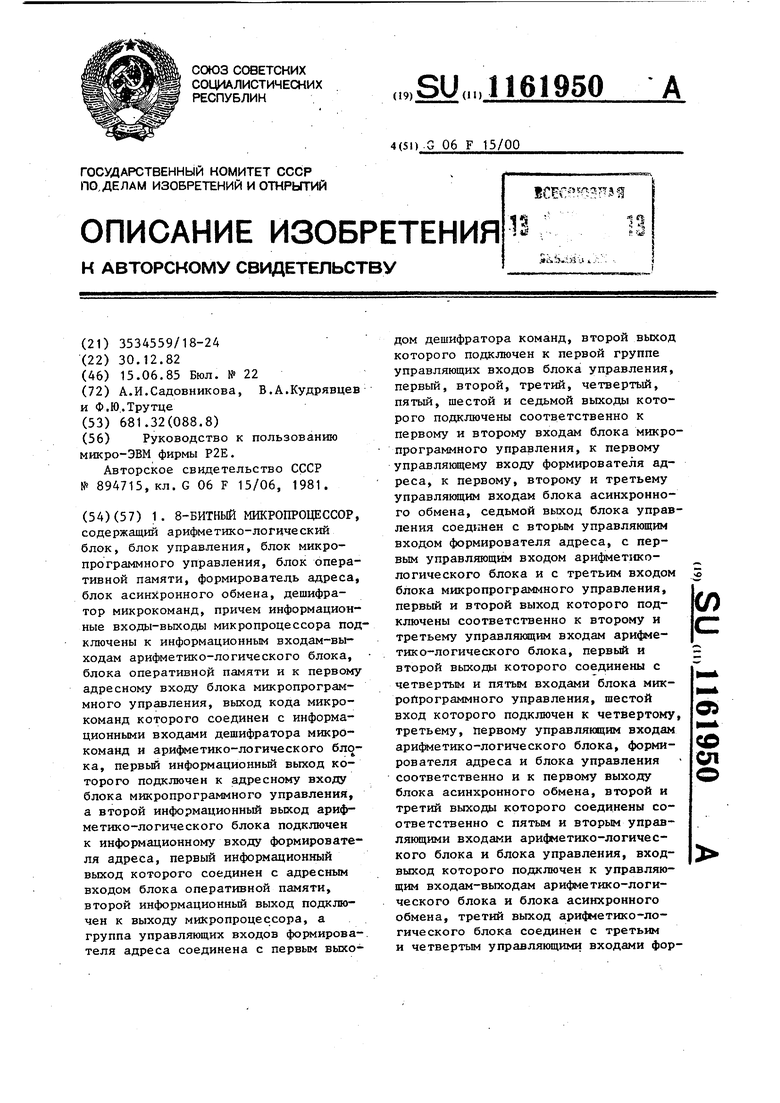

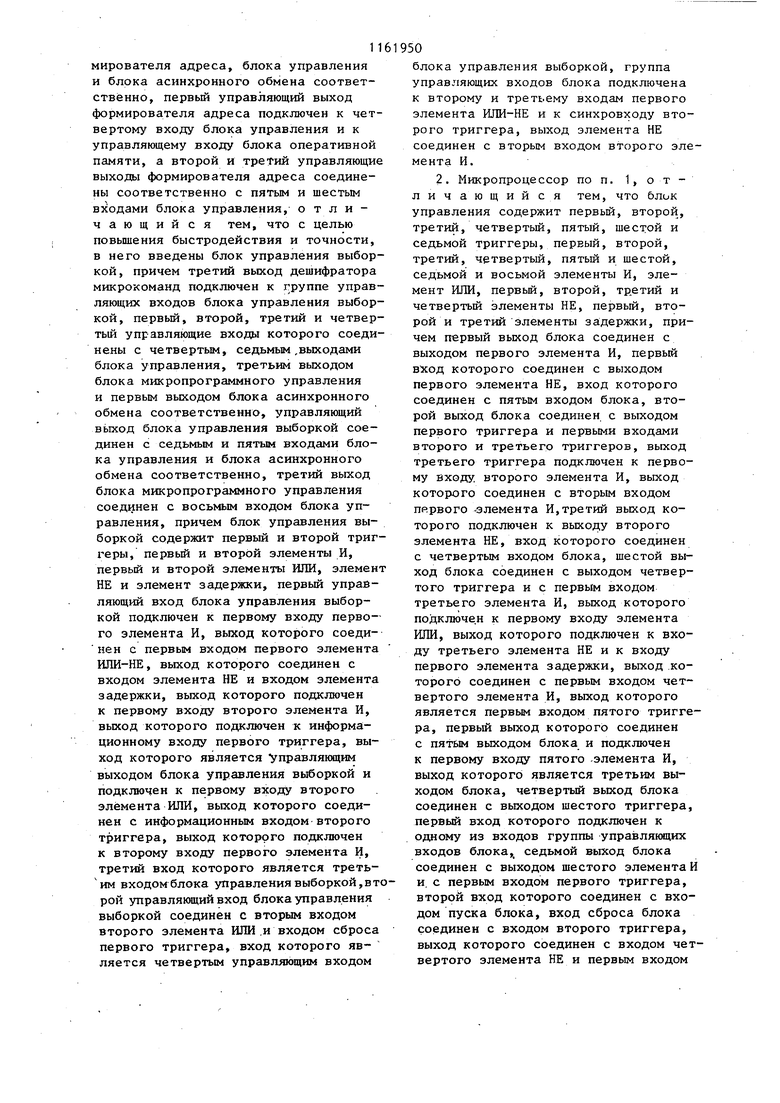

На фиг. 1 представлена функциональная схема предлагаемого 8-битного микропроцессора; на фиг. 2 - функциональная схема блока управления выборкой; на фиг. 3 - функциональная схема арифметико-логического блока; на фиг. 4 - функциональная схема блока микропрограммного управления; на фиг. 5 - функциональная схема формирователя адреса; на фиг. 6 - функциональная схема блока упргшления; на фиг. 7 - функциональная схема блока асинхронного обмена.

8-битный микропроцессор содержит арифметико-логический блок 1, блок 2 микропрограммного управления, блок 3 оперативной памяти, формироватехпь 4 адреса, блок 5 управления, блок 6 асинхронного обмена, дешифратор 7 микрокоманд, информационные входы-выходы 8 микропроцессора, выход 9 кода микрокоманд блока 2 микропрограммного управления, второй информационный выход 10 арифметико-логического блока 1, первый информационный вькод 11 формирователя 4 адреса, второй информационный выход 12 формирователя 4

адреса, первый информационный выход 13 арифметико-логического блока 1, второй управляющий вход 14 арифметико-логического блока 1, четвертый вход 15 блока 2 микропрограммного управления, второй управляющий вход 16 арифметико-логического блока 1, пятый вход 17 блока 2 микропрограммного управления, первый 18 и второй

19 выходы блока 5 управления, первый выход 20, третий управлянщий вход 21 и третий выход 22 блока 6 асинхронного обмена, третий выход 23 арифметико-логического блока 1, второй

управляющий вход 24 и вход-выход 25 блока 6 асинхронного Ъбмена, четвертый выход 26 блока 5 управления, второй выход 27 блока 6 асинхронного обмена, седьмой выход 28 блока 5 управления, третий вьиод 29, второй выход 30, первый выход 31, первый управляющий вход 32 и управляющую группу входов 33 формирователя 4 адреса, группу управлякяцих выходов 34

дешифратора 7 микрокоманд, блок 35 управления выборкой, выход 36 блока 35 управлений выборкой, третий выход 37 блока 2 микропрограммного управления, группу управляющих входов 38

блока 5 управления.

Блок 35 управления выборкой содерит первый 39 и второй 40 триггеры, первый 41 и второй 42 элементы И, первый 43 и второй 44 элементы ИЛИ, элемент НЕ 45 и элемент 46 задержки. Ари41метико-логический блок (фиг.З содержит регистр 47 микрокоманд, дешифратор 48 микрокоманд, регистр 49 состояния, блок 50 сдвигателя, комбинационньй сумматор 51, блок 52 регистров общего назначения, рабочий регистр 53, первый блок 54 магистрал ных переключающих элементов, второй блок 55 магистральных переключающих элементов, третий блок 56 ма.гистраль ных переключающих элементов, первый элемент 57 задержки, второй элемент 58 задержки, третий элемент 59 задержки, четвертый элемент 60 задержки, пятый элемент 61 задержки, шестой элемент 62 задержки, первый элемент ИЛИ 63, второй элемент ЩИ 64, третий элемент ИЖ 65, первьй элемен И 66, второй элемент И 67, третий элемент И 68, четвертый элемент И 69 первьй элемент НЕ 70, второй элемент НЕ 71, первый магистральный элемент 7 второй магистральный переключающий элемент 73. Блок 2 микропрограммного управления (фиг. 4) содержит регистр 74 команд, блок 75 ПЗУ, регистр 76 состояния, регистр 77 следующего адреса, регистр 78 управления, регистр 7 управления, первьй элемент 80 задерж ки, второй элемент 81 задержки, третий элемент 82 задержки, первьй элемент ИЛИ 83, второй элемент ИЛИ 84, элемент И 85, первьй элемент НЕ 86, второй элемент НЕ 87. Формирователь 4 адреса (фиг. 3) содержит счетчик 88 адреса, счетчик 89 команд, регистр 90 адреса, адресньй мультиплексор 91, первьй 92, второй 93, третий 94 и четвертьй 95 триггеры, первьй 96, второй 97, третий 98, четвертьй 99, пятьй 100 и шестой 101 элементы И. Блок управления (фиг. 6) содержит первьй 102, второй 103, третий 104, четвертьй 105, пятьй 106, и седьмой 108 триггеры, первьй 109, второй 110 третий 111, четвертьй 112, пятьй 113 шестой 114,седьмой 115 и восьмой 116 элементы И, элемент ИЛИ 117, первьй 118, второй 119, третий 120 и четвер тьй 121 элементы НЕ, первьй 122, вто рой 123 и третий 124 элементы задерж-jj са

ки.

Блок 6 асинхронного обмена (фиг. 7) содержит первьй 125 и второй 126 тригДля пуска процессора необходимо в .блок управления подать команду Пуск, при этом устанавливается в геры, первьй 127, второй 128, третий 129, четвертый 130 и пятьй 131 элементы И, элемент ИЛИ 132, первьй 133, второй 134, третий 135, четвертьй 136 и пятый 137 элементы задержки, элемент НЕ 138, первьй 139, второй 140 и третий 141 магистральные переключающие элементы. Устройство работает следующим образом. Арифметико-логический блок (ЛЛБ) 1 и блок 2 микропрограммного управления (БМУ) представляют собой блоки обработки адресов и операндов, АЛБ 1, получив микрокоманду из БМУ 2, выполняет арифметические, логические и сдвиговые операции над числами, хранящимися в его регистрах или поступающими по магистрали. Команды, включающие в себя собственно операции над числами и вычисления адресов операндов и следующей команды, реализуются как последовательности микрокоманд БМУ 2 при поступлении на вход БМУ 2 команд. Функциональное распределение регистров блока регистров следующее: РО - регистры общего назначения; Р1, Р2, РЗ -регистр-указатель старшего байта; Р4 - регистр-указатель младаего байта; Р5 - регистр-указатель стека; Р6 - регистр старшего байта команды; Р7 - регистр-счетчик команд. Память разбивается на три части: область программ и данньк (ОДЦ); область памяти блокнотного типа (ОПБ); область регистров периферийных устройств (СП). Каждая из перечисленных областей выбирается с помощью специальных признаков, задаваемых микропрограммно . Перед началом работы необходимо привести в исходное состояние АЛБ блок БМУ и триггеры процессора. Для этого в блок 5 управления необходимо подать команду Сброс, при этом триггер устанавливается в 1, формируя на элементах НЕ 121, И 114 и элементе 123 задержки импульс 28 длительностью 2,1 мкс. По этому сигналу устанавливаются в О триггеры процессора и формируется микрокоманда Исходное состояние, по которой формируется сигнал 37 Конец комана в регистр 77 следующего адредызаносится адрес начала команды.

1 триггер 102, формируя сигнал 19 Пуск, а на триггере 104 и элементе И 110 - сигнал 18 Команда выдана. Команда принимается в БМУ 2 на регистр /4 команд, а затем формируется сигнал 20 Команда принята. Далее БМУ 2 вырабатывает последовательность микрокоманд, сопровождаемых сигналом 16 Начать, по которым устанавливаются в 1 указатель стека Р5, в О - старший байт команды Р6 и счетчик команд Р7; содержимое регистров Р6 и Р7 передается в адресную магистраль.

При вьщаче старшего байта команды АЛБ 1 формирует сигнал 17 Исполнено для блока БМУ 2 и сигнал 23 Выдан адрес, по которому в формирователе 4 адреса на триггере 93 и элементе И 101 вырабатывается признак старшего байта, разрешающий прием адреса на счетчик 89 команд.

После, приема старшего байта команд на счетчик 89 команд блок 6 асинхронного обмена формирует сигнал 22 Принят адрес, по которому АЛБ 1 переходит к выполнению микрокоманд выдачи в магистраль содержимого счетчика команд.

По этой микрокоманде дешифратор 7 микрокоманд вырабатывает управляющую группу сигналов 38, устанавливающих в 1 триггер 107 в блоке 4 управления, формируя сигнал Чтение, и триггер 40 в блоке 35 управления выборкой (фиг. 2). АЛБ 1 формирует сигнал 23 Выдан адрес, по которому в формирователе адреса на элементе И 96 формируется сигнал 29 Признак младшего байта,разрешающий прием адреса на регистр 90 адреса. После приема- младшего байта адреса блок 6 асинхронного обмена формирует сигналы Выдан адрес задержанный 27 и Принят адрес 22. По сигналам Признак младшего байта 29, Выдан адрес 23 и Вьщан адрес задержанный 27 в блоке 5 управления возбуждается элемент И 115, устанавливая в 1 триггер 108.

В момент выработки в блоке БМУ 2 признака 37 Конец команды в блоке 35 управления выборкой возбуждается элемент И 41, который по цепи: элементы ИЛИ 43, НЕ, 46 задержки, И 42 устанавливает триггер 39- в 1, формируя сигнал 36, в результате чего в блоке 5управления срабатывает

элемент И 116, сигнал с которого по цепи: элементы ИЛИ 117, НЕ 120 122 задержки, И 112 устанавливает триггер 106 в 1, формируя сигнал24 Выборка и импульсный сигнал 32 Выборка. В блоке 6 асинхронного приема-передачи через 400 не относительно сигнала Выборка формируется сигнал 25 Выданы данные, по которому считанная из памяти команда принимается на регистр 74 команд БМУ 2.

В качестве примера рассмотрим выполнение команды Чтение из блокнотной памяти или из внешних регистров.

Команда Чтение из блокнотной памяти или из внешних регистров двухбайтовая.

В первом байте хранится команда, во втором - адрес ячейки блокнотной памяти или внешнего регистра.

Выполнение командь осуществляется в три этапа: формирование адреса ячейки операнда; считывание содержимого блокнотной памяти в регистр; формирование адреса следующей команды.

Команда состоит из пяти микрокоман по которым выполняются следунщие действия: содержимое счетчика кома:нд увеличивается на 1 и выдается на второйинформационный выход 10 АЛБ 1; содержимое следующей за командой ячейки принимается ,по информационным входам-выходам 8 в АЛВ t на накопительный регистр, затем,передается на второй информационный выход 10 АЛБ 1; формируется признак обращения к блокнотной памяти, и содержимое ячейки блокнотной памяти принимается по второму информационному входу-выходу на накопительный регистр АПБ 1; выполняется запись содержимого накопителя регистра АЛБ 1 в регистр общего назначения; содержимое счетчика команд увеличивается на 1 и передается на второй информационный выход 10 АЛБ 1.

В результате выполнения первой микрокоманды содержимое счетчика команд в АЛБ 1 увеличивается на 1 и передается ра второй информационный выход 10 АЛБ 1; с сигналом кви-. тирования 23 Выдан адрес. В форми рователе 4 адреса срабатьтает элемент И 96, обеспечивакяций прием младшего байта адреса на регистр 90 адреса, после чего блок 6 асинхронного обмена формирует сигналы Вьщан ад71pec задержанньй 27 и Принят адрес 22 по цепи: элементы И 130, 135 и 136 и магистральный переключающий элемент 141, по которым в блоке 5 управления срабатывает элемент 115, устанавливая в 1 триггер 108. АЛБ переходит к выполнению следующей мик рокоманды. По второй микрокоманде дешифратор 7 микрокоманд вьфабатывает сигнал в группе управляющих входов 34, по которому в блоке 35 управления выборкой по цепи: элементы ИЛИ 43, НЕ 45, И 42 и 46 задержки триггер 39 устанавливается в 1. При этом в блоке 5 управления возбужд-ается элемент И 116 и по цепи: элементы ИЛИ 117, НЕ 120, И 112 и 122 задержки устанавливает триг- гер 106 в 1, в результате чего формируются сигнал 32 Выборка для считьшания операнда и сигнал 24 для формирования в блоке асинхронного обмена по цепи: элементы 137 задержки, И 128, 134 задержки, НЕ 138, И 129 триггер 126, магистральньй переключающий элемент 139 сигнала 25 Выданы данные. АЛБ 1 принимает операнд по информационным входам-выходам 8, формируя сигнал 20 Приняты данные и передает его на второй информационный выход АЛБ 1 с сигналом квитирования 23 Выдан адрес. Сформированные сигнал 30 Приняты данные устанавливает в О триггеры 39, 106 и 108.« По третьей микрокоманде дешифратор 7 микрокоманд вырабатьшает сигнал 8 в третьем разряде управляющей группы выходов 33, по которому устанавливается в 1 триггер 94, формирующий признак обращения к блокнотной памяти. Далее аналогичньм образом формируется сигнал 32 Выборка. По этому сигналу с фор1Мрователя 4 адреса срабатывает элемент И 98, вырабатывая сигнал 31 Признак блок1нота, и информация из блокнотной памяти записывается в накопительный регистр АЛБ 1. По четвертой микрокоманде происходит перепись информации из накопительного регистра в. заданный регистр АЛБ 1. После записи информации в регистр АЛБ 1 формируется сигнал 17 Исполнено и БМУ 2 переходит к формированию следующей микрокоманды, по которой содержимое счетчика команд Р7 увеличивается на 1 и передается в адресную магистраль, формируя адрес следукяцей команды и единичное значение конца команды. При этом устанавливается в 1 триггер 106 и формируется сигнал 32 Выборка. По сигнао1у Выборка формируется сигнал Приняты данные, по которому считанная из памяти команда принимается на регистр команд. Таким образом, в отличие от прототипа сигнал Выборка формируется по .сигналу 36, поступающему из блока 35 управления выборкой с триггера 39, в момент прихода микрокоманды, содержащей признак обращения к памяти. В прототипе для формирования сигнала Выборка используется задержанньй сигнал Принят адрес, сформированньй в предыдущей микрокоманде. При этом величина задержки выбирается такой, чтобы сигнал Выборка сформировался после выдачи с БМУ 2 микрокоманды, содержащей признак обращения к памяти. Вследствие разброса параметров, применяемых АЛБ 1 и БМУ 2, величина задержки является непостоянной, что приводит к необходимости регулировки величины задержки при наст ройке процессора и к снижению надежности его работы. Таким образом, введение дополнительного блока управления выборкой при выполнении операций над последовательным массивом данных в 8-разряДной структуре процессора позволяет повысить надежность изделия, исключив элемент регулировки, а также быстродействие и технологичность микропроцессора. Повьшение быстродействия достигается за счет исключения постоянной линии задержки и замены ее электронной схемой, которая позволяет выборку следующей команщ 1 выполнить сразу после окончания обмена по магистрали данных. Устранение элемента регулировки позволяет сократить время наладки изделия на 15%.

8

25

Чп

If

/

Г7

16

г f

Щ

-2

It

a.

If if

26

4

IL

28

I/2.

7F

л

J

л

ж.

yg Jr

E-pr

Ss:

пж

IS

г

л

1Ж

5J

ГЪ

ffi

36

J9

Фиг.2

Фиг.З

w:

20, 25.

К.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Микропроцессор | 1979 |

|

SU894715A1 |

Авторы

Даты

1985-06-15—Публикация

1982-12-30—Подача