Изобретение относится к вычислительной технике и может быть использовано при создании систем управления подвижными объектами, например робототехническими комплексами или изделиями ракетно-космической техники, работающими при неблагоприятных внешних воздействиях, в том числе мощных электромагнитных воздействиях. Эти воздействия могут быть вызваны разрядами атмосферного электричества или импульсными ионизирующими излучениями космического пространства, вызванных вспышками на Солнце или техногенными авариями на атомных энергетических установках или объектах атомной промышленности. В результате внешних воздействий во время действия импульса нарушается работа вычислительных средств, после окончания которой вычислители способны правильно функционировать, если провести восстановление вычислительного процесса путем использования заранее подготовленных в памяти результатов расчета предыдущих циклов восстановления и реального времени. Однако при ионизирующих воздействиях из-за дозовых нарушений может изменяться быстродействие, что также приводит к нарушению работоспособности, которую при отсутствии катастрофических отказов можно подобрать в соответствии с текущим быстродействием компонентов, подбирая нужное быстродействие по результатам тестовых проверок, для чего требуется обеспечить перестройку частоты задающего генератора, тактирующего формирователь синхроимпульсов.

Известна трехканальная вычислительная система (См., например, АС №1156273, содержащая в каждом канале внешнее устройство и вычислительное устройство, информационный выход которого подключен к первому входу первого мажоритарного элемента и к первому входу первого элемента сравнения всех каналов. Второй вход первого элемента сравнения соединен с выходом первого мажоритарного элемента и со входом внешнего устройства, выход которого подключен к первому информационному входу второго мажоритарного элемента всех каналов, второй и третий информационные входы которого соединены соответственно со вторым и третьим информационными входами вторых мажоритарных элементов других каналов и с выходами внешних устройств соответственно. Выход второго мажоритарного элемента подключен к первому входу второго элемента сравнения и к первому входу вычислительного устройства. Второй вход второго элемента сравнения соединен с первым входом второго мажоритарного элемента, а выход - с выводом связи. В каждом канале содержится также регистр номера канала, четыре блока анализа, группа элементов И, контрольный регистр и элемент ИЛИ, выход которого подключен ко входу прерывания вычислительного устройства. Первый вход контрольного регистра соединен с выходом последовательной передачи информации вычислительного устройства. Входы контрольного регистра соединены с выходами группы элементов И. Вторые выходы соединены со входами элемента ИЛИ. Кроме того, каждый канал содержит элемент НЕ, а каждый блок анализа выполнен в виде дешифратора, связанного входами с выходами элементов сравнения.

Это известное устройство благодаря установке мажоритарных элементов в выходных информационных шинах вычислителей обеспечивает нейтрализацию неисправности, возникающей в одном из каналов при правильной работе двух других каналов. Кроме того, благодаря введению схем сравнения, подключенных к связям внешних устройств, обеспечивается обнаружение неправильной работы одного из них по отличию его информации от двух других, что позволяет диагностировать отказы внешних устройств путем анализа состояний контрольного регистра вычислительным устройством. Эти свойства являются достаточно положительными. Особенно важным является нейтрализация неисправности в одном из каналов вычислительного устройства. В то же время после возникновения неисправности в одном из каналов надежность дальнейшей работы системы резко снижается, так как возникновение неисправности в любом из двух оставшихся исправными вычислительных устройств приводит к полной неработоспособности системы. Это происходит потому, что интенсивность отказа в двух каналах в два раза больше, чем у одноканального вычислителя. Целесообразно максимально полно использовать имеющуюся избыточность в виде двух дополнительно введенных каналов вычислителей для сохранения работоспособности системы после возникновения второй неисправности. Задача сохранения работоспособности системы при возникновении двух неисправностей в системе частично решена в резервированном вычислительном устройстве (См. АС №1200292). В данном устройстве для повышения надежности между блоками памяти и процессорами введен коммутатор, переключающий блоки по сигналам встроенных устройств оперативного контроля.

Общим недостатком известных вычислительных устройств является то, что как для работы схем мажоритации, так и для работы коммутатора, переключающего блоки в процессе работы, требуется синхронная и синфазная работа всех каналов устройства, что обеспечивается введением единого генератора синхроимпульсов. При такой реализации резервирования отказ этого генератора приводит к отказу устройства в целом, кроме того, наличие временного рассогласования одноименных сигналов разных каналов резервированного устройства требует снижения быстродействия с целью учета межканальных рассогласований, вызванных некоторыми отличиями задержек элементов разных каналов. Более того, в процессе работы в блоках вычислительного устройства под влиянием температуры и особенно из-за воздействия внешнего ионизирующего излучения, например, космического пространства происходит деградация параметров комплектующих элементов, учесть которую при проектировании невозможно. Кроме того, при действии внешних факторов, например мощных импульсных электромагнитных или ионизирующих излучений, происходит временное нарушение работы всех блоков и модулей системы. В результате несмотря на отсутствие катастрофических отказов прекращается решение функциональных задач, что приводит к отказу системы управления и даже потере объекта управления. Особенно это характерно для подвижных объектов. С целью устранения отмеченных недостатков в части критичности отказа единого генератора синхроимпульсов, обеспечения максимально возможного быстродействия на каждом интервале времени, а также восстановления работоспособности системы после окончания внешних воздействий предлагается Управляющая вычислительная система.

Раскрытие сущности изобретения

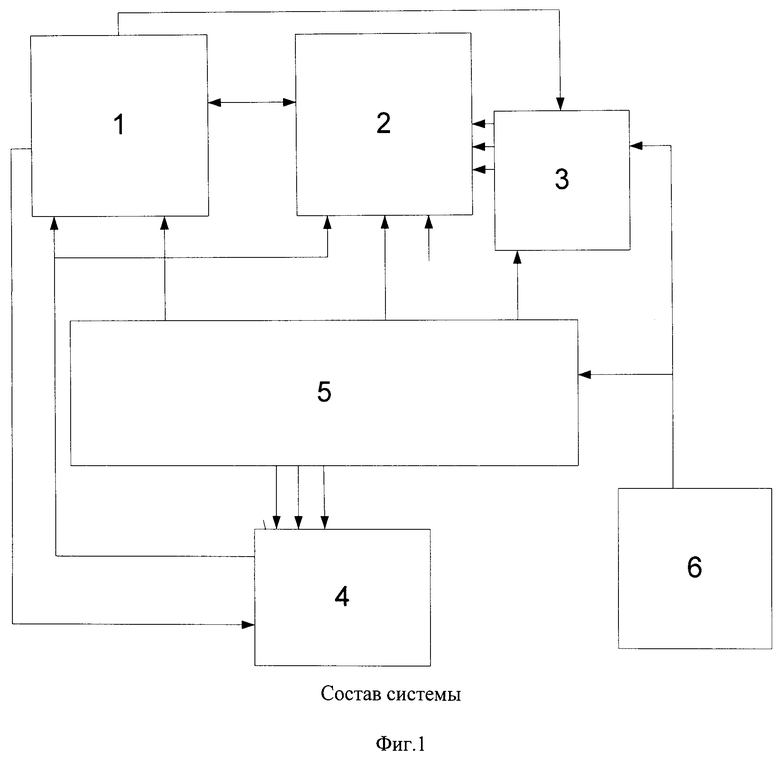

Управляющая вычислительная система содержит (см. фиг.1) процессор, обозначенный цифрой 1, подключенное к нему двунаправленными связями запоминающее устройство (ЗУ), обозначенное цифрой 2, формирователь сигналов блокировки (ФСБ), обозначенный цифрой 3, формирователь синхроимпульсов (ФСИ), обозначенный цифрой 4, устройство формирования интервалов (УФИ), обозначенное цифрой 5, и датчик внешнего фактора (ДВФ), обозначенный цифрой 6. У процессора входы синхронизации и прерывания подключены соответственно к ФСИ и УФИ, у которого выход метки времени подключен к входу ЗУ, а фазирующие выходы подключены к одноименным входам ФСИ, подключенного синхронизирующими выходами к ЗУ и процессору, первый управляющий выход которого подключен к одноименному входу ФСИ, а второй управляющий выход подключен к управляющему входу УФИ. У УФИ и ФСБ запускающие входы и подключены к выходу ДВФ. Выходы ФСИ подключены к синхронизирующему входам процессора и ЗУ, блокирующие входы которого подключены к выходам ФСБ.

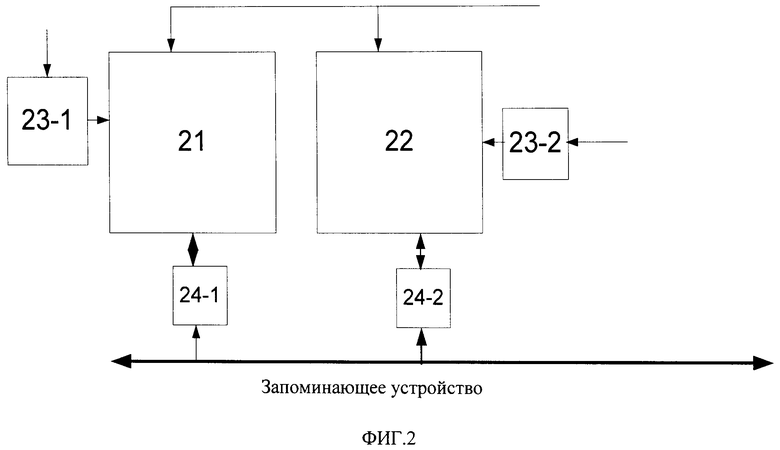

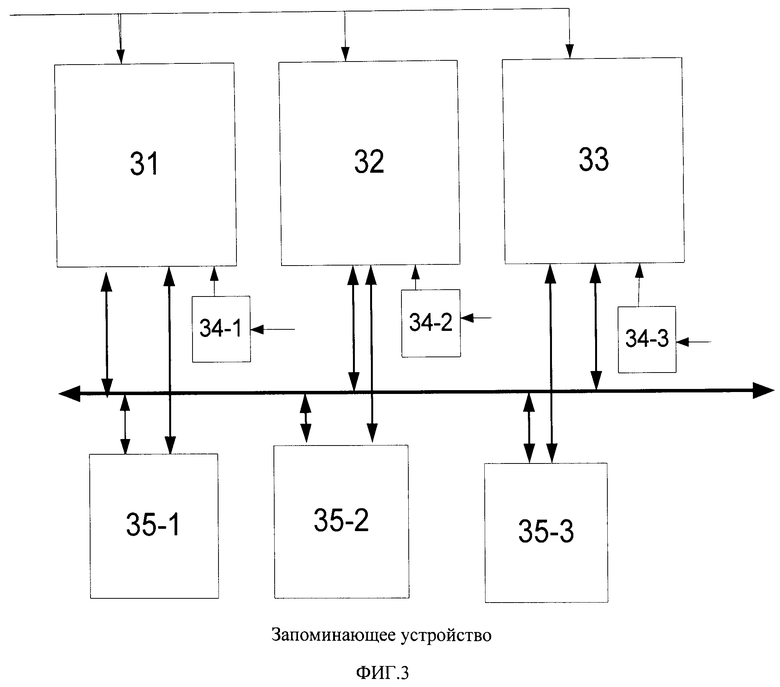

На фиг.2 и 3 приведен состав ЗУ соответственно с двумя и тремя накопителями. Цифрами 21, 22, 31, 32 и 33 обозначены энергонезависимые накопители. В каждом ЗУ накопители подключены к информационной шине, а блокирующими входами подключены к шине блокировки, являющейся входом-выходом ЗУ. Цифрами 23-1, 23-2, 34-1, 34-2 и 34-3 обозначены сумматоры меток времени, а цифрами 24-1, 24-2, 35-1, 35-2 и 35-3 обозначены сумматоры массивов. Входы сумматоров меток являются входами ЗУ, подключенными к УФИ, а их выходы подключены к входам накопителей. Сумматоры массивов подключены двусторонними связями к шине данных ЗУ с одной стороны и к накопителям - с другой.

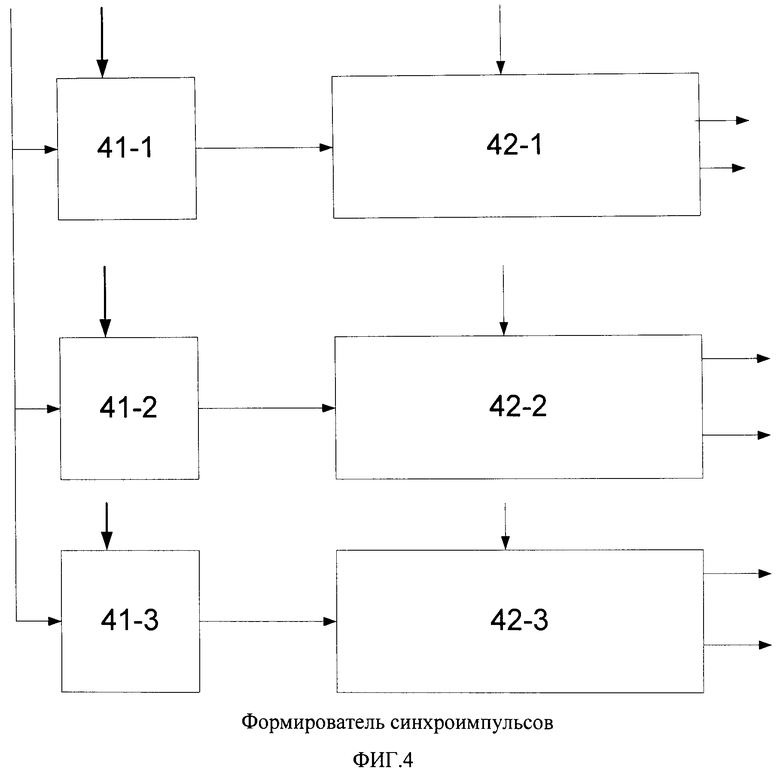

На фиг.4 приведена структура формирователя синхроимпульсов, который содержит 3 идентичных канала, в которых цифрами 41-1, 41-2 и 41-3 обозначены соответственно первый, второй и третий задающие генераторы, подключенные выходами к своим блокам фазирования, первому 42-1, второму 42-2 и третьему 42-3, выходы которых являются выходами формирователя и ФСИ. При этом первый и второй установочные входы генераторов и фазирующие входы блоков фазирования являются одноименными входами формирователя.

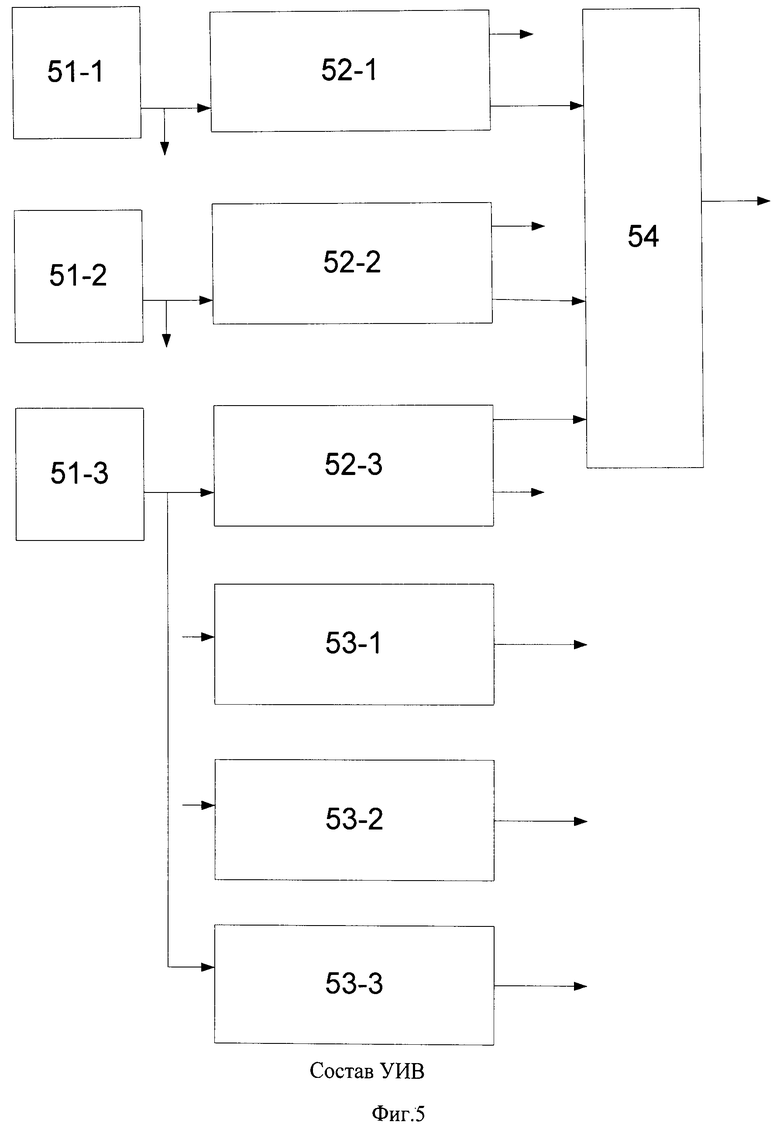

На фиг.5 приведен состав УФИ, который содержит три стабилизированных кварцем задающих генератора импульсов: первый 51-1, второй 51-2 и третий 51-3, выходы которых подключены к первым делителям частоты: первому 52-1, второму 52-2 и третьему 52-3, фазирующие выходы которых являются выходами УФИ, а интервальные выходы подключены к входам мажоритарного элемента 54, выход которого является выходом устройства. Кроме того, выход каждого из генераторов подключен к входу своего формирователя метки времени, соответственно первому 53-1, второму 53-2 и третьему 53-3, выходы которых являются выходами УИВ.

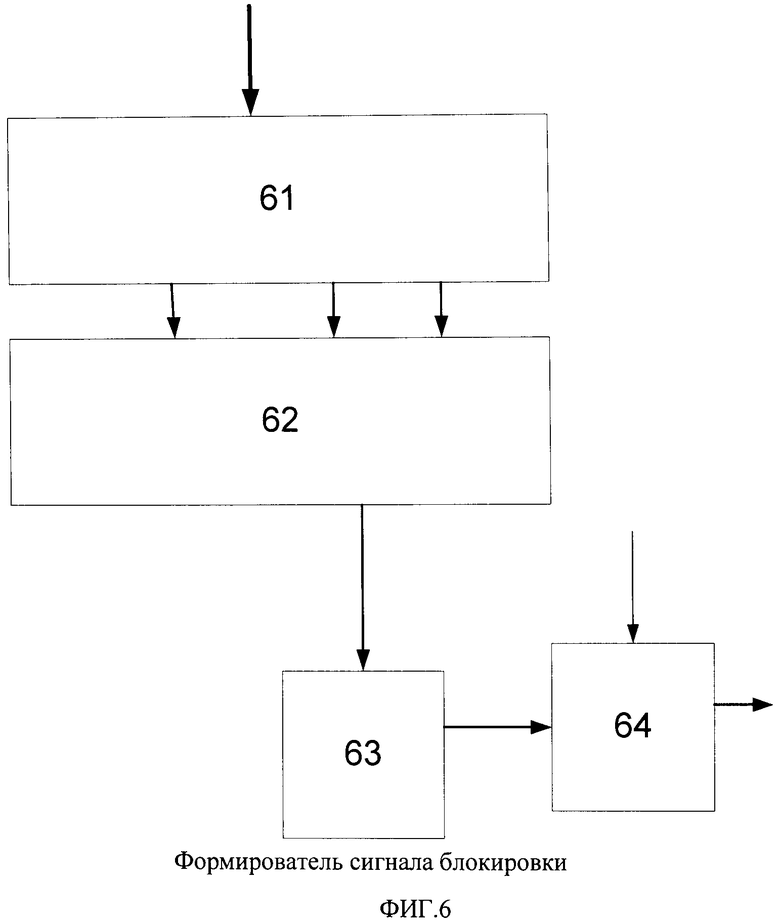

На фиг.6 приведен состав формирователя сигнала блокировки, который содержит регистр 61, подключенный выходами к дешифратору 62, выход которого подключен к входу триггера 63, подключенного выходом к первому входу элемента И, второй вход которого является входом формирователя, подключенным к датчику внешнего воздействия, а выход элемента является выходом формирователя.

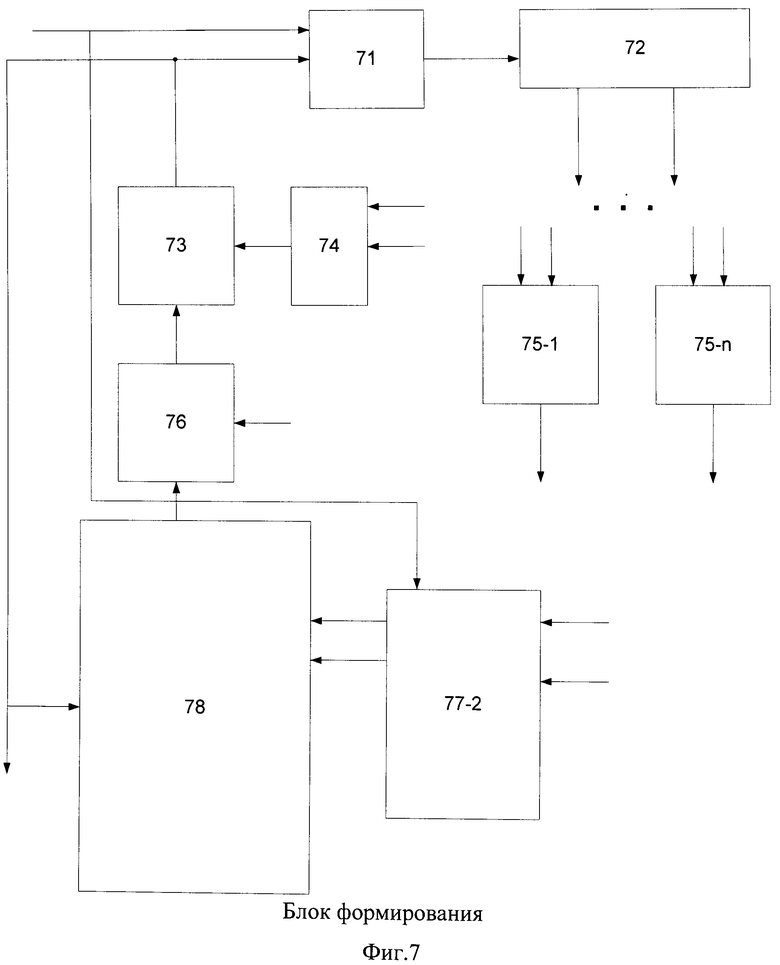

На фиг.7 приведена схема блока фазирования, который содержит логический элемент 71, первый вход которого является входом блока, подключенным к генератору импульсов, а выход подключен к сдвиговому регистру 72, выходы которого подключены к входам сдвигового дешифратора 74, выход которого подключен к запускающему входу триггера останова 73, выход которого является фазирующим выходом блока и подключен ко второму входу логического элемента и первому входу мажоритарного элемента 78, к второму и третьему входам которого подключены выходы триггеров привязки 77, синхронизирующий вход которых объединен с первым входом элемента И, а первый и второй входы являются фазирующими входами блока. Выход мажоритарного элемента подключен к входу триггера пуска 76, выход которого подключен к сбрасывающему входу триггера останова, а выходы нечетных и четных разрядов сдвигового регистра являются соответственно запускающими и сбрасывающими входами триггеров формирователей 75-1-75-n, выходы которых являются выходами блока.

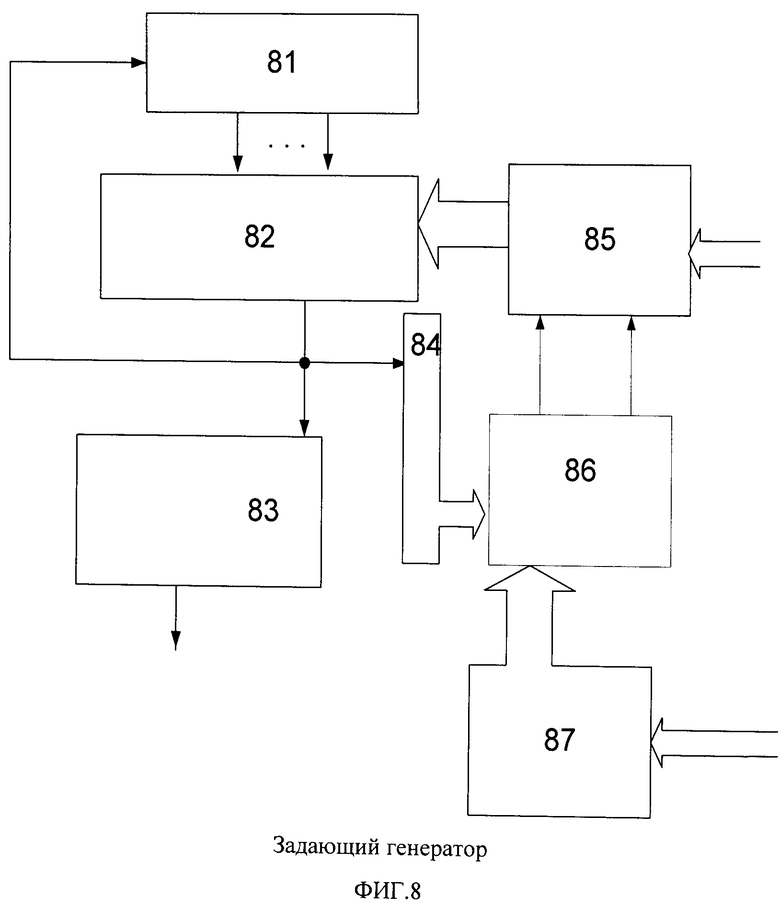

На фиг.8 приведена схема генератора импульсов, который содержит n последовательно соединенных инверторов 81, выходы которых подключены к мультиплексору 82, выход подключен к входу первого инвертора, образуя кольцевой генератор, и входам буфера 83 и счетчика частоты 84, выход буфера 83 является выходом генератора. Выходы счетчика кода частоты подключены к первым входам схемы сравнения 86, подключенной первым и вторым выходами соответственно к инкрементному и декрементному входам счетчика кода частоты, выходы которого подключены к управляющим входам мультиплексора. При этом ко второму входу схемы сравнения подключен выход регистра кода частоты, вход которого и регистра частоты являются соответственно первым и вторым входами задающего генератора.

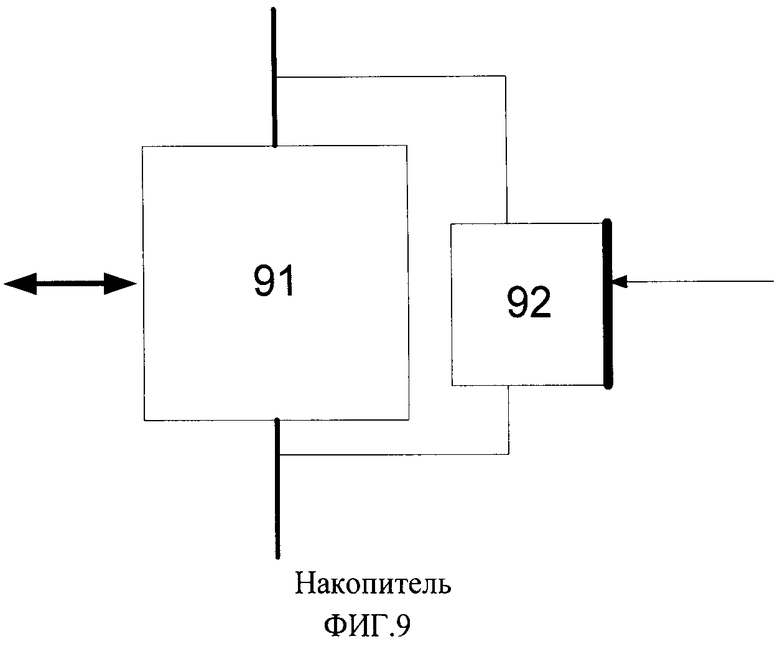

На фиг.9 приведена схема накопителя, где цифрой 91 обозначен собственно энергонезависимый элемент хранения, который может быть реализован на основе многоотверстных ферритовых пластин или тонких цилиндрических магнитных пленок, а также современных интегральных элементов типа FRAM или MRAM, цифрой 92 обозначен нормально замкнутый ключ (МОП транзистор с встроенным каналом), подключенный стоком и истоком параллельно шинам записи элемента хранения, двунаправленные шины которого являются шинами накопителя, а затвор ключа является блокирующим входом накопителя.

Таким образом, восстановлением массива результатов с использованием данных из заблокированных зон памяти и сформированного интервала реального времени обеспечивается восстановление вычислительного процесса, вызванного временной неработоспособностью во время действия импульса, а дозовые изменения быстродействия учитываются установлением нужного значения тактовой частоты задающего генератора.

Система работает следующим образом.

В исходном состоянии в регистр 61 ФСБ записан код, разрешающий обращение к ЗУ со стороны процессора, который записывает результирующие массивы каждого цикла расчетов поочередно в разные накопители таким образом, что в каждый момент один из накопителей остается заблокированным. При этом при поступлении очередного слова на запись из фиксированного адреса вызывается контрольная сумма, которая корректируется на сумматоре с учетом значения записываемого слова и вновь записывается в фиксированный адрес. Текущее реальное время также хранится в отдельном адресе и инкрементируется на своем сумматоре при поступлении метки времени. При возникновении внешнего воздействия срабатывает датчик, сигнал которого вызывает формирование УФИ сигнала блокировки накопителей и сигнала обнуления процессора. После снятия сигнала блокировки и обнуления процессор выходит на программу восстановления, при выполнении которой он записью в регистр 61 ФСБ разрешает обращение к ЗУ, определяет достоверный массив по контрольной сумме или для троированных накопителей выбирает рабочий массив сравнением данных или контрольных сумм по принципу «2 из 3», добавляет к текущему времени фиксированное значение, равное длительности сигнала обнуления и переходит на решение текущих задач управления, работая с поочередно блокируемыми зонами памяти накопителей до очередного воздействия.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОНТРОЛЛЕР ПЕРЕДАЧИ ДАННЫХ | 2013 |

|

RU2514135C1 |

| СИСТЕМА УПРАВЛЕНИЯ ПОДВИЖНЫМИ ОБЪЕКТАМИ | 2011 |

|

RU2503581C2 |

| ТЕХНОЛОГИЧЕСКАЯ УВМ | 2013 |

|

RU2563139C2 |

| МАГИСТРАЛЬНО-МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2564626C2 |

| МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2474868C1 |

| НЕЙРОВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2553098C2 |

| АДАПТИВНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2477882C2 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2536434C2 |

| СБОЕУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2541839C2 |

| САМООРГАНИЗУЮЩАЯСЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2473113C1 |

Изобретение относится к вычислительной технике и может быть использовано при создании вычислительных устройств (вычислительных машин), входящих в состав систем управления подвижными объектами. Техническим результатом является повышение быстродействия на каждом интервале времени, а также обеспечение восстановления работоспособности системы после окончания внешних воздействий. Управляющая вычислительная система содержит процессор с подключенным к нему запоминающим устройством, формирователь синхроимпульсов, выходы которого подключены к процессору и запоминающему устройству. Процессор подключен к формирователю синхроимпульсов посредством управляющего выхода. Система содержит формирователь сигнала блокировки, устройство формирования интервалов и датчик внешнего фактора, выход которого подключен к входу устройства формирования интервалов и к первому входу формирователя сигнала блокировки, подключенного первым выходом к блокирующему входу запоминающего устройства, вторым входом - к управляющему выходу процессора, а третьим входом - к устройству формирования интервалов, у которого выходы обнуления и метки времени подключены соответственно к процессору и запоминающему устройству, а фазирующие выходы - к формирователю синхроимпульсов. 8 з.п. ф-лы, 9 ил.

1. Управляющая вычислительная система, содержащая процессор с подключенным к нему запоминающим устройством, формирователь синхроимпульсов, выходы которого подключены к процессору и запоминающему устройству, отличающаяся тем, что управляющий выход процессора подключен к формирователю синхроимпульсов, а также введением формирователя сигнала блокировки, устройства формирования интервалов и датчика внешнего фактора, выход которого подключен к входу устройства формирования интервалов и к первому входу формирователя сигнала блокировки, подключенного первым выходом к блокирующему входу запоминающего устройства, вторым входом - к управляющему выходу процессора, а третьим входом - к устройству формирования интервалов, у которого выходы обнуления и метки времени подключены соответственно к процессору и запоминающему устройству, а фазирующие выходы - к формирователю синхроимпульсов.

2. Система по п.1, отличающаяся тем, что запоминающее устройство содержит два накопителя, подключенные двунаправленными шинами к шине устройства, два сумматора массивов, подключенные входами к шине устройства, а входами-выходами к соответствующим накопителям, и два сумматора меток времени, входы которых являются входами устройства, блокирующий вход которого является блокирующим входом накопителей.

3. Система по п.1, отличающаяся тем, что запоминающее устройство содержит три накопителя, подключенные двунаправленными шинами к шине устройства, три сумматора массивов, подключенные входами к шине устройства, а входом-выходом к соответствующим накопителям, и три сумматора меток времени, входы которых являются входами устройства, блокирующий вход которого является блокирующим входом накопителей.

4. Система по п.1, отличающаяся тем, что формирователь синхроимпульсов содержит три блока фазирования и три генератора импульсов, у которых первый и второй установочные входы являются одноименными входами формирователя, а выход каждого генератора подключен к входу своего блока фазирования, фазирующий вход каждого из которых подключен к фазирующим входам двух других блоков, а синхронизирующие выходы блока являются одноименными выходами формирователя.

5. Система по п.1, отличающаяся тем, что формирователь интервалов содержит три кварцевых генератора, три делителя частоты, три формирователя меток и мажоритарный элемент, выход которого является выходом устройства, причем выход каждого генератора подключен к входам формирователей меток и делителей частоты своего канала, интервальные выходы которых подключены к входам мажоритарного элемента, а их фазирующие выходы и выходы формирователей меток являются выходами устройства.

6. Система по п.1, отличающаяся тем, что формирователь сигнала блокировки содержит регистр, выход которого подключен к входу дешифратора, выход которого подключен к первому входу триггера, второй вход которого является входом формирователя, а выход подключен к первому входу элемента И, второй вход которого является входом формирователя, а выход - выходом формирователя.

7. Система по п.4, отличающаяся тем, что формирователь метки времени содержит логический элемент, первый вход которого является входом формирователя, а выход подключен к входу сдвигового регистра, выход которого подключен к входу сдвигового дешифратора, подключенного выходом к запускающему входу триггера останова, выход которого является фазирующим выходом формирователя и подключен ко второму входу логического элемента и первому входу мажоритарного элемента, выход которого подключен к входу триггера пуска, подключенного выходом к сбрасывающему входу триггера останова, а к второму и третьему входу мажоритарного элемента подключены выходы триггеров привязки, входы которых являются фазирующими входами блока, а их синхронизирующий вход объединен с первым входом логического элемента, при этом выходы нечетных и четных разрядов сдвигового регистра подключены соответственно к запускающим и сбрасывающим входам триггеров-формирователей, выходы которых являются выходами блока.

8. Система по п.2, отличающаяся тем, что накопитель содержит энергонезависимый элемент памяти, входы-выходы которого являются одноименными входами-выходами накопителя, а параллельно его шинам записи подключен МОП транзистор со встроенным каналом, вход затвора которого является блокирующим входом накопителя.

9. Система по п.4, отличающаяся тем, что генератор импульсов содержит n последовательно включенных инверторов, подключенных выходами к входам мультиплексора, выход которого подключен к входу первого инвертора, буферному элементу, выход которого является выходом генератора, и входу счетчика кода частоты, выходы которого являются первыми входами схемы сравнения, первый и второй выходы которой подключены соответственно к инкрементному и декрементному входам счетчика кода частоты, выходы которого подключены к управляющим входам мультиплексора, а входы счетчика и входы регистра кода частоты и являются первым и вторым входами генератора.

| Устройство для формирования импульсов | 1986 |

|

SU1338031A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

| Резервированное устройство для контроля и управления | 1991 |

|

SU1830535A1 |

| Резервированное вычислительное устройство | 1983 |

|

SU1200292A1 |

| Устройство для контроля и восстановления микропроцессорной системы | 1985 |

|

SU1317441A1 |

| СИСТЕМА УПРАВЛЕНИЯ СУДНОМ | 2010 |

|

RU2428350C1 |

| EP 1538753 B1, 20.08.2008 | |||

| Автоматический огнетушитель | 0 |

|

SU92A1 |

| US 7764129 B1, 27.07.2010 | |||

Авторы

Даты

2014-06-20—Публикация

2011-10-28—Подача