Настоящее техническое решение относится к системам автоматического управления и, в частности, к области судовождения и управления широким классом подвижных объектов а именно движением широкого класса подвижных объектов как водного транспорта, так и систем управления для наземного транспорта, а также систем управления авиационными объектами и изделиями ракетно-космической техники, к которым предъявляются повышенные требования по точностным характеристикам и надежности работы. Известна система автоматического управления судном (см. патент RU 2248914 (В63Н 25/04)) от 01.03.2004, содержащая датчик и задатчик курса, датчик угловой скорости, датчик кормовых рулей, выходы которых подключены к входам первого сумматора-усилителя, выход которого соединен с входом рулевого привода кормовых рулей, датчик угла дрейфа и датчик носовых рулей, выход которого подключен к первому входу второго сумматора-усилителя. Кроме того, в состав системы введены датчик и задатчик бокового смещения судна, задатчик допустимого угла дрейфа и блок логики, содержащий алгебраический сумматор, сумматор модулей двух сигналов, диод и электромагнитное реле с двумя нормально-разомкнутой и нормально-замкнутой контактными группами. Недостатками данного технического решения являются:

1. Нестабильность характеристик. В связи с применением аналоговых узлов, параметры которых существенно зависят от условий эксплуатации (в первую очередь от температуры окружающей среды), будет наблюдаться дрейф параметров системы в целом.

2. Недостаточня отказоустойчивость. В системе не предусмотрено каких-либо средств нейтрализации отказов отдельных узлов, поэтому выход из строя любого узла приведет к отказу системы в целом.

3. Ограниченные функциональные возможности. Внедрение дополнительных управляющих звеньев или расширение набора датчиков потребует полной переработки аппаратуры системы управления.

4. Фиксированный алгоритм управления. Как в случае расширения, а также реализации другого алгоритма управления требуется полная переработка аппаратуры.

Задачи расширения функциональных возможностей, применения различных алгоритмов управления и повышения стабильности благодаря наличию цифрового вычислителя частично решаются в изобретении - аппаратуре автоматического управления движением судна (см. патент RU 2221728 (В632Н 25/04)) от 13.05.2002, содержащей, кроме вычислителя, задатчик путевого угла, датчик угла перекладки руля, рулевой привод, опорную и вспомогательную антенну, приемник системы спутниковой навигации (ССН), сумматор, два интегратора и дифференциатор. Однако недостаток - низкая отказоустойчивость в данной аппаратуре - по-прежнему присутствует, так как любой отказ вычислительного устройства влечет за собой отказ всей системы. В то же время катастрофический отказ может быть нейтрализован за счет использования заранее введенных в состав системы резервных компонентов, а параметрический дрейф параметров отдельных узлов может быть нейтрализован перестройкой параметров работы схем электрических, например изменением быстродействия блоков цифровой обработки или учетом изменения параметров, например стабильности токов и напряжений аналоговых узлов, их измерениям в процессе работы и последующим учетом их отклонений при обработке данных в вычислительных устройствах. Наиболее полно задача нейтрализации одиночных отказов в вычислительном устройстве, являющемся основным звеном системы решена в СИСТЕМЕ УПРАВЛЕНИЯ СУДНОМ (см. заявку на изобретение №2010133015/11 (0468744)), по которой принято решение о выдаче патента (№010133015 (046744), от 11 марта 2011 г. Данное решение может быть взято за прототип. Для нейтрализации последствий одиночных отказов вычислительного устройства и сохранения работоспособности системы управления в целом в состав системы введены три вычислительных устройства с общим устройством синхронизации, обеспечивающим синхронную и синфазную работу вычислителей, выходные сигналы которых, прежде чем поступить на исполнительные органы объекта, проходят через узел мажоритации. Данное решение обеспечивает нейтрализацию первого отказа в любом из вычислителей. Однако после возникновения первой неисправности в любом из вычислительных устройств надежность дальнейшей работы системы резко снижается, так как возникновение любого второго отказа в любом из двух оставшихся исправными вычислителей приводит к отказу системы в целом, а интенсивность отказов вычислителей, приводящих к потере управления при таком варианте резервирования, в два раза больше, чем при работе с одним оставшимся исправным вычислителем. Целесообразно после возникновения первого отказа перейти от структуры с мажоритацией к структуре, в которой к выходу подключен один из вычислителей, что требует введения дополнительных средств контроля работы вычислителей и переключения их выходных сигналов. Кроме того, наличие общего устройства синхронизации, отказ в котором приводит к неработоспособности системы, также не способствует требованиям высокой надежности системы. В большинстве вычислительных устройств, работающих длительное время в неблагоприятных внешних условиях, а именно расширенном диапазоне температур, потоках ионизирующего излучения как естественного непрерывного фонового, так и импульсного (при вспышках на Солнце или техногенных авариях на объектах с атомными энергоустановками), происходит дрейф параметров элементов, приводящий в цифровых устройствах, как правило, к изменению быстродействия, а в аналоговых узлах - к изменению стабильности и точности их работы. В то же время, подстраивая частоту обработки информации в цифровых узлах под их фактическое быстродействие и учитывая дрейф параметров в аналоговых узлах (например, в аналого-цифровых преобразователях), можно сохранить работоспособность и точностные характеристики системы управления. Решение этих задач требует существенной переработки известных решений.

С целью повышения надежностных и точностных характеристик системы управления и расширения состава объектов для ее применения предлагается СИСТЕМА УПРАВЛЕНИЯ, содержащая различные датчики (угловой скорости, ускорения и т.д.), аппаратуру спутниковой навигации (АСН), блок сбора информации (БСИ), три управляющих вычислительных устройства (УВУ) с формирователем синхроимпульсов (ФСИ), исполнительные органы (ИО) объекта управления. Кроме того, в состав системы введены подсистема инерциальной навигации (ПИН), подсистема оптической коррекции (ПОК).

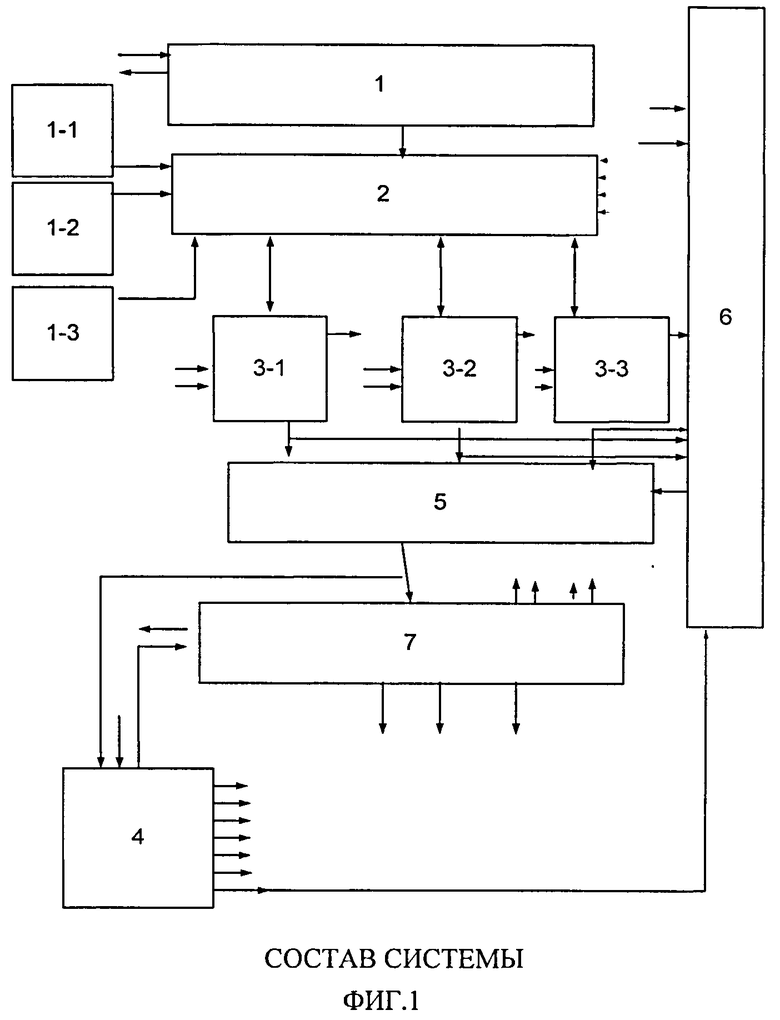

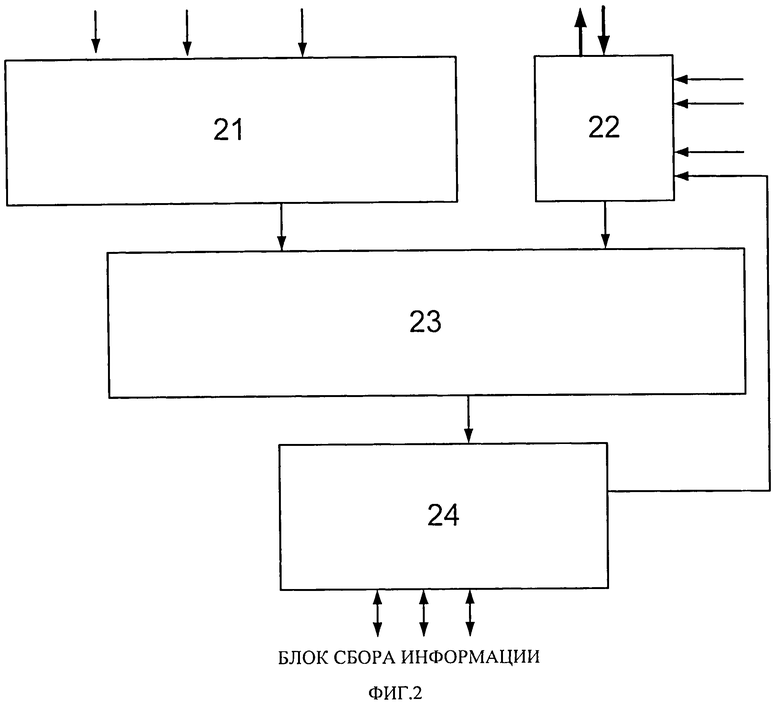

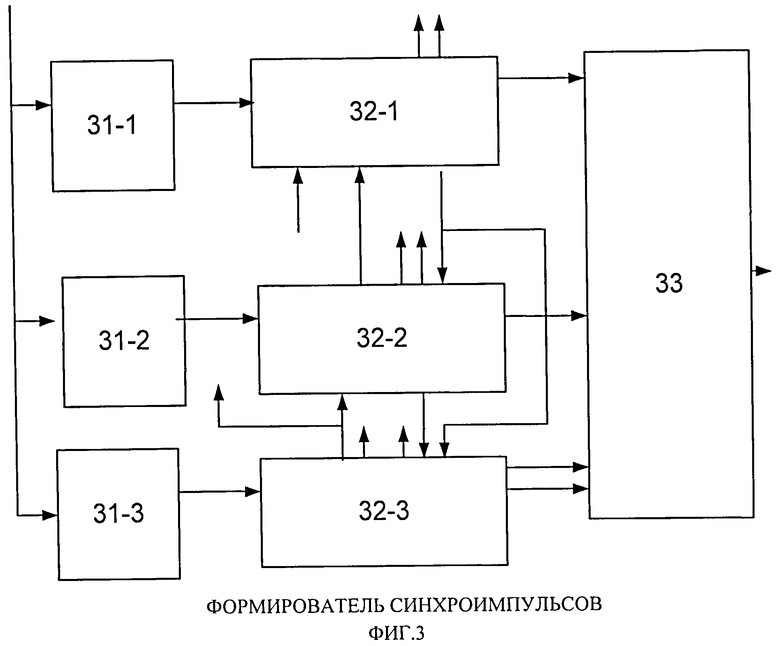

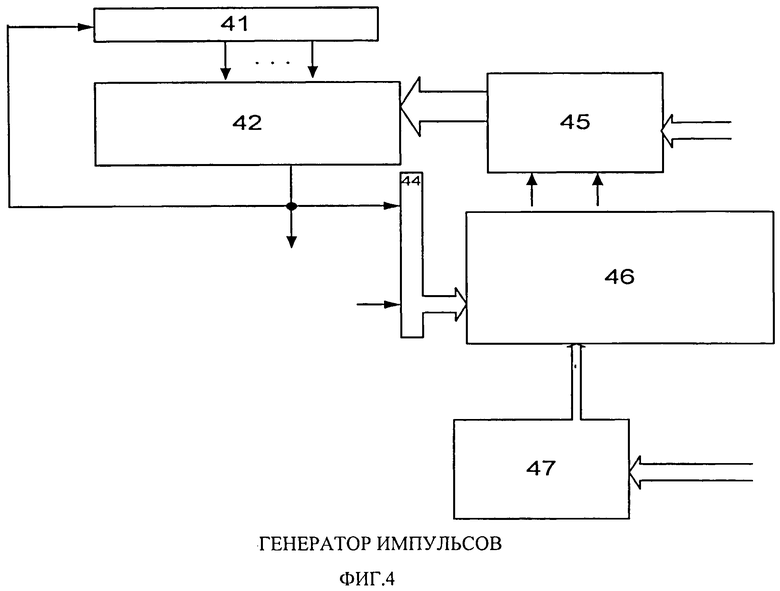

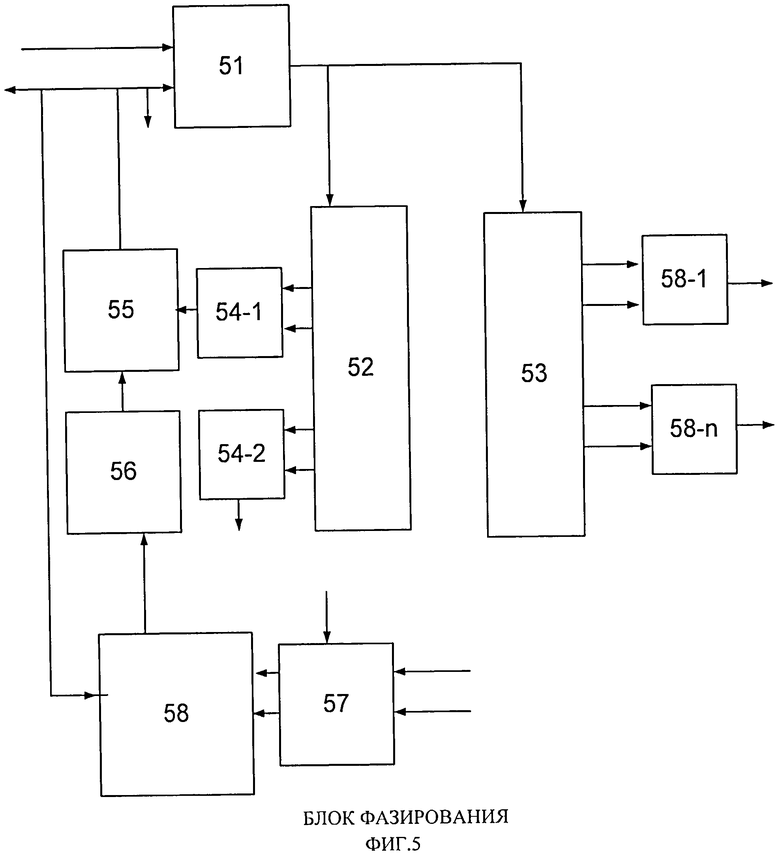

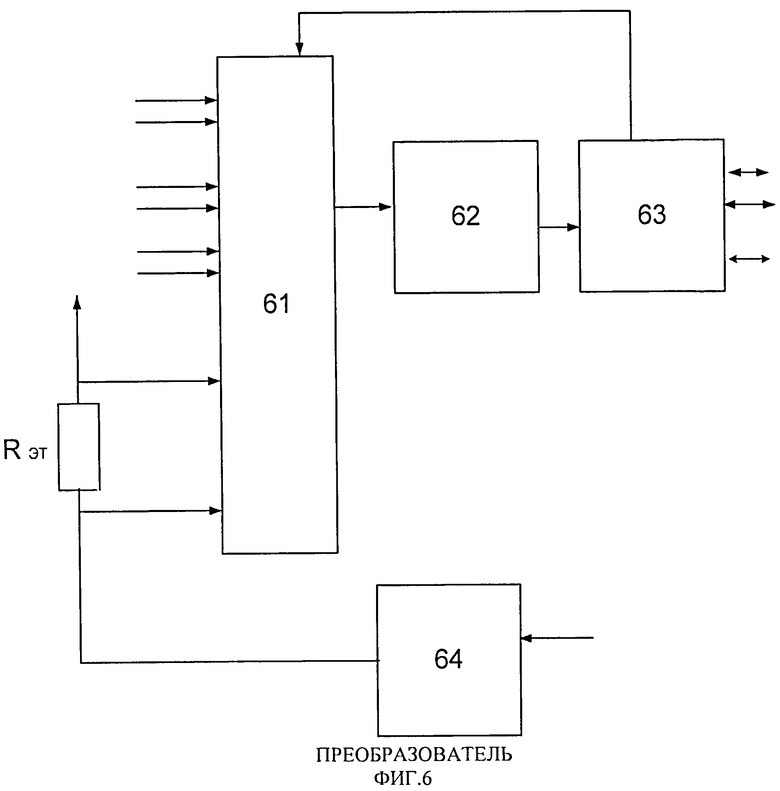

Состав системы приведен на фигуре 1, где цифрой 1 обозначены датчики, цифрой 1-1 - аппаратура спутниковой навигации, цифрой 1-2 - подсистема инерциальной навигации и цифрой 1-3 - подсистема оптической коррекции, цифрой 2 обозначен блок сбора информации (БСИ), цифрами 3-1, 3-2 и 3-3 обозначены управляющие вычислительные устройства, цифрой 4 - формирователь синхроимпульсов, цифрой 5 - переключатель каналов УВУ, цифрой 6 - блок контроля и управления (БКУ), цифрой 7 - исполнительные органы (ИО) объекта управления с датчиками обратной связи. Датчики 1 подключены к блоку сбора информации, входы-выходы которого подключены к входам-выходам УВУ. Выходы УВУ подключены через переключатель каналов к исполнительным органам, а выходы входящих в состав ИО датчиков обратных связей подключены к входам блока сбора информации, токовые выход и вход, выделенный на фигуре жирной линией, последовательно подключены к датчикам 1 и датчикам обратной связи, входящим в состав ИО. Выходы меток времени ФСИ подключены к входам прерывания УВУ, а его синхронизирующие выходы подключены к входам синхронизации УВУ, БСИ и БКУ. Управляющий вход ФСИ подключен к выходу переключателя каналов. На фигуре 2 приведен состав блока сбора информации. Блок содержит приемные регистры 21, входы которых являются входами блока, преобразователь «аналог-код» 22, токовый вход-выход которого является одноименным входом-выходом блока. Приемные регистры и преобразователь подключены через схемы гальванической развязки 23 к узлу связи, вход-выход которого является входом-выходом блока, подключенным к УВУ. Управляющий выход узла связи подключен к управляющему входу преобразователя. ФСИ (См. фигуру 3) содержит три генератора импульсов 31-1, 31-2 и 31-3, каждый из которых подключен к своему блоку фазирования 32-1, 32-2 и 32-3, фазирующий выход каждого из которых подключен к фазирующим входам двух других формирователей. Выходы метки времени боков подключены к мажоритарному элементу, выход которого является выходом формирователя и блока в целом. Генератор импульсов (См. фиг.4) содержит n последовательно соединенных инверторов 41, подключенных к мультиплексору 42, выход которого является выходом генератора и подключен к входу первого инвертора и входу счетчика частоты 44. Управляющий вход мультиплексора подключен к выходу счетчика кода частоты 45, инкрементный и декрементный входы которого подключены к одноименным выходам схемы сравнения 46. Первый вход схемы сравнения подключен к выходу счетчика частоты. А второй вход - к выходу регистра кода частоты 47. При этом входы счетчика кода частоты и регистра кода частоты являются управляющим входом генератора. Блок фазирования (См. фиг.5) содержит элемент И 51, первый вход которого является входом формирователя, подключенным к генератору импульсов. Выход элемента подключен к счетчику 52 и сдвиговому регистру 53. Выходы счетчика подключены к входам первого 54-1 и второго 54-2 дешифраторов. Выход первого дешифратора подключен к входу триггера останова 55, выход которого является фазирующим выходом формирователя и подключен ко второму входу элемента И и первому входу мажоритарного элемента 58, к второму и третьему входу которого подключены выходы триггеров привязки 57, входы которых являются фазирующими входами формирователя, их синхронизирующий вход объединен с первым входом элемента И. Выход второго дешифратора является выходом метки времени блока и формирователя в целом. Выход мажоритарного элемента подключен к входу триггера пуска 56, выход которого подключен к сбрасывающему входу триггера останова. Выходы нечетных и четных разрядов сдвигового регистра подключены к запускающим и сбрасывающим входам n триггеров формирователей синхроимпульсов (58-1 - 58-n), выходы которых являются синхронизирующими выходами блока и формирователя в целом. Преобразователь (См. фиг.6) содержит коммутатор 61, информационные входы которого являются входами преобразователя, выход подключен к преобразователю напряжения в частоту 62, выход которого подключен к блоку связи 63, вход-выход которого является входом-выходом преобразователя. Кроме того, преобразователь содержит источник тока 64, выход которого через последовательно включенный эталонный резистор Rэт поступает на выход для запитки внешних резисторных датчиков, а токовый вход источника является входом преобразователя для шины, приходящей от внешних датчиков. Управляющий выход блока связи подключен к управляющему входу коммутатора, а его управляющий вход является одноименным входом преобразователя. Система работает следующим образом.

После включения питания начинают работать генераторы импульсов ФСИ и через несколько периодов высокой частоты с выхода ФСИ в УВУ начинают поступать синхронно и синфазно метки времени на вход прерывания и синхроимпульсы на синхровходы УВУ и остальных модулей системы, УВУ приступают к выполнению программ управления, опрашивая через блок сбора информации внешние датчики и корректирующие подсистемы АСН, ПИН и ПОК. Результаты вычислений выдаются через переключатель каналов на ИО объекта управления, выходная информация всех каналов УВУ поступает одновременно в блок контроля и управления переключателем, в который, кроме того, поступают сигналы неисправности, вырабатываемые встроенными в каждое УВУ аппаратурными средствами контроля, например по mod3. Можно обозначить сигналы от этих средств через Нi, где i - номер УВУ(1, 2 или 3). Для логики работы переключателя все УВУ расположены по кольцу: 1, 2, 3, 1. Таким образом для УВУ3(i) УВУ2 будет иметь индекс i-1, a УВУ 1 будет иметь индекс i+1 и т.д. При обнаружении неисправности i-го УВУ переключатель подключает к выходу сигналы предыдущего по номеру, т.е. i-1 вычислителя. В случае неисправности двух вычислителей к выходу подключены сигналы третьего исправного. Таким образом, после возникновения первого отказа к выходу подключены сигналы всегда одного вычислителя, что существенно снижает вероятность отказа системы после возникновения первой неисправности.

В случае формирования сигналов неисправности трех вычислителей, что может быть следствием ограниченной достоверности работы встроенных средств контроля или схем сравнения, к выходу остается подключенным последний признанный исправным вычислитель, что исключает неопределенность в логике работы переключателя.

Логику выработки сигналов неисправности УВУ, вырабатываемых БКУ, по которым происходит переключение каналов, можно представить в виде логической формулы Обозначим:

Нi - неисправность i-го УВУ, нi - неисправность этого же вычислителя, сформированную внутренними средствами контроля,

Ci - неисправность этого же вычислителя, сформированную схемами сравнения.

Тогда Нi=Сi ∨ нi

Логику выработки сигнала неисправности, формируемого схемами сравнения, можно записать следующим образом:

сi=(иi ∧ иi+1 ∧ JИi-1 ∨ иi ∧ иi-1 ∧ иi+1) ∨ (Jиi ∧ Jиi+1 ∧ иi-1 ∨ иi ∧ J и i+1 ∧ иi-1 ∨ Jиi ∧ Jиi-1 ∧ иi+1).

Таким образом, введение переключателя с блоком контроля и управления позволяет нейтрализовать по крайней мере две неисправности в вычислительных устройствах и сохраняет вероятность работоспособности системы при трех неисправностях УВУ. Наличие в ФСИ трех генераторов импульсов и трех взаимно фазируемых блоков фазирования обеспечивает нейтрализацию как одной постоянной неисправности в ФСИ, так и нейтрализацию кратковременных отказов (сбоев) в формирователе, в которых реализована функция взаимного фазирования за 2-3 периода высокой частоты. После чего начинается формирование синхронных и синфазных меток реального времени и синхроимпульсов, обеспечивающих работу УВУ и системы в целом.

Введение перестройки частоты генераторов импульсов, входящих в состав УВУ, позволяет на каждый интервал времени установить частоту синхронизации, соответствующую текущему быстродействию цифровых узлов, что позволяет не только повысить надежность работы системы при снижении быстродействия, но и использовать возникающие запасы по быстродействию, для чего предусмотрено периодическое выполнение программ тестовых проверок УВУ, позволяющее оценить работоспособность при текущей или устанавливаемой частоте синхронизации.

Для нейтрализации параметрических уходов аналоговых узлов в блоке сбора информации в качестве основного выбран преобразователь напряжения в частоту, обладающий тем несомненным преимуществом, что зависимость точности и стабильности его работы определяется всего двумя элементами - резистором и конденсатором, выбором типов которых и предварительной их термотренировкой можно обеспечить требуемую стабильность на продолжительном интервале времени. Нестабильность работы источника тока, необходимого для запитки датчиков в предложенной системе, нейтрализуется установкой в токовую цепь высокостабильного эталонного резистора, замеряя падение напряжения, на котором определяют текущее значения тока опроса датчиков и проводят необходимый пересчет результатов замеров.

Совокупность предложенных решений в виде дополнительных блоков, организации перестройки структуры при возникновении отказов, а также нейтрализация параметрических уходов параметров как цифровых узлов, так и аналоговых позволяет существенно повысить надежность и точность работы системы управления, работающей длительное время в условиях воздействия внешних дестабилизирующих факторов, что существенно расширяет по сравнению с известными решениями диапазон применения системы для объектов различного назначения.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 2011 |

|

RU2494006C2 |

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 2013 |

|

RU2534955C1 |

| СИСТЕМА УПРАВЛЕНИЯ КОСМИЧЕСКОГО АППАРАТА | 2013 |

|

RU2560204C2 |

| МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2474868C1 |

| СИСТЕМА УПРАВЛЕНИЯ ПОДВИЖНЫМИ ОБЪЕКТАМИ | 2011 |

|

RU2503581C2 |

| МОДЕЛИРУЮЩИЙ КОАП | 2013 |

|

RU2516703C1 |

| ТЕХНОЛОГИЧЕСКАЯ УВМ | 2013 |

|

RU2563139C2 |

| СБОЕУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2541839C2 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2536434C2 |

| СИСТЕМА АСТРОНАВИГАЦИИ | 2013 |

|

RU2548927C1 |

Изобретение относится к системам автоматического управления, работающих длительное время при воздействии неблагоприятных внешних факторов. Система управления, содержащая три управляющих вычислителя с подключенными к ним через блок сбора информации датчиками, аппаратурой спутниковой навигации, подсистемой инерциальной навигации, подсистемой оптической коррекции, содержит формирователь синхроимпульсов, переключатель каналов вычислителей, подключенный входами к вычислителям, а выходом - к исполнительным органам с датчиками обратной связи и формирователю синхроимпульсов, блок контроля и управления. Блок контроля и управления подключен входами к выходам вычислителей и их контрольных устройств, а выходами - к управляющему входу переключателя, причем выходы датчиков и датчиков обратной связи подключены к входам блока сбора информации, токовая шина которого последовательно проходит через датчики и датчики обратной связи исполнительных органов и возвращается в блок сбора информации, входы-выходы которого подключены к вычислителям. Достигается повышение надежности и точности работы системы управления. 5 з.п. ф-лы, 6 ил.

1. Система управления, содержащая три управляющих вычислителя с подключенными к ним через блок сбора информации датчиками, аппаратурой спутниковой навигации, подсистемой инерциальной навигации, подсистемой оптической коррекции, содержащая формирователь синхроимпульсов, отличающаяся тем, что в ее состав введены переключатель каналов вычислителей, подключенный входами к вычислителям, а выходом - к исполнительным органам с датчиками обратной связи и формирователю синхроимпульсов, блок контроля и управления, подключенный входами к выходам вычислителей и их контрольных устройств, а выходами - к управляющему входу переключателя, причем выходы датчиков и датчиков обратной связи подключены к входам блока сбора информации, токовая шина которого последовательно проходит через датчики и датчики обратной связи исполнительных органов и возвращается в блок сбора информации, входы-выходы которого подключены к вычислителям.

2. Система по п.1, отличающаяся тем, что блок сбора информации содержит приемные регистры и преобразователь информации, входы которых являются входами блока, а выходы через схемы гальванической развязки подключены к узлу связи, входы-выходы которого являются входами-выходами блока, а управляющий выход подключен к управляющему входу входящего в состав блока преобразователя «аналог-код», токовая шина которого подключена последовательно к датчикам и датчикам обратной связи, после которых возвращается на вход блока.

3. Система по п.1, отличающаяся тем, что формирователь синхроимпульсов содержит три генератора импульсов, выход каждого из которых подключен к своему блоку фазирования, фазирующий выход каждого из которых подключен к фазирующим входам двух других блоков, а выходы меток времени блоков подключены к мажоритарному элементу, выход которого является одноименным выходом формирователя, а выходы синхроимпульсов блоков являются одноименными выходами формирователя.

4. Система по п.3, отличающаяся тем, что генератор импульсов содержит n последовательно соединенных инверторов, выходы которых подключены к входам мультиплексора, выход которого является выходом генератора и подключен к входам первого инвертора и счетчика частоты, выход которого подключен к первому входу схемы сравнения, ко второму входу которой подключен выход регистра кода частоты, а инкрементный и декрементный выходы схемы сравнения подключены к одноименным входам счетчика кода частоты, выходы которого подключены к управляющим входам мультиплексора, причем входы счетчика кода частоты и регистра кода частоты являются управляющим входом генератора.

5. Система по п.3, отличающаяся тем, что блок фазирования содержит элемент И, первый вход которого является входом блока, а выход подключен к сдвиговому регистру и счетчику, выходы которого подключены к первому и второму дешифраторам, причем выход первого дешифратора подключен к запускающему входу триггера останова, выход которого является фазирующим выходом формирователя и подключен ко второму входу элемента И и первому входу мажоритарного элемента, ко второму и третьему входам которого подключены выходы триггеров привязки, входы которых являются фазирующими входами формирователя, а их синхронизирующий вход объединен с первым входом элемента И, при этом выход второго дешифратора является выходом метки времени блока, а нечетные и четные выходы сдвигового регистра подключены к запускающим и сбрасывающим входам триггеров-формирователей, выходы которых являются синхронизирующими выходами блока.

6. Система по п.2, отличающаяся тем, что преобразователь содержит коммутатор, входы которого являются входами преобразователя, а выход подключен к схеме преобразования напряжения в частоту, выход которой подключен к узлу связи, входы-выходы которого являются входами-выходами преобразователя, а управляющий выход подключен к управляющему входу коммутатора, к дополнительным входам которого подключены выводы эталонного резистора, включенного в шину источника тока, которая поступает на выход и возвращается на вход источника и после прохождения внешних датчиков.

| СИСТЕМА УПРАВЛЕНИЯ СУДНОМ | 2010 |

|

RU2424944C1 |

| СИСТЕМА УПРАВЛЕНИЯ СУДНОМ | 2010 |

|

RU2428350C1 |

| АППАРАТУРА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ ДВИЖЕНИЕМ СУДНА | 2002 |

|

RU2221728C1 |

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ СУДНОМ | 2004 |

|

RU2248914C1 |

Авторы

Даты

2014-09-10—Публикация

2011-10-28—Подача