го элементов И и вторым входом пятого элемента И,, второй выход первого триггера соединен, с вторыми входами второго счетчика, второго и шестого элементов И и первым входом четвертого элемента И., первый выход первогч5 дешифратора соединен с вторым входом третьего элемента И, второй вход - с вторым входом первого элемента И и третьим входом второго элемента И, третий выход - с вторым входом четвертого элемента И, четвертый и пятый выходы дешифратора соединены соответственно с первым входом второго триггера и третьим входом шестого элемента И, второй . вход второго триггера соединен с выходом элемента ИЛИ, первый и второй входы которого соединены с выходами первого и второго элементов И, вь1ход второго триггера соединен с третьими входами третьего и пятого элементов И, выходы первого и второго

элементов И обраэуют второй выход

I

блока, выходы третьего, четвертого и шестого элементов И,, задающего генератора и элемента ИЛИ являются соответственно третьим, четвертым, седьмым, первым и пятым выходами блока, четвертый выход первого дешифратора и выход пятого элемента И образуют шестой выход блока.

2. Устройство по П.1, О т л и чаюадееся тем, что блок останова содержит сукматор-вычитатель регистр адреса останова и формирователь импульса, причем первый вход сумматора-вычитателя является вторым входом блока,, а второй вход соединен с шиной константы,.информационный вход регистра адреса останова является первым входом блока, а выход является первым выходом блока, выход сумматора-вычитателя через формирователь импульса соединен с управляющим входом регистра адреса останова и с вторым выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения интерфейса ввода-вывода с регистратором | 1983 |

|

SU1144100A2 |

| Устройство для сопряжения интерфейсов ввода-вывода с регистратором | 1987 |

|

SU1413636A1 |

| Устройство для сопряжения | 1983 |

|

SU1129603A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для ввода информации | 1981 |

|

SU1005019A1 |

| Устройство для формирования тестов субблока логического блока | 1987 |

|

SU1513453A1 |

| Устройство для контроля и регистрации асинхронных сигналов интерфейса | 1982 |

|

SU1084803A1 |

| Устройство для контроля интерфейса ввода-вывода | 1991 |

|

SU1798792A1 |

| Устройство для отладки и контроля хода программ | 1988 |

|

SU1529227A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

1. УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ИНТЕРФЕЙСА ВВОДА-ВЫВОДА С РЕГИСТРАТОРОМ, содержащее регистр состояния интерфейса, информационный вход которого является информационным входом устройства, блок местной памяти, первый информационный вход которого соединен с выходом регис-. тра состояния интерфейса, таймер, блок управления, информационный постоянный запоминающий блок, выход которого соединен с первым входом блока согласования, выход которого является выходом устройства, выход блежа местной памяти соединен с вторым входом блока согласования, первый-четвертый выходы блока управления соединены соответственно с входом таймера управляющими входами блока местной памяти и регистра состояния интерфейса, третьим входом блока согласования, первый вход блока управления является входом задания режима устройства, отличающееся тем,что, с целью расширения класса решаемых задач, оно содержит схему сравн,ения, счетчик адресов, счетчик интервалов времени, блок останова, регистр времени останова, адресный постоянный запоминаю{4ий блок, причем выход регистра состояния интерфейса соединен с первым входом схемы сравнения, второй вход которой соединен с информационным входом устройства, а выход соединен с вторым входом блока управления, пятЕлй, шестой и седьмой выходы которого соединены соответственно со счетным входом счетчика адресов, управляющим входом счетчика интервалов времени и входом адресного постоянного запоминающего блока, выход которого соединен с входом информационного постоянного запоминающего блока, выход таймера соединен с информационными входами регистра времени останова и счетчика интервалов времени, выход счетчика адресов соединен с адресным входом блока местной памяти и первым входом блока останова, второй вход блока останова и второй информационный вход блока местной памяти соединены с выходом счетчика интервалов времени, первый и второй выходы блока останова соединены соответственно с блокирующими входами счетчика адресов и регистра времени останова, выход которого соединен с четвертьвч входом блока согласования, причем блок управления содержит задаквдий генератор, элемент 2И-ИЛИ, три счетчика, два дешифратора, два триггера, первый-шестой элементы И и элемент ИЛИ причем выход задающего генератора соединен с первьм и вторым входами элемента 2И-ИЛИ.Н первым входом пятого элемента И, третий и четвертый входы СЛ элемента 2 Й-ИЛИ являются соответст венно первым и вторым входами блока, :о ;о выход элемента 2И-ИЛИ соединен с входом счетчика,- выход которого соединен с входом первого дешифратора и первьФл входом второго счетчиКа, выход которого соединен с первым вхо дом шестого элемента И и входом второго дешифратора, выход которого соединен с входом третьего сче-тчика, выход которого соединен с первым входом второго элемента И-, вход первого триггера соединен с первым входом блока, а первый выход соединен с первыми входами первого и третье

Изобретение относится к цифровой вычислительной технике и может быть использовано для контроля ввода-вывода цифровых вычислительных машин и систем.

Известно устройство для измерения времени работы устройств ввода:вывода, содержащее таймер, блок .опроса, первый и второй регистры, блок преобразования кодов., блок сопряжения, регистратор, блок памяти, счетчики, сумматор ell.

Недостатком известного устройства являются его малые функциональные возможности.

Наиболее близким по технической сущности к предлагаемому является устройство для регистрации, содержащее усилители-приемники, вход кото. рых соединен с первым входом устройства, первый регистр состояния интерфейса , первый блок которого подключен к выходу усилителей-приемников, блок местной памяти первый вхо которого соединен с выходом первого регистра состояния интерфейса, блок таймера, блок информационного постоянного запоминающего устройства, регистратор, блок сопряжения с регистратором, два первых входа которого соединены соответственно с выходом блока местной памяти и выходом блока информационного постоянного запоминающего устройства, а выход подключен к входу регистратора, блок управления, первый вход KOTOjioro под

ключен к второму входу устройства, а первые четыре выхода - соответственно к второму входу блока местной памяти, к второму входу первого ре гистра состояния интерфейса, входу блока таймера и третьему входу блока таймера и третьему входу блока сопряжения с регистратором 721.

Недостатком прототипа являются его малые функциональные возможности

Цель настоящего изобретения расширение класса решаемых зада.ч. Поставленная цель достигается тем, что в устройство, содержащее регистр состояния интерфейса, инфор мационный вход которого является информационным входом устройства, блок местной памяти, первый инфогмационный вход которого соединен с выходом регистра состояния интерфейса, таймер, блок управления, информационный постоянный запоминающий блок, выход которого соединен с первым входом блока согласования, выход которого является выходом устройства, выход блока местной памяти соединен с вторым входом блока согласования, первый-четвертый выходы блока управления соединены соответственно с входом таймера, управляющими входами блока местной памяти и регистра состояния интерфейса, третьим входом блока согласования, первый вход блока управления является входом задания режима устройства, введены схема сравнения,счетчик адресов, счетчик интервалов времени, блок останова, регистр времени останова, адресный постоянный запоминающий блок, причем выход регистра состояния интерфейса соединен с первым входом схемы сравнения, второй вход которой соединен с информационным входом устройства/, а выход соединен с вторым входом блока управления, пятый, шестой и седьмой выходы которого соединены соответственно со счетным входом счетчика адресов, управляющим входом-счетчика интервалов {времени и входом адресного постоянного запоминающего блока, выход которого соединен с входом информационного постоянного запоминающего блока, выход таймера соединен с информационными входами регистра времени останова и счетчика интервалов времени, выход счетчика адресов соединен с адресным входом блока местной памяти, и первым входом блока останова, второй вход блока останова и второй информационный вход блока местной памяти соединены с выходом счетчика интервалов времени, первый и .второй выходы блока останова соединены соответственно с блокирующими входами счетчика адресов и регистра времени останова, выход которого соединен с четвертым входом блока согласования, причем блок управления содержит задающий генератор, элемент 2И-ИЛИ, три счетчика, два дешифратора, два триггера, первый-шестой элементы И и элемент ИЛИ-, причем выход задающего генератора соединен с первым и вторым входами элемента 2И-ИЛИ первым входом пятого элемента И, третий и четвертый входы элемента 2И-ИЛИ являются соответственно первым и вторым вхрдами блока, выход элемента 2И-ИЛИ соединен с входом счетчика,выход которого соединен с входом первого дешифратора и первым входом второго счетчика, выход которого соединен с первым входом шестого элемента И и входом второго дешифратора, выход которого соединен с входом третьего счетчика, выход которого соединен с первым входом второго элемента И, вход первого триггера соединен с первым входом блока, а первый выход соединен с первыми входами первого и третьего элементов И и вторым входом пятого элемента И, второй выход первого триггера соединен с вторыми входами второго счетчика, второго и шестого элементов И и первым входом четвертого элемента И-, первый выход первого .дешифратора соединен с вторым входом третьего элемента И,второй вход. - с йторым входом первого элемента И и третьим входом второго элемента И, третий выход - с вторым входом четвертого элемента И, четвертый и пятый выходы дешифратора сбедияены соответственно с первым входом второго триггера и третьим

входом шестого элемента и-, второй вход второго триггера соединен с вы ходом элемента ИЛИ, первый и второй входы которого соединены с выходами первого и второго элементов И, выход второго триггера соединен с третьими входами третьего и пятого элементов И, выходы первого и второго элементов И образуют второй выход блока, выходы третьего, четвертого и шестого элементов И, задающего генератора и элемента ИЛИ являются соответственно третьим, четвертым,седмым, первым и пятым выходами блока, четвертый выход первого дешифратора и выход пятого элемента И образуют шестой выход блока.

Блок останова содержит сумматоровычитатель, регистр адреса останова и формирователь импульса причем первый вход сумматора-вычитателя является вторым входом блока, а второй вход соединен с шиной константы информационный вход регистра адреса останова является первым входом блока, а выход является первым выходом блока,выход сумматора-вычитателя через формирователь .импульса соединен с управляющим входом регистра ареса останова и с вторым выходом блка .

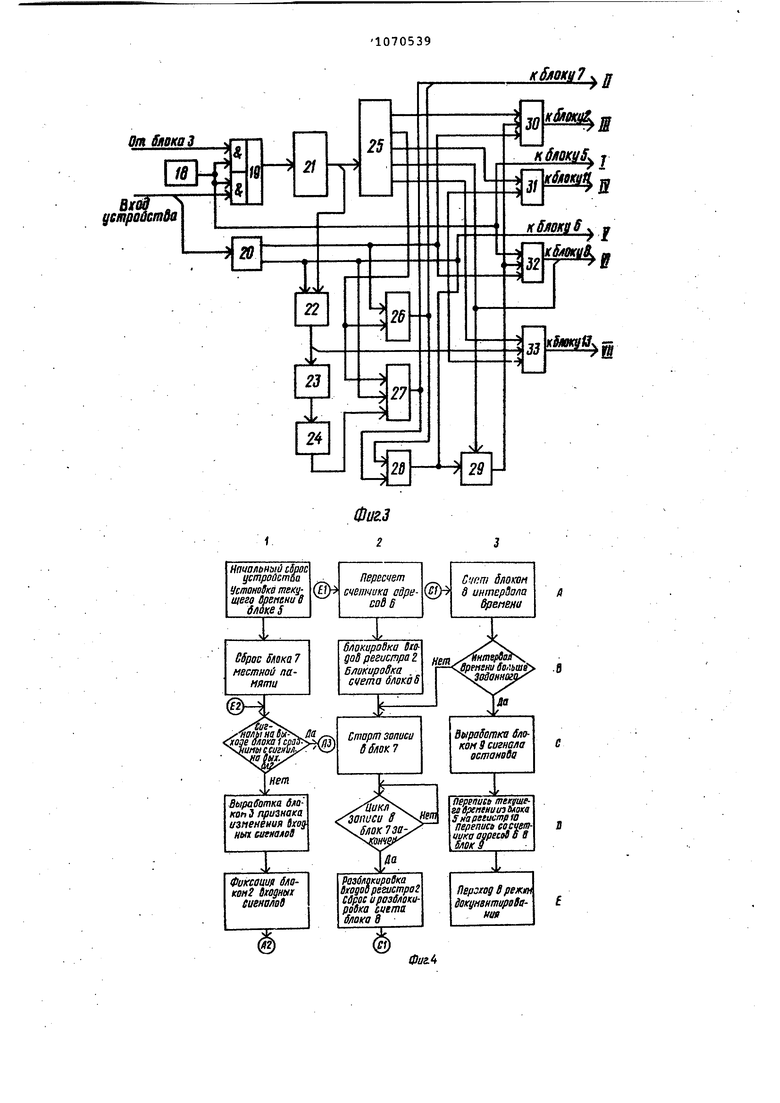

На-фиг. приведена структурная схема устройства; на фиг.2 - структурная схема бгока останова, на фиг.3 - структурная схема блока управления; на фиг.4 - блок-схема алгоритма работы устройства при фиксаци состояний интерфейса ввода-вывода в блоке местной памяти; на фиг.5 блок-схема алгоритма работы устройства при документировании информации на регистраторе; на фиг.6 - временная диаграмма работы блока управления устройства при фиксации состояний интерфейса ввода-вывода; на фиг.7 - временная диаграмма работы блока управления устройства при документировании информации на регистраторе.

Устройство (фиг.1) содержит информационный вход 1, регистр) 2 состояния интерфейса, схему 3 сравнения, блок 4 управления, таймер 5, счетчик б адресов, блок 7 местной памяти, счетчик 8 интервалов времени, блок 9 останова, регистр 10 времени останова, блок 11 согласования, регистратор 12, адресный постоянный запоминающий блок 13, информационный постоянный запоминающий блок 14.

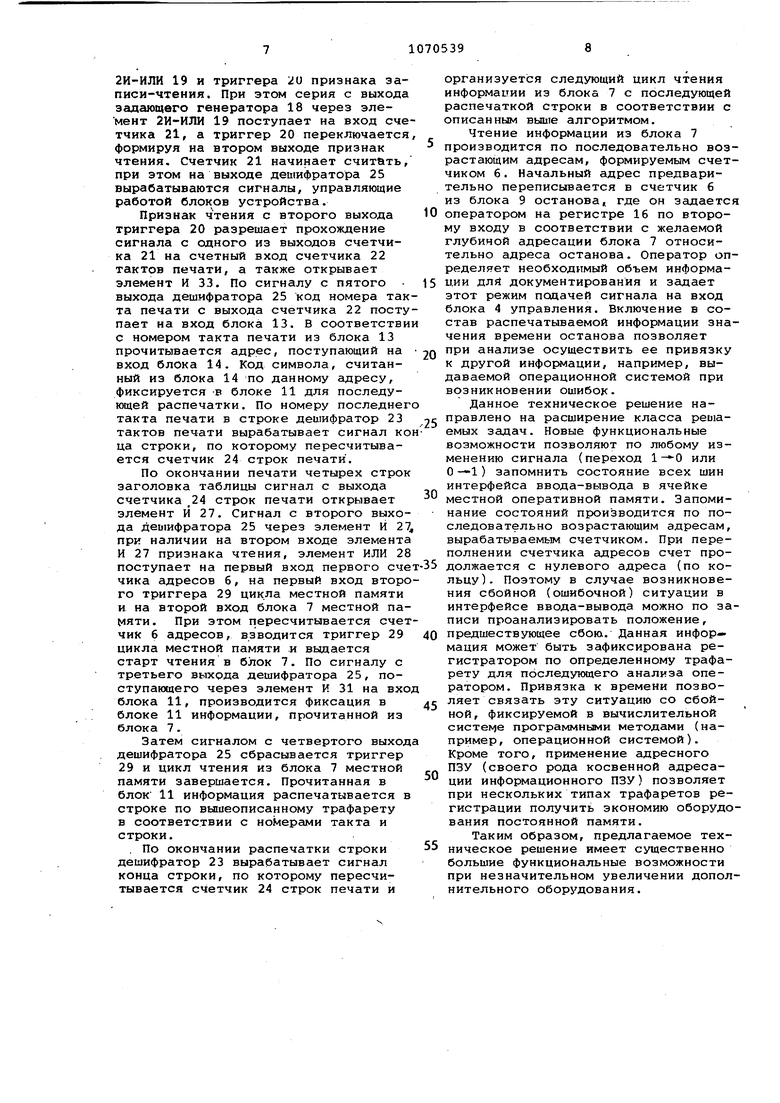

Блок 9 останова (фиг.2) содержит сумматор-вычитатель 15, регистр 16 адреса останова и формирователь 17 импульса. Блок 4 управления (фиг.З) содержит задающий генератор 18, элемент 2И-ИЛИ 19, первый триггер 20, первый счетчик 21, второй счетчик 22, второй дешифратор 23, третий счетчик 2, первый дешифратор 25, первый 26 и второй 27 элементы И, элемент 28 ИЛИ, второй триггер 29 третий 30, четвертый 31, пятый 32 и шестой 33 элементы И, Регистратором 12 может быть, например, электрифицированная пишущая машина типа Консул-256. Устройство работает следующим образом. До установки режима фиксации (записи) состояния интерфейса ввода-вывода в блоке местной памяти (фиг.4 и 6) устройство находится в исходном состоянии. В исходном состоянии все регистры и счетчики устройства сброшены. Задающий генератор 18 формирует серию, поступающую в таймер 5 для выработки значения текущего времени. Оператор задает режим записи, при этом взводится триггер 20 (признака записи или чтения) блока 7 местной памяти. Серия с выхода задающего генератора через элемент И 32 поступит на счетный вход счетчика 8 (интервал звремени) при наличии на входе элемента И 32 признака записи и сброшенном триггере 29 (цикла местной памяти). Сигналы идентификации из интерфей са ввода-вывода поступают на первый вход схемы 3 сравнения, а на второй вход схемы 3 поступает информация с выхода регистра 2 состояния интерфейса. Начальное значение разрядов информации регистра 2 нулевое и отли чается от значений i-того состояния шин интерфейса ввода-вывода. Поэтому схема 3 вырабатывает признак изменения входных сигналов (признак несрав нения), который поступает в блок 4 управления на вход элемента 2И-ИЛИ 19, открывая прохождение серии от задающего генератора 18 на вход счет чика 21. Счетчик 21 начинает считать при этом на выходе дешифратора 25 формируются сигналы управления, организующие работу блоков устройства. По сигналу с первого выхода дешифратора 25, поступающего на второй вход регистра 2 состояния интерфейса через элемент И 30, фиксируется на регистре 2 i-e состояние шин интерфейса. Сигнал с второго выхода дешифратора 25 череэ элемент. И 26, при наличии на первом входе элемента И 26 признака записи, элемент ИЛИ 28 поступает на первый вход счетчика адресов 6, на первый вход триггера 2 цикла местной памяти и на второй вхо блока местной памяти 7. При этом пересчитьшается счетчик 6 адресов, взводится триггер 29 и -вьщается стар записи в блок 7. Сигнал с выхода три гера 29 закрывает входы элементов И 30 и 32 на время, равное циклу записи информации с выходов регистра 2 и счетчика 8 интервалов времени в блок 7 местной памяти, б;юкируя пересчет счетчика 8 и вход регистра 2. По завершении записи информации в блок 7 сигналом с четвертого выхода дешифратора 25 сбрасываются счетчик 8 интервалов времени, триггер 29 Цикла местной памяти и разблокируются входы регистра 2 и счетчика 8. При очередном изменении состояния одной (или нескольких) шин идентификации в интерфейсе схема 3 вновь вырабатывает признак изменения входных сигналов и повторяется описанный вьлие алгоритм. При этом фиксируемая в блоке 7 информация записывается по последовательно возрастающим адресам, вырабатываемым счетчиком 6. При переполнении местной памяти запись производится по кольцу, снова начиная с нулевого адреса. Информация с выхода счетчика 8 поступает а блок 9 останова, где анализируется величина интервала времени от 1-го до i+l изменения состояния сигналов на шинах идентификации интерфейса ввода-вывода, в блоке 9 величина интервала поступает на первый вход сумматора-вычитателя 15, на второй вход которого подается константа интервала времени в обратном двоичном коде, Если величина интервала времени превьшлает значение константы, то на выходе сумматора-вычитателя 15 вырабатывается уровень, поступающий на вход формирователя 17. По импульсу с выхода формирователя 17 производится перепись со счетчика б на регистр 16 адреса ячейки, в которую записывалась последняя -информация о состоянии шин интерфейса перед остановом, а а также перепись на регистр 10 времени останова текущего времени из блока 5. По сигналу останова оператор может задать режим документирования накопленной в блоке 7 информации. В режиме документирования (фиг.5 и 7) производится чтение информации из блока 7 и распечатка информации в виде таблии.ы. Заголовок таблицы состоит из четырех строк, содержащих наименование информации документирования последующих строк таблицы. Строка таблицы содержит информацию о состоянии шин интерфейса ввода-вывода, о времени останова (часы, минуты,секунды), об интервале времени (мкс,нс) между двумя изменениями состояния шин интерфейса ввода-вывода. Описание трафаретов распечатки заголовка и последующих строк таблицы хранится в виде констант в блоке 14. Блок 13 определяет последовательность распечатываемой информации. В первую очередь распечатывается заголовок таблицы. Оператор задает признаки режима окументирования и чтения, поступаюие соответственно на входы элемента

2И-ИЛИ 19 и триггера признака записи-чтения. При этом серия с выхода задающего генератора 18 через элемент 2И-ИЛИ 19 поступает на вход счетчика 21, а триггер 20 переключается, формируя иа втором выходе признак чтения. Счетчик 21 начинает считать, при этом на выходе дешифратора 25 вырабатываются сигналы, управляющие работой блоков устройства.

Признак чтения с второго выхода триггера 20 разрешает прохождение сигнала с одного из выходов счетчика 21 на счетный вход счетчика 22 тактов печати, а также открывает элемент И 33. По сигналу с пятого выхода дешифратора 25 код номера такта печати с выхода счетчика 22 поступает на вход блока 13. В соответствии с номером такта печати из блока 13 прочитывается адрес, поступающий на вход блока 14. Код символа, считанный из блока 14 по данному адресу, фиксируется -в блоке 11 для последующей распечатки. По номеру последнего такта печати в строке дешифратор 23 тактов печати вырабатывает сигнал конца строки, по которому пересчитывается счетчик 24 строк печати.

По окончании печати четырех строк заголовка таблицы сигнал с выхода счетчика 24 строк печати открывает элемент И 27. Сигнал с второго выхода дешифратора 25 через элемент И 27, при наличии на втором входе элемента И 27 признака чтения, элемент ИЛИ 28 поступает на первый вход первого счет чика адресов б, на первый вход второго триггера 29 цикла местной памяти и на второй вход блока 7 местной памяти. При этом пересчитывается счетчик 6 адресов, взводится триггер 29 цикла местной памяти .и выдается старт чтения в блок 7. По сигналу с третьего выхода дешифратора 25, поступающего через элемент И 31 на вход блока 11, производится фиксация в блоке 11 информации, прочитанной из блока 7.

Затем сигналом с четвертого выхода дешифратора 25 сбрасывается триггер 29 и цикл чтения из блока 7 местной памяти завершается. Прочитанная в блок 11 информация распечатывается в строке по вышеописанному трафарету в соответствии с номерами такта и строки.

. По окончании распечатки строки дешифратор 23 вырабатывает сигнал конца строки, по которому пересчитывается счетчик 24 строк печати и

организуется следующий цикл чтения информации из блока 7 с последующей распечаткой строки в соответствии с описанным выи1е алгоритмом.

Чтение информации из блока 7 производится по последовательно возрастающим адресам, формируемым счетчиком 6. Начальный адрес предварительно переписывается в счетчик 6 из блока 9 останова, где он задаетс оператором на регистре 16 по второму входу в соответствии с желаемой глубиной адресации блока 7 относительно адреса останова. Оператор определяет необходимый объем информации дли документирования и задает этот режим подачей сигнала на вход блока 4 управления. Включение в состав распечатываемой информации значения времени останова позволяет при анализе осуществить ее привязку к другой информации, например, выдаваемой операционной системой при возникновении ошибокДанное техническое решение направлено на расширение класса решаемых задач. Новые функциональные возможности позволяют по любому изменению сигнала (переход или О -1) запомнить состояние всех шин интерфейса ввода-вывода в ячейке местной оперативной памяти. Запоминание состояний производится по последовательно возрастающим адресам, вырабатываемым счетчиком. При переполнении счетчика адресов счет продолжается с нулевого адреса (по кольцу). Поэтому в случае возникновения сбойной (ошибочной) ситуации в интерфейсе ввода-вывода можно по записи проанализировать положение, предшествующее сбою. Данная информация может быть зафиксирована регистратором по определенному трафарету для последующего анализа оператором. Привязка к времени позволяет связать эту ситуацию со сбойной, фиксируемой в вычислительной системе программньв 1и методами (например, операционной системой). Кроме того, применение адресного ПЗУ (своего рода косвенной адресации информационного ПЗУ) позволяет при нескольких типах трафаретов регистрации получить экономию оборудования постоянной памяти.

Таким образом, предлагаемое техническое решение имеет существенно большие функциональные возможности при незначительном увеличении дополнительного оборудования.

Фиг.1

Ys 7

I « 1 МГП

ч/

константа

Фиг.г

к5локи7

0

/

Задание нацального адреса опроса длаки

Инфорнация В блоке 11 BomoSa

А к распечатке

Пересчет 5четцика адреса в 8

f

Старт твния из 6flui(u 7

Форпиробанив 6л а коп 4 сигнала опроса SnoKu 7 а 8з8вдвние тригг&л цик/иг месгнва naff.

Останов распечатки

Серия задающего еенвратора ПППЛПППППППППППП Г1ПП dOoOffuieto w// 2fl|22 lJb4j4njmnJUinnJTJTJm

Фи&7

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для измерения времени работы устройств ввода-вывода | 1976 |

|

SU737944A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3899776, кл.а 06 F 3/00, | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-01-30—Публикация

1982-10-21—Подача